1

Изобретение относится к измерительной и вычислительной технике, устройствам запоминания и может быть использовано как совместно при построении высокопроизводительных систем сбора,и обработки аналоговых данных с использованием мультиплицированной структуры и ЭВМ, так и отдельно при построении многоканальных систем и буферных накопителей,

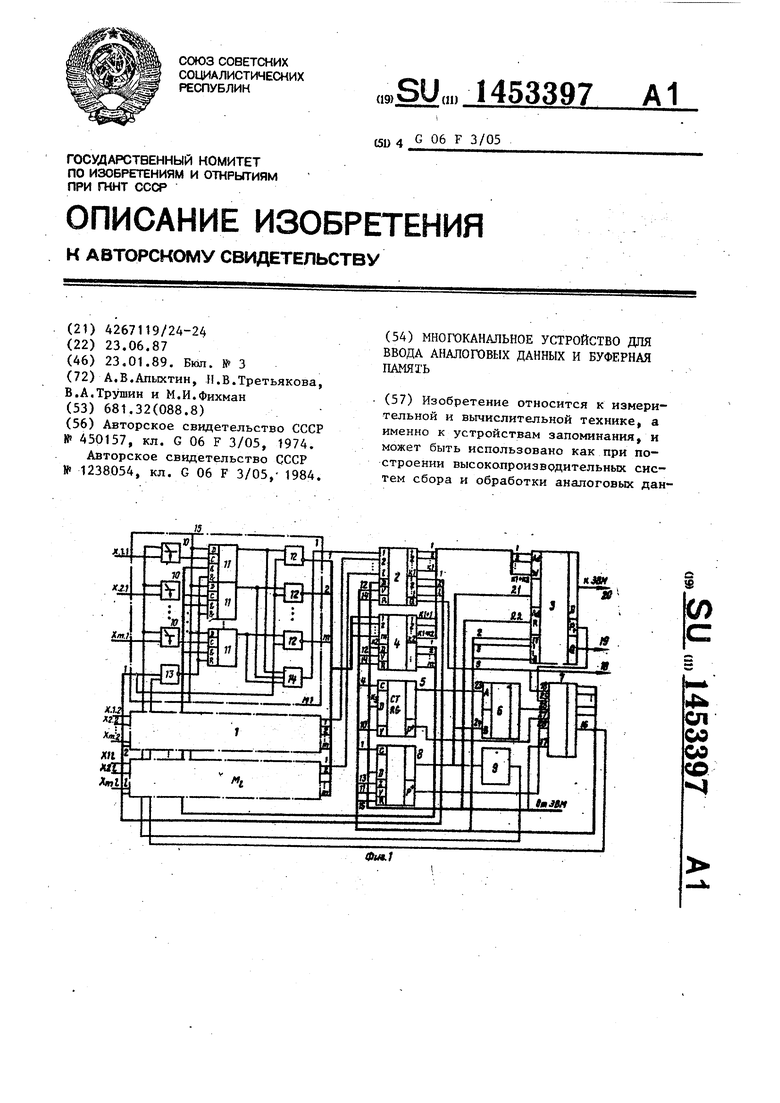

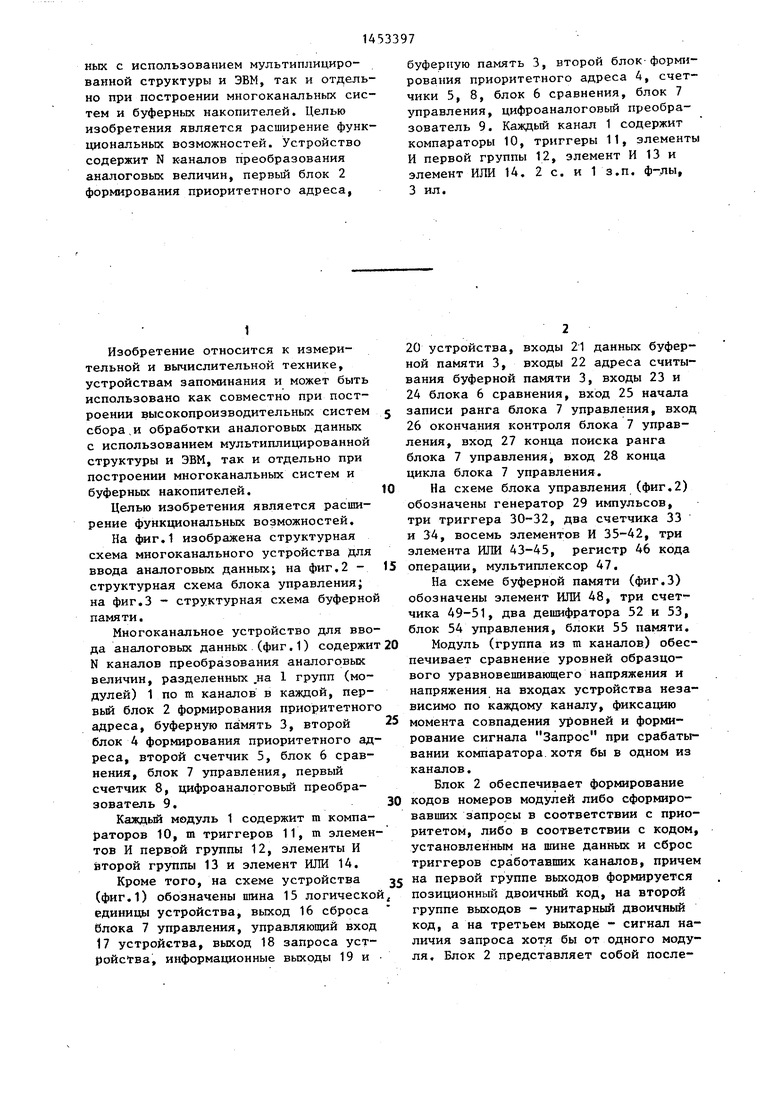

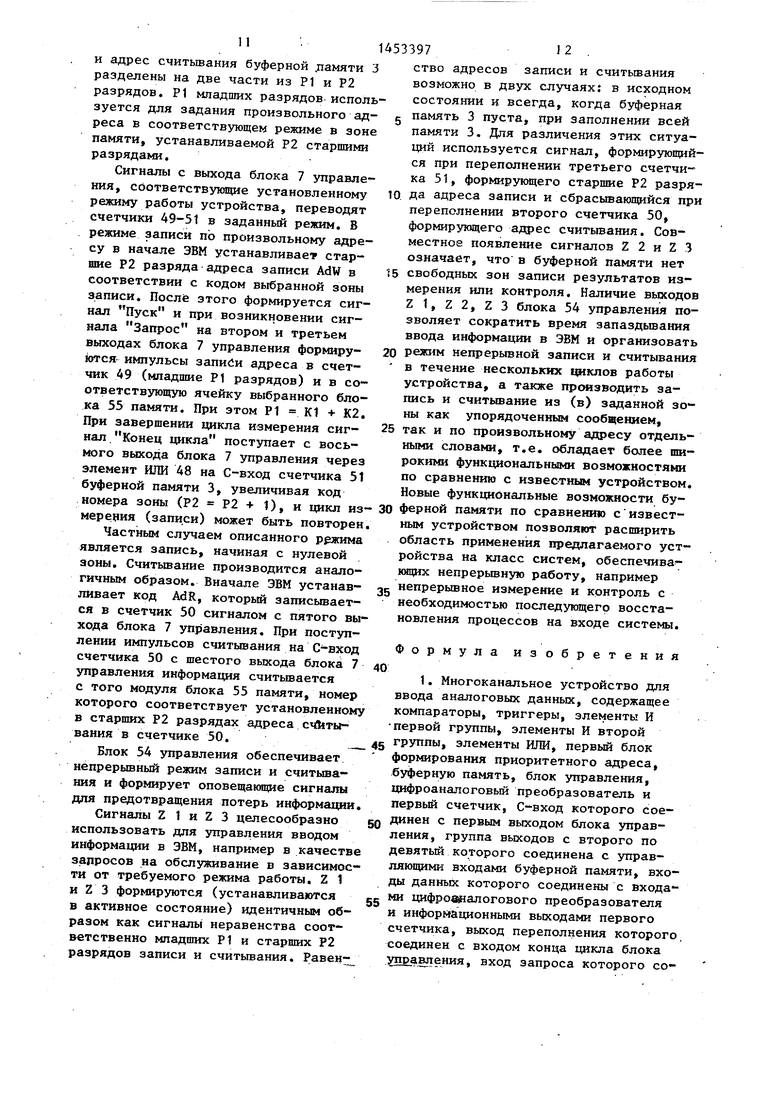

Целью изобретения является расширение функциональных возможностей. На фиг,1 изображена структурная схема многоканального устройства для ввода аналоговых данных; на фиг,2 - структурная схема блока управления; на фиг.З - структурная схема буферно памяти.

Многоканальное устройство для ввода аналоговых данньгх (фиг, 1) содержи N каналов преобразования аналоговых величин, разделенных .на 1 групп (модулей) 1 по m каналов в каждой, пер- вьй блок 2 формирования приоритетног адреса, буферную память 3, второй блок 4 формирования приоритетного адреса, второй счетчик 5, блок 6 сравнения, блок 7 управления, первый счетчик 8, цифроаналоговьш преобразователь 9,

Каждый модуль 1 содержит m компараторов 10, m триггеров 11, m элементов И первой группы 12, элементы И второй группы 13 и элемент ИЛИ 14,

Кроме того, на схеме устройства (фиг,1) обозначены шина 15 логическо единицы устройства, выход 16 сброса блока 7 управления, управляющий вход 17 устройства, выход 18 запроса устройства, информационные выходы 19 и

20 устройства, входы 21 данных буферной памяти 3, входы 22 адреса считывания буферной памяти 3, входы 23 и 24 блока 6 сравнения, вход 25 начала записи ранга блока 7 управления, вход 26 окончания контроля блока 7 управления, вход 27 конца поиска ранга блока 7 управления, вход 28 конца цикла блока 7 управления.

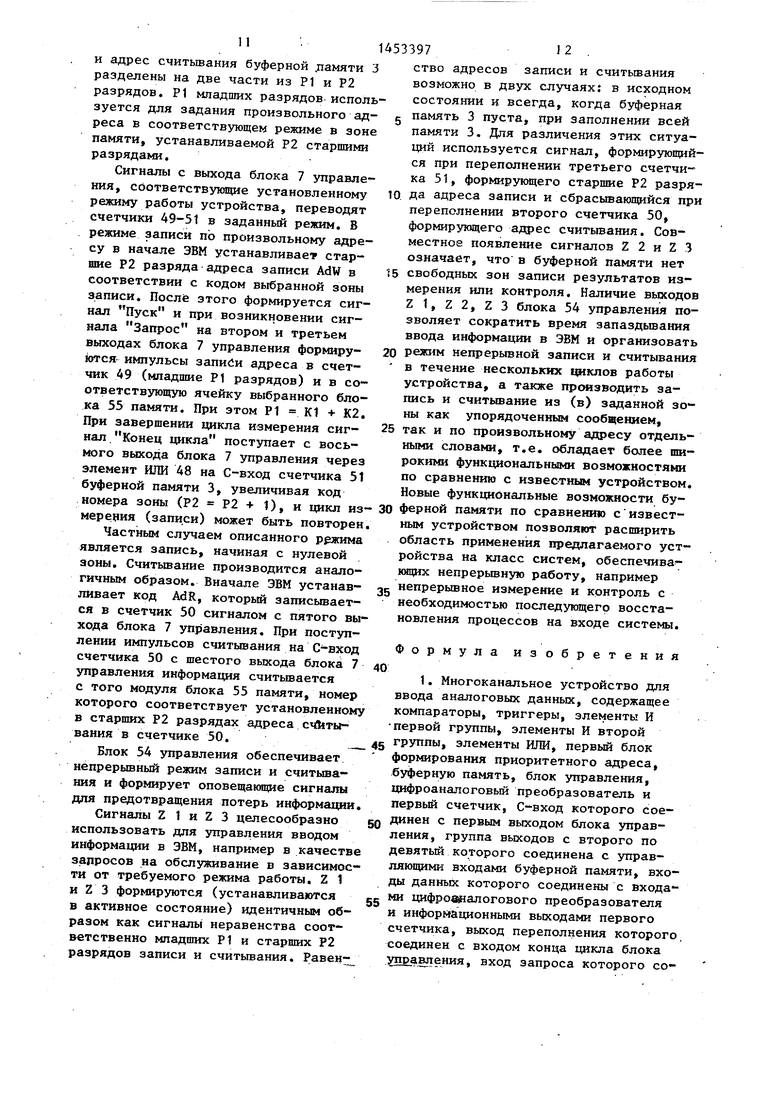

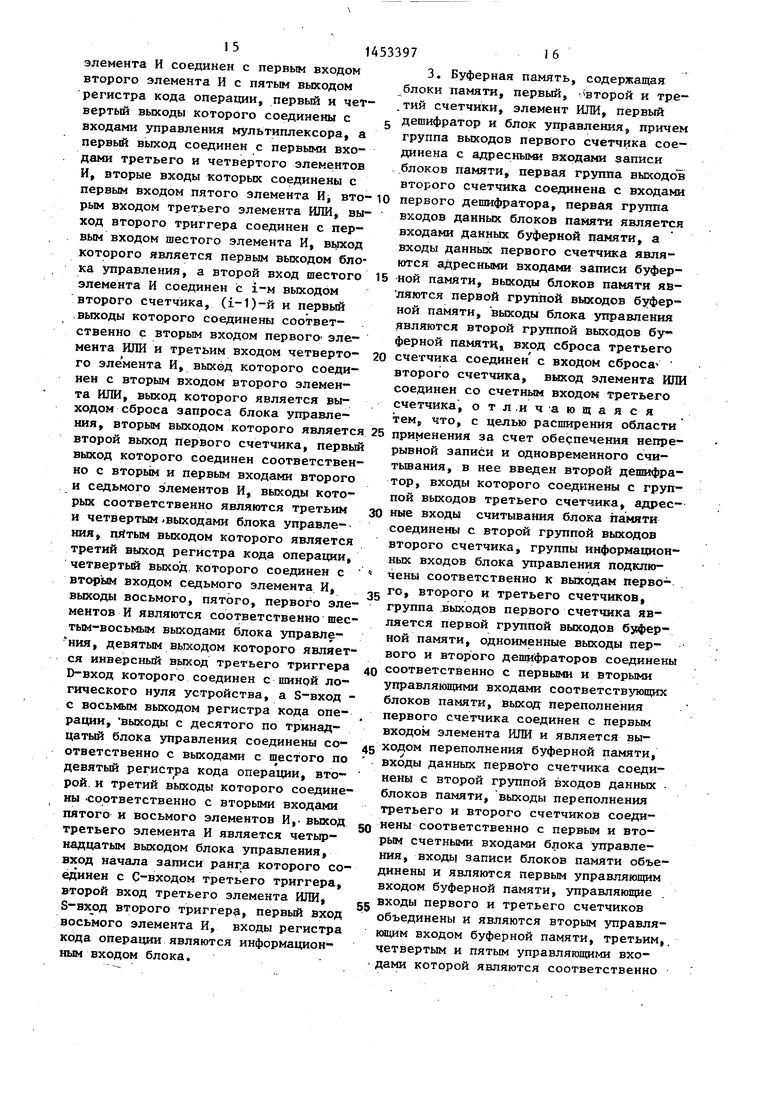

На схеме блока управления (фиг,2) обозначены генератор 29 импульсов, три триггера 30-32, два счетчика 33 и , восемь элементов И 35-42, три элемента ИЛИ 43-45, регистр 46 кода операции, мультиплексор 47,

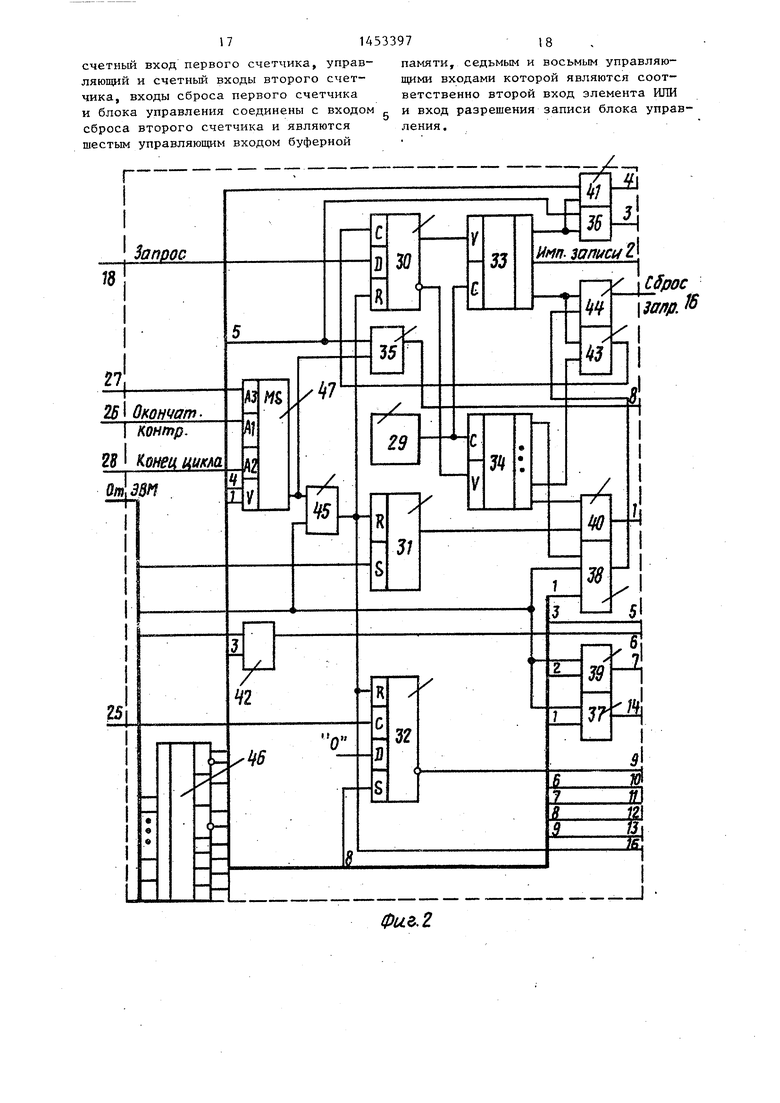

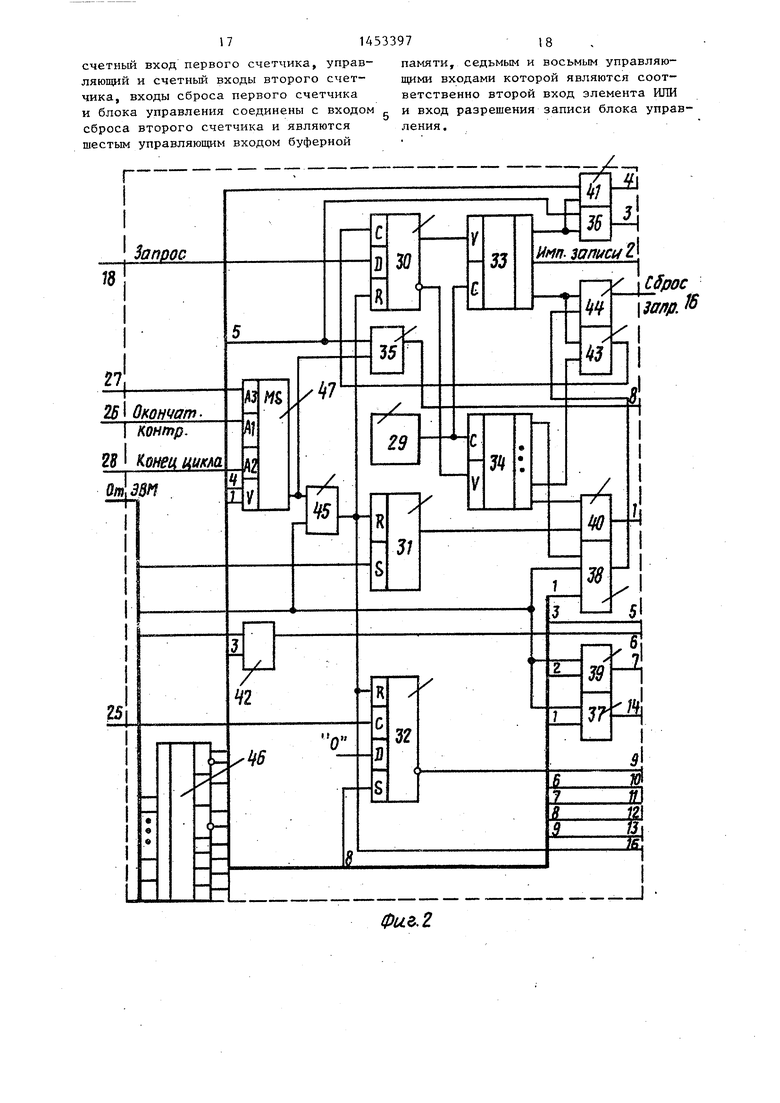

На схеме буферной памяти (фиг.З) обозначены элемент ИЛИ 48, три счетчика 49-51, два дешифратора 52 и 53, блок 54 управления, блоки 55 памяти,

Модуль (группа из m каналов) обеспечивает сравнение уровней образцового уравновешивающего напряжения и напряжения на входах устройства независимо по каждому каналу, фиксацию момента совпадения уровней и формирование сигнала Запрос при срабатывании компаратора хотя бы в одном из каналов,

Блок 2 обеспечивает формирование кодов номеров модулей либо сформировавших запросы в соответствии с приоритетом, либо в соответствии с кодом, установленным на шине данных и сброс триггеров сработавших каналов, причем на первой группе выходов формируется позиционный двоичный код, на второй группе выходов - унитарный двоичный код, а на третьем выходе - сигнал наличия запроса хотя бы от одного модуля. Блок 2 представляет собой после

1

довательно соединенные приоритетный шифратор и дешифратор, выходы которы являются соответственно первой и второй группой выходов блока 2. Вьрсоды дешифратора соединены также с соответствующими первыми входами двухвхо довых схем ИГШ, вторые входы которых объединены и являются R-входом сброса блока 2. Все линии шины данных D подключены к соответствующим выходам приоритетного шифратора по схеме МОНТАЖНОГО ИЛИ. Вход приоритетного шифратора является управляющим входом блока 2,

Буферная память 3 обеспечивает согласование времени преобразования N аналоговых сигналов в коды и времени ввода данных в ЭВМ с целью максимального использования быстродействия подсистем сбора и обработки данных. Буферная память 3 позволяет осуществлять запись по произвольно заданному адресу или в последовательно расположенные ячейки памяти, а считывание производить как законченным и упорядоченным сообщением последовательно по одной ячейке, начиная с ячейки с заданным начальным адресом, так и по одному слову с произвольного адреса, причем запись и считывание могут производиться как в одно и то же, так и в разное время. По логике работы считывание и запись всегда производятся по несовпадающим адресам.

Блок 54 управления представляет собой два устройства сравнения кодов двухвходовьй элемент ИЛИ, выход кото рого соединен с счетньм входом счетного триггера, R-вход которого является R-входом блока 54 управления, V-вход которого соединен с первым выходом элемента ИЛИ, второй вход которого соединен с выходом первого устройства сравнения, причем с первыми и вторыми входами первого устройства сравнения соединены младшие Р1 разрядов соответственно первого и третьего счетчиков, а с первыми и вторыми входами устройства сравнения со единены старшие Р2 разрядов соответственно второго и третьего счетчиков. Выходы элемента ИЛИ и второго устройства сравнения являются соответственно выходами Z1 и Z2 блока управления, выход Z3 которого является выходом счетного триггера.

Блок 4 обеспечивает формирование кодов номеров каналов в модулях, сформировавших запросы в соответствии с приоритетом, причем на первой группе выходов формируется позиционный двоичный код, на второй группе выходов - унитарный двоичный код, а также сброс триггеров сработавших каналов. Блок 4 реализуется аналогично блоку 2.

Счетчик 5 может быть выполнен на микросхемах К155ТМ7.

Блок 6 сравнения может быть реа- лизован, например, на микросхемах K555CII1.

30

20

25

Блок 7 управления обеспечивает управление и синхронизацию работы всей системы, а также прием команд управления извне, например от ЭВМ.

Устройство может работать в двух режимах: режиме измерения и режиме контроля.

Работа устройства для ввода аналоговых данных и буферная память в режиме измерения осуществляются под управлением ЭВМ, которая формирует управляющее слово соответствующего режима для записи в регистр 46 кода операции, а также команды Пуск, Сброс, Сброс буферной памяти и Импульсы считывания, поступающие на вход 17 блока 7 управления и на входы данных блоков 2 и 4 и счетчи- 5 ков 5 и 8. В исходном состоянии при включении питания или начале работы

0

счетчик 8, все триггеры 11 всех мо- дулей 1, триггеры 30-32, счетчики 33 и 34 блока 7 управления, счетчики 40- 51, буферной памяти 3 установлены в исходное (нулевое) состояние и на выходах 19 буферной памяти 3 сформированы Z1 О, Z2 О и Z3 1, что соответствует разрешению записи и запрещению считывания из буферной памяти 3 из-за отсутствия данных в последней. При поступлении сигнала Пуск в блок 7 управления на его первом выходе формируются импульсы с

частотой f,j , поступающие на

счетчик 8, выходы которого подключены к входам преобразователя 9. При 55 атом на выходе преобразователя 9 формируется ступенчато изменяющееся образцовое напряжение. В момент совпадения уровня образцового напряжения и напряжения на одном или нескольких

входах устройства X,-: , где i 1 ,ni, j на выходе, соответствующем этому входу (входам), компаратора 10 формируется перепад напряжения (ца- пример, из состояния О в 1), по которому соответствующий триггер 11 переходит в единичное состояние. Уровень логической единицы с выхода триггера 11 в j-rpynne через элемент ИЛИ 14 в качестве запроса qj от j-й группы каналов поступает- на вход блока 2. Блок 2 по одному или нескольким запросам с. формирует на

своих двух группах выходов соответственно унитарный и позиционные коды наиболее приоритетного из сформиро- вавпшх запрос модулей 1, а на выходе - сигнал Запрос - Q, поступаю- щий на выход 18 блока 7 управления. Унитарный код с второй группы выходов блока 2 разрешает подключение к входам блока 4 сигналов наиболее приоритетного из выставивших запросы модулей, так как логическая 1 в одном из разрядов унитарного кода разрешает прохождение сигналов с выхода сработавшего триггера 11 на вход блока 4. В это время на выходах всех остальных элементов И 12 модулей 1 - высокий уровень, что обеспечивает реализацию МОНТАЖНОГО.ИЛИ. Блок 4 фор- мирует .на двух группа,х выходов позиционный и унитарный коды номера наиболее приоритетного канала в обслу- яоиваемом модуле. Выходы унитарного кода поступают на вторые входы сброса триггеров 11, разрешая прохождение сигнала Сброс на триггер 11 наиболее приоритетного из сработйвщих каналов. Объединенные первые группы выходов блока 2 и блoka 4 образуют адрес записи буферной памяти 3. Запись в буферную память 3 осуществляется блоком 7 управления при возникновении сигнала Запрос и в соответствии с установленным режимом работы устройства. По окончании записи блок 7 управления формирует на своем выходе 16 импульс Сброс залроса, который установит в нулевое состояние триггер, наиболее приоритетный из сработавших триггеров 11. Если сигнал Запрос сформирован несколькими каналами в одном модуле 1 или несколькими модулями, то процедура записи повторяется, в противном случае блок 2 снимает Запрос и блок 7 управления разрешает формирование сту-,

14533976

пенчато изменяющегося образцового напряжения до появления очередного сигнала Запрос.

Рассмотрим брлее подробно работу блока 7 управления.

Регистр 46 кода операции блока 7 управления предназначен для хранения кода режима работы системы. При этом 10 принято следующее кодирование;

1разряд - режим работы устройства: О - измерение, 1 - контроль.

2разряд - режим считывания: О - считывание по произвольному адресу,

15 1 считывание массивом.

3разряд - режим записи О - -

20

25

разряде соот- меньше.

30

35

пись по произвольному адресу,

запись с последовател Ьной адресацией.

4 и 5 разряды - режим контроля: 1 - в 4 разряде соответствует режиму больше, 1 - в 5 ветствует режиму

6разряд - режим измерения по заданному адресу: О - измерение по произвольному адресу, 1 - измерение по заданному адресу.

7разряд - реверс счетчика 8: О - соответствует +1, 1 - соответствует -1 .

8блоке управления генератор 29 формирует тактовые импульсы с часто- той f , которые обеспечивают реализацию принципа синхронного управления всеми блоками устройства, поступают на оба счетчика 33 и 34, Счетчики 33 и 34 используются в качестве делителей частоты и распределителей импульсов, причем счет чик 34 используется для упра вления счетчи40 ком 8 преобр;азователя 9, а счетчик

33- для управления записью данных в буферную память. Время установления напряжения на выходе преобразователя 9 (tVi) заданной погрешностьй существенно больше времени записи в буферную память 3 и поэтому коэффициент деления счетчика 34 больше, чем счетчика 33. Таким образом, за время 2 иэм можно Произвести несколько записей в буферную память 3. Импульсы с (i-l)-ro выхода счетчика 34 через элемент ШШ 43 поступают на С-вход триггера 30 и в случае наличия запроса q переводят последний в единичное состояние. В этом состоянии триггер 30 запрещает работу счетчика

34(формирование очередного импульса для счетчика 8), т.е. приостанавливает развертку на время записи в бу45

50

55

1 -

0

5

разряде соот- меньше.

0

5

пись по произвольному адресу,

запись с последовател Ьной адресацией.

4 и 5 разряды - режим контроля: 1 - в 4 разряде соответствует режиму больше, 1 - в 5 ветствует режиму

6разряд - режим измерения по заданному адресу: О - измерение по произвольному адресу, 1 - измерение по заданному адресу.

7разряд - реверс счетчика 8: О - соответствует +1, 1 - соответствует -1 .

8блоке управления генератор 29 формирует тактовые импульсы с часто- той f , которые обеспечивают реализацию принципа синхронного управления всеми блоками устройства, поступают на оба счетчика 33 и 34, Счетчики 33 и 34 используются в качестве делителей частоты и распределителей импульсов, причем счет чик 34 используется для упра вления счетчи0 ком 8 преобр;азователя 9, а счетчик

33- для управления записью данных в буферную память. Время установления напряжения на выходе преобразователя 9 (tVi) заданной погрешностьй существенно больше времени записи в буферную память 3 и поэтому коэффициент деления счетчика 34 больше, чем счетчика 33. Таким образом, за время 2 иэм можно Произвести несколько записей в буферную память 3. Импульсы с (i-l)-ro выхода счетчика 34 через элемент ШШ 43 поступают на С-вход триггера 30 и в случае наличия запроса q переводят последний в единичное состояние. В этом состоянии триггер 30 запрещает работу счетчика

34(формирование очередного импульса для счетчика 8), т.е. приостанавливает развертку на время записи в бу5

0

5

ферную память 3 и разрешает работу счетчика 33. По импульсам с первых двух выходов счетчика 33 (второй, третий и четвертый выходы блока 7 управления) в буферную память 3 осуществляется запись данных в соответствии с выбранным режимом записи буферной памяти 3: запись по произвольному адресу (по номеру сработавшего канала), запись с последовательной адресацией (запись ранжированных по уровню сигнала номеров каналов). Передний ФРОНТ импульса с третьего выхода счетчика 33 (выход 16 блока 7 управления) через элемент ИЛИ 44 устанавливает триггер 11 обслуженного модуля 1 в нулевое состояние. Задний фронт импульса с третьего выхода счетчика 33 через элемент ИЛИ 43 установит триггер 30 в состояние, соот ветствунщее уровню сигнала Запрос на входе 18 блока 7 управления. При этом процедура записи повторяется до тех пор, пока блок 2 не снимет сигнал Запрос. В этом случае на D-BXO- де триггера 30 блока 7 управления сформируется уровень логического нуля и триггер 30 перейдет в нулевое состояние, при этом возобновится формирование образцового напряжения до появления очередного запроса. По достижению ступенчато изменяющимся образцовым напряжением граниш 1 диапазона счетчик 8 формирует импульс Пере- полнение, который поступает на вход 28 блока 7 управления. Этот импульс через мультиплексор 47 и элемент ИЛИ 45 блока 7 управления поступает на R-вход триггеров 30-32, устанавливая их в нулевое состояние. При этом запрещается формирование импульсов для счетчика 8 (элемент И 40) и оповещается буферная память 3 об окончании записи информации об N аналоговых сигналах.

-

После каждого цикла преобразования N аналоговых сигналов (цикла измере- ния) счетчик 8 и все триггеры 11 автоматически устанавливаются в исход- ное состояние.

Рассмотрим работу устройства в ре- жнме контроля.

В этом случае в регистр 46 кода операции (КОП) из ЭВМ записывается соответствующее управляющее слово, i Режим контроля имеет два подрежима; режим измерения в заданных границах i и собственно режим контроля. Режим

10

3540

30

0

5

измерения в заданных границах осуществляется следующим образом. Управляющее слово, передаваемое ЭВМ в ре- 1 истр 46, в этом случае 1111000. При этом в счетчик 8 записьтается код Ш1жней уставки. Затем управляющее слово меняется на 1110100 и в счетчик 5 записьшается код верхней уставки. Далее ЭВМ формирует сигнал Пуск и устройство функционирует аналогично режиму Измерение при записи в память 55 ранжированного ряда с noc-t ледозател : ной адресацией. При этом в tg счетчике 49 буферной памяти 3 накапливается число записываемых в память слов. Сигнал окончания контроля в этом случае формирует блок 6 сравнения в момент равенства верхней устав- 20 ки и кода ступенчато изменяющегося напряжения. Возможны следуйяцие модификации режима. Измерение упорядоченного по номерам каналов ряда значений (управлякяцее слово в этом случае 25 1101000). Измерение упорядоченного по значениям ряда от максимального к минимальному (управлякицее слово 1111001). Режим, ближайший к заданному сверху. Измерение начинается с заданного значения (нижняя уставка) до первог о сработавшего канала (уп- равляюй ее слово 1100100), Режим, ближайший к заданному снизу. Измерение начинается с заданного значения (верхняя уставка) до первого сработавшего, канала при изменении ступенчато изменяющегося образцового напряжения в сторону уменьшения (управляющее слово 1101001).

В режиме собственно контроля границы могут быть заданы верхним и нижним номерами значений в ранжированном ряду (ранговыми статистиками). В этом случае осуществляется преобразование только тех величин, значение которых , лежит между заданными ранговыми статистиками. Реализация данного режима на аппаратном фовне существенно упрощает статистическую обработку сигналов. Запись нижней уставки в дополнительном, коде в счетчик 49 буферной памяти 3 осуществляется по управляю- . щему слову 1110010. Затем записывается верхняя уставка в дополнительном коде в счетчик 5 управляющим словом 1111000. Работа устройства далее осуществляется так же, как и в режиме измерения при записи с последовательной адресацией. До переполнения счет45

9145339710

чика 49 (начало записи ранга) триггер 32 блока 7 управления блокирует сигнал Z1 буферной-памяти 3, что соответствует сигналу отсутствия информации в данной зоне буферной па- мяти. После переполнения счетчика 49 в буферную память 3 начинают записываться значения с номерами больше заданного в ранжированном ряду. Сигнал 10 ваются и их номера записьгоаются в Конец поиска ранга 27 (выход пере- память 55. Таким образом, режим кон- лолнения счетчика 5) действует аналогично сигналу Конец цикла. К этому моменту в буферную память записан отрезок ранжир ованного ряда между двумя заданными ранговыми статистиками. Модификациями данного режима являются следующие.

управляющее слово 111 1110100 и в счетчик 8 записывается код верхней уставки. Между этими моментами време- g ни триггеры 11 каналов, в которых измеряемые сигналы меньше нижней уставки, устанавливаются в ноль. Каналы, сработавшие при образцовом напряжении, равном верхней уставке, опрашитроля Зона осуществляется в два такта. Модификациями данного режима являются; режим Меньше заданного, 15 реализуется в режиме Зона при равенстве О нижней уставки, режим Больше заданного, реализуется в ре жиме Зона при равенстве верхней

Измерение наперед заданной ранговой статистики (поиск ранга). В зтом случае верхняя граница устанавливается равной заданному рангу RN, а нижняя граница - равной (RN - 1). Управляющее слово в этом случае не меN

няется. При RN - осуществляется измерение медианы.

При RN N реализуется режим поиска максимального значения.

При RN . 1 осуществляется режим поиска минимального значения.

уставки границе диапазона.

20 Число измеряемьк величин, записан ных в блоки 55 памяти передается в ЭВМ из счетчика 49 буферной памяти 3 Буферная память 3 работает под уп равлением управляющих сигналов и обе

25 спечивает различные режимы функционирования: режим записи по произволь ному адресу, режим записи с последовательной адресацией в предварительно установленную зону адресного про30 странства, режим считьшания по произ вольному адресу, режим считьшания массивом с предварительно установлен ной. зоной адресного пространства. Кроме того, в режиме записи с после30 странства, режим считьшания по произвольному адресу, режим считьшания массивом с предварительно установлен-, ной. зоной адресного пространства. Кроме того, в режиме записи с послеВ случае, если управляющее слово равно 1110010 и сохраняется неизменным в течение цикла измерения, реали- 35 довательной адресацией обеспечивает- зуется режим измерения по заданному ся подсчет числа импульсов записи и

возможность считьгоания его внешним устройством (ЭВМ) с выходов 20 буферной памяти З..ВО всех режимах ра- 40 боты буферной памяти 3 обеспечивается формирование извещакяцпс сигналов на выходе- 19, Z 1 - разрешение считывания словом, Z 2 - разрешение записи, Z 3 - разрешение считьшания массивом, 45 которые могут быть использованы ЭВМ при управлении устройством.

Буферная 3 состоит из модулей двухпортовых блоков 55 памяти, находящихся в режиме считывания по адресным входам считывания при наличии сигнала разрешения на первом управляющем входе. При изменении адреса считывания Ad R изменяется информация на выходе блоков 55 памяти.

1110100. При этом на выходе преобра- 55 Запись данных (вход данных) осущест- зователя 9 формируется образцрвое вляется по адресу записи AdW при наличии импульсов записи и сигнала разрешения записи на втором управляющем входе блоков 55 памяти. Адрес записи

адресу. При этом блоки 2 и. 4 работают в качестве дешифраторов выбора заданного канала. Длительность цикла в режимах измерения в заданных границах с последователь ной адресацией блоков 55 памяти в общем случае меньше цикла измерения с записью по произвольному адресу, так как нет необходимос-г ти в доведении образцового напряжет ния до гранищл диапазона измерения. Режимы контроля характеризуются тем, что контролируемые входные сигналы не преобразуются в код, так как в этих случаях требуется информация только о номерах каналов. Рассмотрим работу устройства 8 режиме Зона. ЭВМ вместе с кодом нижней уставки задает устройству управляющее слово

50

напряжение, равное нижней уставке. По сигналу Отсутствие запроса с выхода 19 блока 2 ЭВМ устанавливает

ваются и их номера записьгоаются в память 55. Таким образом, режим кон-

управляющее слово 111 1110100 и в счетчик 8 записывается код верхней уставки. Между этими моментами време- ни триггеры 11 каналов, в которых измеряемые сигналы меньше нижней устав- ки, устанавливаются в ноль. Каналы, сработавшие при образцовом напряжении, равном верхней уставке, опрашиваются и их номера записьгоаются в память 55. Таким образом, режим кон-

троля Зона осуществляется в два такта. Модификациями данного режима являются; режим Меньше заданного, реализуется в режиме Зона при равенстве О нижней уставки, режим Больше заданного, реализуется в режиме Зона при равенстве верхней

ставки границе диапазона.

Число измеряемьк величин, записанных в блоки 55 памяти передается в ЭВМ из счетчика 49 буферной памяти 3. Буферная память 3 работает под управлением управляющих сигналов и обеспечивает различные режимы функционирования: режим записи по произвольному адресу, режим записи с последовательной адресацией в предварительно установленную зону адресного пространства, режим считьшания по произвольному адресу, режим считьшания массивом с предварительно установлен-, ной. зоной адресного пространства. Кроме того, в режиме записи с последовательной адресацией обеспечивает- ся подсчет числа импульсов записи и

. 145339712

разд е„ь нГдвГ: ° ™- « считьшания Р 2Г 2 возможно в двух случаях: в исходном зуегся дАя состоянии и всегда, когда буферная

реса в cooTBe cT«L 5 ь 3 пуста, при заполнении всей

памяти, уста:авл в :::/рТс: Различения этих ситуа- разрядами старшими ции используется сигнал, формирующийСигналы с nuvona « -, переполнении третьего счетчиГе: ™ « .:.- счетчики 49-51 «Р аОДят переполнении второго счетчика 50,

гг, :. „ггг„записи, поел. 3.Z ф„; р еТ/Г- ГГТг г « - Яz/iiL ;-.-- Т Г - - еИ;„.г:. г™г г , и:1Г:: -- - -«::.- S ™ т----.

ка 55 пам и этоГрГ- К1 /S « нтьшание из (в) заданной . .-:

элемент S 48 на Г ™« Функциональными возможностями буферной 3 вГ °° сравнению с известным устройством, номера ГПГГГ , Новые функциональные возможности - ггу:.

° пpeдлaгLг ::Г;c ™:г г Еп :пр:рГ т:. .

хода блока 7 - -°« -лении импульсов считывания на С-входФормула ис,,«

счетчика 50 с шестого выхода блока / ° Р « У изобретения

управления информация считьшартгяi м

с того модуля блокГ55 М ° °«анапьное устройство для

г:-лтр .----- - -- .

вания в счетчике зГ группы, элементы И второй

Кттп. сл , -45 группы, злементы ИЛИ, первый блок

непоеп обеспечивает формирования приоритетного адреса, непрерывный режим записи и считыва- буферную память, блок управления НИН и формирует оповещающие сигналы Дифроаналоговьй преобразоват и Сиг±ь ГГ 7 первый счетчик. С-вход которого сое- Hcnonl Ll целесообразно gO ««« первым выходом блока управ т 1 .гг;-„ гг - .т..1, .™::

L L-r-S,-а- ГиГ.

13

единен с выходом запроса первого блока формирования приоритетного адреса, выходы позиционного кода которого соединены с соответствующими адресными входами записи буферной памяти, выходы первой и второй групп которой являются информационными выходами устройства, выходы унитарного кода первого блока формирования приоритетного адреса соединены с первыми входами соответствующих элементов И первой и второй групп, вторые входы элементов И второй группы соединены .с выходом сброса блока управления, информационный вход которого является управляющим входом устройства, информационными входами которого являются одни входы компараторов, другие вхо

с первыми и вторыми входами блока сравнения, выход которого соединен с входом окончания контроля блока уп- 5 равления, вход конца поиска ранга которого соединен с выходом переполне- ния второго счетчика, С-вход которого соединен с четвертым выходом блока управления, вход начала записи ранга 10 которого соединен с выходом переполнения буферной памяти, выходы соответствующих элементов И первой группы объединены и соединены с соответствующими информационными входами второго 15 блока формирования приоритетного адреса, выходы позиционного кода которого соединены с соответствующими адресными входами записи буферной памяти, вторые входы сброса соответды которых соединены с выходом цифро- 20 ствующих триггеров объединены и поданалогового преобразователя, выход каждого компаратора соединен с С-вхо- дом соответствующего триггера, выходы которых соединены .с вторыми входаключены к выходам унитарного кода второго блока формирования приоритетного адреса, входы адреса считывания буферной памяти, входы данньрс

ми соответствующих элементов И первой 25 первого и второго счетчиков, а также

группы и входами соответствующих элементов ШШ, выход каждого элемента ИЛИ соединен с соответствующим входом первого блока формирования приоритетного адреса, D-входы всех триггеров соединены с шиной логической единицы устройства, первые входы сброса соответствующих триггеров соединены с выходом соответствующего элемента И второй группы, отличающееся тем, что, с целью расширения функциональных возможностей, в устройство дополнительно введены второй блок фop sиpoвaния приоритетного адреса, блок сравнения и второй счетчик, R-входы первого и второго блоков формирования приоритетного адреса соединены с четырнадцатым выходом блока управления, десятый выход блока управления соединен с управляющим входом второго счетчика, одиннадцатый выход блока управления соединен с управляющим входом первого счетчика, двенадцатый выход блока управления соединен с управляющими входами первого и второго блоков формирования приоритетного адреса, тринадцатый выход блока управления соединен с входом управления изменением направления счета первого счетчика, пятнадцатый выход блока управления соединен с входом сброса первого счетчикаj информационные выходы первого и второго счетянков соединены соотве-гственно

30

35

40

входы данных первого и второго блоко формирования приоритетного адреса являются управляющимивходами устройства, выход запроса первого блока формирования приоритетного адреса яв ляется выходом запроса устройства. .

2. Устройство ПОП.1, отлича ющееся тем, что блок управления содержит генератор импульсов, три триггера, два счетчика, восемь элементов И, три элемента ИЛИ, регистр кода операции и мультиплексор, D-вход первого триггера является вхо дом запроса блока управления, С-вход соединен с выходом первого элемента ИЛИ, первый вход которого соединен с первым входом второго элемента ИЛИ и третьим выходом.первого счетчика, управляющий вход котораго соединен с прямым выходом первого триггера, инверсный выход которого соединен с управлякяцим входом второго счетчика, С-вход которого соединен с С-входом первого счетчика и выходом генерато- ра, первый, второй и третий входы мультиплексора соединены с входами окончания контроля, конца цикла, поиска ранга блока управления, выход мультиплексора соединен с первым вхо де дом первого элемента И и с первым входом третьего элемента ИЛИ, выход которого соединен с R-входами тригге ров и является пятнадцатым выходом блока управления, второй вход первог

45

50

1453397

14

с первыми и вторыми входами блока сравнения, выход которого соединен с входом окончания контроля блока уп- равления, вход конца поиска ранга которого соединен с выходом переполне- ния второго счетчика, С-вход которого соединен с четвертым выходом блока управления, вход начала записи ранга которого соединен с выходом переполнения буферной памяти, выходы соответствующих элементов И первой группы объединены и соединены с соответствующими информационными входами второго блока формирования приоритетного адреса, выходы позиционного кода которого соединены с соответствующими адресными входами записи буферной памяти, вторые входы сброса соответствующих триггеров объединены и подключены к выходам унитарного кода второго блока формирования приоритетного адреса, входы адреса считывания буферной памяти, входы данньрс

5 первого и второго счетчиков, а также

0

5

0

входы данных первого и второго блоков формирования приоритетного адреса являются управляющимивходами устройства, выход запроса первого блока формирования приоритетного адреса является выходом запроса устройства. .

2. Устройство ПОП.1, отличающееся тем, что блок управления содержит генератор импульсов, три триггера, два счетчика, восемь элементов И, три элемента ИЛИ, регистр кода операции и мультиплексор, D-вход первого триггера является входом запроса блока управления, С-вход соединен с выходом первого элемента ИЛИ, первый вход которого соединен с первым входом второго элемента ИЛИ и третьим выходом.первого счетчика, управляющий вход котораго соединен с прямым выходом первого триггера, инверсный выход которого соединен с управлякяцим входом второго счетчика, С-вход которого соединен с С-входом первого счетчика и выходом генерато- ра, первый, второй и третий входы мультиплексора соединены с входами окончания контроля, конца цикла, поиска ранга блока управления, выход мультиплексора соединен с первым входе дом первого элемента И и с первым входом третьего элемента ИЛИ, выход которого соединен с R-входами триггеров и является пятнадцатым выходом блока управления, второй вход первого

5

0

5 145339716

элемента И соединен с первым входомз RvA.n

второго элемента И с пятым выходомй„ Г Буферная память, содержащая

регистра кода операции, первьГПет- ° ™ °Р°« « Р вертьй выходы которого с „Р « «ики, элемент ИЛИ. первьй

входами управления мультип екс а а « блок управления, причем

первьй вьпсод соединен с первь, вхо- Г дами третьего и четвертого элементовJ адресныьш входами записи

И. вторые входы которое ™

первым входом пятого элемента И вто-ш четчика соединена с входами

рь« входом третьего элемента ИИ Дешифратора, перв грушха

ход второго триггера соединен с пеп- ° ° является

вьш входом шестого элемента S в л ° буферной памяти, а

КОТОРОГО является первьж вьосо оЛл -ScTaSp c T° ° - ка управления, а второй вход шестого1-5 й входами записи буфер- элемента И соединен fc i-м вьпсопомпамяти, выходы блоков памяти яв- второго счетчика. (1-1)-й и первГгй .выходы которого соединены соответ- ° памяти, выходы блока управления

ственно с вторь., входом первого эле- ° ° °

мента ИЛИ и третьим входом четверто-,п третьего

го элемента И. выход которого соеди- Г иен с вторым входом второго элемен- ° ° счетчика, выход элемента ШШ

та ИЛИ. вьпсод которого является ° °«° ходом сброса запроса блока управле- счехчика. отл.и чающаяся ния. вторым выходом которого является 9с расширения области второй вьпсод первого счетчика перв2 а счет обеспечения непре- выход КОТОРОГО соединен соотв;тстве ° одновременного счи- но с вторым и первым входами ВТОРОГО « «ее введен второй дешифра- . и седьмого элементов И, выходы кото- - ° соединены с груп- рых соответственно являются третьим ° «ьосодов третьего счетчика, адрес- и четвертым .выходами блока упоавле- - считывания блока памяти ния. пйтьп. вьосодом которого в яется выходов третий выход регистра кода операции Г счетчика, группы информацион- четвертьй вьпсод которого соеди еГс - . Управления подклю- вторым входом седьмого элемента Sсоответственно к выходам первовыходы восьмого, пятого, первого эле- « третьего счетчиков, ментов И являются соответственно шее- ™ первого счетчика яв- тьш-восьмым вьпсодами блока ГГ ° °«° ния. девять-м вьпсодом которого являет- ого ПГ ««Д перся инверсный выход третьего ТВИГГРПЯвторого дешифраторов соединены D-вход которого соединен с шиной ло- ° с первыми и вторыми гического нуля устройства а S-вхол - Управляющими входами соответствующих с восьмью вькодом регистра кода one- ° переполнения рации, -выходы с десятого по тринал- счетчика соединен с первым Цатый блока управления соеди ены о- хоГ° является вы- ответственно с выходами с шестого по переполнения буферной памяти, девятьй регистра кода опера ции. вто- °« nepBoi-o счетчика соедирой. и третий вькоды которогГсое ине- «Z ° °«° ны .соответственно с вторыми входамипамяти, выходы переполнения

пятого и восьмого элементов И.- выход второго счетчиков соеди- третьего элемента И является четып- соответственно с первым и вто- надцатым выходом блока управления входами блока управле- вход начала записи ранг,а которого со- записи блоков памяти объе- единен с С-входом третьего триггеоа и являются первым управляющим второй вход третьего элемента ИЛИ буферной памяти, управляющие . S-вход второго триггера, первый °« первого и третьего счетчиков восьмого элемента И. регистра , и являются вторым управлякода операции являются ™ третьим,. ным входом блока.четвертым и пятым управляющими вхо Дами которой являются соответственно

счетный вход первого счетчика, управляющий и счетный входы второго счетчика, входы сброса первого счетчика и блока управления соединены с входом сброса второго счетчика и являются шестым управляющим входом буферной

памяти, седьмым и восьмым управляющими входами которой являются соответственно второй вход элемента ИЛИ и вход разрешения записи блока управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для ввода аналоговых данных и буферная память | 1984 |

|

SU1238054A1 |

| Устройство ранжирования чисел | 1987 |

|

SU1425653A1 |

| Микропрограммное устройство управления | 1988 |

|

SU1649540A1 |

| Устройство для сопряжения управляющей вычислительной машины с периферийными устройствами | 1983 |

|

SU1201841A1 |

| Многоканальное устройство для ввода аналоговых данных | 1985 |

|

SU1273911A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Устройство для преобразования малокадрового телевизионного стандарта | 1985 |

|

SU1256245A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1278867A2 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1280642A2 |

| Микропрограммный процессор | 1981 |

|

SU1037262A1 |

Изобретение относится к измерительной и вычислительной технике, а именно к устройствам запоминания, и может быть использовано как при построении высокопроизводительных систем сбора и обработки аналоговых дан

--I

Ui

.I

Фиг. 2

f;

Фиг.З

| Многоканальная система ввода аналоговой информации | 1973 |

|

SU450157A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Многоканальное устройство для ввода аналоговых данных и буферная память | 1984 |

|

SU1238054A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-01-23—Публикация

1987-06-23—Подача