Настоящее изобретение относится к области радиотехники и связи, и может быть использовано для построения схемных и конструктивных решений по формирователям сигналов, твердотельным усилителям мощности и антенно-фидерным системам КВ-диапазона.

В области передачи и обработки информации основную роль играют цифровые технологии. В радиосвязи наиболее заметное распространение цифровые технологии стали получать при использовании персональных компьютеров для модуляции и демодуляции радиосигналов. Таким образом, практически весь объем работ по обработке сигнала перекладывался на программное обеспечение, что и определило термин Software Defined Radio (SDR). Цель такого подхода - создать систему, которая может принимать и передавать практически любые радиосигналы с помощью программного обеспечения, которое априори является гибким и адаптивным. В настоящее время SDR технологии широко применяются в радио- и сотовой связи, где в режиме реального времени требуется поддержка разнообразных изменяющихся радиопротоколов.

Известны различные способы формирования и обработки сигналов. Например, патенты РФ №№2527943, 2305295, 2432580, 2001107088, 2110809, US 6469657 В1, 22.10.2002. US 6148195 А, 10.05.1998. WO 2005045459 A3, 07.07.2005. US 6903685 В1, 07.06.2005.

Известно устройство оптимальной обработки последовательностей сигналов с модуляцией несущей частоты. Патент РФ №2237908 10.10.2004 г. (Прототип). Устройство оптимальной обработки последовательностей широкополосных сигналов с модуляцией несущей частоты содержит параллельные каналы, каждый из которых включает полосовой фильтр, квадратурный фазовый детектор, фазовращатель на 90 градусов, линию задержки, аналого-цифровой преобразователь, буферное запоминающее устройство, фильтровой блок селекции движущихся целей, N блоков задержки, N коммутаторов, выходные каналы, каждый из которых содержит фильтр сжатия, блок определения модуля, пороговый блок.

Однако ни аналоги, ни прототип не обеспечивают улучшения приема информации в условиях замирания сигнала, вследствие его распространения по радиоканалу, а также компенсации помех и адаптации их по частоте.

Целью изобретения является улучшение приема информации в условиях замирания сигнала, вследствие его распространения по радиоканалу, а также компенсации помех и адаптации их по частоте.

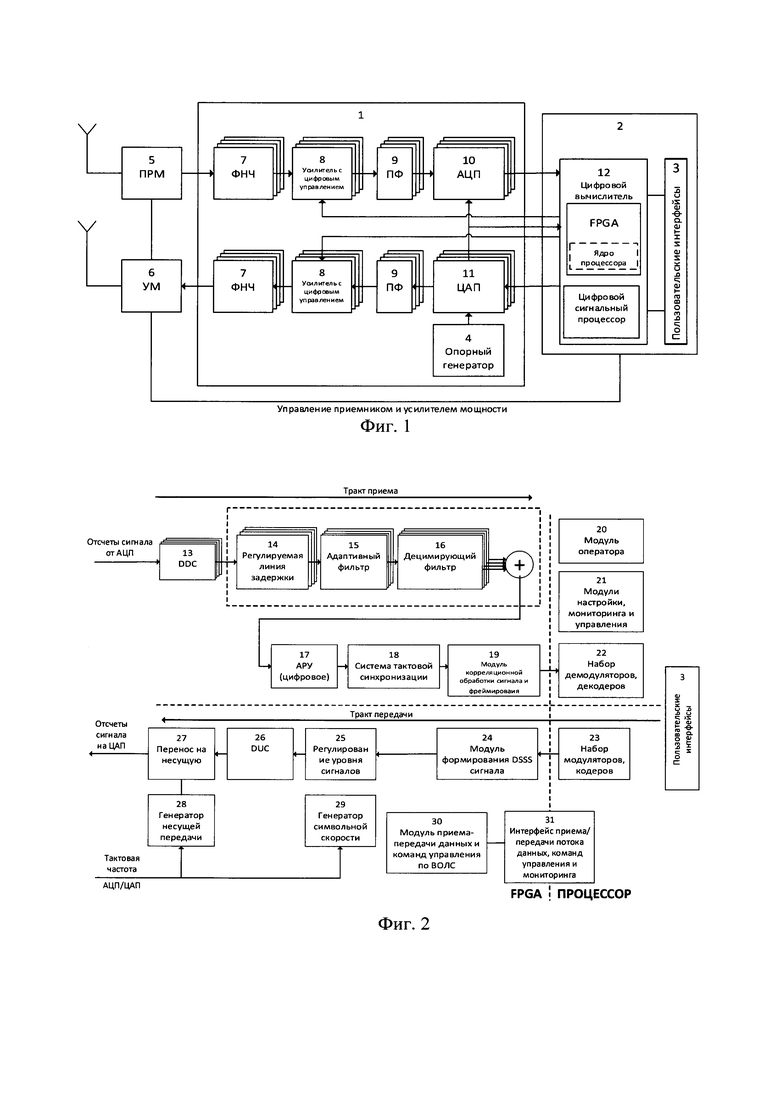

Поставленная цель заключается в том, что система формирования и обработки сигналов, выполнена в виде двух модулей, при этом первый модуль преобразования частоты представляет собой четырех канальный аналого-цифровой преобразователь (АЦП), который содержит фильтр нижней частоты (ФНЧ), усилитель с цифровым управлением, полосовой фильтр (ПФ), аналого-цифровой преобразователь и опорный генератор, причем ФНЧ последовательно соединен с усилителем с цифровым управлением, ПФ и АЦП, второй модуль представляет собой блок цифровой обработки сигнала (ЦОС) и управления, в который входит цифровой вычислитель состоящий из цифрового сигнального процессора и ядра процессора при этом цифровой вычислитель соединен своими входами с АЦП а выходом с интерполирующим цифроаналоговым преобразователем (ЦАП), который соединен с опорным генератором, причем цифровой вычислитель соединен с пользовательскими интерфейсами и через усилитель мощности с приемником, при этом четыре аналого-цифровых преобразователя, работают синхронно от одного задающего генератора, а для устранения межсимвольной интерференции и работы в основном окне Найквиста частота преобразования выбирается в диапазоне от 65 до 250 МГц, при этом такая архитектура позволяет принимать сигнал от четырех антенн одновременно для построения радиоприемного устройства, причем синхронный прием сигналов от четырех различных антенн позволяет реализовать современные алгоритмы адаптивной обработки.

Таким образом система формирования и обработки сигналов (СФОС) в отличии от аналогов и прототипа обеспечивает улучшение приема информации в условиях замирания сигнала при распространении его по радиоканалу, а также компенсацию помех и адаптацию их по частоте.

Структурная схема предлагаемой СФОС представлена на фиг.1.

1 - модуль преобразования частоты;

2 - модуль цифровой обработки сигнала и управления;

3 - пользовательские интерфейсы;

4 - опорный генератор;

5 - радиоприемник;

6 - усилитель мощности;

7 - фильтры нижних частот;

8 - усилитель с цифровым управлением;

9 - полосовые фильтры;

10- аналого-цифровой преобразователь;

11 - цифроаналоговый преобразователь;

12 - цифровой вычислитель.

Модуль преобразования частоты 1 содержит в своем составе: фильтр нижних частот 7, усилитель с цифровым управлением 8, полосовой фильтр 9, аналого-цифровой преобразователь 10, цифроаналоговый преобразователь 11 и опорный генератор 4.

Модуль ЦОС и управления 2 обеспечивает высокоскоростной интерфейс для связи по волоконно-оптическим линиям связи (ВОЛС) нескольких аппаратных платформ СФОС. В этом случае одна из платформ устанавливается в непосредственной близости от антенн. После предварительной обработки сигналы транслируются на значительные расстояния на другую платформу. На этой платформе модуль аналого-цифровой преобразования 10 можно не устанавливать, или вместо него установить модуль с дополнительными оптическими интерфейсами.

Четырехканальный входной и выходной фильтры нижней частоты 7 обеспечивают селекцию сигналов, т.е. перенос спектра сигналов, поступающих от антенных элементов в область низких частот. Входные аналоговые фильтры представляют собой ФНЧ 7 с частотой среза 30 МГц, имеющий уровень подавления не хуже 80 дБ.

Усилитель с цифровым управлением 8 преобразует уровень поступающего на его вход сигнала до значения, необходимого для последующего преобразования и цифровой обработки (в приемном тракте) или для излучения (в тракте передачи). Аналоговые усилители с цифровым управлением 8 имеют линейную амплитудно-числовую характеристику (АЧХ) в полосе от 0 до 30 МГц с возможностью изменения коэффициента усиления в пределах от 0 до 100 дБ.

Полосовые фильтры 9 обеспечивают полосу пропускания в зависимости от вида использующейся манипуляции с  , где

, где  - ширина полосы занимаемая сигналом и

- ширина полосы занимаемая сигналом и  - частота несущей; АЦП 10 и ЦАП 11 обеспечивают шаг квантования по уровню не более 1,5×10-5 и работают от опорного генератора с тактовой частотой ~168 МГц и частотой опорного генератора оптического интерфейса ~125 МГц. Применение ЦАП 11 с интерполирующими фильтрами при частоте поступления входных отсчетов 250 МГц и четырехкратной интерполяции позволит достичь частоты цифроаналогового преобразования в 1 ГГц. В результате формируемый сигнал, даже на верхней границе КВ-диапазона, будет обладать хорошими спектральными характеристиками. Применение современного ЦАП с интерполирующими фильтрами при частоте поступления входных отсчетов 250 МГц и четырехкратной интерполяции позволит достичь частоты цифроаналогового преобразования в 1 ГГц. В результате формируемый сигнал, даже на верхней границе КВ-диапазона, будет обладать хорошими спектральными характеристиками.

- частота несущей; АЦП 10 и ЦАП 11 обеспечивают шаг квантования по уровню не более 1,5×10-5 и работают от опорного генератора с тактовой частотой ~168 МГц и частотой опорного генератора оптического интерфейса ~125 МГц. Применение ЦАП 11 с интерполирующими фильтрами при частоте поступления входных отсчетов 250 МГц и четырехкратной интерполяции позволит достичь частоты цифроаналогового преобразования в 1 ГГц. В результате формируемый сигнал, даже на верхней границе КВ-диапазона, будет обладать хорошими спектральными характеристиками. Применение современного ЦАП с интерполирующими фильтрами при частоте поступления входных отсчетов 250 МГц и четырехкратной интерполяции позволит достичь частоты цифроаналогового преобразования в 1 ГГц. В результате формируемый сигнал, даже на верхней границе КВ-диапазона, будет обладать хорошими спектральными характеристиками.

Цифровой вычислитель 12 реализуется на ПЛИС технологии и обеспечивает различные пользовательские интерфейсы (Ethernet, асинхронный последовательный интерфейс и т.д.), при этом тактовая частота опорного генератора схем ЦОС составляет -200 МГц.

Если ширина спектра сигнала, в котором осуществляется передача информации, не превышает десятков килогерц то, как уже отмечалось, алгоритмы формирования и приема модемных сигналов целесообразно реализовать на сигнальном процессоре. Алгоритмы реализуются для сигналов, представленных в комплексной форме с центром спектра, расположенным на нулевой частоте (так называемый смещенный сигнал - BaseBand). Перенос спектра сигнала из BaseBand в диапазон частот, в котором осуществляется передача по радиоканалу, не требует большой алгоритмической сложности, но вычислительные ресурсы требуются довольно значительные. Если частота радиосигнала не превышает нескольких сотен мегагерц, имеется возможность непосредственной работы с таким сигналом в цифровом виде. Необходимо осуществить перенос сигнала для передачи вверх по спектру и для приема - вниз. Для этого служат цифровые блоки - преобразователи DUC (Digital Up Converter) и DDC (Digital Down Converter) соответственно.

Имеется обширная номенклатура микросхем DUC/DDC, однако все они предназначены для узкой или специализированной области применения. Некоторые приложения могут потребовать более высокую вычислительную точность, больший динамический диапазон или более глубокой фильтрации, что могут обеспечить существующие специализированные интегральные микросхемы. Получить полностью конфигурируемое решение позволяет применение ПЛИС. При таком подходе блоки DUC/DDC реализуются с любыми характеристиками, и что самое ценное, вариант реализации не будет «заморожен», а может подвергаться модернизации и модификации под другие области применения. Например, при достаточных ресурсах ПЛИС возможна реализация одновременного многоканального приема и передачи.

Алгоритмы собственно модуляции и демодуляции для каналов КВ-диапазонов характеризуются относительно низкой информационной скоростью и высокой вычислительной сложностью, большой разветвленностью, а также присутствием элементов нечеткой логики. Такие алгоритмы хорошо реализуются в программном виде на сигнальных процессорах, однако часть рутинных операций можно реализовать на ПЛИС.

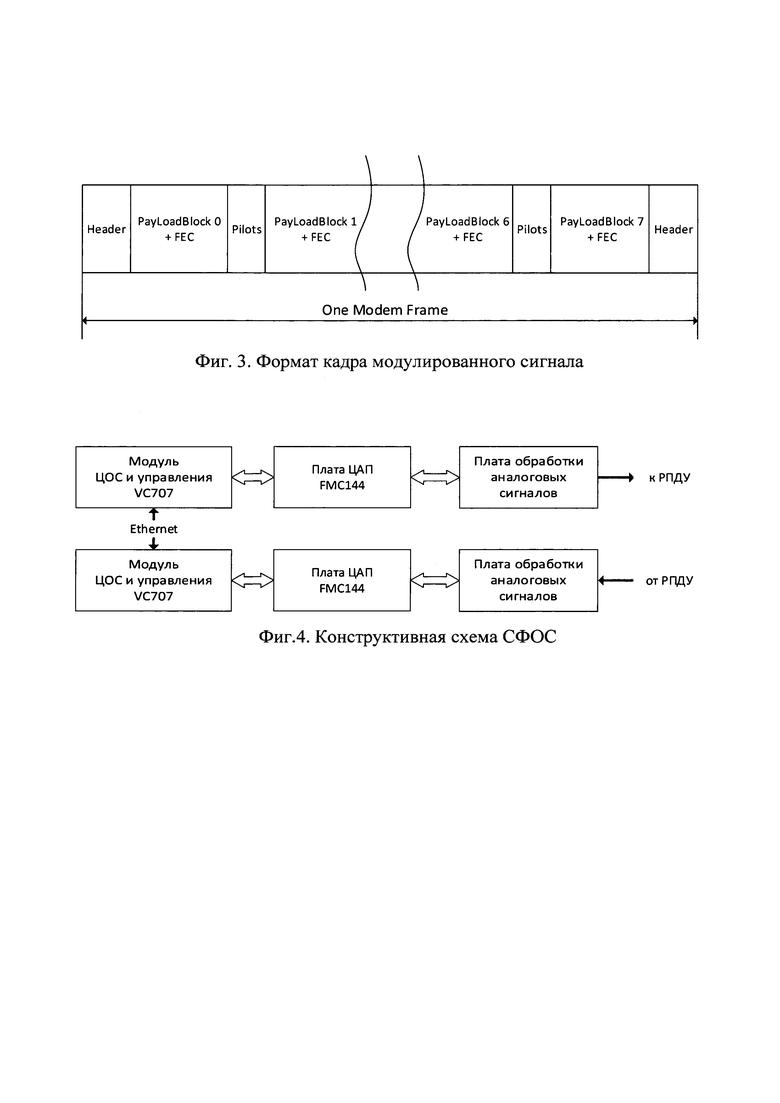

Предлагается функциональная схема модуля ЦОС и управления с распределенной обработкой на ПЛИС (FPGA) и процессором (фиг.2) в составе:

13- блока DDC;

14 - регулируемой линии задержки;

15 - адаптивного фильтра;

16- децемирующего фильтра;

17 - цифрового АРУ;

18 - системы тактовой сигнализации;

19- модуля корреляционной обработки сигнала и фреймирования;

20 - модуля оператора;

21 - модуля настройки, мониторинга и управления;

22 - набора демодуляторов, декодеров;

23 - набора модуляторов, кодеров;

24 - модуля формирования DSSS (Direct Sequence Spread Spectrum -метод прямой последовательности для расширения спектра);

25 - регулятора уровня сигналов блока переноса сигнала на несущую;

26 -блока DUC;

27 - перенос на несущую;

28 - генератора несущей передачи;

29 - генератора символьной скорости;

30 - модуля приема/передачи данных и команд управления по ВОЛС;

31 - интерфейса приема/передачи потока данных, команд управления и мониторинга.

Сигнал, поступающий на вход приемного тракта, подается на блок DDC 13. Блок подавляет помеху по зеркальному каналу приема более, чем на 100 дБ и полностью устраняет помеху на нулевой частоте. Принцип цифрового преобразования в блоке DDC 13 сводится к получению из широкополосного комплексного цифрового сигнала (при очень высокой частоте дискретизации) единственного целевого сигнала, полоса которого существенно уже полосы исходного сигнала. Архитектура блока, обеспечивающая выполнение цифровой фильтрации на высокой скорости потока данных, требует большого вычислительного ресурса и выполняется только аппаратно. Она реализована на ПЛИС Digital Signal Processing (DSP) со встроенными аппаратными умножителями.

Регулируемая линия задержки 14 позволяет скорректировать фазовые сдвиги сигнала, возникшие в результате прохождения сигнала через канал передачи. Адаптивный фильтр 15 производит операцию свертки входных отсчетов с коэффициентами. Децимирующий фильтр 16 позволяет понизить частоту следования отсчетов сигнала.

Блок цифрового АРУ 17 осуществляет автоматическую установку уровня сигнала для последующей его обработки.

Система тактовой синхронизации 18 обеспечивает равенство скоростей обработки сигналов (кодирование и декодирование отсчетов, объединение и разделение цифровых потоков) на передающей и приемной станциях.

Модуль корреляционной обработки сигнала и фреймирования сигнала 19 позволяет разделить входной поток на отдельные информационные слова. После фреймирования каждое информационное слово, в зависимости от поступившего сигнала, поступает на блок цифровой демодуляции и декодирования 22.

Модуль оператора 20 позволяет, в зависимости от типа сообщения, производить коммутацию внутри блока процессора на модули пользовательских интерфейсов 3.

При передаче сигнала операции выполняются в обратном порядке с изменением, при необходимости, частоты дискретизации для увеличения скорости передачи.

Управление схемой, представленной на фиг.2, выполняется по ВОЛС 30 с помощью ПЛИС фирмы Xilinx. Состояние системы выводиться на интерфейс приема/передачи потока данных, команд управления и мониторинга 31.

Распределение функциональной нагрузки между ПЛИС и процессором делается с учетом алгоритмической сложности, требуемой скорости работы, а также расположения функционального элемента в общей схеме конвейера обработки данных и сигналов.

При реализации предлагаемой системы предусмотрена конфигурация т.е. в тракте передачи и приема установлены мультиплексоры, позволяющие изменять состав функциональных элементов в конвейере обработки, например, в тракте приема «обойти» систему тактовой синхронизации или исключить из тракта передачи модуль формирования DSSS сигнала.

На схеме не показаны логические связи между процессором и функциональными элементами в ПЛИС, по которым производится их конфигурирование, настройка, управление и мониторинг 21. Так, например, адаптивный фильтр 15 производит операцию свертки входных отсчетов с коэффициентами на довольно высокой скорости, а сами коэффициенты в более медленном темпе рассчитываются в подпрограмме адаптации и загружаются в фильтр под управлением процессора.

Сложные алгоритмы, такие как демодуляция, декодирование 22, сжатие речи и т.д. с учетом низкой информационной скорости реализуются в виде программных модулей для процессора. На процессор возлагаются также функции работы с пользовательскими интерфейсами и общее управление системой.

С целью увеличения устойчивости канала связи к физическим явлениям среды распространения, введена фреймовая структура модулированного сигнала, сохраняя при этом его непрерывность. Вариант формата кадра представлен на фиг.3.

Здесь служебные поля Header и Pilots не несут пользовательских данных, а предназначены для облегчения и улучшения качества демодуляции полей с пользовательскими данными PayLoad Blocks. Достигается это благодаря следующему:

- вид модуляции полей Header и Pilots позволяет их демодулировать при достаточно низком качестве канала передачи;

- поля Pilots имеют предопределенные значения;

- поле Header имеет сильные автокорреляционные свойства и несет закодированную информацию о виде модуляции и помехоустойчивом кодировании полей PayLoad Blocks.

Используя эти свойства на приемной стороне, улучшается качество демодуляции, оценивая по известным параметрам частоту и фазу сигнала, символьную скорость, отношение сигнал/шум и т.д. Кроме того, установка и поддержание связи проще и надежнее реализуется, когда известны параметры сигнала, передаваемые в поле Header.

Принцип передачи дополнительной служебной информации в надежном информационном контейнере позволяет также реализовать адаптацию по скорости передачи пользовательских данных в зависимости от условий приема.

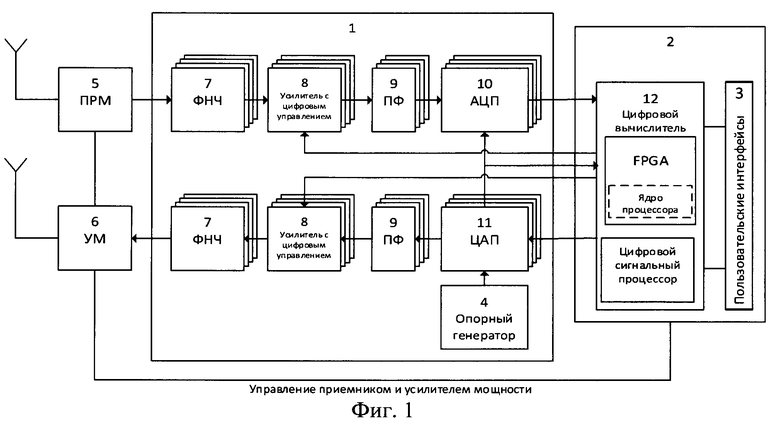

Конструктивно аппаратная платформа СФОС реализуется на шести отдельных платах (фиг.4).

Модули ЦОС и управления для приемного и передающего трактов представляют собой две независимые платы Xilinx Virtex-7, содержащие до двух миллионов логических ячеек каждая, со скоростью внутреннего обмена до 2,8 Tb/s.

Платы АЦП 10 и ЦАП 11 для приемного и передающих трактов представляют собой две независимые 16 разрядные платы FMC144 размером 85×60 мм, позволяющие реализовать до четырех независимых каналов со скоростью преобразования 370 Msps для АЦП и 2,5 Gsps для ЦАП.

Таким образом система формирования и обработки сигналов обеспечивает улучшение приема информации в условиях замирания сигнала при распространении его по радиоканалу, а также компенсацию помех и адаптацию их по частоте.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ФОРМИРОВАНИЯ И ОБРАБОТКИ РАДИОСИГНАЛОВ В КОРОТКОВОЛНОВОМ ДИАПАЗОНЕ | 2024 |

|

RU2825855C1 |

| ПРОЦЕССОР ЦИФРОВОГО РАЗДЕЛЕНИЯ КВАДРАТУР | 2022 |

|

RU2784002C1 |

| Многофункциональный модуль приема сообщений автоматического зависимого наблюдения вещания для малого космического аппарата | 2023 |

|

RU2808790C1 |

| СПОСОБ И УСТРОЙСТВО ОБРАБОТКИ СИГНАЛОВ ЛИНИЙ СВЯЗИ ПО МОДЕЛИ СИГНАЛА И ПЕРЕПРОГРАММИРУЕМЫМ ЭЛЕКТРИЧЕСКИМ СХЕМАМ | 2005 |

|

RU2317641C2 |

| КОРОТКОВОЛНОВАЯ - УЛЬТРАКОРОТКОВОЛНОВАЯ РАДИОСТАНЦИЯ | 2023 |

|

RU2819306C1 |

| Носимая автоматизированная радиостанция диапазона КВ-УКВ | 2018 |

|

RU2696977C1 |

| ВЫЧИСЛИТЕЛЬНЫЙ КОМПЛЕКС РЕГИСТРАЦИИ И СИНТЕЗА РАДИОТЕХНИЧЕСКИХ СИГНАЛОВ | 2007 |

|

RU2351979C2 |

| ПОРТАТИВНАЯ КОРОТКОВОЛНОВАЯ - УЛЬТРАКОРОТКОВОЛНОВАЯ РАДИОСТАНЦИЯ | 2023 |

|

RU2823629C1 |

| КОРАБЕЛЬНОЕ УСТРОЙСТВО ШИРОКОПОЛОСНОЙ СВЯЗИ | 2022 |

|

RU2796961C1 |

| Комплексированное приемопередающее устройство информационного обмена с летательными аппаратами | 2023 |

|

RU2805378C1 |

Изобретение относится к радиотехнике и служит для построения схемных и конструктивных решений по формирователям сигналов, твердотельным усилителям мощности и антенно-фидерным системам КВ-диапазона. Технический результат – улучшение качества приема информации в условиях быстрых и медленных замираний сигналов, наличествующих в ионосферном радиоканале, а также компенсации помех и адаптации их по частоте. Результат достигается тем, что предложена система формирования и обработки радиосигналов в коротковолновом диапазоне, в которой цифровой вычислитель соединен с пользовательскими интерфейсами через усилитель мощности с приемником, причем четыре аналого-цифровых преобразователя выполнены с возможностью синхронной работы от одного задающего генератора и возможностью выбора частоты преобразования в диапазоне от 65 до 250 МГц для работы в основном окне Найквиста, при этом такая архитектура выполнена с возможностью приема радиосигналов от четырех различных антенн одновременно для построения радиоприемного устройства и возможностью применения алгоритмов адаптивной обработки. 4 ил.

Система формирования и обработки радиосигналов в коротковолновом диапазоне, выполненная в виде двух модулей, при этом первый модуль представляет собой четырехканальный аналого-цифровой преобразователь (АЦП), который содержит фильтр нижней частоты (ФНЧ), усилитель с цифровым управлением, полосовой фильтр (ПФ), аналого-цифровой преобразователь и опорный генератор, причем ФНЧ последовательно соединен с усилителем с цифровым управлением, ПФ и АЦП, второй модуль представляет собой блок цифровой обработки сигнала и управления, в который входит цифровой вычислитель, состоящий из цифрового сигнального процессора и ядра процессора, при этом цифровой вычислитель соединен своими входами с АЦП, а выходом с интерполирующим цифроаналоговым преобразователем, который соединен с опорным генератором, причем цифровой вычислитель соединен с пользовательскими интерфейсами и через усилитель мощности с приемником, при этом четыре аналого-цифровых преобразователя выполнены с возможностью синхронной работы от одного задающего генератора и возможностью выбора частоты преобразования в диапазоне от 65 до 250 МГц для работы в основном окне Найквиста, при этом такая архитектура выполнена с возможностью приема радиосигналов от четырех различных антенн одновременно для построения радиоприемного устройства и возможностью применения алгоритмов адаптивной обработки.

| УСТРОЙСТВО ОПТИМАЛЬНОЙ ОБРАБОТКИ ПОСЛЕДОВАТЕЛЬНОСТЕЙ ШИРОКОПОЛОСНЫХ СИГНАЛОВ С МОДУЛЯЦИЕЙ НЕСУЩЕЙ ЧАСТОТЫ | 1990 |

|

RU2237908C2 |

| АКТИВНАЯ ФАЗИРОВАННАЯ АНТЕННАЯ РЕШЕТКА | 2019 |

|

RU2726281C1 |

| РАДИОВОЛНОВОЕ УСТРОЙСТВО ДЛЯ ТРЕВОЖНОЙ СИГНАЛИЗАЦИИ С НЕПРЕРЫВНЫМ ИЗЛУЧЕНИЕМ ЧАСТОТНО-МОДУЛИРОВАННЫХ КОЛЕБАНИЙ | 2014 |

|

RU2584496C1 |

| US 6469657 B1, 22.10.2002 | |||

| US 10605921 B2, 31.03.2020. | |||

Авторы

Даты

2023-11-23—Публикация

2023-06-23—Подача