Предполагаемое изобретение относится к области перспективной элементной базы нейроморфной электроники и может быть использовано в качестве синаптического элемента при интегральной реализации нейронных сетей.

Аналогом заявляемого изобретения является интегральный электронный КМОП синапс с цифровым управлением [Asghar, M.S.; Arslan, S.; Kim, H. A Low-Power Spiking Neural Network Chip Based on a Compact LIF Neuron and Binary Exponential Charge Injector Synapse Circuits. Sensors 2021, 21, 4462. https://doi.org/10.3390/s21134462, с. 8, фиг. 4], содержащий МОП-транзисторы с дырочной проводимостью каналов, определяющие синаптический вес, количество которых M равно логарифму по основанию 2 от числа уровней проводимости N интегрального электронного синапса (M = log2N), причем значения ширины каналов Wi МОП-транзисторов, определяющих синаптический вес, связаны между собой соотношением Wi = 2Wi-1, где i – порядковый номер МОП-транзистора (i = 0, 1,…, M-1); M ключевых МОП-транзисторов с дырочной проводимостью каналов; M КМОП инверторов на основе комплементарных пар МОП-транзисторов с электронной и дырочной проводимостью, контакты затворов которых соединены и образуют входную линию КМОП-инвертора, а контакты стоков которых соединены и образуют выходную линию КМОП-инвертора, причем все ключевые МОП-транзисторы с дырочной проводимостью имеют одинаковые параметры каналов, контакт стока i-го МОП-транзистора с дырочной проводимостью канала, определяющего синаптический вес, соединен с контактом истока i-го ключевого МОП-транзистора с дырочной проводимостью канала для всех i = 0, 1,…, M-1, контакты стоков всех ключевых МОП-транзисторов с дырочной проводимостью канала соединены с выходной линией электронного синапса, контакты затворов всех МОП-транзисторов, определяющих синаптический вес, соединены с линией постоянного напряжения смещения, определяющего проводимости каналов МОП-транзисторов, определяющих синаптический вес, входные линии всех КМОП инверторов соединены со входной линией электронного синапса, выходная линия i-го КМОП инвертора соединена с контактом затвора i-го ключевого МОП-транзистора с дырочной проводимостью канала для всех i = 0, 1,…, M-1, контакты истоков МОП-транзисторов с дырочной проводимостью комплементарных пар всех КМОП-инверторов соединены с линией питания, контакты истоков МОП-транзисторов с электронной проводимостью комплементарных пар КМОП инверторов образуют M-разрядную цифровую управляющую шину электронного синапса.

Недостатками данного интегрального электронного КМОП синапса с цифровым управлением являются:

– узкий рабочий диапазон входного напряжения, обусловленный использованием КМОП-инверторов, обеспечивающих корректное функционирование интегрального электронного КМОП синапса только при амплитуде входных импульсов, равной напряжению питания;

– необходимость использования отдельного КМОП-инвертора для управления каждым из M ключевых МОП-транзисторов, что приводит к увеличению площади, занимаемой электронным синапсом на кристалле, увеличению входной емкости электронного синапса (поскольку входная линия электронного синапса соединена с входными линиями всех M КМОП-инверторов) и, как следствие, к повышению потребляемой мощности;

– одинаковые параметры каналов ключевых МОП-транзисторов с дырочной проводимостью, что приводит, с одной стороны, к увеличению площади, занимаемой ключевыми транзисторами на кристалле, (для ключевых транзисторов, соединенных с МОП-транзисторами, определяющими синаптический вес, с наименьшими значениями ширины каналов), а с другой стороны, к увеличению погрешности установки уровня проводимости (синаптического «веса») (для ключевых транзисторов, соединенных с МОП-транзисторами, определяющими синаптический вес, с наибольшими значениями ширины каналов).

Наиболее близким по технической сущности к заявляемому изобретению (прототипом) является интегральный электронный КМОП синапс [Рындин Е.А., Андреева Н.В. Интегральный электронный КМОП синапс // Патент РФ на изобретение № 2808951, дата приоритета 27.07.2023, дата государственной регистрации в Государственном реестре изобретений Российской Федерации 05.12.2023], содержащий МОП-транзисторы с дырочной проводимостью каналов, определяющие синаптический вес, количество которых M равно логарифму по основанию 2 от числа уровней проводимости N интегрального электронного синапса (M = log2N), причем значения ширины каналов Wi МОП-транзисторов, определяющих синаптический вес, связаны между собой соотношением Wi = 2Wi-1, где i – порядковый номер МОП-транзистора (i = 0, 1,…, M-1); M ключевых МОП-транзисторов с дырочной проводимостью каналов, причем ширина канала i-го ключевого МОП-транзистора с дырочной проводимостью канала равна ширине канала i-го МОП-транзистора с дырочной проводимостью канала, определяющего синаптический вес, для всех i = 0, 1,…, M-1, контакты истоков всех ключевых МОП-транзисторов с дырочной проводимостью каналов соединены с линией питания, контакт стока i-го ключевого МОП-транзистора с дырочной проводимостью канала соединен с контактом истока i-го МОП-транзистора с дырочной проводимостью канала, определяющего синаптический вес, для всех i = 0, 1,…, M-1, контакты стоков всех МОП-транзисторов с дырочной проводимостью каналов, определяющих синаптический вес, соединены с выходной линией электронного синапса, контакты затворов всех ключевых МОП-транзисторов с дырочной проводимостью каналов образуют M-разрядную цифровую управляющую шину электронного синапса, КМОП-инвертор на основе комплементарной пары МОП-транзисторов с электронной и дырочной проводимостью, контакты затворов которых соединены и образуют входную линию электронного синапса, а контакты стоков соединены и образуют выходную линию КМОП-инвертора, причем контакт истока МОП-транзистора с дырочной проводимостью КМОП-инвертора соединен с линией питания, контакт истока МОП-транзистора с электронной проводимостью КМОП-инвертора соединен с линией постоянного напряжения смещения, контакты затворов всех МОП-транзисторов с дырочной проводимостью каналов, определяющих синаптический вес, соединены с выходной линией КМОП-инвертора.

Признаками прототипа, совпадающими с существенными признаками заявляемого изобретения, являются МОП-транзисторы с дырочной проводимостью каналов, определяющие синаптический вес, количество которых M равно логарифму по основанию 2 от числа уровней проводимости N интегрального электронного синапса (M = log2N), причем значения ширины каналов Wi МОП-транзисторов, определяющих синаптический вес, связаны между собой соотношением Wi = 2Wi-1, где i – порядковый номер МОП-транзистора (i = 0, 1,…, M-1); M ключевых МОП-транзисторов с дырочной проводимостью каналов, причем ширина канала i-го ключевого МОП-транзистора с дырочной проводимостью канала равна ширине канала i-го МОП-транзистора с дырочной проводимостью канала, определяющего синаптический вес, для всех i = 0, 1,…, M-1, контакты истоков всех ключевых МОП-транзисторов с дырочной проводимостью каналов соединены с линией питания, контакт стока i-го ключевого МОП-транзистора с дырочной проводимостью канала соединен с контактом истока i-го МОП-транзистора с дырочной проводимостью канала, определяющего синаптический вес, для всех i = 0, 1,…, M-1, контакты стоков всех МОП-транзисторов с дырочной проводимостью каналов, определяющих синаптический вес, соединены с выходной линией электронного синапса, контакты затворов всех ключевых МОП-транзисторов с дырочной проводимостью каналов образуют M-разрядную цифровую управляющую шину электронного синапса.

Недостатком прототипа является узкий рабочий диапазон входного напряжения, обусловленный использованием КМОП-инвертора на основе комплементарной пары МОП-транзисторов с электронной и дырочной проводимостью, обеспечивающего корректное функционирование интегрального электронного КМОП синапса только при амплитуде входных импульсов, равной напряжению питания. Описанный технический недостаток ограничивает область применения данного КМОП синапса аппаратной реализацией только импульсных нейронных сетей.

Задачей изобретения является расширение области применения интегрального электронного синаптического КМОП-элемента для аппаратной реализации любых видов нейронных сетей за счет достижения технического результата, заключающегося в расширении от нуля до напряжения питания рабочего диапазона входного аналогового напряжения, обеспечивающего формирование выходного тока, определяемого произведением двоичного кода синаптического веса (проводимости) на произвольный уровень входного аналогового напряжения (в диапазоне от нуля до напряжения питания).

Задача решается тем, что в интегральный электронный синаптический КМОП-элемент, содержащий МОП-транзисторы с дырочной проводимостью каналов, определяющие синаптический вес, количество которых M равно логарифму по основанию 2 от числа уровней проводимости N интегрального электронного синапса (M = log2N), причем значения ширины каналов Wi МОП-транзисторов, определяющих синаптический вес, связаны между собой соотношением Wi = 2Wi-1, где i – порядковый номер МОП-транзистора (i = 0, 1,…, M-1); M ключевых МОП-транзисторов с дырочной проводимостью каналов, причем ширина канала i-го ключевого МОП-транзистора с дырочной проводимостью равна ширине канала i-го МОП-транзистора с дырочной проводимостью, определяющего синаптический вес, для всех i = 0, 1,…, M-1, контакты истоков всех ключевых МОП-транзисторов с дырочной проводимостью каналов соединены с линией питания, контакт стока i-го ключевого МОП-транзистора с дырочной проводимостью канала соединен с контактом истока i-го МОП-транзистора с дырочной проводимостью канала, определяющего синаптический вес, для всех i = 0, 1,…, M-1, контакты стоков всех МОП-транзисторов с дырочной проводимостью каналов, определяющих синаптический вес, соединены с выходной линией электронного синаптического КМОП-элемента, контакты затворов всех ключевых МОП-транзисторов с дырочной проводимостью каналов образуют M-разрядную цифровую управляющую шину электронного синаптического КМОП-элемента, введены инвертирующий усилитель, образованный интегральным операционным усилителем, первым, вторым, третьим и четвертым интегральными резисторами. Причем первый интегральный резистор соединен своим первым контактом с входной линией, а вторым контактом – с инвертирующим входом операционного усилителя. Второй интегральный резистор соединен своим первым контактом с инвертирующим входом операционного усилителя, а вторым контактом – с выходной линией операционного усилителя. Третий интегральный резистор соединен своим первым контактом с линией питания, а вторым контактом – с неинвертирующим входом операционного усилителя. Четвертый интегральный резистор соединен своим первым контактом с неинвертирующим входом операционного усилителя, а вторым контактом – с линией нулевого потенциала. Контакт положительного полюса питания операционного усилителя соединен с линией питания, а контакт отрицательного полюса питания операционного усилителя соединен с линией нулевого потенциала. Контакты затворов всех МОП-транзисторов с дырочной проводимостью каналов, определяющих синаптический вес, соединены с выходной линией операционного усилителя. Соотношение сопротивлений первого и второго, третьего и четвертого интегральных резисторов обеспечивает изменение напряжения на выходной линии операционного усилителя и соединенных с ней контактах затворов всех МОП-транзисторов с дырочной проводимостью каналов, определяющих синаптический вес, в диапазоне, соответствующем квазилинейному участку проходных характеристик МОП-транзисторов с дырочной проводимостью каналов, определяющих синаптический вес.

Достижение технического результата обеспечивается за счет введения перечисленных элементов, а также за счет того, что соотношение сопротивлений первого и второго, третьего и четвертого интегральных резисторов обеспечивает изменение напряжения на выходной линии операционного усилителя и соединенных с ней контактах затворов всех МОП-транзисторов с дырочной проводимостью каналов, определяющих синаптический вес, в диапазоне, соответствующем квазилинейному участку проходных характеристик МОП-транзисторов с дырочной проводимостью каналов, определяющих синаптический вес, обеспечило формирование выходного тока синаптического КМОП-элемента, равного произведению любого уровня напряжения на входной линии (в диапазоне от нуля до напряжения питания) на проводимость – синаптический вес, определяемые двоичным кодом на M-разрядной цифровой управляющей шине, благодаря чему получен положительный эффект, заключающийся в расширении рабочего диапазона входного аналогового напряжения электронного синаптического КМОП-элемента от нуля до напряжения питания с целью расширения области его применения для аппаратной реализации любых видов нейронных сетей.

Изобретение поясняется чертежами.

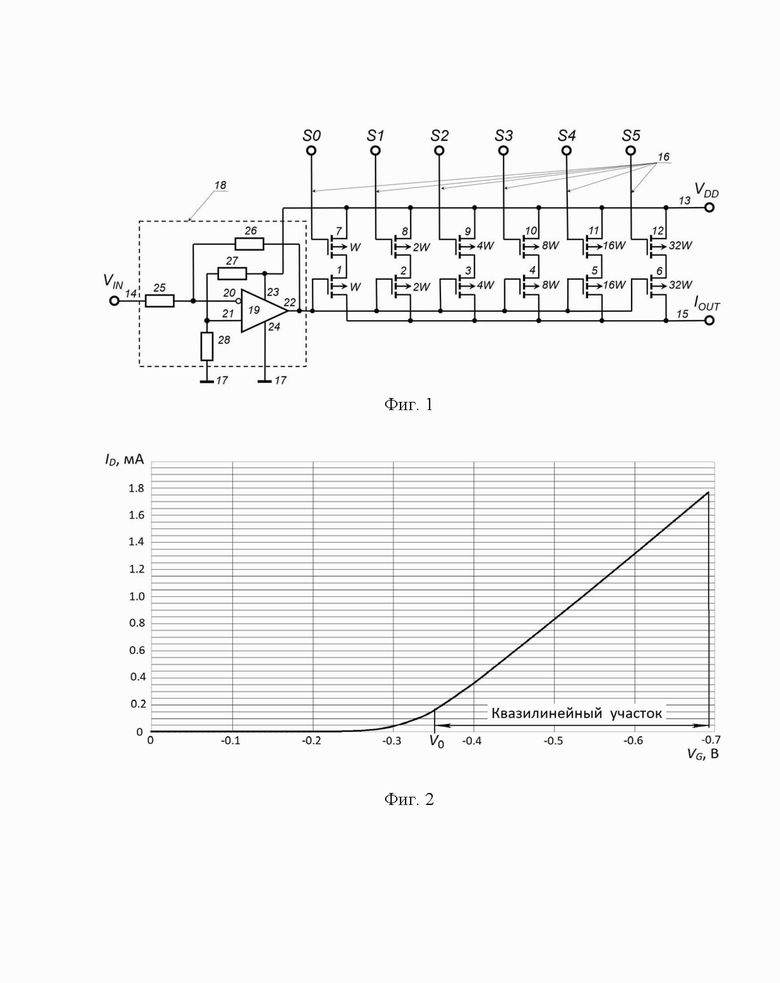

На фиг. 1 приведена схема электрическая принципиальная предлагаемого интегрального электронного синаптического КМОП-элемента (на примере для количества M МОП-транзисторов, определяющих синаптический вес, M = log264 = 6).

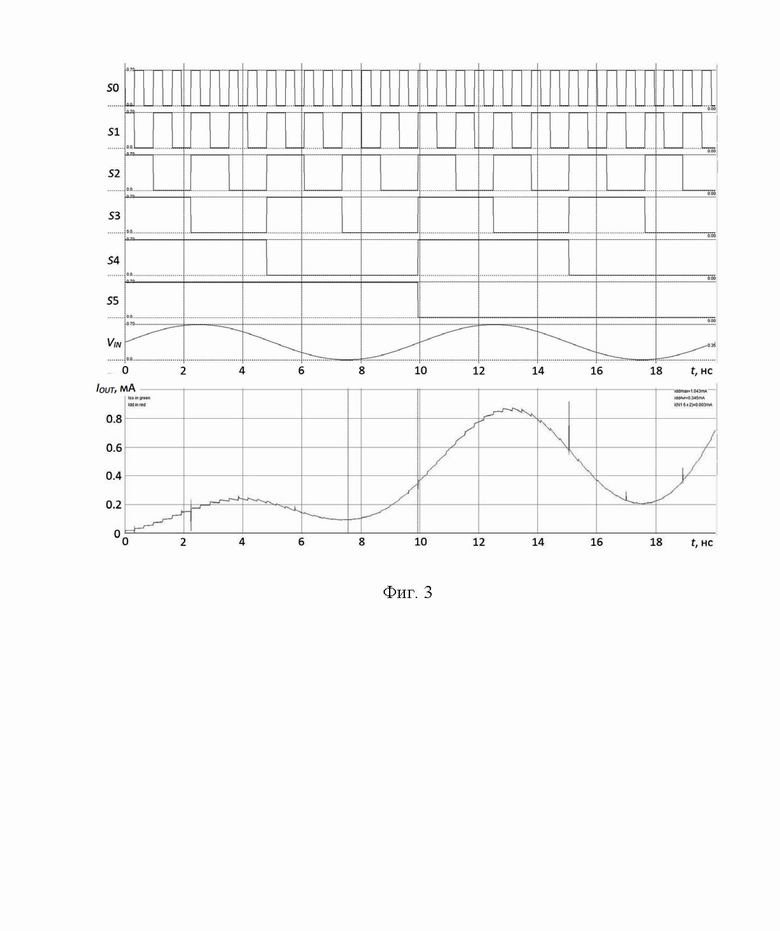

На фиг. 2 приведена проходная вольт-амперная характеристика МОП-транзисторов, определяющих синаптический вес.

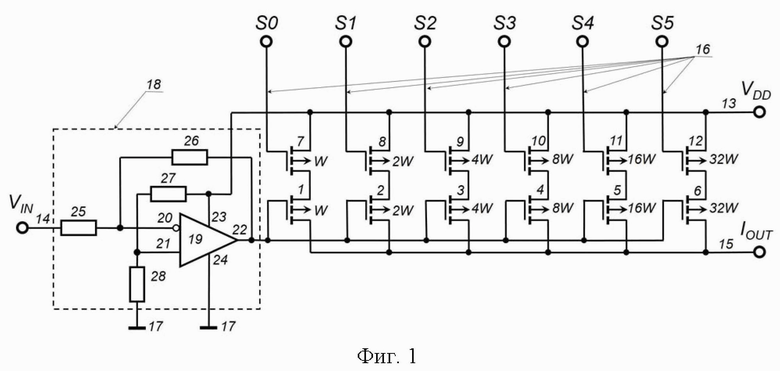

На фиг. 3 приведены временные диаграммы предлагаемого интегрального электронного синаптического КМОП-элемента.

Интегральный электронный КМОП синапс (фиг. 1) содержит МОП-транзисторы 1 – 6 с дырочной проводимостью каналов, определяющие синаптический вес, ключевые МОП-транзисторы 7 – 12 с дырочной проводимостью каналов, линию питания 13 VDD, входную линию 14 электронного синаптического КМОП-элемента VIN, выходную линию 15 электронного синаптического КМОП-элемента IOUT, цифровую управляющую шину 16 электронного синапса S5 – S0 (S5 – старший разряд, S0 – младший разряд), образованную контактами затворов ключевых МОП-транзисторов 7 – 12 с дырочной проводимостью каналов, линию нулевого потенциала 17, инвертирующий усилитель 18, образованный интегральным операционным усилителем 19 с инвертирующим входом 20, неинвертирующим входом 21, выходной линией 22, контактом положительного полюса питания 23 и контактом отрицательного полюса питания 24, первым интегральным резистором 25, вторым интегральным резистором 26, третьим интегральным резистором 27 и четвертым интегральным резистором 28.

Контакты истоков ключевых МОП-транзисторов 7 – 12 с дырочной проводимостью каналов соединены с линией питания 13 VDD. Контакт стока каждого i-го из ключевых МОП-транзисторов с дырочной проводимостью канала 7-12 соединен с контактом истока соответствующего i-го из МОП-транзисторов 1-6 с дырочной проводимостью каналов, определяющих синаптический вес, для всех i = 0, 1,…, M-1. Контакты стоков МОП-транзисторов 1 – 6 с дырочной проводимостью каналов, определяющих синаптический вес, соединены с выходной линией 15 электронного синаптического КМОП-элемента IOUT. Контакты затворов ключевых МОП-транзисторов 7 – 12 с дырочной проводимостью каналов образуют M-разрядную цифровую управляющую шину 16. Первый интегральный резистор 25 соединен своим первым контактом со входной линией 14, а вторым контактом – с инвертирующим входом 20 операционного усилителя. Второй интегральный резистор 26 соединен своим первым контактом с инвертирующим входом 20 операционного усилителя, а вторым контактом – с выходной линией 22 операционного усилителя. Третий интегральный резистор 27 соединен своим первым контактом с линией питания 13, а вторым контактом – с неинвертирующим входом 21 операционного усилителя. Четвертый интегральный резистор 28 соединен своим первым контактом с неинвертирующим входом 21 операционного усилителя, а вторым контактом – с линией нулевого потенциала 17. Контакт положительного полюса питания 23 операционного усилителя 19 соединен с линией питания 13, контакт отрицательного полюса питания 24 операционного усилителя соединен с линией нулевого потенциала 17. Контакты затворов МОП-транзисторов 1 – 6 с дырочной проводимостью каналов, определяющих синаптический вес, соединены с выходной линией 22 операционного усилителя.

Количество M МОП-транзисторов 1 – 6 с дырочной проводимостью каналов, определяющих синаптический вес, равно логарифму по основанию 2 от числа уровней проводимости N интегрального электронного синапса (на фиг. 1 M = log264 = 6), причем значения ширины каналов Wi МОП-транзисторов 1 – 6 связаны между собой соотношением Wi = 2Wi-1, где i – порядковый номер МОП-транзистора (i = 0, 1,…, M-1). Ширина канала i-го ключевого МОП-транзистора с дырочной проводимостью равна ширине канала i-го МОП-транзистора с дырочной проводимостью, определяющего синаптический вес, для всех i = 0, 1,…, M-1. Соотношение сопротивлений первого интегрального резистора 25 и второго интегрального резистора 26, третьего интегральный резистора 27 и четвертого интегрального резистора 28 обеспечивает изменение напряжения на выходной линии 22 операционного усилителя 19 и соединенных с ней контактах затворов МОП-транзисторов 1 – 6 с дырочной проводимостью каналов, определяющих синаптический вес, в диапазоне, соответствующем квазилинейному участку проходных характеристик МОП-транзисторов 1 – 6 с дырочной проводимостью каналов, определяющих синаптический вес.

На фиг.2: ID – ток стока, VG – напряжение затвор-исток МОП-транзистора с дырочной проводимостью канала, V0 – начальное напряжение квазилинейного участка проходной вольт-амперной характеристики МОП-транзистора.

Работает устройство следующим образом.

Напряжение питания VDD подается на линию питания 13, соединенную с истоками ключевых МОП-транзисторов 7 – 12 и контактом положительного полюса питания 23 операционного усилителя 19, относительно линии 17 нулевого потенциала, соединенной с контактом отрицательного полюса питания 24 операционного усилителя 19.

При подаче двоичного кода синаптического веса (с активным уровнем логического нуля) на управляющую цифровую шину 16, ключевые МОП-транзисторы 7 – 12, на затворы которых подан активный нулевой уровень напряжения, откроются, подавая напряжение питания VDD с линии 13 на истоки соответствующих МОП-транзисторов 1 – 6, определяющих синаптический вес. Поскольку значения ширины каналов Wi МОП-транзисторов 1 – 6, определяющих синаптический вес, связаны между собой соотношением Wi+1 = 2Wi, где i – номер соответствующего двоичного разряда цифровой управляющей шины 16, проводимости каналов Gi транзисторов 1 – 6 будут связаны между собой аналогичным образом Gi+1 = 2Gi. В результате полная проводимость электронного синаптического КМОП-элемента GS будет определяться выражением:

где M – число двоичных разрядов управляющей шины 16 (S0 – SM-1), принимающих значения 0 или 1 в соответствии с цифровым кодом синаптического веса; G0 – проводимость канала МОП-транзистора 1.

При этом напряжение VIN, изменяющееся во времени в диапазоне от нуля до напряжения питания VDD, со входной линии 14 электронного синаптического КМОП-элемента подается на вход инвертирующего усилителя 18, образованного соединением первого контакта первого интегрального резистора 25 со входной линией 14 электронного синаптического КМОП-элемента, второго контакта первого интегрального резистора 25 с инвертирующим входом 20 операционного усилителя 19, первого контакта второго интегрального резистора 26 с выходной линией 22 операционного усилителя 19, второго контакта второго интегрального резистора 26 с инвертирующим входом 20 операционного усилителя 19, первого контакта третьего резистора 27 с линией питания 13 электронного синаптического КМОП-элемента, второго контакта третьего резистора 27 и первого контакта четвертого интегрального резистора 28 с неинвертирующим входом 21 операционного усилителя 19, второго контакта четвертого интегрального резистора 28 с линией нулевого потенциала 17. Соотношения между сопротивлениями интегральных резисторов 25, 26, 27 и 28 рассчитываются из условия обеспечения диапазона изменения выходного напряжения операционного усилителя 19, соответствующего квазилинейному участку приведенной на фиг. 2 проходной вольт-амперной характеристики МОП-транзисторов 1 – 6 с дырочной проводимостью каналов, определяющих синаптический вес, что обеспечит прямо пропорциональную зависимость проводимости транзисторного канала G0 в выражении (1) и, как следствие, тока IOUT интегрального синаптического КМОП-элемента на выходной линии 15, напряжению VIN на входной линии 14, при выполнении следующих соотношений:

где R1 – сопротивление первого интегрального резистора 25;

R2 – сопротивление второго интегрального резистора 26;

R3 – сопротивление третьего интегрального резистора 27;

R4 – сопротивление четвертого интегрального резистора 28;

V 0 – начальное напряжение квазилинейного участка проходной вольт-амперной характеристики МОП-транзисторов 1 – 6 с дырочной проводимостью каналов, определяющих синаптический вес (фиг. 2);

VDD – напряжение питания.

В результате выходной ток IOUT синаптического КМОП-элемента будет определяться произведением аналогового уровня входного напряжения VIN на двоичный код синаптического веса на цифровой управляющей шине 16.

Сопротивления каналов ключевых МОП-транзисторов 7 – 12, соединенных последовательно с каналами МОП-транзисторов 1 – 6, будут вносить погрешность в устанавливаемые в соответствии с выражением (1) значения проводимости электронного синаптического КМОП-элемента. Для минимизации данной погрешности (и одновременно занимаемой площади, емкости и энергопотребления) ширина канала i-го ключевого МОП-транзистора с дырочной проводимостью канала равна ширине канала i-го МОП-транзистора, определяющего синаптический вес, для всех

i = 0, 1,…, M-1, то есть значения ширины каналов Wi ключевых МОП-транзисторов 7 – 12 связаны между собой соотношением Wi = 2Wi-1, так же, как значения ширины каналов МОП-транзисторов 1 – 6. При этом суммарная проводимость ключевых МОП-транзисторов 7 – 12 пропорциональна цифровому коду S5 – S0 на управляющей цифровой шине 16, аналогично суммарной проводимости МОП-транзисторов 1 – 6.

Таким образом, интегральный электронный синаптический КМОП-элемент разработан и реализован как аналоговый электронный синапс с цифровым управлением проводимостью (с прямым преобразованием «цифровой код – уровень проводимости»), обеспечивающий формирование выходного тока, определяемого произведением двоичного кода синаптического веса (проводимости) на произвольный уровень входного аналогового напряжения (в диапазоне от нуля до напряжения питания), что обеспечивает применимость данного электронного синаптического КМОП-элемента для аппаратной реализации любых нейронных сетей.

В соответствии с временными диаграммами на фиг. 3, полученными в результате схемотехнического моделирования топологической реализации предлагаемого интегрального электронного синаптического КМОП-элемента по технологии с проектной нормой 50 нм для напряжения питания VDD = 0.7 В, при инкременте двоичного кода синаптического веса на цифровой управляющей шине (временные диаграммы S5 – S0) и синусоидальном изменении напряжения VIN на входной линии интегрального электронного синаптического КМОП-элемента в пределах от 0 до напряжения питания VDD, амплитуда синусоиды выходного тока IOUT интегрального электронного синаптического КМОП-элемента ступенчато увеличивается с увеличением двоичного кода на цифровой управляющей шине, то есть выходной ток определяется произведением уровня входного аналогового сигнала VIN на двоичный код синаптического веса.

Положительный эффект, заключающийся в расширении рабочего диапазона входного аналогового напряжения электронного синаптического КМОП-элемента от нуля до напряжения питания, получен за счет введения перечисленных выше новых признаков, не определяется конкретной технологией реализации устройства и обеспечивает возможность использования электронного синаптического КМОП-элемента для аппаратной реализации любых видов нейронных сетей.

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегральный электронный КМОП синапс | 2023 |

|

RU2808951C1 |

| МОП ДИОДНАЯ ЯЧЕЙКА МОНОЛИТНОГО ДЕТЕКТОРА ИЗЛУЧЕНИЙ | 2011 |

|

RU2494497C2 |

| НИЗКОВОЛЬТНОЕ КМОП ТОКОВОЕ ЗЕРКАЛО | 2013 |

|

RU2544780C1 |

| ЕМКОСТНАЯ МОП ДИОДНАЯ ЯЧЕЙКА ФОТОПРИЕМНИКА-ДЕТЕКТОРА ИЗЛУЧЕНИЙ | 2014 |

|

RU2583955C1 |

| Операционный усилитель на КМОП транзисторах | 1988 |

|

SU1676065A1 |

| Многоканальный коммутатор | 1989 |

|

SU1644373A1 |

| ФУНКЦИОНАЛЬНО-ИНТЕГРИРОВАННАЯ ЯЧЕЙКА ФОТОЧУВСТВИТЕЛЬНОЙ МАТРИЦЫ | 2012 |

|

RU2517917C2 |

| УПРАВЛЯЕМЫЙ КОЛЬЦЕВОЙ ГЕНЕРАТОР ИМПУЛЬСОВ | 2014 |

|

RU2546073C1 |

| ИНТЕГРАЛЬНЫЙ N-РАЗРЯДНЫЙ ЦИФРОАНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ (ЦАП) (ВАРИАНТЫ) | 1995 |

|

RU2113055C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ КМОП КОМПАРАТОР НАПРЯЖЕНИЯ | 1992 |

|

RU2019913C1 |

Изобретение относится к области нейроморфной электроники и может быть использовано в качестве синаптического элемента при интегральной реализации нейронных сетей. Технический результат заключается в расширении рабочего диапазона входного аналогового напряжения электронного синаптического КМОП-элемента. Для этого предложен интегральный электронный синаптический КМОП-элемент, содержащий МОП-транзисторы с дырочной проводимостью каналов и дополнительно содержащий инвертирующий усилитель, образованный интегральным операционным усилителем, первым, вторым, третьим и четвертым интегральными резисторами. 3 ил.

Интегральный электронный синаптический КМОП-элемент, содержащий МОП-транзисторы с дырочной проводимостью каналов, определяющие синаптический вес, количество которых M равно логарифму по основанию 2 от числа уровней проводимости N интегрального электронного синапса, причем значения ширины каналов Wi МОП-транзисторов, определяющих синаптический вес, связаны между собой соотношением Wi = 2Wi-1, где i – порядковый номер МОП-транзистора (i = 0, 1, …, M-1); M ключевых МОП-транзисторов с дырочной проводимостью каналов, причем ширина канала i-го ключевого МОП-транзистора с дырочной проводимостью равна ширине канала i-го МОП-транзистора с дырочной проводимостью, определяющего синаптический вес, для всех i = 0, 1, …, M-1, контакты истоков всех ключевых МОП-транзисторов с дырочной проводимостью каналов соединены с линией питания, контакт стока i-го ключевого МОП-транзистора с дырочной проводимостью канала соединен с контактом истока i-го МОП-транзистора с дырочной проводимостью канала, определяющего синаптический вес, для всех i = 0, 1, …, M-1, контакты стоков всех МОП-транзисторов с дырочной проводимостью каналов, определяющих синаптический вес, соединены с выходной линией электронного синаптического КМОП-элемента, контакты затворов всех ключевых МОП-транзисторов с дырочной проводимостью каналов образуют M-разрядную цифровую управляющую шину электронного синаптического КМОП-элемента, отличающийся тем, что в него введены инвертирующий усилитель, образованный интегральным операционным усилителем, первым, вторым, третьим и четвертым интегральными резисторами, причем первый интегральный резистор соединен своим первым контактом со входной линией интегрального электронного синаптического КМОП-элемента, а вторым контактом – с инвертирующим входом операционного усилителя, второй интегральный резистор соединен своим первым контактом с инвертирующим входом операционного усилителя, а вторым контактом – с выходной линией операционного усилителя, третий интегральный резистор соединен своим первым контактом с линией питания интегрального электронного синаптического КМОП-элемента, а вторым контактом – с неинвертирующим входом операционного усилителя, четвертый интегральный резистор соединен своим первым контактом с неинвертирующим входом операционного усилителя, а вторым контактом – с линией нулевого потенциала интегрального электронного синаптического КМОП-элемента, контакт положительного полюса питания операционного усилителя соединен с линией питания интегрального электронного синаптического КМОП-элемента, контакт отрицательного полюса питания операционного усилителя соединен с линией нулевого потенциала интегрального электронного синаптического КМОП-элемента, контакты затворов всех МОП-транзисторов с дырочной проводимостью каналов, определяющих синаптический вес, соединены с выходной линией операционного усилителя, соотношение сопротивлений первого и второго, третьего и четвертого интегральных резисторов обеспечивает изменение напряжения на выходной линии операционного усилителя и соединенных с ней контактах затворов всех МОП-транзисторов с дырочной проводимостью каналов, определяющих синаптический вес, в диапазоне, соответствующем квазилинейному участку проходных характеристик МОП-транзисторов с дырочной проводимостью каналов, определяющих синаптический вес.

| Интегральный электронный КМОП синапс | 2023 |

|

RU2808951C1 |

| СИНАПТИЧЕСКИЙ РЕЗИСТОР | 2018 |

|

RU2701705C1 |

| Станок для придания концам круглых радиаторных трубок шестигранного сечения | 1924 |

|

SU2019A1 |

| US 5704014 A1, 30.12.1997. | |||

Авторы

Даты

2025-03-18—Публикация

2024-09-13—Подача