Перекрестная ссылка на родственные заявки

Настоящее изобретение испрашивает приоритет по заявке на патент Китая 202110753695.0, озаглавленной «ЯЧЕЙКА ПАМЯТИ И СПОСОБ ЕЕ ИЗГОТОВЛЕНИЯ, А ТАКЖЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО И СПОСОБ ЕГО ИЗГОТОВЛЕНИЯ», поданной в Национальное управление интеллектуальной собственности Китая (CNIPA) 2 июля 2021 года, которая полностью включена в настоящий документ посредством ссылки.

Область техники

Настоящее изобретение относится к технической области полупроводников и, в частности, к ячейке памяти и способу ее изготовления, а также к запоминающему устройству и способу его изготовления.

Уровень техники

Динамическое запоминающее устройство с произвольным доступом (dynamic random access memory, DRAM) представляет собой полупроводниковое запоминающее устройство, которое произвольно записывает и считывает данные на высокой скорости и широко используется в устройствах или аппаратуре хранения данных.

DRAM обычно включает в себя основу, массив ячеек памяти, образованный множеством повторяющихся ячеек памяти, и периферийную схему, размещенную на основе. Множество ячеек памяти расположены с интервалами вдоль направления, параллельного основе. Каждая из ячеек памяти обычно включает в себя конденсаторную структуру и транзистор, затвор которого соединен с линией слов в массиве ячеек памяти, сток соединен с линией битов в массиве ячеек памяти, а исток соединен с конденсаторной структурой.

Однако конструкция не подходит для изготовления малогабаритных запоминающих устройств.

Раскрытие сущности изобретения

В первом аспекте вариантов реализации настоящего изобретения предложена ячейка памяти, включающая в себя:

первый транзистор, расположенный в первом диэлектрическом слое;

второй транзистор, расположенный во втором диэлектрическом слое, причем второй диэлектрический слой расположен над первым диэлектрическим слоем; и

соединительный провод, расположенный в первом диэлектрическом слое и во втором диэлектрическом слое, причем один конец соединительного провода соединен с первым транзистором, а другой конец соединен со вторым транзистором; при этом

первый транзистор и второй транзистор представляют собой металл-оксидные тонкопленочные транзисторы.

Во втором аспекте вариантов реализации настоящего изобретения предложено запоминающее устройство, включающее в себя:

основу, причем периферийная схема размещена на поверхности основы;

множество ячеек памяти, описанных выше, расположенных над периферийной схемой; и

линию передачи данных, выполненную с возможностью соединения периферийной схемы с ячейками памяти.

В запоминающем устройстве, описанном выше, множество ячеек памяти расположены в направлении, параллельном основе, с образованием горизонтального массива; и/или

множество ячеек памяти уложены в стопу в направлении, перпендикулярном основе, с образованием вертикального массива.

В третьем аспекте вариантов реализации настоящего изобретения предложен способ изготовления ячейки памяти, включающий в себя:

формирование первого транзистора в первом диэлектрическом слое, при этом первый транзистор представляет собой металл-оксидный тонкопленочный транзистор;

формирование части соединительного провода в первом диэлектрическом слое, при этом один конец соединительного провода соединен с первым транзистором;

формирование второго диэлектрического слоя на первом диэлектрическом слое;

формирование другой части соединительного провода во втором диэлектрическом слое, причем один конец соединительного провода вблизи первого диэлектрического слоя соединен с соединительным проводом, сформированным в первом диэлектрическом слое; и

формирование второго транзистора во втором диэлектрическом слое, причем второй транзистор соединен с одним концом соединительного провода на удалении от первого диэлектрического слоя, и второй транзистор представляет собой металл-оксидный тонкопленочный транзистор.

В четвертом аспекте вариантов реализации настоящей заявки предложен способ изготовления запоминающего устройства, включающий в себя:

обеспечение основы, причем периферийная схема размещена на поверхности основы;

формирование множества ячеек памяти последовательно на основе, причем множество ячеек памяти расположены в направлении, параллельном основе, с образованием горизонтального массива; и/или множество ячеек памяти уложены в стопу в направлении, перпендикулярном основе, с образованием вертикального массива; при этом ячейка памяти получена с использованием вышеописанного способа изготовления ячейки памяти;

формирование линии передачи данных, причем линия передачи данных выполнена с возможностью соединения периферийной схемы с ячейками памяти.

В дополнение к техническим проблемам, решенным вариантами реализации настоящего изобретения, техническим признакам, составляющим технические решения, и обеспечивающим преимущество эффектам, вызванным техническими признаками этих технических решений, другие технические проблемы, которые должны быть решены посредством ячейки памяти и способа ее изготовления, а также запоминающего устройства и способу его изготовления в вариантах реализации настоящего раскрытия, другие технические признаки, включенные в технические решения, и обеспечивающие преимущество эффекты, вызванные этими техническими признаками, подробно описаны в конкретных вариантах осуществления.

Краткое описание чертежей

Для более ясного описания технических решений в вариантах реализации настоящего изобретения или в предшествующем уровне техники, ниже кратко описаны чертежи, необходимые для описания вариантов реализации или предшествующего уровня техники. Очевидно, чертежи в нижеследующем описании показывают некоторые варианты реализации настоящего изобретения, и специалист в данной области техники может при этом получить другие чертежи из этих чертежей без творческих усилий.

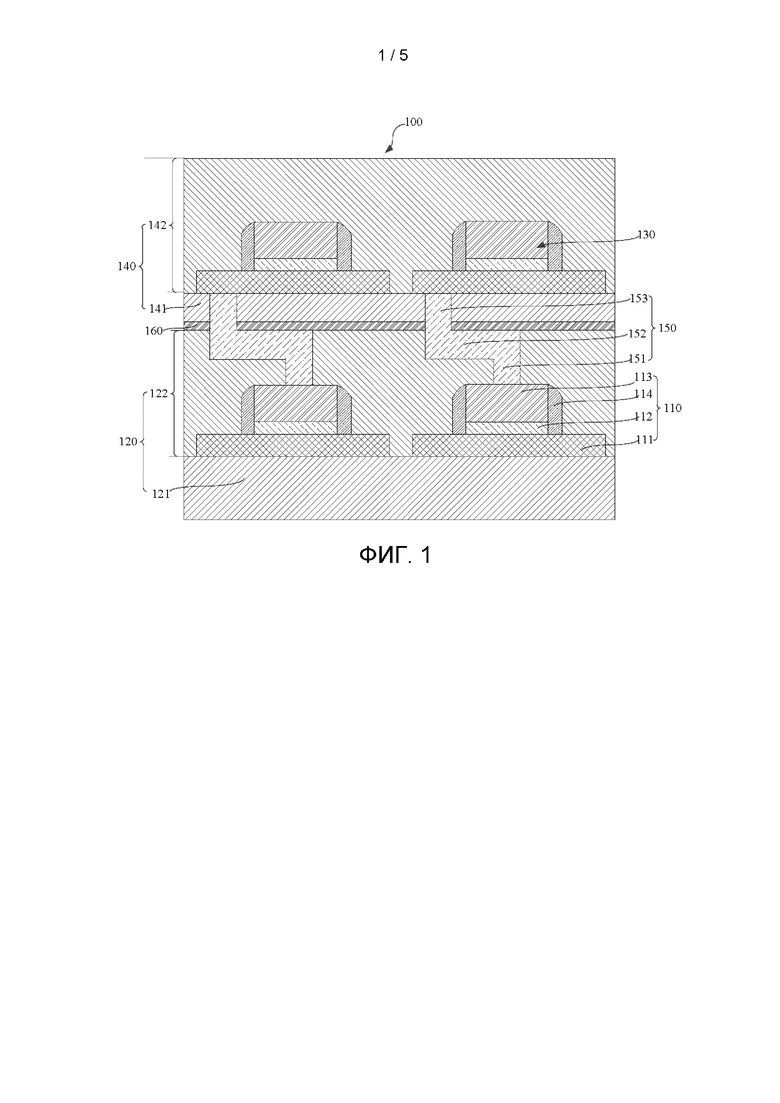

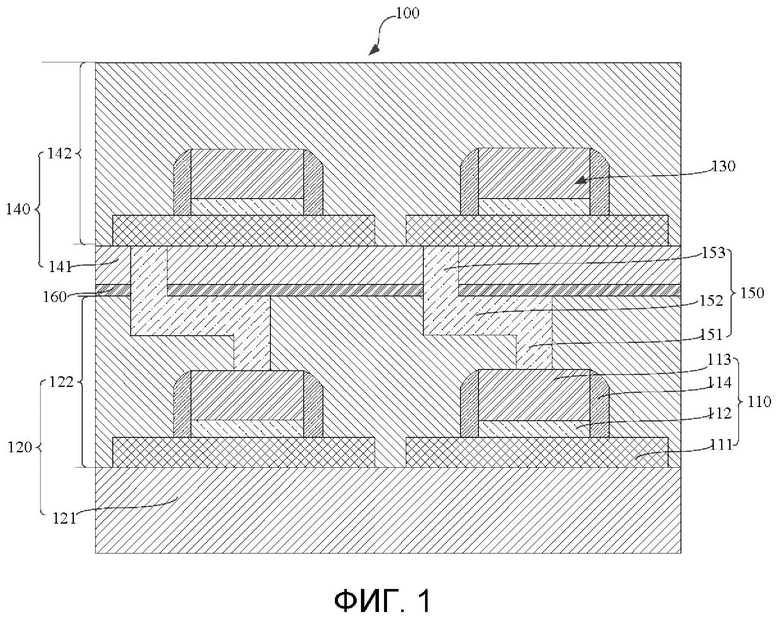

На фиг. 1 схематически показана схема конструкции ячейки памяти согласно варианту реализации 1 настоящего изобретения.

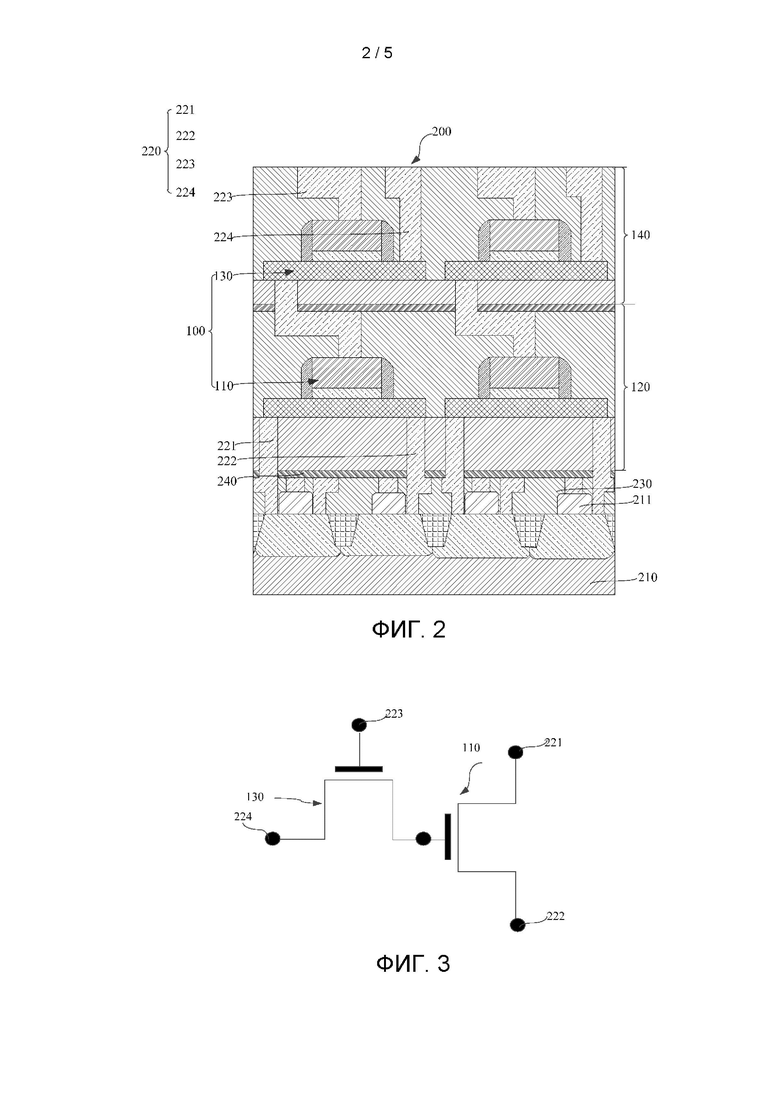

На фиг. 2 схематически показана схема конструкции запоминающего устройства в соответствии с вариантом реализации 2 настоящего изобретения;

На фиг. 3 показана принципиальная электрическая схема запоминающего устройства согласно варианту реализации 2 настоящего изобретения;

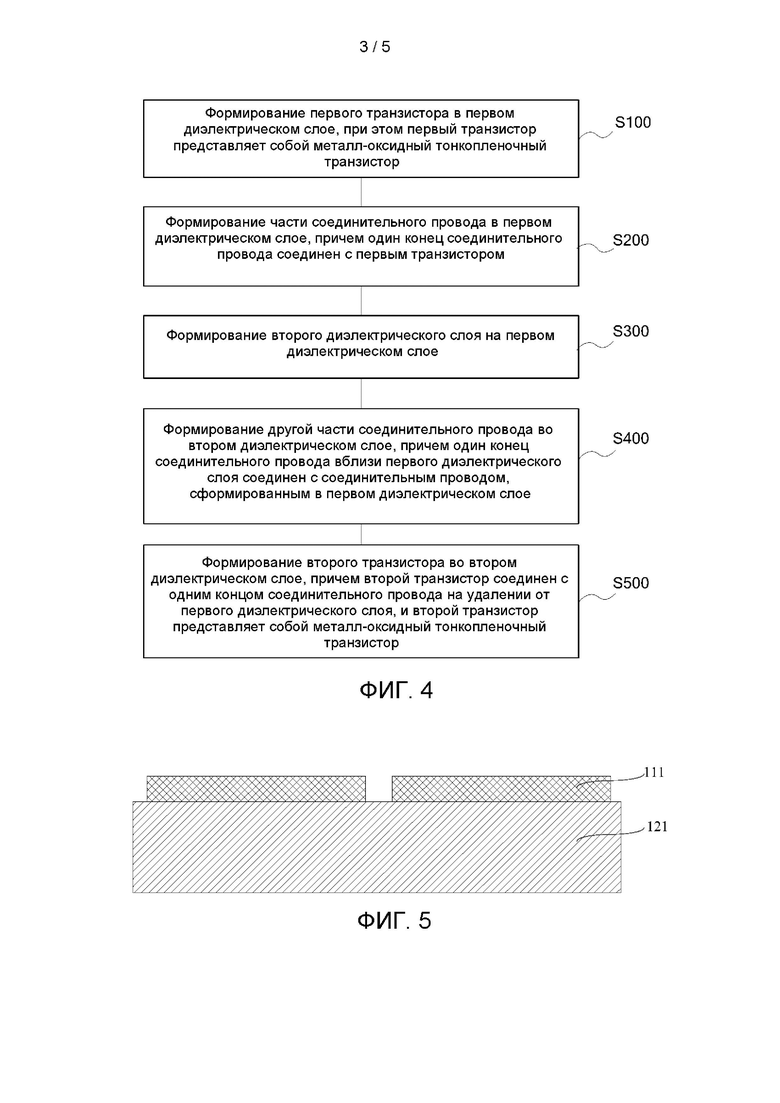

На фиг. 4 показана блок-схема способа изготовления ячейки памяти согласно варианту реализации 3 настоящего изобретения;

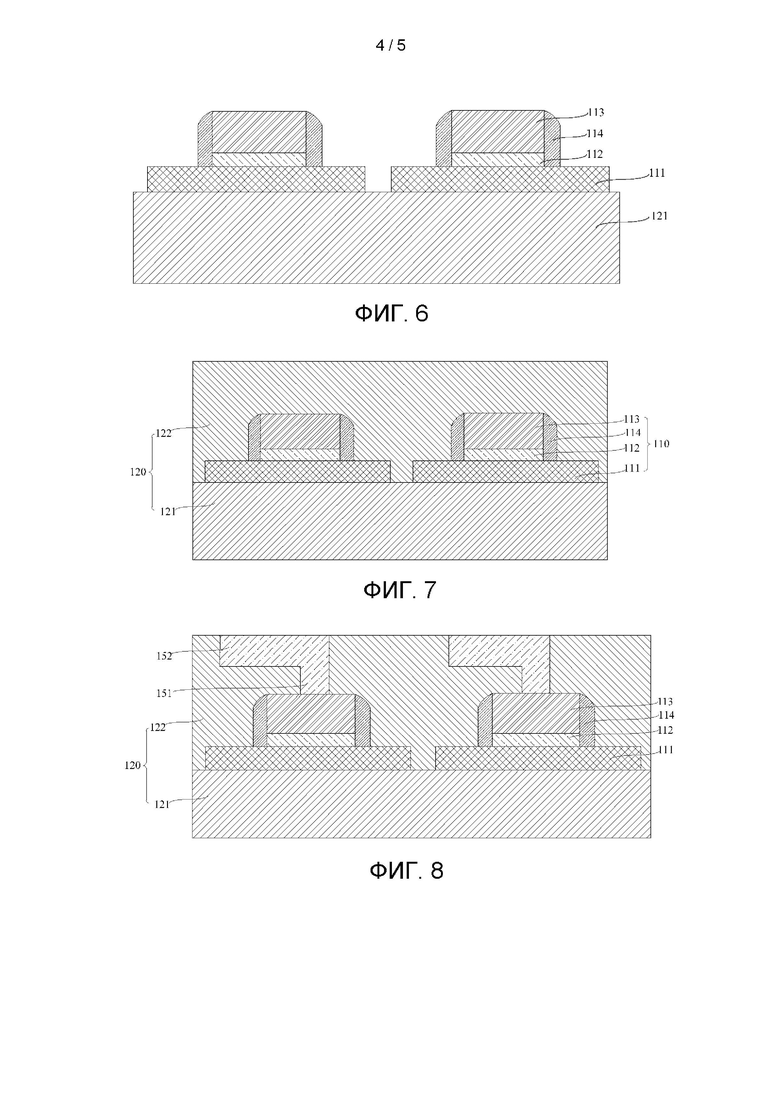

На фиг. 5 схематически показана схема конструкции активного слоя, образованного в способе изготовления ячейки памяти согласно варианту реализации 3 настоящего изобретения;

На фиг. 6 схематически показана схема конструкции первого транзистора, образованного в способе изготовления ячейки памяти в соответствии с вариантом реализации 3 настоящего изобретения;

На фиг. 7 схематически показана схема конструкции второго изолирующего слоя, образованного в способе изготовления ячейки памяти в соответствии с вариантом реализации 3 настоящего изобретения;

На фиг. 8 схематически показана схема конструкции первой контактной части и металлического провода, образованного в способе изготовления ячейки памяти в соответствии с вариантом реализации 3 настоящего изобретения;

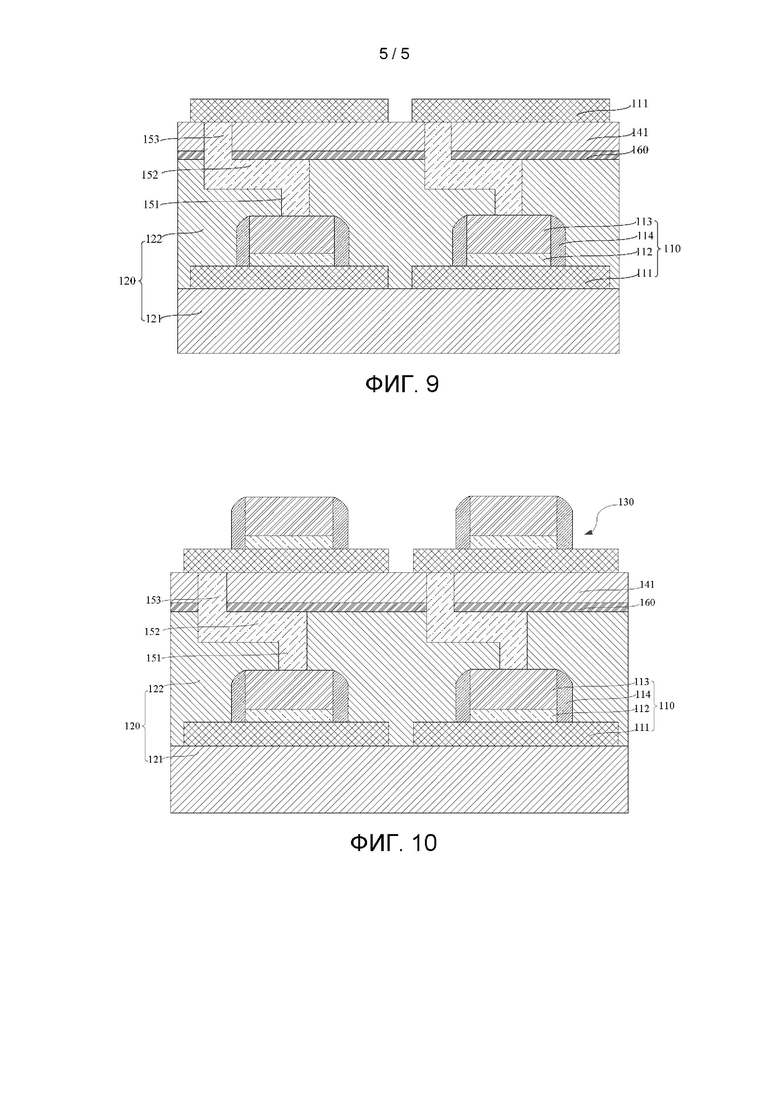

На фиг. 9 схематически показана схема конструкции второй контактной части и активного слоя, образованного в способе изготовления ячейки памяти согласно варианту реализации 3 настоящего изобретения; и

На фиг. 10 схематически показана схема конструкции второго транзистора, образованного в способе изготовления ячейки памяти в соответствии с вариантом реализации 3 настоящего изобретения.

Осуществление изобретения

Динамическое запоминающее устройство с произвольным доступом (DRAM), как правило, включает в себя множество повторяющихся ячеек памяти, которые расположены на расстоянии друг от друга в направлении, параллельном подложке. Каждая ячейка памяти включает в себя конденсаторы и транзисторы, так что запоминающее устройство имеет больший объем. По мере развития динамических запоминающих устройств с произвольным доступом в направлении интеграции в каждой ячейке памяти продолжают использовать один транзистор и один конденсатор (1Т1С, 1 Transistor 1 Capacitor). В частности, конденсаторы имеют ограничение по уменьшению размера, что затрудняет обеспечение объема хранения и времени удержания зарядов в ячейке памяти, в результате чего снижается производительность запоминающего устройства.

На основании вышеуказанных технических проблем, в вариантах реализации настоящего изобретения предложена ячейка памяти и способ ее изготовления, запоминающее устройство и способ его изготовления. Ячейка памяти включает в себя первый транзистор и второй транзистор, которые уложены в стопу. Паразитная емкость в первом транзисторе или во втором транзисторе используется в качестве элемента памяти для замены конденсатора в соответствующем уровне техники таким образом, что объем, занимаемый ячейками памяти, может быть уменьшен, чтобы улучшить встраивание ячейки памяти и обеспечить развитие ячеек памяти в направлении встраивания.

Кроме того, первый транзистор и второй транзистор оба являются метал-оксидными тонкопленочными транзисторами, так что запоминающее устройство может иметь более длительное время удержания заряда, чтобы улучшить производительность запоминающего устройства при уменьшении объема запоминающего устройства.

Чтобы сделать более понятными цели, признаки и преимущества вариантов реализации настоящего изобретения, ниже четко и полностью описаны технические решения в вариантах реализации настоящего изобретения со ссылкой на чертежи в вариантах реализации настоящего изобретения. Очевидно, описанные варианты реализации представляют собой лишь некоторые, а не все варианты реализации настоящего изобретения. Все другие варианты реализации, полученные специалистами в данной области техники на основании вариантов реализации настоящего раскрытия без творческих усилий, подпадают под объем защиты настоящего изобретения.

Вариант реализации 1

Как показано на фиг. 1, этот вариант реализации настоящего изобретения обеспечивает ячейку 100 памяти. Ячейка 100 памяти может включать в себя первый диэлектрический слой 120 и второй диэлектрический слой 140, размещенные на первом диэлектрическом слое 120. Первый транзистор 110 размещен в первом диэлектрическом слое 120. Второй транзистор 130 размещен во втором диэлектрическом слое 140. Первый транзистор 110 соединен со вторым транзистором 130 с помощью соединительного провода 150, размещенного в первом диэлектрическом слое 120 и втором диэлектрическом слое 140. Первый транзистор 110 и второй транзистор 130 могут представлять собой металл-оксидные тонкопленочные транзисторы.

Ячейка 100 памяти, относящаяся к этому варианту реализации, включает в себя первый транзистор 110 и второй транзистор 130, которые уложены в стопу. Паразитная емкость в первом транзисторе 110 или втором транзисторе 130 используется в качестве элемента памяти для замены конденсатора в соответствующем уровне техники, так что объем, занимаемый ячейками 100 памяти, может быть уменьшен, чтобы гарантировать, что ячейки 100 памяти разработаны в направлении встраивания.

Кроме того, первый транзистор 110 и второй транзистор 130 представляют собой металл-оксидные тонкопленочные транзисторы, так что запоминающее устройство может иметь более длительное время удержания заряда, чтобы улучшить характеристики запоминающего устройства при уменьшении объема запоминающего устройства.

Следует отметить, что первый транзистор 110 и второй транзистор 130 имеют одну и ту же структуру. Для простоты описания первый транзистор 110 используется в качестве примера в следующем варианте реализации, и описана конструкция первого транзистора 110.

Например, со ссылкой на фиг. 1, первый транзистор 110 включает в себя активный слой 111, оксидный слой 112 затвора и затвор 113. Активный слой 111 включает в себя канальную область и исток и сток, которые соответственно расположены с двух сторон канальной области. Оксидный слой 112 затвора и затвор 113 наслоены последовательно на активный слой 111. Выступ затвора 113 на активном слое 111 охватывает канальную область таким образом, что существует перекрывающаяся область между затвором 113 и активным слоем 111. Таким образом, когда между активным слоем 111 и затвором 113 генерируется разность напряжений, между затвором 113 и активным слоем 111 образуется емкость. Емкость используется в качестве элемента памяти ячейки памяти для считывания или записи данных.

Кроме того, в данном варианте реализации материал активного слоя 111 может включать в себя оксид индия, галлия и цинка, который обладает более высокой подвижностью носителя, тем самым значительно улучшая чувствительность первого транзистора и снижая потребление энергии ячейкой памяти.

Материал оксидного слоя 112 затвора может включать в себя оксид кремния и/или оксид алюминия, а материал затвора 113 может включать в себя одно из группы, состоящей из нитрида титана, нитрида тантала, алюминия и вольфрама.

Следует отметить, что в этом варианте реализации проекция затвора 113 на активный слой 111 покрывает канальную область, что может быть понято как то, что площадь проекции затвора 113 на активный слой 111 равна площади канальной области или что площадь проекции затвора 113 на активный слой 111 меньше площади канальной области.

Кроме того, первый транзистор 110 дополнительно включает в себя защитный слой 114. Защитный слой 114 расположен по бокам затвора 113 и оксидного слоя 112 затвора. Защитный слой 114 размещен для электрической изоляции затвора от других элементов.

В некоторых вариантах реализации соединительный провод 150 может иметь один конец, соединенный с затвором первого транзистора 110, и другой конец, соединенный с истоком или стоком второго транзистора 130. Электрический сигнал на истоке или стоке второго транзистора 130 используют для управления первым транзистором 110 для открытия или закрытия.

Следует отметить, что форма соединительного провода 150 может быть произвольной. Например, соединительный провод 150 может представлять собой прямую линию или линию со сгибами.

Например, соединительный провод 150 включает в себя первую контактную часть 151, металлический провод 152 и вторую контактную часть 153. Первая контактная часть 151 и вторая контактная часть 153 проходят в вертикальном направлении. То есть, первая контактная часть 151 и вторая контактная часть 153 размещены в направлении, перпендикулярном первому диэлектрическому слою 120. Металлический провод 152 проходит в горизонтальном направлении. Один конец металлического провода 152 соединен с первой контактной частью 151. Один конец металлического провода 152 соединен со второй контактной частью 153.

Первая контактная часть 151 соединена с затвором 113 первого транзистора 110, а вторая контактная часть 153 соединена с истоком или стоком второго транзистора 130.

В этом варианте реализации один конец металлического провода 152 соединен с первой контактной частью 151, что можно понимать как то, что один конец металлического провода 152 соединен со средней частью первой контактной части 151 или что один конец металлического провода 152 соединен с одним концом первой контактной части 151.

Например, один конец металлического провода 152 может быть соединен с концом первой контактной части 151 на удалении от затвора 113 первого транзистора 110, а другой конец металлического провода 152 может быть соединен с концом второй контактной части 153 удалении от второго транзистора 130.

В некоторых вариантах реализации первая контактная часть 151 и металлический провод 152 могут быть расположены в первом диэлектрическом слое 120. Второй контактный участок 153 может быть расположен во втором диэлектрическом слое 140. Однако вышесказанное является просто способом размещения соединительного провода 150. Соединительный провод 150 может быть дополнительно полностью размещен в первом диэлектрическом слое 120 или во втором диэлектрическом слое 140.

Для предотвращения диффузии проводящих материалов в первом диэлектрическом слое 120 и втором диэлектрическом слое 140 друг в друга, между первым диэлектрическим слоем 120 и вторым диэлектрическим слоем 140 также размещен барьерный слой 160. Барьерный слой 160 расположен на металлическом проводе 152. Вторая контактная часть 153 проходит через барьерный слой 160 и соединена с металлическим проводом 152.

Материал барьерного слоя 160 может включать в себя изоляционный материал, такой как нитрид кремния.

Вариант реализации 2

Как показано на фиг. 2, этот вариант реализации настоящего изобретения дополнительно обеспечивает запоминающее устройство 200, которое включает в себя основу 210, ячейку 100 памяти и линию 220 передачи данных.

Основа 210 служит в качестве опорного элемента запоминающего устройства и выполнено с возможностью поддержки других компонентов, предусмотренных на нем. Основа 210 может быть выполнена из полупроводникового материала. Полупроводниковый материал может представлять собой одно или более из группы, состоящей из кремния, германия, кремний-германия и кремний-углерода.

Периферийная схема 211 размещена на поверхности основы 210 и может дополнительно включать в себя логическую схему или схему обработки.

Множество ячеек 100 памяти размещены над периферийной схемой 211, а ячейки 100 памяти соединены с периферийной схемой 211 с помощью линии 220 передачи данных.

По сравнению с техническим решением в соответствующем уровне техники, в котором периферийная схема размещена с двух сторон ячеек памяти в горизонтальном направлении, этот вариант реализации, в котором периферийная схема размещен ниже ячеек памяти, может уменьшить площадь ячеек памяти и обеспечить развитие памяти в направлении встраивания.

Кроме того, как показано на фиг. 2, линия 220 передачи данных включает в себя линию 221 слов для считывания, линию 222 битов для считывания, линию 223 слов для записи и линию 224 битов для записи.

Линия 223 слов для записи и линия 224 битов для записи могут быть размещены во втором диэлектрическом слое 140. Линия 223 слов для записи проходит в первом направлении и соединена с затвором второго транзистора 130 в каждой из множества ячеек 100 памяти. Линия 224 битов для записи проходит во втором направлении и соединена с истоком или стоком второго транзистора 130 в каждой из множества ячеек 100 памяти, и соединение между линией битов для записи и истоком или стоком второго транзистора отличается от соединения между соединительным проводом 150 и истоком или стоком второго транзистора.

Другими словами, если соединительный провод 150 соединен с истоком второго транзистора 130, линия 224 битов для записи соединена со стоком второго транзистора 130.

Линия 221 слов для считывания и линия 222 битов для считывания могут быть размещены в первом диэлектрическом слое 120. Линия 221 слова для считывания проходит в третьем направлении и соединена с истоком или стоком первого транзистора 110 в каждой из множества ячеек 100 памяти. Линия 222 битов для считывания проходит в четвертом направлении и соединена с истоком или стоком первого транзистора 110 в каждой из множества ячеек 100 памяти, и соединение между линией битов для считывания и истоком или стоком первого транзистора отличается от соединения между линией слов для считывания и истоком или стоком первого транзистора.

Другими словами, если линия 221 слов для считывания соединена с истоком первого транзистора 110, то линия 222 битов для считывания соответственно соединена со стоком первого транзистора 110.

Проекция первого направления и проекция второго направления на поверхность, параллельную или перпендикулярную основе, образуют первый угол, проекция третьего направления и проекция четвертого направления на поверхность, параллельную или перпендикулярную основе, образуют второй угол, при этом ни первый угол, ни второй угол не равны нулю. То есть линия слов для записи и линия битов для записи размещены с образованием пересечения, и линия слов для считывания и линия битов для считывания также размещены с образованием пересечения.

Как показано на фиг. 3, при применении к линии 223 слов для записи может быть использовано высокое напряжение для управления затвором второго транзистора 130 с целью открытия, а разность напряжений генерируется между истоком и стоком второго транзистора 130 для реализации проводимости между истоком и стоком второго транзистора. Напряжение на линии 224 битов для записи работает на затворе первого транзистора 110 для записи данных на линии 224 битов для записи в первый транзистор.

При необходимости считывания данных в первом транзисторе происходит открытие затвора первого транзистора 110, так что открывается исток и сток первого транзистора. В этом случае данные в первом транзисторе 110 передаются в периферийную схему 211 посредством использования строки 222 битов для считывания, а периферийная схема 211 обрабатывает данные для реализации функции считывания запоминающего устройства.

В некоторых вариантах реализации множество ячеек 100 памяти расположены в направлении, параллельном основе 210, с образованием горизонтального массива, то есть множество ячеек 100 памяти размещены последовательно в горизонтальном направлении. Кроме того, множество ячеек 100 памяти уложены в стопу в направлении, перпендикулярном основе 210, с образованием вертикального массива. Таким образом, в этом варианте реализации может быть уменьшено количество ячеек 100 памяти, которые расположены последовательно в горизонтальном направлении, может быть уменьшена область, занимаемая множеством ячеек памяти, и может быть улучшено встраивание ячеек памяти, чтобы гарантировать, что запоминающее устройство развивается в направлении встраивания.

Кроме того, по сравнению с техническим решением в соответствующей области техники, в котором множество ячеек памяти расположены в горизонтальном направлении, множество ячеек 100 памяти уложены в стопу в направлении, перпендикулярном основе 210, с образованием вертикального массива, таким образом, что высота запоминающего устройства увеличивается, чтобы уменьшить ширину запоминающего устройства в горизонтальном направлении, тем самым уменьшая объем запоминающего устройства и улучшая встраивание ячеек памяти.

В некоторых вариантах реализации на основе 210 размещен периферийный диэлектрический слой 230. Периферийный диэлектрический слой 230 покрывает периферийную схему 211 для электрической изоляции ячеек в периферийной схеме 211.

Материал периферийного диэлектрического слоя 230 может включать в себя нитрид кремния.

Кроме того, между периферийным диэлектрическим слоем 230 и первым диэлектрическим слоем 120 ячейки 100 памяти также размещен периферийный барьерный слой 240. Благодаря такому размещению предотвращается воздействие проводящего материала в первом диэлектрическом слое на производительность периферийной схемы.

Когда периферийный барьерный слой 240 размещен между периферийным диэлектрическим слоем 230 и первым диэлектрическим слоем 120, линия 220 передачи данных должна проходить через периферийный барьерный слой 240 и периферийный диэлектрический слой 230, а затем соединяться с периферийной схемой 211.

Вариант реализации 3

Как показано на фиг. 4, в данном варианте реализации настоящего изобретения дополнительно предложен способ изготовления ячейки памяти, включающий в себя:

Этап S100: формируют первый транзистор в первом диэлектрическом слое, причем первый транзистор представляет собой металл-оксидный тонкопленочный транзистор.

Первый диэлектрический слой 120 может быть использован в качестве несущего корпуса первого транзистора 110 или изолирующей среды между первым транзистором 110 и другим элементом. Материал первого диэлектрического слоя 120 может включать в себя оксид кремния или нитрид кремния.

Первый транзистор 110 может быть изготовлен, например, следующим образом:

Этап a: обеспечивают первый изолирующий слой.

Следует отметить, что первый изолирующий слой 121 является частью первого диэлектрического слоя 120.

Этап b: формируют активный слой на первом изолирующем слое, причем материал активного слоя включает в себя оксид индия, галлия и цинка.

Например, как показано на фиг. 5, активный слой 111 может быть образован на первом изолирующем слое 121 с использованием процесса осаждения, который может быть одним из процесса физического осаждения из паровой фазы, процесса химического осаждения из паровой фазы или процесса атомно-слоевого осаждения.

Этап c: формируют канальную область в активном слое и исток и сток, соответственно, расположенные с двух сторон канальной области.

На этом этапе на активном слое 111 может быть образован слой фоторезиста, а затем нанесен узор для образования в нем отверстия. Отверстие может открывать часть активного слоя 111. Затем легированные ионы вводят в отверстие с использованием процесса ионной имплантации с образованием истока в активном слое 111.

В ходе вышеупомянутого процесса в активном слое 111 также образуется сток.

Этап d: формируют оксидный слой затвора на активном слое, причем длина оксидного слоя затвора меньше, чем длина активного слоя.

Оксид кремния или оксид алюминия осаждается определенной толщиной на активный слой 111 посредством процесса осаждения. Оксид кремния или оксид алюминия образуют оксидный слой 112 затвора.

Этап e: формируют затвор на оксидном слое затвора, при этом проекция затвора на активный слой покрывает канальную область.

Процесс осаждения используют непрерывно для формирования затвора 113 на оксидном слое 112 затвора. Материал затвора 113 может быть одним из группы, состоящей из нитрида титана, нитрида тантала, алюминия и вольфрама.

Этап f: формируют защитный слой на активном слое, причем защитный слой охватывает стороны затвора и оксидного слоя затвора, а структура защитных слоев показана на фиг. 6.

Начальные защитные слои могут быть образованы на активном слое посредством процесса осаждения. Исходные защитные слои покрывают боковые поверхности оксидного слоя затвора и верхнюю поверхность и боковые поверхности затвора. Затем травильный газ или травильный раствор используют для удаления исходного защитного слоя на верхней поверхности затвора, а исходные защитные слои на боковых поверхностях затвора и оксидных слоев затвора удерживают для формирования защитных слоев 116.

Этап g: формируют второй изолирующий слой, покрывающий активный слой, оксидный слой затвора, затвор и защитный слой на первом изолирующем слое, причем второй изолирующий слой и первый изолирующий слой образуют первый диэлектрический слой, а структура первого изолирующего слоя показана на фиг. 7.

Этап S200: формируют часть соединительного провода в первом диэлектрическом слое, причем один конец соединительного провода соединен с первым транзистором.

Например, как показано на фиг. 8, первая контактная часть 151 и металлический провод 152, соединенный с первой контактной частью 151, сформированы во втором изолирующем слое 122. Первая контактная часть 151 проходит в вертикальном направлении и соединена с затвором 113 первого транзистора 110. Металлический провод 152 проходит в горизонтальном направлении. Первая контактная часть 151 и металлический провод 152 образуют часть соединительного провода.

На этом этапе первую контактную часть 151 и металлический провод 152 формируют с помощью процесса двойной инкрустации или могут быть сформированы с использованием процесса двойной инкрустации дважды.

Следует отметить, что в этом варианте реализации один конец соединительного провода может быть понят как один конец первой контактной части на удалении от металлического провода.

Этап S300: формируют второй диэлектрический слой на первом диэлектрическом слое.

Например, барьерный слой 160 может быть образован на первом диэлектрическом слое 120, то есть барьерный слой 160 может быть образован первым на втором изолирующем слое 122. Барьерный слой используют для предотвращения диффузии проводящих материалов в первом диэлектрическом слое и втором диэлектрическом слое друг в друга.

Материалы второго диэлектрического слоя и первого диэлектрического слоя могут быть одинаковыми и оба содержат оксид кремния. Второй диэлектрический слой 140 может включать в себя третий изолирующий слой 141 и четвертый изолирующий слой 142, которые последовательно уложены в стопу. Третий изолирующий слой 141 размещен на барьерном слое 160.

Этап S400: формируют другую часть соединительного провода во втором диэлектрическом слое, причем один конец соединительного провода вблизи первого диэлектрического слоя соединен с соединительным проводом, сформированным в первом диэлектрическом слое.

Например, заполненная канавка может быть образована во втором диэлектрическом слое и обнажает часть металлического провода 152. Затем в заполненной канавке посредством процесса осаждения формируют токопроводящий материал. Проводящий материал образует вторую контактную часть 153. Вторая контактная часть 153 соединена с металлическим проводом 152 таким образом, что первая контактная часть 151, вторая контактная часть 153 и металлический провод 152 образуют соединительный провод.

Этап S500: формируют второй транзистор во втором диэлектрическом слое, причем второй транзистор соединен с одним концом соединительного провода на удалении от первого диэлектрического слоя, и второй транзистор представляет собой металл-оксидный тонкопленочный транзистор.

Например, как показано на фиг. 9, третий изолирующий слой 141 образован на первом диэлектрическом слое 120.

После формирования третьего изолирующего слоя 141 активный слой 111 может быть образован на третьем изолирующем слое 141 посредством процесса осаждения. Материал активного слоя 111 включает оксид индия, галлия и цинка.

Следует отметить, что этап формирования активного слоя на третьем изолирующем слое является таким же, как и этап формирования активного слоя на первом изолирующем слое, который подробно не описан снова в этом варианте реализации.

Этапы c - f повторяются, чтобы сформировать второй транзистор 130 на третьем изолирующем слое 141, и структура второго транзистора показана на фиг. 10.

После формирования второго транзистора 130 на третьем изолирующем слое 141 формируют четвертый изолирующий слой 142, покрывающий активный слой, оксидный слой затвора, затвор и защитный слой. Четвертый изолирующий слой 142 и третий изолирующий слой 141 образуют второй диэлектрический слой 140.

В этом варианте реализации настоящего изобретения, на основе предшествующих этапов, формируются первый транзистор и второй транзистор, которые укладываются в стопу и используются в качестве элементов памяти ячеек памяти для замены конденсатора в соответствующем уровне техники, чтобы уменьшить объем, занимаемый ячейками памяти, улучшить встраивание ячейки памяти и обеспечить разработку ячеек памяти в направлении встраивания.

Вариант реализации 4

В этом варианте реализации настоящего изобретения предложен способ изготовления запоминающего устройства, включающий в себя:

Этап S10: Обеспечивают основу, причем периферийная схема размещена на поверхности основы.

На этом этапе периферийная схема может быть изготовлена с использованием способа в соответствующей области техники, который подробно не описан снова в этом варианте реализации.

После формирования периферийной схемы на основе может быть сформирован периферийный диэлектрический слой 230, покрывающий периферийную схему.

Затем на периферийном диэлектрическом слое 230 посредством процесса осаждения может быть сформирован периферийный барьерный слой 240.

Этап S20: формируют множество ячеек памяти последовательно на основе, причем множество ячеек памяти расположены в направлении, параллельном основе, с образованием горизонтального массива; и/или множество ячеек памяти уложены в стопу в направлении, перпендикулярном основе, с образованием вертикального массива.

Ячейки памяти получены с использованием способа изготовления ячейки памяти в вышеизложенном варианте реализации, который подробно не описан снова в данном варианте реализации.

Этап S30: формируют линию передачи данных, причем линия передачи данных выполнена с возможностью соединения периферийной схемы с ячейками памяти.

Следует отметить, что линия передачи данных может быть изготовлена в два этапа. Один этап может быть завершен до формирования первого транзистора. Другой этап может быть завершен после формирования второго транзистора.

Например, после формирования первого диэлектрического слоя 120 в первом диэлектрическом слое 120 может быть образована линия 221 слов для считывания и линия 222 битов для считывания, которые изолированы друг от друга. Линия 221 слов для считывания выполнена с возможностью соединения с истоком или стоком первого транзистора 110 в каждой из множества ячеек 100 памяти, линия 222 битов для считывания выполнена с возможностью соединения с истоком или стоком первого транзистора 110 в каждой из множества ячеек 100 памяти, при этом соединение между линией битов для считывания и истоком или стоком первого транзистора отличается от соединения между линией 221 слов для считывания и истоком или стоком первого транзистора.

После того, как линия 221 слов для считывания и линия 222 битов для считывания образованы непрерывно, первый транзистор 110 может быть сформирован в первом диэлектрическом слое 120, второй диэлектрический слой 140 может быть сформирован на первом диэлектрическом слое 120, и второй транзистор 130 может быть сформирован во втором диэлектрическом слое 140.

После формирования второго транзистора 130 линия 223 слов для записи и линия 224 битов для записи могут быть сформированы во втором диэлектрическом слое 140. Линия 223 слов для записи выполнена с возможностью соединения с затвором второго транзистора 130 в каждой из множества ячеек 100 памяти, линия 224 битов для записи выполнена с возможностью соединения с истоком или стоком второго транзистора 130 в каждой из множества ячеек 100 памяти, и соединение между линией битов для записи и истоком или стоком второго транзистора отличается от соединения между соединительным проводом 150 и истоком или стоком второго транзистора.

На этом этапе линия слов для считывания, линия битов для считывания, линия слов для записи и линия битов для записи могут быть изготовлены с помощью процесса двойной инкрустации.

По сравнению с техническим решением в соответствующей области техники, согласно которому множество ячеек памяти расположены последовательно в горизонтальном направлении, этот вариант реализации, в котором множество ячеек памяти уложены в стопу в вертикальном направлении, может уменьшить площадь, занимаемую ячейками памяти, уменьшить размер запоминающего устройства и улучшить встраивание ячеек памяти.

Кроме того, по сравнению с техническим решением в соответствующей области техники, в котором периферийная схема размещена вне массива ячеек памяти, этот вариант реализации, в котором периферийная схема размещена ниже ячеек памяти, может дополнительно уменьшить размер запоминающего устройства и улучшить интеграцию.

Варианты реализации или варианты осуществления настоящего описания описаны прогрессивным образом, и каждый вариант реализации фокусируется на отличиях от других вариантов реализации. Одинаковые или аналогичные части между вариантами реализации могут относиться друг к другу.

В описании этого описания изобретения описание со ссылкой на термин «один вариант осуществления», «некоторые варианты осуществления», «приведенный для примера вариант осуществления», «пример», «конкретный пример», «некоторые примеры» или тому подобное означает, что конкретный признак, структура, материал или характеристика, описанные в сочетании с вариантом (вариантами) осуществления или примером (примерами), включены по меньшей мере в один вариант осуществления или пример настоящего изобретения.

В этом описании изобретения схематическое выражение вышеуказанных терминов не обязательно относится к одному и тому же варианту осуществления или примеру. Кроме того, описанный конкретный признак, структура, материал или характеристика могут быть соответствующим образом объединены в любой один или более вариантов осуществления или примеров.

Наконец, следует отметить, что вышеприведенные варианты осуществления использованы только для объяснения технических решений настоящего изобретения, но не предназначены для ограничения настоящего изобретения. Несмотря на то, что настоящее изобретение подробно описано со ссылкой на предшествующие варианты реализации, специалистам в данной области техники должно быть понятно, что они все еще могут модифицировать технические решения, описанные в предшествующих вариантах реализации, или осуществлять эквивалентные замены некоторых или всех технических признаков в них. Модификации или замены не делают сущность соответствующих технических решений отличной от сущности и объема технических решений вариантов реализации настоящего изобретения.

Настоящее изобретение относится к ячейке памяти и способу ее изготовления, а также к запоминающему устройству и способу его изготовления и относится к области техники полупроводников. Ячейка памяти включает в себя первый диэлектрический слой и второй диэлектрический слой, которые уложены в стопу. В первом диэлектрическом слое размещен первый транзистор. Второй транзистор размещен во втором диэлектрическом слое. Первый диэлектрический слой соединен со вторым диэлектрическим слоем посредством соединительного провода. Паразитная емкость в первом транзисторе или втором транзисторе используется в качестве элемента памяти для замены конденсатора в соответствующем уровне техники, так что объем, занимаемый ячейками памяти, может быть уменьшен, чтобы гарантировать, что ячейки памяти развиты в направлении встраивания. Кроме того, первый транзистор и второй транзистор - оба являются метал-оксидными тонкопленочными транзисторами, так что запоминающее устройство может иметь более длительное время удержания заряда, чтобы улучшить производительность запоминающего устройства при уменьшении объема запоминающего устройства. 9 з.п. ф-лы, 10 ил.

1. Ячейка памяти, содержащая:

первый транзистор, расположенный в первом диэлектрическом слое;

второй транзистор, расположенный во втором диэлектрическом слое, причем второй диэлектрический слой расположен над первым диэлектрическим слоем; и

соединительный провод, расположенный в первом диэлектрическом слое и во втором диэлектрическом слое, причем один конец соединительного провода соединен с первым транзистором, а другой конец соединен со вторым транзистором; при этом

первый транзистор и второй транзистор представляют собой металл-оксидные тонкопленочные транзисторы,

а паразитная емкость в первом транзисторе или во втором транзисторе используется в качестве элемента памяти.

2. Ячейка памяти по п. 1, в которой каждый из первого транзистора и второго транзистора содержит:

активный слой, причем материал активного слоя содержит оксид индия, галлия и цинка, а активный слой содержит канальную область и исток и сток, которые соответственно расположены с двух сторон канальной области;

оксидный слой затвора, размещенный на активном слое; и

затвор, размещенный на оксидном слое затвора, причем проекция затвора на активный слой покрывает канальную область.

3. Ячейка памяти по п. 2, в которой каждый из первого транзистора и второго транзистора дополнительно содержит защитный слой, причем защитный слой расположен на сторонах затвора и оксидного слоя затвора.

4. Ячейка памяти по п. 2, в которой соединительный провод имеет один конец, соединенный с затвором первого транзистора, и другой конец, соединенный с истоком или стоком второго транзистора.

5. Ячейка памяти по п. 4, в которой соединительный провод содержит первую контактную часть и вторую контактную часть, которые размещены вертикально, и металлический провод, размещенный горизонтально; при этом

первая контактная часть соединена с затвором первого транзистора, вторая контактная часть соединена с истоком или стоком второго транзистора, и металлический провод соединяет первую контактную часть со второй контактной частью.

6. Ячейка памяти по п. 5, в которой первая контактная часть и металлический провод расположены в первом диэлектрическом слое, а вторая контактная часть расположена во втором диэлектрическом слое.

7. Ячейка памяти по п. 5 или 6, в которой барьерный слой размещен между первым диэлектрическим слоем и вторым диэлектрическим слоем, барьерный слой расположен на металлическом проводе, а вторая контактная часть соединена с металлическим проводом после прохождения через барьерный слой.

8. Ячейка памяти по любому из пп. 1-6, причем множество ячеек памяти составляют запоминающее устройство, также содержащее:

основу, причем периферийная схема размещена на поверхности основы;

линию передачи данных, выполненную с возможностью соединения периферийной схемы с множеством ячеек памяти,

причём множество ячеек памяти расположены над периферийной схемой.

9. Ячейка памяти по п. 8, в которой указанное множество ячеек памяти расположены в направлении, параллельном основе, с образованием горизонтального массива; и/или

множество ячеек памяти уложены в стопу в направлении, перпендикулярном основе, с образованием вертикального массива.

10. Ячейка памяти по п. 8, в которой линия передачи данных содержит линию слов для записи, линию битов для записи, линию слов для считывания и линию битов для считывания; при этом

линия слов для записи проходит в первом направлении и соединена с затвором второго транзистора в каждой из множества ячеек памяти, линия битов для записи проходит во втором направлении и соединена с истоком или стоком второго транзистора в каждой из множества ячеек памяти, при этом соединение между линией битов для записи и истоком или стоком второго транзистора отличается от соединения между соединительным проводом и истоком или стоком второго транзистора, линия слов для считывания проходит в третьем направлении и соединена с истоком или стоком первого транзистора в каждой из множества ячеек памяти, линия битов для считывания проходит в четвертом направлении и соединена с истоком или стоком первого транзистора в каждой из множества ячеек памяти, при этом соединение между линией битов для считывания и истоком или стоком первого транзистора отличается от соединения между линией слов для считывания и истоком или стоком первого транзистора.

| CN 104752432 A, 01.07.2015 | |||

| CN 111146200 A, 12.05.2020 | |||

| СПОСОБ ИЗГОТОВЛЕНИЯ ТРАНЗИСТОРА С НЕЗАВИСИМЫМ КОНТАКТОМ К ПОДЛОЖКЕ | 2020 |

|

RU2739861C1 |

| CN 112640089 A, 09.04.2021. | |||

Авторы

Даты

2023-12-28—Публикация

2022-02-15—Подача