Изобретение относится к устройствам управления и может применяться в системах автоматизации технологическим оборудованием.

Известно устройство, содержащее входной блок, блок коммутации подключенный выходом к вычислительному блоку, выход которого связан с блоком оперативной памяти и выходным блоком, программный блок, выходы которого подключены, через командные и адресные шины к входам всех перечисленных выше блоков, генератор импульсов [1]

Недостатком данного устройства является большое число командных и адресных шин.

Наиболее близким по технической сущности является устройство, содержащее входной и выходной блоки, блоки оперативной памяти и синхронизации, адресные шины, генератор импульсов, связанный с блоком синхронизации, программный блок, блок коммутации, состоящий из трехвходового дешифратора, трех двухвходовых элементов И, элемента ИЛИ и элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и управляемой ячейки памяти, командные шины, соединяющие программный блок с соответствующими входами трехвходового дешифратора, элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и ячейки памяти [2]

К недостаткам этого устройства можно отнести относительно большое число командных шин.

Целью изобретения является сокращение линий связи между блоком коммутации и программным блоком.

Поставленная цель достигается тем, что в известное устройство для дистанционного программного управления электроприводными механизмами и сигнализацией, содержащее входной и выходной блоки, блок оперативной памяти, блок коммутации, блок синхронизации, программный блок и генератор импульсов, при этом блок синхронизации состоит из двух счетных триггеров, четырех элементов И и инвертора, вход которого подключен к выходу генератора импульсов, соединенному с входом первого счетного триггера и первыми входами первого и второго элементов И, вторые входы которых подключены к прямому и инверсному выходам первого счетного триггера, выход инвертора подключен к первому входу второго счетного триггера и к первому входу четвертого элемента И, соединенного вторым входом с выходом второго счетного триггера, а выходом с первым входом третьего элемента И, второй вход и выход которого подключены соответственно к инверсному выходу первого счетного триггера и к второму входу второго счетного триггера, выход первого элемента И соединен с входом программного блока, блок коммутации содержит дешифратор, три элемента И, элемент ИЛИ, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и ячейку памяти, при этом в блоке коммутации первый и второй выходы дешифратора подключены к первым входам первого и второго элементов И, подключенных выходами через элемент ИЛИ к первому входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с вторым входом третьего элемента И, первый вход которого подключен к выходу четвертого элемента И блока синхронизации, а выход к управляющему входу ячейки памяти, выход которой подключен к информационным входам блока оперативной памяти и выходного блока, тактовые входы которых подключены к выходу второго элемента И блока синхронизации, а их управляющие входы соединены соответственно с третьим и четвертым выходами дешифратора, выход блока оперативной памяти подключен к второму входу второго элемента И блока коммутации, второй вход первого элемента И которого соединен с выходом входного блока, группа информационных входов которого является группой информационных входов устройства, а группы адресных входов входного и выходного блоков и блока оперативной памяти подключены к первой группе выходов программного блока, в блок коммутации введен блок преобразования кода, четырехразрядный вход которого подключен к второй группе выходов программного блока, выходы разрядов с первого по третий блока преобразования кода соединены с соответствующими входами дешифратора, выход четвертого разряда соединен с вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, а выход пятого разряда с информационным входом ячейки памяти блока коммутации.

Изобретение поясняется фиг. 1 5.

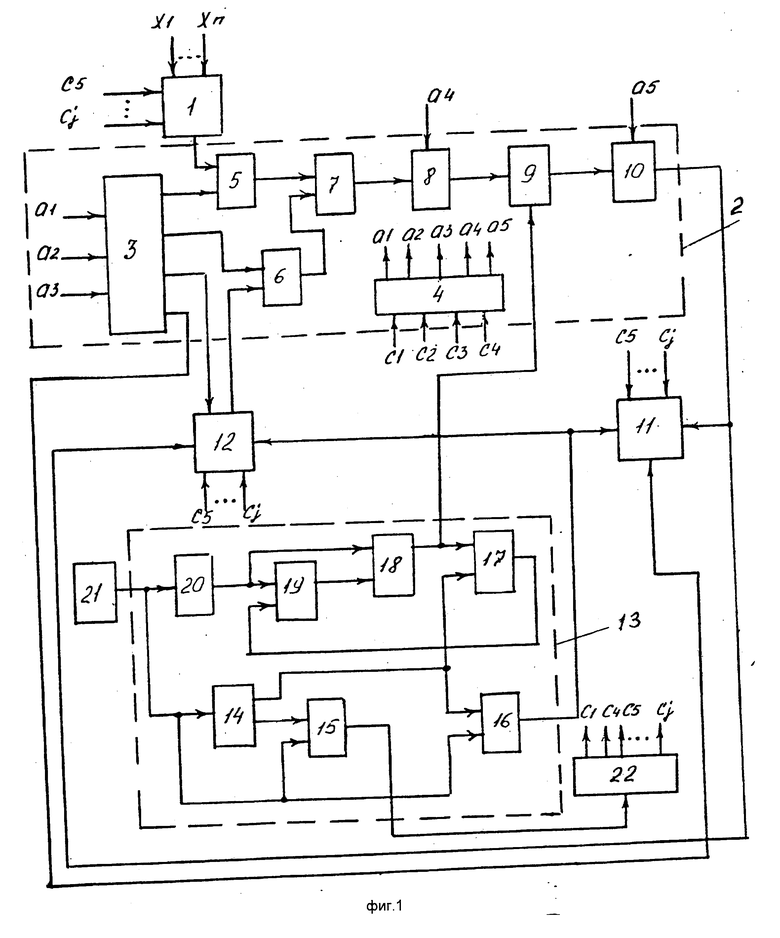

Предлагаемое устройство (фиг. 1) состоит из входного блока 1, входы которого подключены к адресным шинам и первичным датчикам Х1.Xn, а выход связан с блоком коммутации (БК) 2, содержащим дешифратор 3, связанный входами через а1, а2 и а3 с тремя выходами блока преобразования кода 4, а выходами соответственно с входами первого и второго элементов И 5 и И 6, выходы которых, через элемент ИЛИ 7 подключены к первому входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 8, второй вход которого связан с шиной а4, а выход через третий элемент И 9 связан с управляющим входом ячейки памяти 10, информационный вход которого соединен с шиной а5, а выход подключен к выходному блоку 11 и блоку оперативной памяти 12, связанным с выходом блока синхронизации 13, содержащего первый счетный триггер 14, подключенный прямым выходом к элементу И 15, а инверсным выходом к первым входам элементов И 16 и И 17, второй вход последнего подключен к выходу элемента И 18, входы которого связаны с прямым выходом второго счетного триггера 19 и с выходом инвертора 20, вход которого связан с генератором импульсов 21. Управляет работой всего устройства программный блок 22, связанный со всеми блоками устройства.

Работа блока синхронизации аналогична его работе в прототипе. Выход элемента И 16 обеспечивает запись информации в ячейки памяти блоков 12, 13 во второй четверти такта, выход элемента 18 обеспечивает запись информации в триггер 10 в третьей четверти. В случае сбоя синхроимпульсов относительно такта, элемент И 17 формирует импульс сброса, который обнулит счетный триггер 19 и положение синхроимпульса восстановится. Стрелками, направленными к элементам и блокам, помечены входы всех элементов и блоков.

С1.С4 командные сигналы, управляющие работой блока 2.

С5.Cj адресные сигналы, определяющие адреса ячеек памяти в блоках 11 и 12 или необходимого входа в блоке 1.

Входной блок 1 известной конструкции представлен на фиг. 2. Он содержит элементы согласования 23, элементы считывания 24, содержащих элементы И, элементы ИЛИ 25 и дешифратор 26.

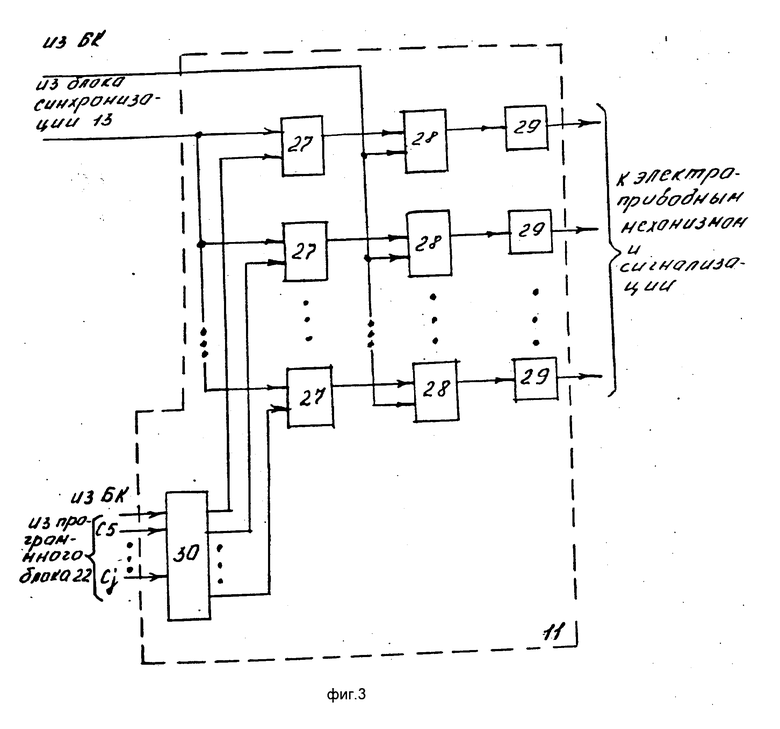

Выходной блок 11 (фиг. 3) состоит из элементов И 27, стандартных ячеек памяти 28, усилителей 29 и дешифратора 30.

Программный блок 22 известной конструкции содержит счетчик импульсов 31, дешифратор 32, распределяющий импульсы во времени и по направлению, стандартные ППЗУ 33, в которые записывается программа работы всего устройства (фиг. 4).

Блок оперативной памяти 12 (фиг. 5) содержит элементы 34 (элементы И), ячейки памяти 35, элементы считывания И 36, элемент ИЛИ 37, первый и второй дешифраторы 38. Работа блоков 1, 11, 22, 12 описана в прототипе и легко воспроизводится по схемам на фиг. 2 5 соответственно. В качестве ячейки памяти могут использоваться управляемые триггеры.

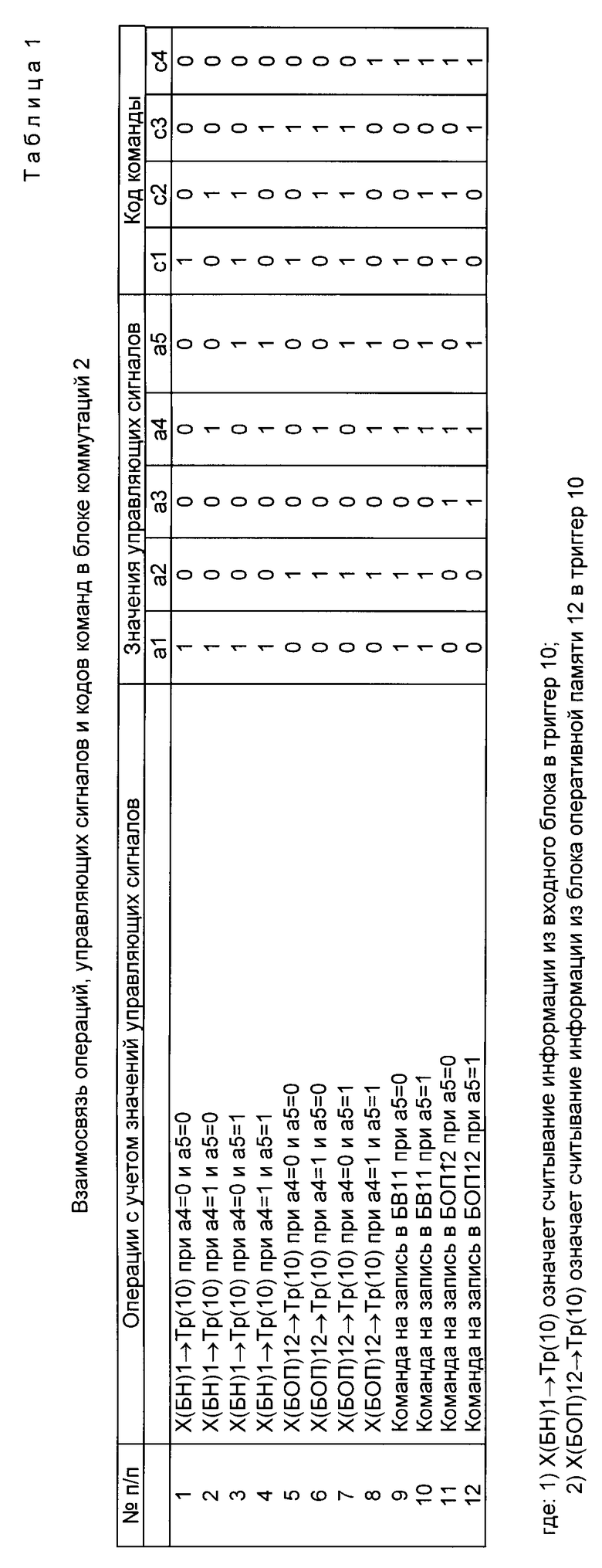

В таблице представлен перечень операций в блоке БК2 в соответствии с управляющими сигналами а1.а5 и кодами команд С1.С4. Принцип действия предлагаемого устройства рассмотрим на примере работы электропривода в зависимости от результата вычисления логической функции  , причем значения Х1, Х2 и Х3 поступают от датчиков, а значение Х4 было предварительно записано в блок оперативной памяти 12.

, причем значения Х1, Х2 и Х3 поступают от датчиков, а значение Х4 было предварительно записано в блок оперативной памяти 12.

Перед началом работы ячейка памяти (триггер) 10 устанавливается в исходное единичное состояние, т.е. на его выходе присутствует логическая единица.

Будем считать, что при сочетании входных сигналов на дешифраторе 3 а1, а2, а3 соответственно 100 активизируется первый верхний выход дешифратора 3, при 010 активизируется второй выход, при 110 активизируется третий выход, а при 001 активизируется четвертый нижний выход дешифратора 3. Оговоримся, что запись значения а5 происходит в триггер 10, когда на его управляющем входе находится логическая единица.

На первом такте необходимо в соответствии с таблицей подать из программного блока команды С1= 0, С2=1, С3=0, С4=0, обеспечивающие на выходе блока 4 следующие сигналы: а1=1, а2=0, а3=0, а4=1, а5=0 и путем адресных команд С5.Cj найти значение Х1 в блоке 1 и подать его на верхний вход элемента 5.

При этом значение Х1 под действием сигналов а1=1, а2=0, а3=0, а4=1 инвертируется и поступит через элементы 5, 7, 8 и 9 в третьей четверти первого такта на управляющий (тактовый) вход триггера 10. При этом, если Х1=1, то триггер 10 останется в прежнем состоянии, а если Х1=0, то триггер 10 перейдет в нулевое состояние. В соответствии с таблицей на втором такте аналогично под действием тех же команд С1.С4 значение Х2 при соответствующих информационных командах С5.Cj поступит на тактовый вход триггера 10 и так же при Х2=1 состояние триггера 10 остается в предыдущем состоянии, а если Х2=0, то предыдущее, например единичное, состояние триггера 10 перейдет в нулевое состояние, а если триггер 10 был в нулевом состоянии, то он так же в этом состоянии и останется. Переход состояния триггера 10 всегда происходит в третьей четверти такта. На третьем такте под действием команд С1=1, С2=1, С3= 0, С4= 1 во второй четверти третьего такта значение выхода триггера 10 запишется в блок оперативной памяти, т.к. активизируется третья сверху шина дешифратора 3 в соответствии с таблицей по сигналам а1.а5.

Запись произойдет в ячейку памяти с адресом, определяемым значением команд С5.Cj.

В третьей четверти третьего такта произойдет под действием команды а4=1 запись нулевого значения информации С5 в триггер 10. На четвертом такте под действием команд С1=1, С2=1, С3=0, С4=0 и значит сигналов а1=1, а2=0, а3=0, а4= 0, а5= 1 и соответственно значений команд С5.Cj входной сигнал Х3 в третьей четверти такта появится на управляющем входе триггера 10, и если Х3= 0, то состояние триггера 10 не изменится, а если Х3=1, то триггер 10 перейдет в единичное состояние.

На пятом такте под действием сигналов а1=0, а2=1, а3=0, а4=1, а5=1 (С1= 0, С2=0, С3=0, С4=1) активизируется вторая шина дешифратора 3 и значение Х4 из блока 12, определяемое адресом С5.Cj и значением а4=1, из блока 12 через элементы 6, 7 и 8 в третьей четверти такта появится на управляющем входе триггера 10. Если Х4= 0, то произойдет установка триггера 10 в новое единичное состояние.

Если Х4=1, то состояние триггера 10 останется прежним.

На шестом такте при значениях команд С1.С5 0110 и соответственно сигналов а1= 0, а2=1, а3=0, а4=1, а5=0 значение результата вычисления функции Х1•Х2, ранее записанное в блок оперативной памяти 12 через элементы 6, 7, 8 и 9, подается на тактовый вход триггера 10, и если Х1•Х2=1, то значение сигнала на выходе триггера 10 не меняется, т.к. на его тактовом входе имеется нулевой сигнал, а если Х1•Х2=0, то триггер 10 переключается в нулевое состояние.

Поэтому при Х1•Х2= 1, если значение функции, вычисленной на предыдущих тактах, т.е. Х3+Х4=1, то значение сигнала на входе триггера 10 равно 1, если Х3+Х4= 0, то на выходе триггера 10 имеется нулевой сигнал. На седьмом такте выходное значение триггера 10, т.е. результат вычисления функции  записывается в выходной блок по соответствующим командам и сигналам а1=0, а2=0, а3=1. При этом активизируется нижний выход дешифратора 3, который и разрешает запись в ячейку памяти выходного блока 11 значение логического сигнала с выхода триггера 10.

записывается в выходной блок по соответствующим командам и сигналам а1=0, а2=0, а3=1. При этом активизируется нижний выход дешифратора 3, который и разрешает запись в ячейку памяти выходного блока 11 значение логического сигнала с выхода триггера 10.

Ячейка памяти соответствует адресу, код которого определяется адресными командами С5.Cj.

Как видно из примера, включение блока преобразования кода 4 в блок БК2 позволило сократить число программируемых командных шин, управляющих работой блока БК2 с 5 до 4 за счет того, что количество операций в соответствии с таблицей позволяет составить двоичные коды из четырех переменных.

Сокращение количества командных шин в блоке 22 приводит к сокращению проводных линий связи между блоками 4 и 22 и упрощению процесса программирования блока 22 при сохранении остальных параметров.

Изобретение относится к устройствам управления и может применяться в системах автоматизации технологическими линиями и оборудованием. Целью изобретения является сокращение линий связи между блоками и упрощение процесса программирования при использовании устройства. Эта цель достигается тем, что в устройство, содержащее входной и выходной блоки, блок оперативной памяти и генератор импульсов, связанный с блоком синхронизации, адресные и командные шины, программный блок и блок коммутации, состоящий из управляемой ячейки памяти, трех элементов И, элемента ИЛИ, элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и трехвходового дешифратора, связанного первым и вторым входами с первыми входами первого и второго элементов И, вторые входы которых подключены к выходам входного блока и блока оперативной памяти, а выходы элементов И соединены через элемент ИЛИ с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен через третий элемент И с управляющим входом ячейки памяти, в блок коммутации введен блок преобразования кода, имеющий четыре входа, соединенные через командные шины с программным блоком, и пять выходов, три из которых подключены к входам дешифратора, четвертый выход связан с элементом ИСКЛЮЧАЮЩЕЕ ИЛИ, а пятый выход с информационным входом ячейки памяти. При этом сокращается число линий связи между блоком программ и блоком коммутации устройства. 5 ил., 1 табл.

Устройство для дистанционного программного управления электроприводами и сигнализацией, содержащее входной и выходной блоки, блок оперативной памяти, блок коммутации, блок синхронизации, программный блок и генератор импульсов, при этом блок синхронизации состоит из двух счетных триггеров, четырех элементов И и инвертора, вход которого подключен к выходу генератора импульсов, соединенному с входом первого счетного триггера и с первыми входами первого и второго элементов И, вторые входы которых подключены соответственно к прямому и инверсному выходам первого счетного триггера, выход инвертора подключен к первому входу второго счетного триггера и к первому входу четвертого элемента И, соединенного вторым входом с выходом второго счетного триггера, а выходом с первым входом третьего элемента И, второй вход и выход которого подключены соответственно к инверсному выходу первого счетного триггера и к второму входу второго счетного триггера, выход первого элемента И соединен с входом программного блока, блок коммутации содержит дешифратор, три элемента И, элемент ИЛИ, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и ячейку памяти, при этом в блоке коммутации первый и второй выходы дешифратора подключены к первым входам первого и второго элементов И, подключенных выходами через элемент ИЛИ к первому входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с вторым входом третьего элемента И, первый вход которого подключен к выходу четвертого элемента И блока синхронизации, а выход к управляющему входу ячейки памяти, выход которой подключен к информационным входам блока оперативной памяти и выходного блока, тактовые входы которых подключены к выходу второго элемента И блока синхронизации, а их управляющие входы соединены соответственно с третьим и четвертым выходами дешифратора, выход блока оперативной памяти подключен к второму входу второго элемента И блока коммутации, второй вход первого элемента И которого соединен с выходом входного блока, группа информационных входов которого является группой информационных входов устройства, а группы адресных входов входного и выходного блоков и блока оперативной памяти подключены к первой группе выходов программного блока, отличающееся тем, что в блок коммутации введен блок преобразования кода, четырехразрядный вход которого подключен к второй группе выходов программного блока, выходы разрядов с первого по третий блока преобразования кода соединены с соответствующими входами дешифратора, выход четвертого разряда соединен с вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, а выход пятого разряда с информационным входом ячейки памяти блока коммутации.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для дистанционного программного управления сигнализацией и электроприводными механизмами | 1989 |

|

SU1652964A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для дистанционного программного управления сигнализацией и электропроводными механизмами | 1990 |

|

SU1801223A3 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1997-10-10—Публикация

1993-07-20—Подача