Изобретение относится к радиотехнике, в частности к цифровым устройствам, и предназначено для контроля и защиты выходов цифровых устройств от перегрузок по току, включая случаи короткого замыкания в линиях связи.

Необходимость защиты выходов цифровых устройств от сбоев в работе нагрузок возникла сразу же, как появилась возможность управления удаленными устройствами и передачи цифровых сигналов по линиям связи, в связи с чем попытки решения указанной задачи предпринимаются достаточно давно. При этом наиболее обоснованным представляется отключение выхода устройства от нагрузки при увеличении выходного тока сверх допустимого значения. Типичным примером реализации указанного принципа является схема (прототип) содержащая магистральный усилитель, элемент задержки, логический элемент И-НЕ и инвертор, при этом вход магистрального усилителя организован как логическая функция 2И, что позволяет один из входов использовать как сигнальный, а второй - как управляющий [А. с. СССР №434616. Опубл. в Б. И., 1974 г., №24]. Особенность схемы защиты состоит в том, что в случае уменьшения напряжения на выходе магистрального усилителя ниже уровня логического нуля при наличии на его сигнальном входе уровня логической единицы, на управляющий вход магистрального усилителя подается запрещающий уровень, и в результате на выходе усилителя устанавливается уровень логического нуля, чем обеспечивается защита выхода усилителя. В то же время, если напряжение на нагрузке уменьшится до величины не ниже порогового уровня логического нуля, то факт перегрузки однозначно определен не будет, по причине появления недопустимого (нелогического) уровня на входе инвертора. Кроме того, если на нагрузку извне будет подано напряжение близкое к питающему, то в микросхему потечет ток, который в аварийных ситуациях может достигать недопустимо больших значений и ограничиваться только внутренним сопротивлением открытого транзистора выходного каскада (под магистральным усилителем в нашем случае понимается цифровая микросхема с повышенной нагрузочной способностью) и, следовательно, вывести устройство из строя. Указанный алгоритм защиты от перегрузок оказывается эффективным только при коротком замыкании на общую шину, но не на шину питания с потенциалом отличным от нуля, что снижает эффективность и, следовательно, надежность защиты.

Технический результат, достигаемый при использовании настоящего изобретения, заключается в повышении эффективности защиты от перегрузок, причем независимо от характера их возникновения и проявления.

Технический результат (вариант 1) достигается тем, что в известную схему защиты от перегрузок выходов цифровых устройств, содержащую магистральный усилитель и элемент задержки, согласно изобретению введены дискриминатор, формирователь импульсов сброса и токоограничивающий резистор, а магистральный усилитель выполнен с возможностью перехода в высокоимпедансное состояние на выходе, сигнальный вход магистрального усилителя является входом схемы, управляющий вход магистрального усилителя соединен с выходом дискриминатора, первый вход которого через элемент задержки подключен ко входу схемы, а второй вход - к выходу схемы, к которому через токоограничивающий резистор подключен выход магистрального усилителя, вход сброса дискриминатора соединен с выходом формирователя импульсов сброса, вход которого соединен с выходом дискриминатора.

Технический результат (вариант 2) достигается тем, что в известную схему защиты от перегрузок выходов цифровых устройств, содержащую магистральный усилитель и элемент задержки, согласно изобретению введены дискриминатор и токоограничивающий резистор, а магистральный усилитель выполнен с возможностью перехода в высокоимпедансное состояние на выходе, сигнальный вход магистрального усилителя является входом схемы, управляющий вход магистрального усилителя соединен с выходом дискриминатора, первый вход которого через элемент задержки подключен ко входу схемы, а второй вход - к выходу схемы, к которому через токоограничивающий резистор подключен выход магистрального усилителя, вход сброса дискриминатора является входом принудительного сброса схемы.

Кроме того, для достижения технического результата дискриминатор содержит входной резистор, триггер Шмитта, логический элемент исключающее или, фильтр нижних частот и одновибратор с перезапуском, выход которого является выходом дискриминатора, первым и вторым входами которого являются соответственно первый вход элемента исключающее или и вход триггера Шмита, выход которого соединен со вторым входом элемента исключающее или, выход которого через фильтр нижних частот подключен к запускающему входу одновибратора, вход обнуления которого является входом сброса дискриминатора, второй вход которого через входной резистор соединен с общей шиной.

В другом варианте для достижения технического результата дискриминатор содержит входной резистор, триггер Шмита, логический элемент исключающее или, фильтр нижних частот и D-триггер, выход которого является выходом дискриминатора, первым и вторым входами которого являются соответственно первый вход элемента исключающее или и вход триггера Шмита, выход которого соединен со вторым входом элемента исключающее или, выход которого через фильтр нижних частот подключен к тактовому входу D-триггера, информационный вход которого является входом логической единицы, а вход обнуления является входом сброса дискриминатора, второй вход которого через входной резистор соединен с общей шиной.

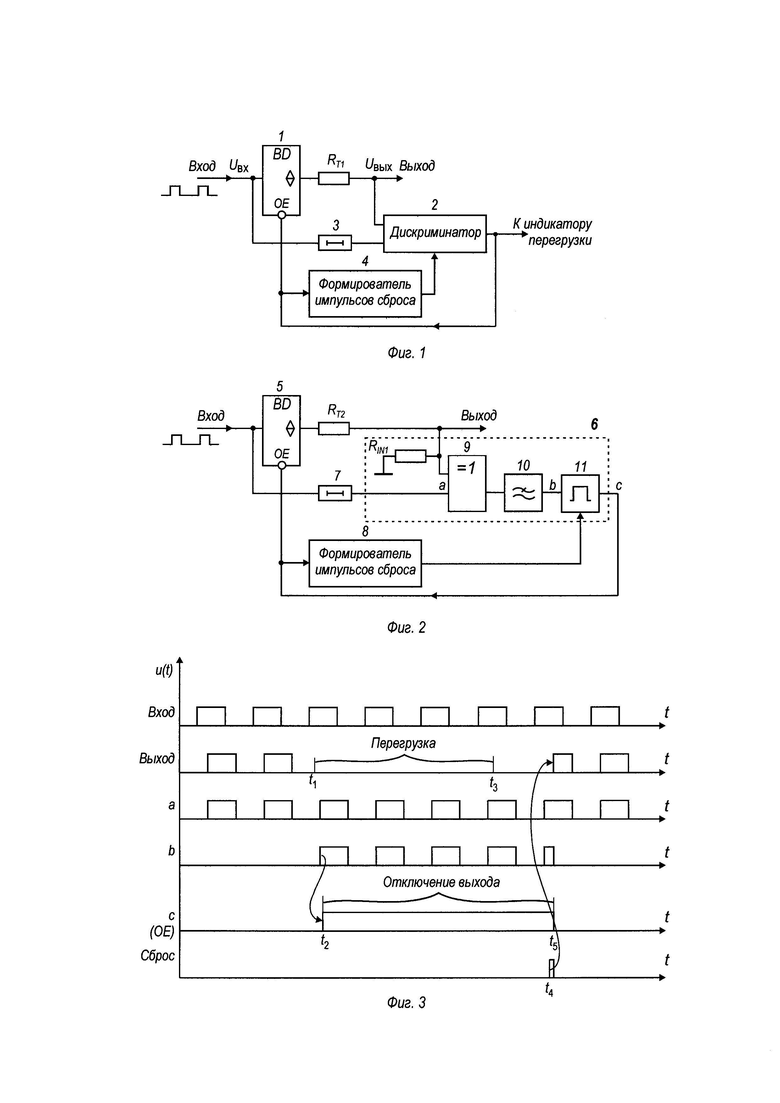

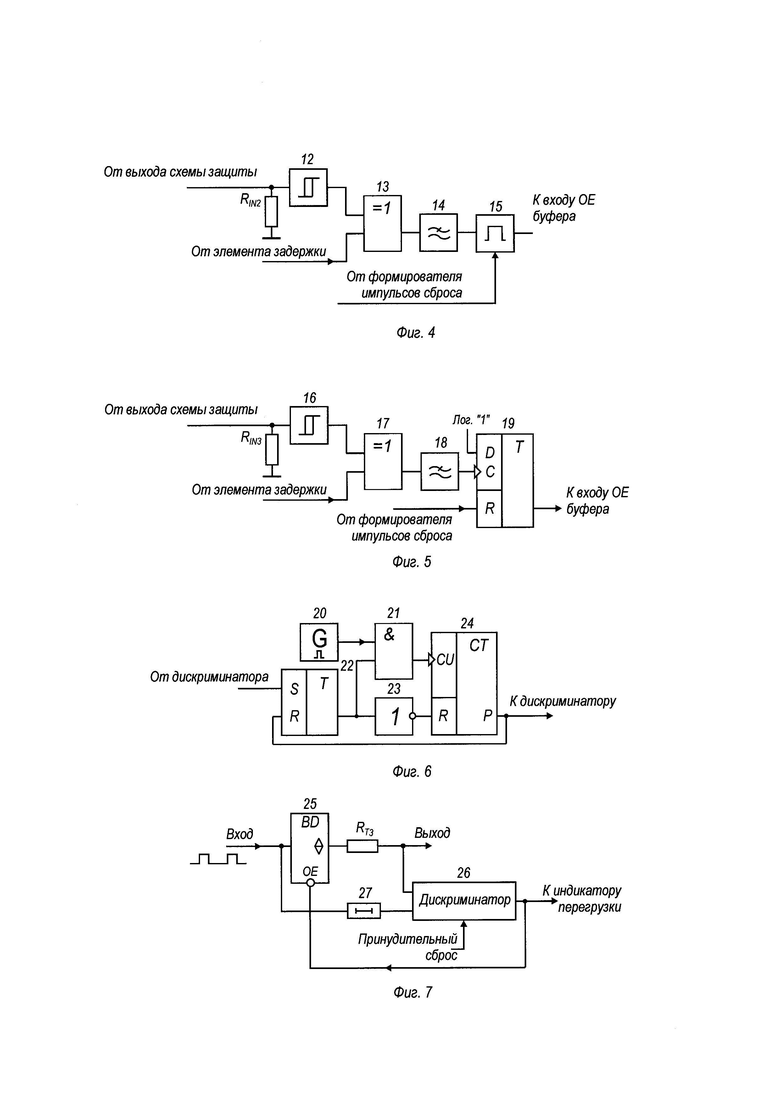

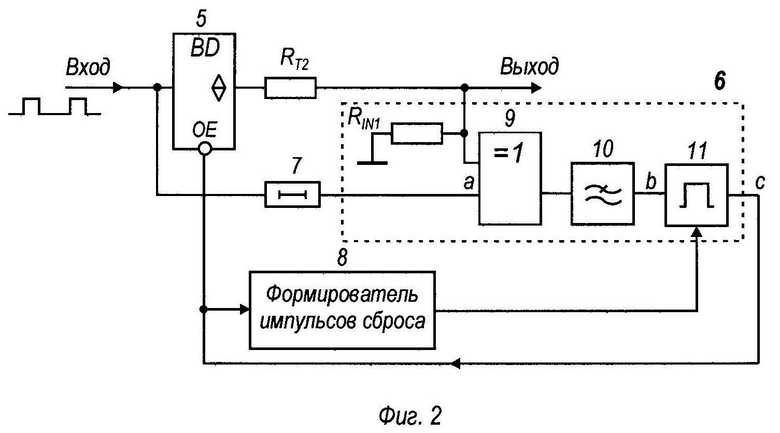

Сущность изобретения иллюстрируется чертежами. На фиг. 1 и фиг. 2 на функциональном уровне показаны схемы защиты от перегрузок, реализующие первый вариант. На фиг. 3 показана временная диаграмма, поясняющая принцип действия вышеупомянутых схем. На фиг. 4, 5 показаны различные варианты реализации амплитудного дискриминатора, а на фиг. 6 - пример формирователя импульсов сброса. На фиг. 7 показан второй вариант схемы защиты от перегрузок.

Функциональная схема по фиг. 1 содержит магистральный усилитель 1, дискриминатор 2, элемент 3 задержки, формирователь 4 импульсов сброса и токоограничивающий резистор RT1, сигнальный вход магистрального усилителя 1 является входом схемы, управляющий вход магистрального усилителя 1 соединен с выходом дискриминатора 2, первый вход которого через элемент 3 задержки подключен ко входу схемы, а второй вход

- к выходу схемы, к которому через токоограничивающий резистор RT1 подключен выход магистрального усилителя 1, вход сброса дискриминатора 2 соединен с выходом формирователя 4 импульсов сброса, вход которого соединен с выходом дискриминатора 2.

Функциональная схема по фиг. 2 содержит магистральный усилитель 5, дискриминатор 6, элемент 7 задержки, формирователь 8 импульсов сброса и токоограничивающий резистор RT2, сигнальный вход магистрального усилителя 5 является входом схемы, управляющий вход магистрального усилителя 5 соединен с выходом дискриминатора 6, первый вход которого через элемент 7 задержки подключен ко входу схемы, а второй вход

- к выходу схемы, к которому через токоограничивающий резистор RT2 подключен выход магистрального усилителя 5, вход сброса дискриминатора 6 соединен с выходом формирователя 8 импульсов сброса, вход которого соединен с выходом дискриминатора 6. В свою очередь, дискриминатор 6 состоит из логического элемента исключающее или 9, ФНЧ 10, одновибратора 11 с перезапуском и резистора RIN1.

Временная диаграмма по фиг. 3 включает в себя импульсы («Вход») на входе схемы, импульсы («Выход») на выходе схемы, импульсы («а») на нижнем по схеме входе элемента исключающее или 9, импульсы («b») на входе и импульс («с») соответственно на входе и выходе одновибратора 11, импульс («Сброс») на выходе формирователя 8.

Схема дискриминатора по фиг. 4 содержит резистор RIN2, триггер Шмитта 12, логический элемент исключающее или 13, ФНЧ 14 и одновибратор 15 с перезапуском, выход которого является выходом дискриминатора, первым и вторым входами которого являются соответственно первый вход элемента исключающее или 13 и вход триггера Шмитта 12, выход которого соединен со вторым входом элемента исключающее или 13, выход которого через ФНЧ 14 подключен к запускающему входу одновибратора 15, вход обнуления которого является входом сброса дискриминатора, второй вход которого через резистор RIN2 соединен с общей шиной.

Схема дискриминатора по фиг. 5 содержит резистор RIN3, триггер Шмита 16, логический элемент исключающее или 17, ФНЧ 18 и D-триггер 19, выход которого является выходом дискриминатора, первым и вторым входами которого являются соответственно первый вход элемента исключающее или 17 и вход триггера Шмитта 16, выход которого соединен со вторым входом элемента исключающее или 17, выход которого через ФНЧ 18 подключен к тактовому входу D-триггера 19, информационный вход которого является входом логической единицы, а вход обнуления является входом сброса дискриминатора, второй вход которого через резистор RIN3 соединен с общей шиной.

Формирователь импульсов сброса, схема которого показана на фиг.6, содержит генератор 20 тактовых импульсов, логический элемент И 21, триггер 22, инвертор 23 и счетчик 24, выход переноса которого является выходом формирователя, входом которого является установочный вход триггера 22, к выходу которого подключены объединенные первый вход элемента И 21 и вход инвертора 23, второй вход элемента И 21 соединен с выходом генератора 20 тактовых импульсов, а выход элемента И 21 соединен с суммирующим входом счетчика 24, вход обнуления которого соединен с выходом инвертора 23, вход сброса триггера 22 соединен с выходом формирователя.

Второй вариант схемы защиты от перегрузок (см. фиг. 7) содержит магистральный усилитель 25, дискриминатор 26, элемент 27 задержки и токоограничивающий резистор RT3, сигнальный вход магистрального усилителя 5 является входом схемы, управляющий вход магистрального усилителя 25 соединен с выходом дискриминатора 26, первый вход которого через элемент 27 задержки подключен ко входу схемы, а второй вход - к выходу схемы, к которому через токоограничивающий резистор RT3 подключен выход магистрального усилителя 25.

Принцип действия схемы защиты (см. фиг. 1) основан на постоянном сравнении уровней сигналов на входе Uвх и выходе Uвых магистрального усилителя 1, что осуществляется при помощи дискриминатора 2, и, в случае появления недопустимой разности уровней, переводе выхода магистрального усилителя 1 в состояние высокого импеданса.

Возможны два случая перегрузки выхода. В первом случае существенное уменьшение сопротивления нагрузки, подключенной между выходом и общей шиной, приводит к снижению уровня выходного сигнала Uвых при высоком логическом уровне на входе. Ситуация, характерная при коротком замыкании в линии, состоящей из сигнального и общего проводов. Второй случай - поступление на выход большого тока текущего от источника питания при логическом нуле на входе. В такой ситуации втекающий ток увеличивает выходное напряжение усилителя Uвых, что проявляется также как увеличение разности входного и выходного уровней. При этом дискриминатор 2 вырабатывает импульс отключения выхода усилителя вне зависимости от знака разности Uвых-Uвх. То есть, если выполняется условие Uвых≠Uвх, корректное в предположении, что Uвх и Uвых принимают значения логических уровней «0» и «1», а дискриминатор функционирует как сугубо логическое устройство.

После перевода выхода усилителя 1 в высокоимпедансное состояние на выходе дискриминатора 2 поддерживается запрещающий высокий логический уровень и, соответственно, на входе ОЕ магистрального усилителя 1, до тех пор, пока на управляющий вход дискриминатора 2 не поступит импульс сброса с выхода формирователя 4. Вышеуказанный высокий логический уровень также может быть использован для индикации перегрузки, например, световой.

Работу дискриминатора несложно понять, обращаясь к схеме по фиг. 2, на которой приведен пример конкретной реализации дискриминатора. При поступлении на вход схемы защиты последовательности импульсов и нормальном состоянии выхода на выходе элемента исключающее или 9 будет присутствовать уровень логического нуля. Это иллюстрируется начальным участком временных диаграмм, представленных на фиг. 3. При перегрузке выхода в момент времени t1 (средний участок временных диаграмм по фиг. 3), например, в случае короткого замыкания на общую шину, на выходе элемента исключающее или 9 появляются импульсы повторяющие входные. Указанные импульсы через ФНЧ 10 проходят на запускающий вход одновибратора 11, в ответ на что последний в момент t2 вырабатывает импульс, переводящий магистральный усилитель 5 в состояние высокого импеданса на выходе. Учитывая, что одновибратор 11 является устройством с перезапуском, поступающие на его вход импульсы («b») будут периодически его перезапускать, поддерживая таким образом на его выходе («с») высокий логический уровень, отключающий выход магистрального усилителя 5. После устранения перегрузки в момент времени t3 на выходе схемы защиты остается низкий логический уровень, так как соответствующий вход элемента исключающее или 9 связан через сопротивление RIN1 с общей шиной. Перевод выхода магистрального усилителя 5 в рабочее состояние осуществляется, при помощи появившегося в момент t4, импульса сброса на выходе формирователя 8. В результате, после завершения переходных процессов в одновибраторе 11 и усилителе 5, последний в момент t5 переходит в исходное состояние и процесс передачи импульсов в нагрузку возобновляется.

Элемент задержки, присутствующий в рассматриваемых схемах (см. фиг. 1, фиг. 2 и фиг. 7), необходим для получения на сигнальных входах дискриминатора импульсов в один момент времени и, следовательно, должен вносить задержку равную задержке в магистральном усилителе. На практике получить равные задержки невозможно, они будут несколько отличаться на некоторую величину Δτ, что приведет к появлению на выходе элемента исключающее или 9 узких импульсов длительностью Δτ в ситуации, когда на выходе элемента исключающее или 9 должен быть постоянный уровень логического нуля. Для подавления указанных импульсов введен ФНЧ 10. В отдельных случаях, когда одновибратор 11 обладает низким быстродействием, можно исключить ФНЧ, если есть достаточно оснований полагать, что длительность Ах паразитных импульсов будет недостаточной для запуска одновибратора.

Токоограничивающий резистор RT1 и аналогичный в других схемах (см. фиг. 1, фиг. 2 и фиг. 7) позволяет повысить эффективность процесса защиты, расширяя диапазон аварийных токов с одной стороны, а с другой стороны позволяет снизить риск повреждения усилителя 1 на интервале времени от начала перегрузки до момента перевода выходных транзисторов усилителя в закрытое состояние. На практике, если усилитель нагружен на протяженную линию с известным волновым сопротивлением, указанный резистор может одновременно выполнять и согласующую функцию. В этом случае его сопротивление должно быть меньше волнового сопротивления линии на величину выходного сопротивления магистрального усилителя. Что касается сопротивления резистора RIN1 (RIN2, RIN3), то его значение выбирают исходя из общих правил применения униполярных микросхем (предполагается, что схема реализована по КМОП-технологии), и оно может составлять десятки и сотни килоом, для получения уровня логического нуля при отключенном выходе усилителя 1.

Вышерассмотренное является упрощением, позволяющим описать лишь частный случай, когда напряжение Uвых падает ниже порога логического нуля элемента исключающее или 9. В реальности же напряжение на нагрузке в случае перегрузки может понизиться, оставаясь выше уровня логического нуля, но ниже уровня логической единицы. По этой причине во избежание появления «нелогических» уровней на входе элемента исключающее или 9 целесообразно обеспечить нелинейное преобразование уровня, например, путем использования триггера Шмитта, как показано на схеме дискриминатора по фиг. 4. Такая схема исключает появление промежуточных «нелогических» уровней и, в частности, позволяет при снижении напряжения Uвых в случае возрастания выходного тока обеспечить сохранение уровня логической единицы на входе элемента исключающие или 13 до падения Uвых ниже порога отпускания (отключения) триггера. В остальном принцип действия дискриминатора не отличается от представленного на фиг. 2.

Особенность схемы защиты с дискриминатором 6, содержащим одновибратор, состоит в том, что схема может вернуться в исходный режим не только по импульсу сброса, но и самостоятельно при снятии входных импульсов, так как установившийся при этом на выходе элемента исключающее или 9 низкий логический уровень исключает перезапуск одновибратора 11. В этом случае пауза между импульсами должна превышать длительность импульса на выходе одновибратора.

Показанный на фиг. 5 вариант реализации дискриминатора отличается от пока-заннных на фиг. 2 и 4, тем, что одновибратор заменен на D-триггер, который переходит в состояние высокого логического уровня на выходе по переднему фронту импульса, следующего через ФНЧ 18 с выхода элемента исключающее или 17. Это позволяет отказаться от внешних времязадающих цепей, необходимых для работы одновибратора и упростить устройство. Однако такое техническое решение не позволяет возвращать схему защиты в исходное состояние после срабатывания путем снятия входных импульсов.

Частота появления импульсов сброса, необходимых для возврата схемы защиты в исходное состояние, определяется требованиями предъявляемыми к скорости восстановления после нормализации тока в нагрузке. Кроме того, должны учитываться еще и особенности используемых нагрузок, например, наличие повторяющихся кратковременных перегрузок, возможность самовосстановления и др. По сути частота следования импульсов сброса является частотой проверки состояния нагрузки (линии) после срабатывания защиты. Примером построения формирователя импульсов сброса является устройство (см. фиг. 6), в основе которого лежат генератор 20 тактовых импульсов и суммирующий счетчик 24, с выхода переноса которого снимается импульс сброса. Счетчик запускается высоким логическим уровнем, поступающим с выхода дискриминатора (см. фиг. 1) и работает в циклическом режиме в течение времени действия указанного разрешающего уровня, непосредственно поступающего на S-вход триггера 22 Частота следования импульсов сброса (импульсов переноса) зависит как от информационной емкости счетчика 24, так и от частоты генератора 20.

Схема защиты может быть упрощена без ущерба для эффективности ее функционирования за счет исключения формирователя импульсов (см. фиг. 7). Такое решение предполагает наличие внешних цепей принудительного сброса защиты при ее срабатывании, например, по сигналу индикатора перегрузки. В остальном принцип действия схемы не отличается от вышерассмотренных.

Изобретение относится к радиотехнике, в частности к цифровым устройствам. Технический результат: повышение эффективности защиты от перегрузок в случае существенного уменьшения сопротивления нагрузки, подключенной между выходом и общей шиной, и в случае поступления на выход большого тока, текущего от источника питания, при логическом нуле на входе. Такой результат обеспечивается за счет включения в схему защиты магистрального усилителя с возможностью перехода в высокоимпедансное состояние, дискриминатора, элемента задержки, а также за счет импульсов сброса для возврата в исходный режим. Особенностью схемы является наличие дискриминатора, служащего для выявления отличий между выходным и входным сигналами и вырабатывающего импульсы защиты, отключающие выход магистрального усилителя от нагрузки. 2 н. и 4 з.п. ф-лы, 7 ил.

1. Схема защиты от перегрузок выходов цифровых устройств, содержащая магистральный усилитель и элемент задержки, отличающаяся тем, что в нее введены дискриминатор, формирователь импульсов сброса и токоограничивающий резистор, а магистральный усилитель выполнен с возможностью перехода в высокоимпедансное состояние на выходе, сигнальный вход магистрального усилителя является входом схемы, управляющий вход магистрального усилителя соединен с выходом дискриминатора, первый вход которого через элемент задержки подключен ко входу схемы, а второй вход - к выходу схемы, к которому через токоограничивающий резистор подключен выход магистрального усилителя, вход сброса дискриминатора соединен с выходом формирователя импульсов сброса, вход которого соединен с выходом дискриминатора.

2. Схема по п. 1, отличающаяся тем, что дискриминатор содержит входной резистор, триггер Шмитта, логический элемент исключающее или, фильтр нижних частот и одновибратор с перезапуском, выход которого является выходом дискриминатора, первым и вторым входами которого являются соответственно первый вход элемента исключающее или и вход триггера Шмита, выход которого соединен со вторым входом элемента исключающее или, выход которого через фильтр нижних частот подключен к запускающему входу одновибратора, вход обнуления которого является входом сброса дискриминатора, второй вход которого через входной резистор соединен с общей шиной.

3. Схема по п. 1, отличающаяся тем, что дискриминатор содержит входной резистор, триггер Шмита, логический элемент исключающее или, фильтр нижних частот и D-триггер, выход которого является выходом дискриминатора, первым и вторым входами которого являются соответственно первый вход элемента исключающее или и вход триггера Шмита, выход которого соединен со вторым входом элемента исключающее или, выход которого через фильтр нижних частот подключен к тактовому входу D-триггера, информационный вход которого является входом логической единицы, а вход обнуления является входом сброса дискриминатора, второй вход которого через входной резистор соединен с общей шиной.

4. Схема защиты от перегрузок выходов цифровых устройств, содержащая магистральный усилитель и элемент задержки, отличающаяся тем, что в нее введены дискриминатор и токоограничивающий резистор, а магистральный усилитель выполнен с возможностью перехода в высокоимпедансное состояние на выходе, сигнальный вход магистрального усилителя является входом схемы, управляющий вход магистрального усилителя соединен с выходом дискриминатора, первый вход которого через элемент задержки подключен ко входу схемы, а второй вход - к выходу схемы, к которому через токоограничивающий резистор подключен выход магистрального усилителя, вход сброса дискриминатора является входом принудительного сброса схемы.

5. Схема по п. 4, отличающаяся тем, что дискриминатор содержит входной резистор, триггер Шмитта, логический элемент исключающее или, фильтр нижних частот и одновибратор с перезапуском, выход которого является выходом дискриминатора, первым и вторым входами которого являются соответственно первый вход элемента исключающее или и вход триггера Шмита, выход которого соединен со вторым входом элемента исключающее или, выход которого через фильтр нижних частот подключен к запускающему входу одновибратора, вход обнуления которого является входом сброса дискриминатора, второй вход которого через входной резистор соединен с общей шиной.

6. Схема по п. 4, отличающаяся тем, что дискриминатор содержит входной резистор, триггер Шмита, логический элемент исключающее или, фильтр нижних частот и D-триггер, выход которого является выходом дискриминатора, первым и вторым входами которого являются соответственно первый вход элемента исключающее или и вход триггера Шмита, выход которого соединен со вторым входом элемента исключающее или, выход которого через фильтр нижних частот подключен к тактовому входу D-триггера, информационный вход которого является входом логической единицы, а вход обнуления является входом сброса дискриминатора, второй вход которого через входной резистор соединен с общей шиной.

| УСТРОЙСТВО ЗАЩИТЫ ВЫХОДНЫХ КАСКАДОВМАГИСТРАЛЬНОГО УСИЛИТЕЛЯ ОТ КОРОТКОГОЗАМЫКАНИЯ В ЛИНИИ | 1972 |

|

SU434616A1 |

| Устройство для контроля цифровых блоков | 1989 |

|

SU1762280A2 |

| МНОГОКАНАЛЬНАЯ ТЕЛЕМЕТРИЧЕСКАЯ СЕЙСМОРАЗВЕДОЧНАЯ СИСТЕМА | 1994 |

|

RU2107312C1 |

| US 4158866 A, 19.06.1979 | |||

| Генератор ускоряющего напряжения линейного индукционного ускорителя | 1977 |

|

SU600751A1 |

Авторы

Даты

2024-04-16—Публикация

2023-11-17—Подача