Область техники, к которой относится изобретение

[0001] Технология раскрытия относится к процессорным системам с использованием центрального процессора (CPU), также известного как "процессор", а более конкретно, к кэш-памяти в процессорной системе, используемой для того, чтобы сохранять или "кэшировать" копии информации в основной памяти для более быстрого доступа посредством процессора.

Уровень техники

[0002] Центральный процессор (CPU), также известный как "процессор", выполняет вычислительные задачи для широкого множества вариантов применения. Традиционный процессор включает в себя одно или более ядер процессора, также известных как "CPU-ядра". Процессор выполняет компьютерные программные инструкции ("инструкции"), также известные как "программные инструкции", которые получаются выборкой из памяти инструкций. Процессор выполняет полученные выборкой инструкции из памяти, чтобы выполнять операции на основе типа инструкций и операндов данных, и формирует результат. Результат может предоставляться в качестве ввода, который должен потребляться посредством другой инструкции и/или сохраняться в памяти данных в качестве данных. Память инструкций и память данных могут предоставляться в основной памяти в качестве части процессорной системы, которая включает в себя процессор. Память инструкций и память данных также могут предоставляться в форме кэш-памяти. Например, кэш-память данных включает в себя или "кэширует" меньшие копии данных, сохраненных в основной памяти, чтобы предоставлять процессору более быстрый доступ к данным. Система кэш-памяти включает в себя одну или более кэш-памятей, организованных в иерархии между процессором и основной памятью. Данные мигрируют между основной памятью и различными уровнями кэш-памяти на основе удачных обращений и неудачных обращений в кэш. Если процессор запрашивает данные, не сохраненные на любом из уровней кэш-памятей (т.е. неудачное обращение в кэш), данные извлекаются из основной памяти и сохраняются на уровнях кэш-памятей. Если выполняется последующий запрос на идентичные данные, приводящий к удачному обращению в кэш (т.е. данные запрашиваются до того, как данные вытесняются из уровней кэш-памяти), данные предоставляются из кэш-памяти в процессор, в противоположность необходимости повторно осуществлять выборку данных из основной памяти.

[0003] Данные, извлеченные из высокоуровневой кэш-памяти или основной памяти в качестве результата неудачного обращения в кэш в низкоуровневой кэш-памяти, временно сохраняются в выделенной структуре, известной как заполняющий буфер в низкоуровневой кэш-памяти. Заполняющий буфер также известен как регистр запоминания состояний неудачного обращения (MSHR). Заполняющий буфер кэш-памяти выступает в качестве области стадирования для входящих данных, которые должны сохраняться в кэш-памяти до тех пор, пока запись кэша в кэш-памяти не становится доступной для того, чтобы сохранять входящие данные. Кэш-память должна вытеснять существующую запись кэша в массиве данных кэш-памяти на основе политики вытеснения, к примеру, на основе принципа "наиболее давно использованный", для того, чтобы освобождать пространство для новых входящих данных в качестве результата неудачного обращения в кэш. Неудачное обращение в низкоуровневую кэш-память может приводить к запросу данных (т.е. к запросу на считывание) в следующую высокоуровневую кэш-память, которая имеет запрашиваемые данные, сохраненные в массиве данных или по-прежнему сохраненные в заполняющем буфере, перед сохранением в массиве данных кэша. В любом случае, запрашиваемые данные, содержащиеся в заполняющем буфере или в массиве данных высокоуровневой кэш-памяти, могут предоставляться в низкоуровневую кэш-память в ответ на запрос на данные из низкоуровневой кэш-памяти. Кэш-память может сохранять входящие данные в своем заполняющем буфере и не сохранять данные в своем массиве данных до тех пор, пока заполняющий буфер не становится полным, поскольку входящие запросы на данные могут удовлетворяться из заполняющего буфера, а также массива данных.

[0004] Процессор может использовать конвейерную обработку инструкций в качестве технологии обработки, за счет чего пропускная способность выполняемых компьютерных инструкций может увеличиваться посредством разбиения обработки каждой инструкции на последовательность этапов. Эти этапы выполняются в конвейере выполнения команд, состоящем из нескольких стадий. Тем не менее, в конвейере обработки инструкций могут возникать структурные опасности, когда следующая инструкция не может выполняться без приведения к некорректным результатам вычисления. Например, опасность по управлению может возникать в результате выполнения инструкции потока управления, которая вызывает точное прерывание в процессоре. Один пример инструкции потока управления, которая может вызывать опасность по управлению, представляет собой инструкцию условного ветвления. Инструкция условного ветвления может перенаправлять тракт потока выполнения инструкций на основе оцененного условия, когда условие инструкции ветвления управления выполняется. Один подход для максимизации производительности процессора заключает в себе использование схемы прогнозирования для того, чтобы спекулятивно прогнозировать результат условия инструкции условного ветвления перед ее выполнением. Таким образом, младшие инструкции, которые соответствуют прогнозированному тракту потока инструкции условного ветвления, могут получаться выборкой и также обрабатываться в конвейере обработки инструкций вместо остановки до тех пор, пока условие ветвления не разрешается, когда инструкция условного ветвления выполняется. Когда инструкция условного ветвления в завершение достигает стадии выполнения конвейера обработки инструкций и выполняется, результирующий целевой адрес инструкции условного ветвления верифицируется посредством его сравнения с ранее прогнозированным целевым адресам, когда инструкция условного ветвления получена выборкой. Если прогнозированные и фактические целевые адреса совпадают, что означает то, что корректное прогнозирование выполнено, задержка не вызывается при выполнении инструкций, поскольку последующие инструкции в целевом адресе корректно получаются выборкой и уже присутствуют в конвейере обработки инструкций, когда инструкция условного ветвления достигает стадии выполнения конвейера обработки инструкций. Тем не менее, если прогнозированные и фактические целевые адреса не совпадают, в конвейере обработки инструкций возникает опасность ошибочно прогнозированного ветвления, которая вызывает точное прерывание. Как результат, выполняется процесс восстановления после ошибочного прогнозирования, за счет которого младшие инструкции относительно инструкции условного ветвления в конвейере обработки инструкций сбрасываются, и модуль выборки из конвейера обработки инструкций перенаправляется с возможностью осуществлять выборку новых инструкций, начиная с целевого адреса, что приводит к задержке и уменьшенной производительности.

[0005] Даже если восстановление после ошибочного прогнозирования заключает в себе сброс младших инструкций относительно инструкции условного ветвления в некорректно прогнозированном тракте потока и затем выборку и обработку инструкций для инструкций в корректном тракте потока, обработка младших инструкций в некорректном тракте потока по-прежнему может приводить к отправке данных в кэш-память в качестве результата неудачных обращений в кэш. Это может вызывать проблему безопасности в форме утечек. Например, злоумышленный атакующий процесс, выполняющийся в процессоре, может включать в себя код, который загружает большой объем данных из памяти, обеспечивая тем самым заполнение этими данными совместно используемой кэш-памяти, чтобы подготовить (prime) кэш-память. Атакующий процесс также может подготовить схему прогнозирования ветвлений, чтобы она принудительно обеспечивала выполнение некорректного спекулятивного прогнозирования инструкции условного ветвления в выполняемом позднее процессе-жертве в более позднее время. Инструкции загрузки в некорректном спекулируемом тракте потока согласно инструкции условного ветвления в процессе-жертве инструктируют процессору загружать данные в кэш-память, даже если эти инструкции загрузки впоследствии сбрасываются, когда инструкция условного ветвления выполняется, и ее условие разрешается. Это инструктирует некоторым данным в кэш-памяти, подготовленной посредством атакующего процесса, вытесняться из кэш-памяти посредством инструкций загрузки в некорректном тракте потока в процессе-жертве. Когда атакующий процесс выполняется снова после того, как процесс-жертва переключается, атакующий процесс может определять то, какие из его подготовленных данных вытеснены из кэш-памяти. Эта информация может предоставлять информацию относительно адресов данных, к которым осуществляет доступ процесс-жертва.

[0006] Вышеуказанная проблема безопасности может разрешаться посредством предоставления неиспользуемого совместно спекулятивного буфера(ов) за пределами совместно используемой кэш-памяти, чтобы сохранять загруженные данные из обработки спекулятивно обработанных инструкций загрузки. Спекулятивно загруженные данные в спекулятивный буфер из обработки спекулятивно обработанной инструкции загрузки по-прежнему могут предоставляться в потребляющие инструкции в зависимости от спекулятивно обработанной инструкции загрузки. Когда инструкция загрузки, которая инструктирует данным спекулятивно загружаться в спекулятивный буфер, выполняется и становится неспекулятивной, если спекулятивное прогнозирование является корректным, спекулятивный запрос может повторно выдаваться неспекулятивно. Если спекулятивное прогнозирование является не корректным, спекулятивный запрос на данные повторно не выдается, за счет этого предотвращая установку спекулятивно загруженных данных в кэш-памяти. Таким образом, данные не загружаются в кэш-память в качестве результата обработки некорректно спекулируемых инструкций загрузки. Тем не менее, вдвое больше (2X) запросов данных должны выдаваться для того, чтобы загружать данные в процессор, что является неэффективным.

Сущность изобретения

[0007] Аспекты, раскрытые в данном документе, включают в себя отсрочку обновлений состояний кэша в неспекулятивной кэш-памяти в процессорной системе в ответ на спекулятивный запрос данных до тех пор, пока спекулятивный запрос данных не станет неспекулятивным. Процессорная система включает в себя процессор, который может включать в себя одно или более ядер процессора, которые выполняют компьютерные программные инструкции, чтобы выполнять операции на основе загруженных данных, сохраненных в основной памяти. Процессорная система также включает в себя систему кэш-памяти, которая включает в себя одну или более закрытых и/или совместно используемых кэш-памятей, организованных в иерархии между процессором и основной памятью. Каждая кэш-память имеет политику замещения кэша, которая регулирует то, какие данные в ее записях кэша должны вытесняться в высокоуровневую кэш-память или основную память, чтобы освобождать пространство для того, чтобы сохранять новые запросы данных (т.е. запросы на загрузку/считывание). Инструкции на основе загрузки ("инструкции загрузки"), которые спекулятивно обрабатываются посредством процессора в качестве результата спекулятивного прогнозирования условия инструкции условного управления потоком (например, инструкции условного ветвления), инструктируют осуществление запросов данных в систему кэш-памяти. Тем не менее, если условие инструкции условного управления потоком определяется как ошибочно прогнозированное при выполнении, спекулятивно обработанные инструкции на основе загрузки могут сбрасываться. Тем не менее, предыдущие запросы данных в систему кэш-памяти, получающиеся в результате обработки спекулятивных инструкций на основе загрузки, которые более не являются допустимыми, выполняются в систему кэш-памяти. Если таким запросам данных разрешено инструктировать вытеснение других данных кэша в системе кэш-памяти, это может вызывать загрязнение кэша. Это также может вызывать проблемы безопасности. Например, злоумышленный атакующий процесс может распознавать информацию относительно данных, к которым осуществляет доступ процесс-жертва, на основе некорректных спекулятивных данных, загружаемых в систему кэш-памяти. Злоумышленный атакующий процесс может подготавливать систему кэш-памяти собственными данными и подготавливать схему управляющего прогнозирования таким образом, чтобы выполнять ошибочные прогнозирования для инструкций условного управления потоком в процессе-жертве, вызывая загрузку некорректных спекулятивных данных в систему кэш-памяти. Атакующее приложение может распознавать информацию относительно процесса-жертвы на основе того, какие из подготовленных данных в системе кэш-памяти заменены посредством некорректных спекулятивных данных для загрузки в систему кэш-памяти.

[0008] В этом отношении, в примерных аспектах, раскрытых в данном документе, по меньшей мере одно состояние кэша в кэш-памяти отсрочивается в отношении обновления в кэш-памяти в ответ на принимаемый запрос данных до тех пор, пока запрос данных не станет неспекулятивным. Таким образом, кэш-память не обновляется на основе запроса данных, получающегося в результате ошибочного прогнозирования, который не должен выдаваться, если возникает ошибочное прогнозирование, и в силу этого кэш-память представляет собой неспекулятивную кэш-память. Таким образом, загрязнение кэша может уменьшаться. В качестве другого примера, атакующий процесс не может получать информацию относительно доступов к данным посредством процесса-жертвы, выполняющегося в процессоре, посредством заправки ошибочных прогнозирований в схеме управляющего прогнозирования, которая инструктирует запросам данных выдаваться посредством процесса-жертвы, что приводит к спекулятивно измененным состояниям кэша в кэш-памяти. Если запросы данных, которые не разрешаются как неспекулятивные, могут изменять состояние кэша в кэш-памяти, атакующее приложение может получать понимание доступов к данным посредством процесса-жертвы посредством понимания измененных состояний кэша в кэш-памяти.

[0009] В одном примерном аспекте, отсрочка обновления состояния кэша в кэш-памяти предоставляется посредством несохранения первоначально принимаемых спекулятивных запрашиваемых данных в записи кэша в основном массиве данных кэш-памяти, принимаемой из высокоуровневой памяти в качестве результата неудачного обращения в кэш-память. Вместо этого, принимаемые спекулятивные запрашиваемые данные сначала сохраняются в спекулятивной буферной памяти, т.е. не в основном массиве данных кэш-памяти. Например, спекулятивная буферная память может представлять собой заполняющую буферную схему в кэш-памяти, которая выступает в качестве области стадирования для запрашиваемых данных, которые должны сохраняться до тех пор, пока запись кэша в основном массиве данных кэш-памяти не становится доступной для того, чтобы сохранять входящие данные. Спекулятивные запрашиваемые данные, сохраненные в спекулятивной буферной памяти, сохраняются в доступную запись кэша в основном массиве данных кэш-памяти, если инструкция загрузки, которая приводит к запрашиваемому запросу данных, становится неспекулятивной. Новый запрос данных не должен обязательно выдаваться посредством процессора в систему кэш-памяти, чтобы инструктировать спекулятивным запрашиваемым данным, сохраненным в спекулятивной буферной памяти, сохраняться в запись кэша в кэш-памяти в ответ на то, что запрос данных становится неспекулятивным.

[0010] В другом примерном аспекте, когда запрос данных, выданный из процессора в кэш-память в системе кэш-памяти, содержится в записи кэша в основном массиве данных кэш-памяти, в результате получается удачное обращение в кэш. Поскольку спекулятивные запрашиваемые данные уже содержатся в записи кэша основного массива данных в кэш-памяти, спекулятивные запрашиваемые данные в записи кэша удачного обращения в основном массиве данных в кэш-памяти возвращаются запросчику в процессоре. Тем не менее, обновление состояния заменяющего кэша для записи кэша в основном массиве данных, содержащем спекулятивные запрашиваемые данные, может отсрочиваться до тех пор, пока инструкция загрузки, которая инициирует запрос данных для данных, не станет неспекулятивной. Таким образом, например, политика замены для основного массива данных кэш-памяти не должна выполняться на основе состояния заменяющего кэша, которое изменено для записи кэша основного массива данных, содержащего спекулятивные запрашиваемые данные, в качестве результата запроса данных, в случае если запрос данных сбрасывается в качестве результата ошибочного прогнозирования.

[0011] В другом примерном аспекте, если запрос данных, выданный из процессора в кэш-память, не содержится в основном массиве данных, но содержится в спекулятивной буферной памяти, ассоциированной с кэш-памятью, спекулятивные запрашиваемые данные в спекулятивной буферной памяти также возвращаются в запросчик в процессоре в качестве удачного обращения в кэш. Обновление состояния кэша для спекулятивных запрашиваемых данных отсрочивается посредством незаписи спекулятивных запрашиваемых данных в запись кэша в основном массиве данных кэш-памяти до тех пор, пока запрос данных не станет неспекулятивным. Кроме того, в качестве примера, обновление состояния заменяющего кэша для спекулятивных запрашиваемых данных автоматически отсрочивается до тех пор, пока новый запрос данных для идентичных данных не приводит к удачному обращению в кэш в основном массиве данных кэш-памяти, как пояснено выше.

[0012] В этом отношении, в одном примерном аспекте, предоставляется неспекулятивная кэш-память в процессорной системе. Неспекулятивная кэш-память содержит основной массив данных, содержащий множество записей кэша, каждая из которых выполнена с возможностью сохранять данные кэша данных, ассоциированных с адресом памяти, в системе памяти процессорной системы. Неспекулятивная кэш-память также содержит спекулятивную буферную память, содержащую множество записей буфера, каждая из которых содержит запись данных, выполненную с возможностью сохранять кэшированные данные, ассоциированные с адресом памяти, в системе памяти. Неспекулятивная кэш-память также содержит контроллер кэша, выполненный с возможностью принимать от запросчика запрос данных, содержащий целевой адрес и идентификационные данные (ID) инструкции, идентифицирующие инструкцию загрузки, содержащую целевой адрес, обработанный посредством процессора в процессорной системе. Контроллер кэша также выполнен с возможностью выполнять поиск записи кэша в основном массиве данных, ассоциированной с целевым адресом запроса данных. Контроллер кэша также выполнен с возможностью выполнять поиск в спекулятивной буферной памяти на предмет записи буфера, ассоциированной с целевым адресом запроса данных. Контроллер кэша также выполнен с возможностью отправлять запросчику ответ с данными на запрос данных на основе данных кэша в основном массиве данных, ассоциированных с целевым адресом, и данных кэша в записи буфера в спекулятивной буферной памяти, ассоциированной с целевым адресом. Контроллер кэша также выполнен с возможностью принимать индикатор фиксации, содержащий ID инструкции собственно инструкции, которая является неспекулятивной. Контроллер кэша также выполнен с возможностью, в ответ на принимаемый ID инструкции в индикаторе фиксации, указывающем то, что инструкция загрузки запроса данных является неспекулятивной, обновлять состояние кэша для записи кэша в основном массиве данных, ассоциированной с целевым адресом запроса данных.

[0013] В другом примерном аспекте, предоставляется способ обновления состояния кэша в неспекулятивной кэш-памяти в процессорной системе. Способ содержит прием от запросчика запроса данных, содержащего целевой адрес и ID инструкции, идентифицирующий инструкцию загрузки, содержащую целевой адрес, обработанный посредством процессора в процессорной системе. Способ также содержит выполнение поиска в основном массиве данных на предмет записи кэша, ассоциированной с целевым адресом запроса данных, из множества записей кэша, каждая из которых выполнена с возможностью сохранять данные кэша, ассоциированные с адресом памяти, в системе памяти процессорной системы. Способ также содержит выполнение поиска в спекулятивной буферной памяти на предмет записи буфера, ассоциированной с целевым адресом запроса данных, из множества записей кэша, каждая из которых выполнена с возможностью сохранять данные кэша, ассоциированные с адресом памяти, в системе памяти. Способ также содержит отправку запросчику ответа с данными на запрос данных на основе записи кэша в основном массиве данных, ассоциированной с целевым адресом, и данных кэша в записи буфера в спекулятивной буферной памяти, ассоциированной с целевым адресом. Способ также содержит прием индикатора фиксации, содержащего ID инструкции собственно инструкции, которая является неспекулятивной. Способ также содержит обновление состояния кэша для записи кэша в основном массиве данных, ассоциированной с целевым адресом запроса данных, в ответ на принимаемый ID инструкции в индикаторе фиксации, указывающем то, что инструкция загрузки запроса данных является неспекулятивной.

[0014] Специалисты в данной области техники должны принять во внимание объем настоящего раскрытия и реализовывать его дополнительные аспекты после прочтения нижеприведенного подробного описания предпочтительных вариантов осуществления в ассоциации с прилагаемыми чертежами.

Краткое описание чертежей

[0015] Прилагаемые чертежи, включенные и составляющие часть данного подробного описания, иллюстрируют несколько аспектов раскрытия и наряду с описанием служат для того, чтобы пояснять принципы раскрытия.

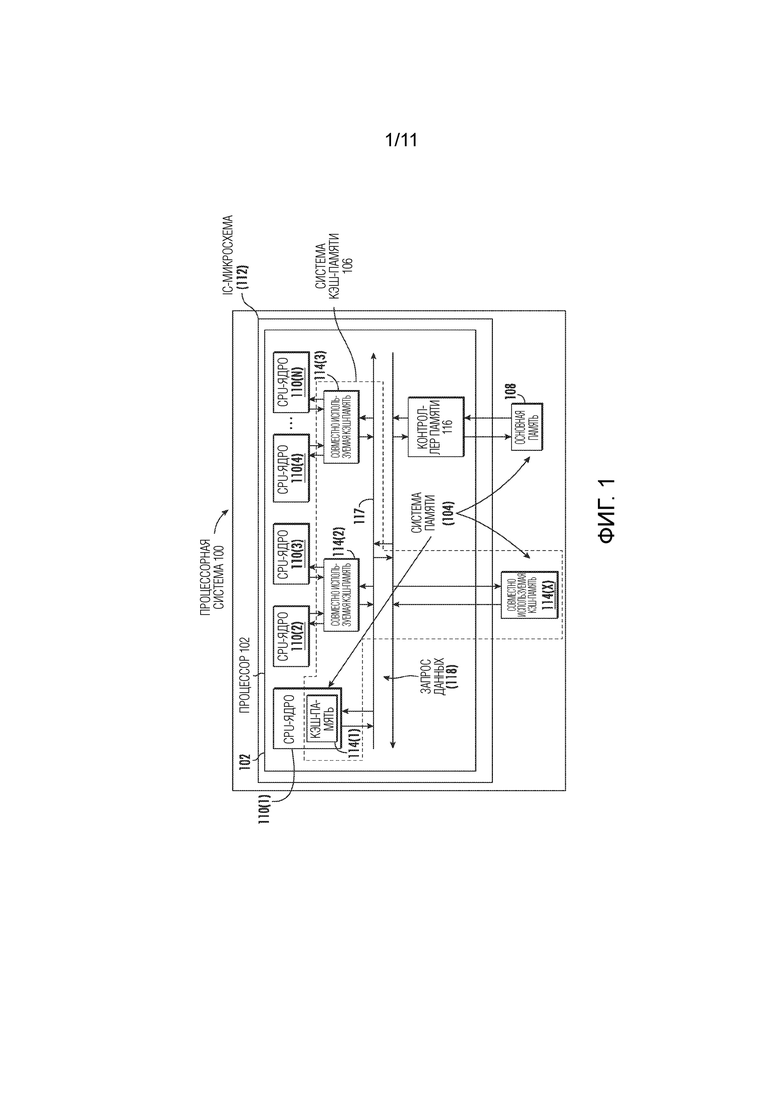

[0016] Фиг. 1 является схемой примерной процессорной системы, которая включает в себя процессор, выполненный с возможностью выдавать запросы на распределение памяти (т.е. запросы на считывание данных и на запись данных) в систему памяти, которая включает в себя систему кэш-памяти и основную память, при этом по меньшей мере одна кэш-память в системе кэш-памяти выполнена с возможностью отсрочивать обновление состояния кэша, в ответ на прием запроса данных из процессора до тех пор, пока запрос данных не станет неспекулятивным;

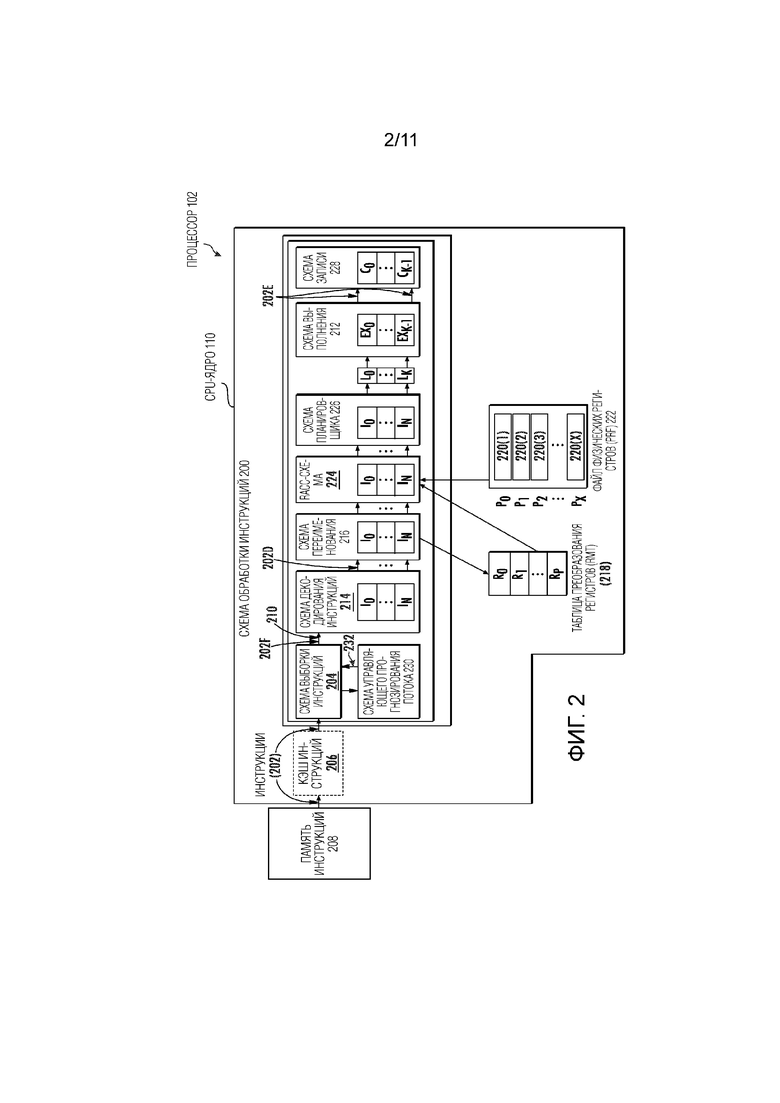

[0017] Фиг. 2 является схемой примерной схемы обработки инструкций, которая может включаться в процессор на фиг. 1, и которая включает в себя один или более конвейеров обработки инструкций для обработки компьютерных инструкций для выполнения, при этом схема обработки инструкций включает в себя схему прогнозирования потока управления, выполненную с возможностью спекулятивно прогнозировать условия инструкций условного управления потоком, полученных выборкой и обработанных посредством схемы обработки инструкций;

[0018] Фиг. 3 является схемой примерной неспекулятивной кэш-памяти в системе кэш-памяти на фиг. 1;

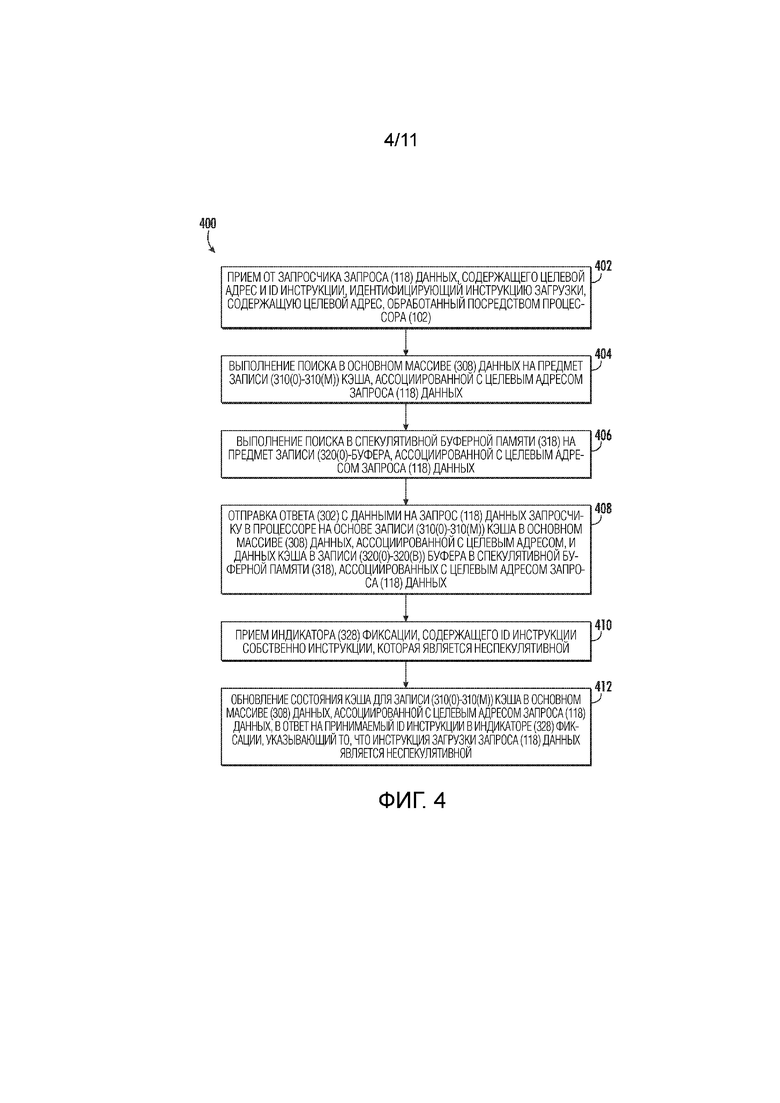

[0019] Фиг. 4 является блок-схемой последовательности операций способа, иллюстрирующей примерный процесс отсрочки, посредством контроллера кэша в кэш-памяти на фиг. 3, обновления состояния кэша данных для принимаемого запроса данных, который является спекулятивным, и обновления отсроченного состояния кэша в основном массиве данных для данных, ассоциированных с запросом данных, в ответ на то, что запрос данных становится неспекулятивным;

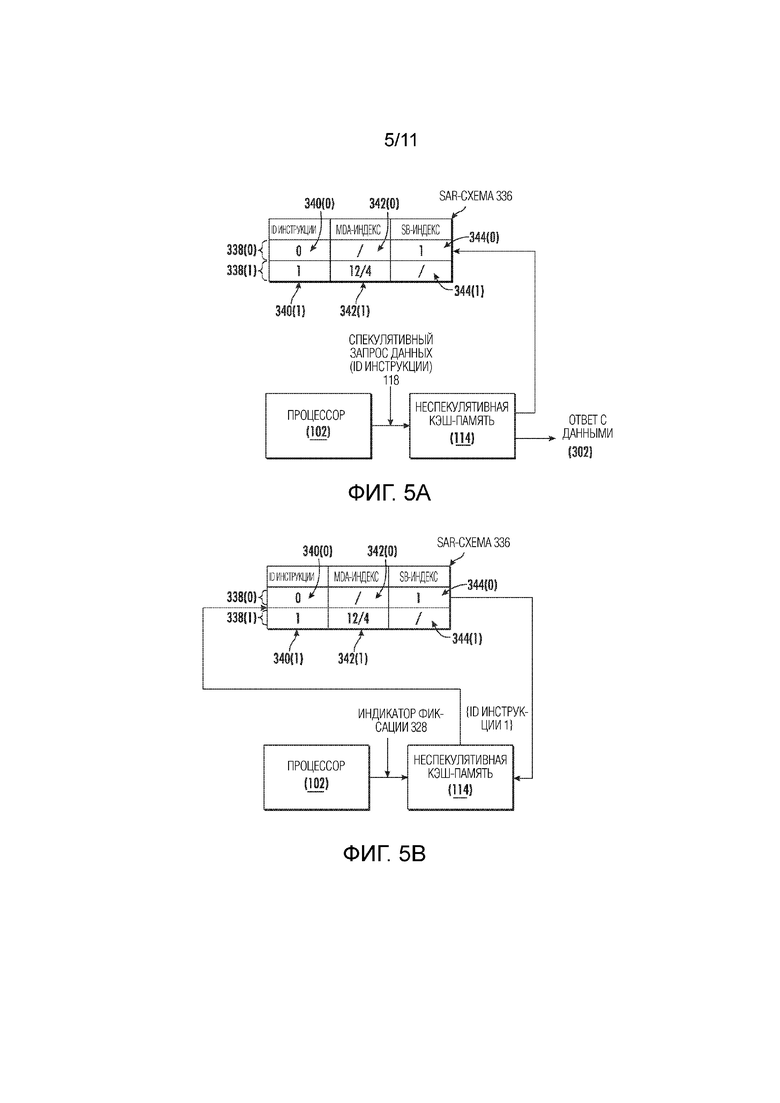

[0020] Фиг. 5A иллюстрирует выдачу, посредством процессора на фиг. 1, запроса данных в систему кэш-памяти, приводящего к удачному обращению в кэш в основном массиве данных кэш-памяти, при этом контроллер кэша кэш-памяти выделяет запись в схеме регистрации спекулятивных доступов (SAR), ассоциированную с инструкцией загрузки, обработанной посредством процессора, который формирует запрос данных, чтобы регистрировать отсрочку обновлений состояний кэша для записи кэша в основном массиве данных, сохраняющем спекулятивные запрашиваемые данные;

[0021] Фиг. 5B иллюстрирует прием, посредством кэш-памяти на фиг. 3, неспекулятивного индикатора из процессора, указывающего то, что инструкция загрузки, обработанная посредством процессора, становится неспекулятивной, и осуществление доступа, посредством контроллера кэша в кэш-памяти, к зарегистрированной отсрочке обновлений состояний кэша, ассоциированной с инструкцией загрузки, которая становится неспекулятивной таким образом, что состояние кэша для записи кэша в основном массиве данных, сохраняющем спекулятивные запрашиваемые данные, обновляется;

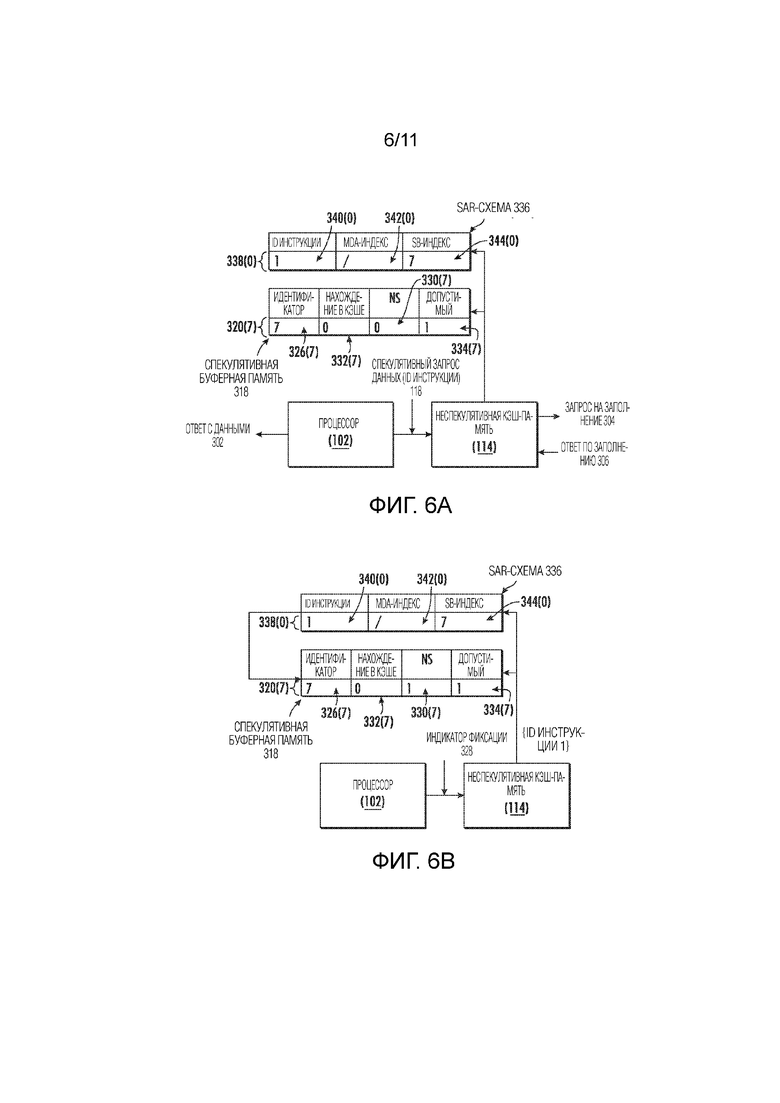

[0022] Фиг. 6A иллюстрирует выдачу, посредством процессора на фиг. 1, запроса данных в систему кэш-памяти, приводящего к неудачному обращению в кэш в основном массиве данных кэш-памяти, и записи, выделяемой в схеме регистрации спекулятивных доступов (SAR), выполненной с возможностью сохранять индекс, ассоциированный с инструкцией, ассоциированной с запросом данных, в записи буфера в спекулятивной буферной памяти, выделяемой для того, чтобы сохранять данные кэша для запроса данных, с тем чтобы регистрировать отсрочку обновлений состояний кэша для запроса данных;

[0023] Фиг. 6B иллюстрирует прием, посредством кэш-памяти на фиг. 3, неспекулятивного индикатора из процессора, указывающего то, что инструкция загрузки, обработанная посредством процессора, становится неспекулятивной, и в ответ, осуществление доступа, посредством контроллера кэша в кэш-памяти, к зарегистрированной отсрочке обновлений состояний кэша, ассоциированной с инструкцией загрузки в спекулятивной буферной памяти, индексированной посредством записи в SAR-схеме, ассоциированной с инструкцией, ассоциированной с запросом данных, чтобы обновлять состояние кэша для записи кэша в основном массиве данных, сохраняющем запрашиваемые данные;

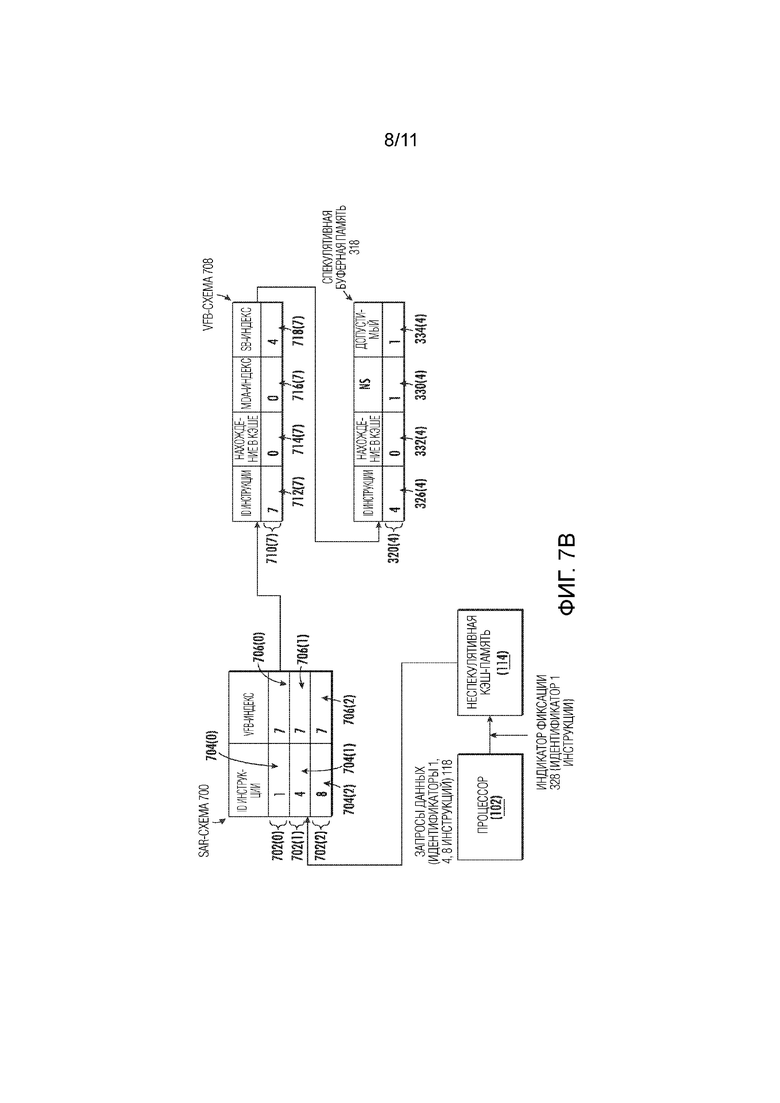

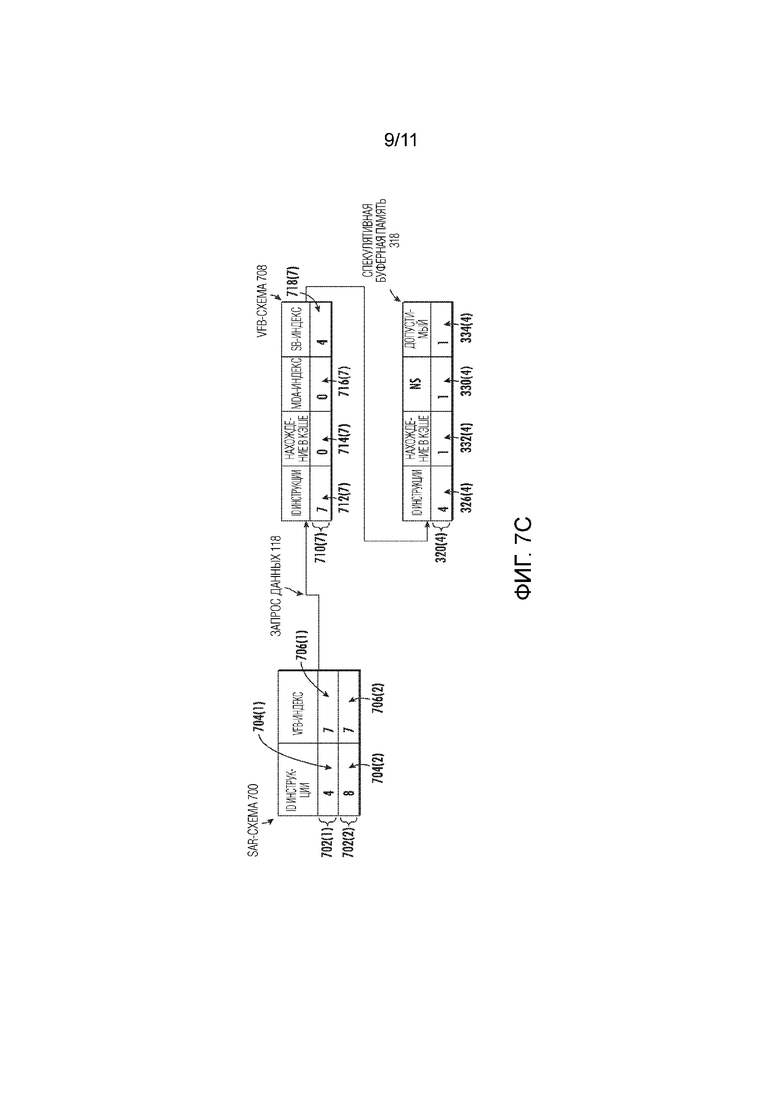

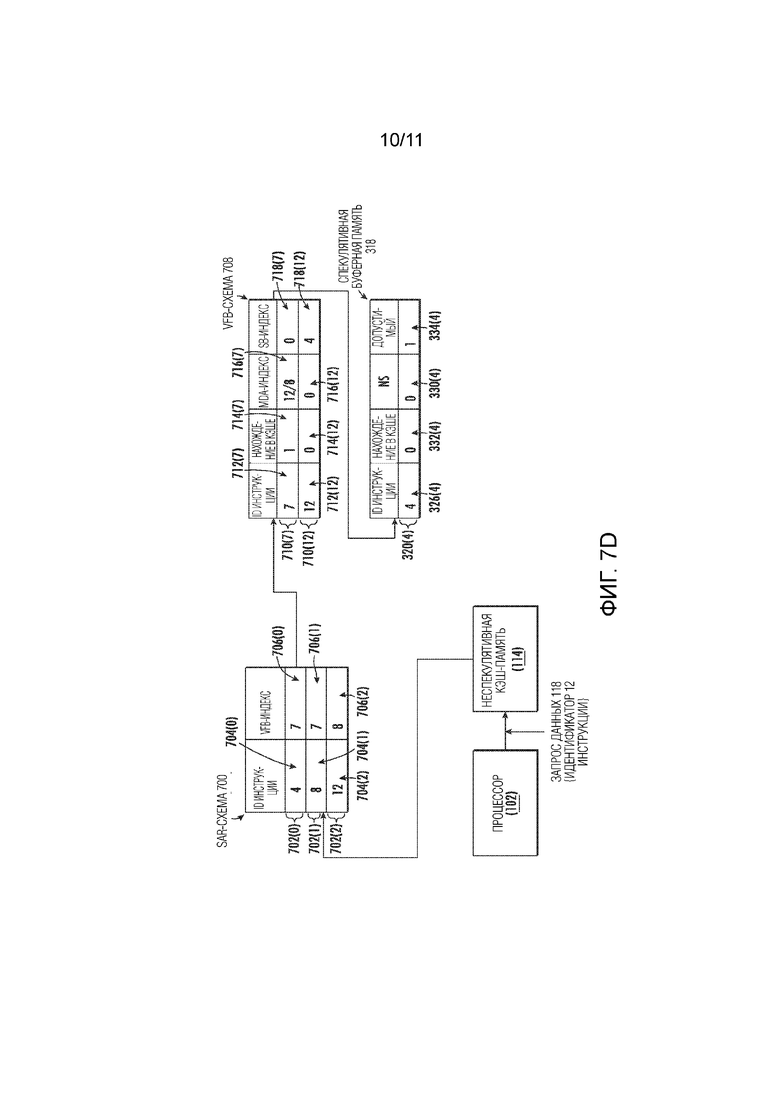

[0024] Фиг. 7A-7D иллюстрируют пример выдачи, посредством процессора на фиг. 1, запросов данных в систему кэш-памяти, приводящих к удачным обращениям в кэш и неудачным обращениям в кэш в основном массиве данных кэш-памяти, и примерную обработку отсрочки обновления состояний кэша для данных кэша в основном массиве данных, ассоциированных с запросами данных, посредством использования SAR-схемы, выполненной с возможностью индексировать виртуальную заполняющую буферную схему, и виртуальную заполняющую буферную схему, выполненную с возможностью индексировать спекулятивную буферную память таким образом, чтобы регистрировать отсроченное обновление состояния кэша для использования при обновлении состояния кэша, ассоциированного с запросами данных, после того как они становятся неспекулятивными; и

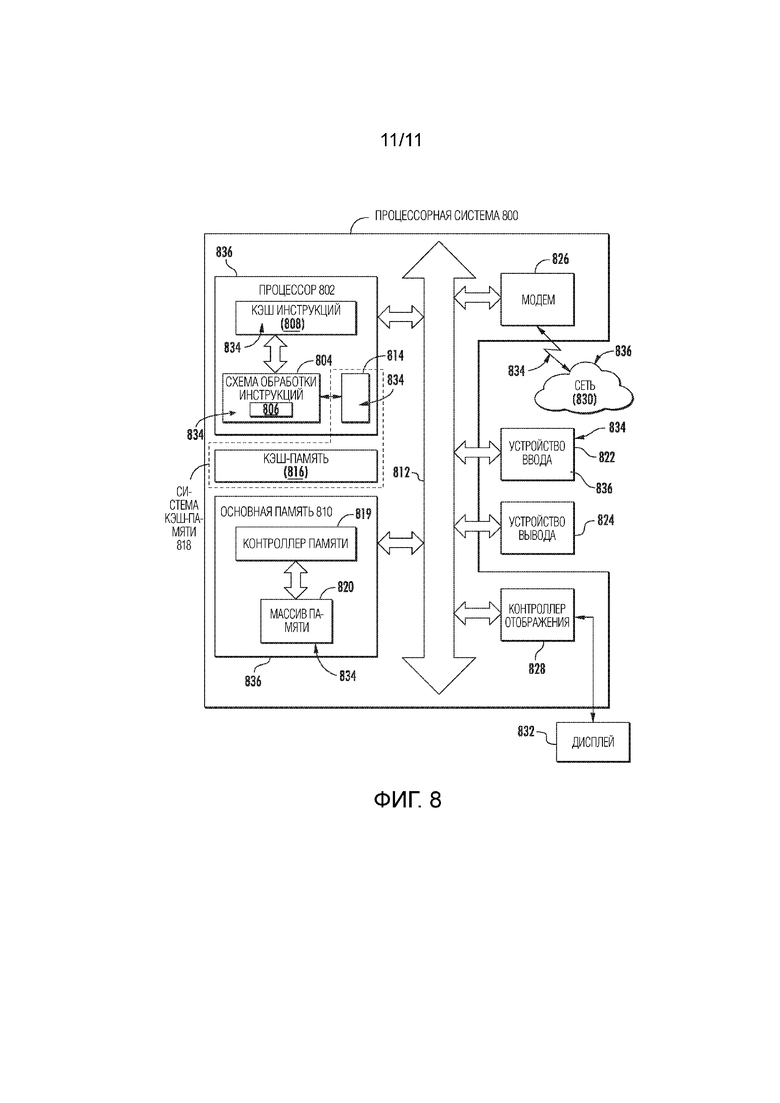

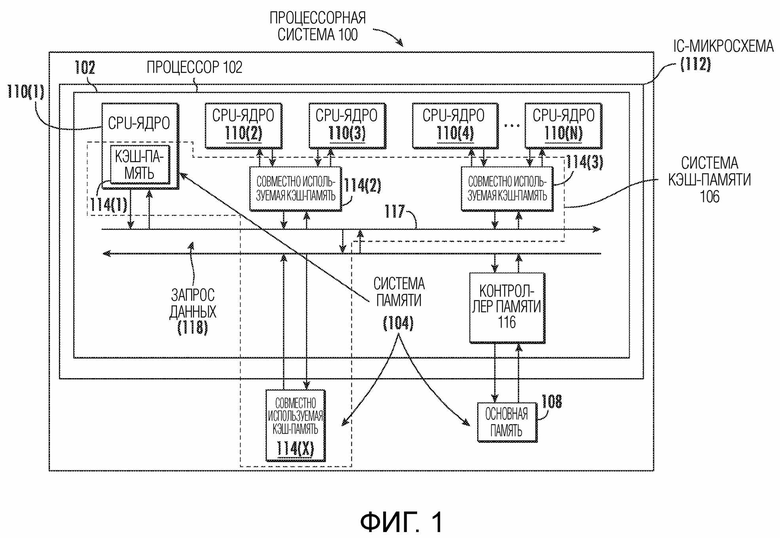

[0025] Фиг. 8 является блок-схемой примерной процессорной системы, включающей в себя процессор, выполненный с возможностью выдавать запросы на распределение памяти в систему памяти, которая включает в себя систему кэш-памяти и основную память, при этом система кэш-памяти включает в себя по меньшей мере одну кэш-память, в том числе, но не только, кэш-памяти на фиг. 1, 3, 5A-5B, 6A-6B и 7A-7D, выполненные с возможностью отсрочивать обновление состояния кэша, в ответ на прием запроса данных из процессора до тех пор, пока запрос данных не станет неспекулятивным.

Подробное описание изобретения

[0026] Аспекты, раскрытые в данном документе, включают в себя отсрочку обновлений состояний кэша в неспекулятивной кэш-памяти в процессорной системе в ответ на спекулятивный запрос данных до тех пор, пока спекулятивный запрос данных не станет неспекулятивным. Процессорная система включает в себя процессор, который может включать в себя одно или более ядер процессора, которые выполняют компьютерные программные инструкции, чтобы выполнять операции на основе загруженных данных, сохраненных в основной памяти. Процессорная система также включает в себя систему кэш-памяти, которая включает в себя одну или более закрытых и/или совместно используемых кэш-памятей, организованных в иерархии между процессором и основной памятью. Каждая кэш-память имеет политику замещения кэша, которая регулирует то, какие данные в ее записях кэша должны вытесняться в высокоуровневую кэш-память или основную память, чтобы освобождать пространство для того, чтобы сохранять новые запросы данных (т.е. запросы на загрузку/считывание). Инструкции на основе загрузки ("инструкции загрузки"), которые спекулятивно обрабатываются посредством процессора в качестве результата спекулятивного прогнозирования условия инструкции условного управления потоком (например, инструкции условного ветвления), инструктируют осуществление запросов данных в систему кэш-памяти. В примерных аспектах, раскрытых в данном документе, по меньшей мере одно состояние кэша в кэш-памяти отсрочивается в отношении обновления в кэш-памяти в ответ на принимаемый запрос данных до тех пор, пока запрос данных не станет неспекулятивным. Таким образом, кэш-память не обновляется на основе запроса данных, получающегося в результате ошибочного прогнозирования, который не должен выдаваться, если возникает ошибочное прогнозирование, и в силу этого кэш-память представляет собой неспекулятивную кэш-память.

[0027] Таким образом, загрязнение кэша может уменьшаться. В качестве другого примера, атакующий процесс не может получать информацию относительно доступов к данным посредством процесса-жертвы, выполняющегося в процессоре, посредством заправки ошибочных прогнозирований в схеме управляющего прогнозирования, которая инструктирует запросам данных выдаваться посредством процесса-жертвы, что приводит к спекулятивно измененным состояниям кэша к кэш-памяти. Если запросы данных, которые не разрешаются как неспекулятивные, могут изменять состояние кэша в кэш-памяти, атакующее приложение может получать понимание доступов к данным посредством процесса-жертвы посредством понимания измененных состояний кэша в кэш-памяти.

[0028] Фиг. 1 является схемой примерной процессорной системы 100, которая включает в себя центральный процессор (CPU) или процессор 102, выполненный с возможностью выдавать запросы на распределение памяти (т.е. запросы на считывание данных и на запись данных) в систему 104 памяти, которая включает в себя систему 106 кэш-памяти и основную память 108. Например, основная память 108 может представлять собой динамическую оперативную память (DRAM), предоставленную в отдельной DRAM-микросхеме. Процессор 102 включает в себя одно или более соответствующих CPU-ядер 110(1)-110(N), при этом "N" является положительным целым числом, представляющим число CPU-ядер, включенных в процессор 102. Процессор 102 может пакетироваться в микросхеме 112 с интегральными схемами (IC). Система 106 кэш-памяти включает в себя одну или более кэш-памятей 114(1)-114(X), которые могут иметь различные иерархии в процессорной системе 100, которые логически находятся между CPU-ядрами 110(1)-110(N) и основной памятью 108, где "X" является положительным целым числом, представляющим число CPU-ядер, включенных в процессор 102. Кэш-памяти сохраняют или кэшируют поднабор данных, содержащихся в основной памяти 108, чтобы предоставлять для CPU-ядер 110(1)-110(N) более быстрый доступ к данным в основной памяти 108 для выполнения запросов данных. Контроллер 116 памяти управляет доступом к основной памяти 108.

[0029] Например, CPU-ядро 110(1)-110(N) в качестве запрашивающего устройства может выдавать запрос 118 данных на то, чтобы считывать данные в ответ на обработку инструкции загрузки. Запрос 118 данных включает в себя целевой адрес данных, которые должны считываться из памяти. Запрос 118 данных также может включать в себя идентификационные данные (ID) инструкции, идентифицирующие инструкцию, которая инструктирует CPU-ядру 110(1)-110(N) выдавать запрос 118 данных. С использованием CPU-ядра 110(1) в качестве примера, если запрашиваемые данные не находятся в закрытой кэш-памяти 114(1) (т.е. неудачное обращение в кэш-память 114(1)), которая может считаться кэш-памятью первого уровня (L1), закрытая кэш-память 114(1) отправляет запрос 118 данных по межсоединительной шине 117 в этом примере в совместно используемую кэш-память 114(X), совместно используемую всеми CPU-ядрами 110(1)-110(N), которая может представлять собой кэш-память третьего уровня (3). Другие совместно используемые кэш-памяти 114(2), 114(3) с процессором 102, совместно используемые только с поднабором CPU-ядер 110(1)-110(N), также могут считаться кэш-памятью второго уровня (2). Запрашиваемые данные в конечном счете получаются либо в кэш-памяти 114(1)-114(X), либо в основной памяти 108, если не содержатся в любой из кэш-памятей 114(1)-114(X). Данные, принимаемые посредством кэш-памяти 114(1)-114(X) из высокоуровневой кэш-памяти 114(1)-114(X) или основной памяти 108 вследствие неудачного обращения в кэш, инструктируют принимающей кэш-памяти 114(1)-114(N) вытеснять данные кэша в высокоуровневую память, чтобы освобождать пространство для новых данных кэша. Каждая кэш-память 114(1)-114(X) имеет политику замещения кэша, которая регулирует то, какие из ее данных кэша должны вытесняться в высокоуровневую кэш-память 114(1)-114(X) или в основную память 108, чтобы освобождать пространство для того, чтобы сохранять новые данные кэша для запроса 118 данных, который приводит к неудачному обращению в кэш.

[0030] Фиг. 2 иллюстрирует схему 200 обработки инструкций, которая предоставляется в CPU-ядре 110, которое может представлять собой любое из CPU-ядер 110(1)-110(N) в процессоре 102 на фиг. 1. Схема 200 обработки инструкций включает в себя один или более конвейеров I0-IN обработки инструкций для обработки полученных выборкой компьютерных инструкций 202F, полученных выборкой посредством схемы 204 выборки инструкций для выполнения из последовательности инструкций 202, сохраненных в кэш-памяти 206 инструкций или в памяти 208 инструкций, в качестве примеров. Кэш-память 206 инструкций может предоставляться в качестве части кэш-памяти 114(1)-114(X) в системе 106 кэш-памяти в процессорной системе 100 на фиг. 1. Память 208 инструкций может предоставляться в или в качестве части основной памяти 108 в процессорной системе 100 на фиг. 1. Схема 204 выборки инструкций выполнена с возможностью предоставлять полученные выборкой инструкции 202F в один или более конвейеров I0-IN обработки инструкций в качестве потока 210 инструкций в схеме 200 обработки инструкций для предварительной обработки, до того, как полученные выборкой инструкции 202F достигают схемы 212 выполнения для выполнения. Конвейеры I0-IN обработки инструкций предоставляются в различных схемах или стадиях обработки схемы 200 обработки инструкций, чтобы предварительно обрабатывать и обрабатывать полученные выборкой инструкции 202F в последовательности этапов, которые могут выполняться параллельно, чтобы увеличивать пропускную способность до выполнения полученных выборкой инструкций 202F посредством схемы 212 выполнения.

[0031] С дальнейшей ссылкой на фиг. 2, схема 200 обработки инструкций включает в себя схему 214 декодирования инструкций, выполненную с возможностью декодировать полученные выборкой инструкции 202F, полученные выборкой посредством схемы 204 выборки инструкций, в декодированные инструкции 202D, с тем чтобы определять тип инструкций и требуемые действия. Декодированные инструкции 202D размещаются в одном или более конвейеров I0-IN обработки инструкций и затем предоставляются в схему 216 переименования в схеме 200 обработки инструкций, чтобы определять то, должны либо нет вообще имена регистров в декодированных инструкциях 202D переименовываться, чтобы разрывать все зависимости между регистрами, которые должны предотвращать параллельную обработку или обработку не по порядку. Схема 216 переименования выполнена с возможностью вызывать таблицу 218 преобразования регистров (RMT) с возможностью переименовывать логический исходный регистровый операнд и/или записывать целевой регистровый операнд декодированной инструкции 202D в доступные физические регистры 220(1)-220(X) (P0, P1, ..., PX) в файле 222 физических регистров (PRF). RMT 218 содержит множество записей преобразования, преобразованных (т.е. ассоциированных) в соответствующий логический регистр R0-RP. Записи преобразования выполнены с возможностью сохранять информацию в форме адресного указателя, чтобы указывать на физический регистр 220(1)-220(X) в файле 222 физических регистров (PRF). Каждый физический регистр 220(1)-220(X) в PRF 222 содержит запись данных, выполненную с возможностью сохранять данные для исходного и/или целевого регистрового операнда декодированной инструкции 202D.

[0032] Схема 200 обработки инструкций также включает в себя схему 224 доступа к регистрам (RACC), выполненную с возможностью осуществлять доступ к физическому регистру 220(1)-220(X) в PRF 222 на основе записи преобразования, преобразованной в логический регистр R0-RP в RMT 218 исходного регистрового операнда декодированной инструкции 202D, чтобы извлекать сформированное значение из выполняемой инструкции 202E в схеме 212 выполнения. RACC-схема 224 также выполнена с возможностью предоставлять извлеченное сформированное значение из выполняемой декодированной инструкции 202E в качестве исходного регистрового операнда декодированной инструкции 202D, которая должна выполняться. Кроме того, в схеме 200 обработки инструкций, схема 226 планировщика предоставляется в конвейере I0-IN обработки инструкций и выполнена с возможностью сохранять декодированные инструкции 202D в записях резервирования до тех пор, пока все исходные регистровые операнды для декодированной инструкции 202D не являются доступными. Схема 226 планировщика выдает декодированные инструкции 202D, готовые к выполнению в трассе L0-LK выполнения, в схему 212 выполнения. Схема 228 записи также предоставляется в схеме 200 обработки инструкций, чтобы записывать обратно или фиксировать сформированные значения из выполняемых инструкций 202E в память, к примеру, в PRF 222, в систему 106 кэш-памяти или в основную память 108.

[0033] С дальнейшей ссылкой на фиг. 2, схема 200 обработки инструкций также включает в себя схему 230 управляющего прогнозирования потока. Схема 230 управляющего прогнозирования потока выполнена с возможностью спекулятивно прогнозировать результат условия полученной выборкой инструкции 202F условного управления потоком, к примеру, инструкции условного ветвления, которая управляет тем, подвергается либо нет выбранный или не выбранный тракт в тракте потока управления инструкциями потока 210 инструкций выборке в конвейеры I0-IN обработки инструкций для выполнения. Таким образом, условие полученной выборкой инструкции 202F условного управления потоком не должно обязательно разрешаться при выполнении посредством схемы 212 выполнения до того, как схема 200 обработки инструкций может продолжать обработку спекулятивно полученных выборкой инструкций 202F. Прогнозирование, выполненное посредством схемы 230 управляющего прогнозирования потока, может предоставляться в качестве информации 232 прогнозирования в схему 204 выборки инструкций для использования посредством схемы 204 выборки инструкций для того, чтобы определять следующие инструкции 202 для выборки.

[0034] Тем не менее, если условие инструкции 202F условного управления потоком определяется как ошибочно прогнозированное, когда инструкция 202F условного управления потоком выполняется в схеме 212 выполнения, спекулятивные полученные выборкой инструкции 202F, которые получены выборкой после инструкции 202F условного управления потоком и обработаны в схеме 202 обработки инструкций, сбрасываются, поскольку эти инструкции не должны обрабатываться. Схема 202 обработки инструкций возвращается в состояние, которое существует до того, когда обрабатывается инструкция 202F условного управления потоком. Спекулятивные полученные выборкой инструкции 202F, которые очищаются в ответ на ошибочное прогнозирование, могут включать в себя инструкции на основе загрузки ("инструкции загрузки"), которые выдают спекулятивные запросы 118 данных в систему 106 кэш-памяти в процессорной системе 100 на фиг. 1. Если такие спекулятивные запросы 118 данных приводят к неудачным обращениям в кэш, данные вытесняются из системы 106 кэш-памяти, чтобы освобождать пространство для ответа с данными на любые такие спекулятивные запросы 118 данных. Это может вызывать загрязнение кэша. Это также может вызывать проблемы безопасности. Например, злоумышленный атакующий процесс, выполняющийся в процессоре 102, может распознавать информацию относительно данных, к которым осуществляет доступ процесс-жертва, выполняющийся в процессоре 102, на основе некорректных спекулятивных данных, загружаемых в систему 106 кэш-памяти. Злоумышленный атакующий процесс может подготавливать систему 106 кэш-памяти собственными данными и подготавливать схему 230 управляющего прогнозирования потока таким образом, чтобы выполнять ошибочные прогнозирования для инструкций 202F условного управления потоком в процессе-жертве, вызывая загрузку некорректных спекулятивных данных в систему 106 кэш-памяти. Атакующее приложение может распознавать информацию относительно процесса-жертвы на основе того, какие из подготовленных воздействуемых данных в системе 106 кэш-памяти заменены посредством некорректных спекулятивных данных для загрузки в систему 106 кэш-памяти.

[0035] В этом отношении, одна или более кэш-памятей 114(1)-114(X) в системе 106 кэш-памяти в процессорной системе 100 на фиг. 1 могут быть выполнены с возможностью представлять собой неспекулятивные кэш-памяти. Неспекулятивная кэш-память выполнена с возможностью отсрочивать обновление состояния кэша для записи кэша для принимаемого запроса 118 данных в отношении обновления до тех пор, пока запрос данных не станет неспекулятивным. Например, фиг. 3 иллюстрирует пример кэш-памяти 114 в процессорной системе 100 на фиг. 1, сконфигурированной в качестве неспекулятивной кэш-памяти 114. Как показано на фиг. 3, неспекулятивная кэш-память 114 включает в себя контроллер 300 кэша, который представляет собой схему, выполненную с возможностью управлять операциями неспекулятивной кэш-памяти 114, включающими в себя обработку запросов 118 данных для доступа к данным кэша, сохраненным в неспекулятивной кэш-памяти 114, предоставление ответов 302 с данными для данных кэша запросчику, запросов 304 на заполнение, чтобы получать данные кэша из высокоуровневой памяти в ответ на неудачное обращение в кэш для принимаемого запроса 118 данных, и ответов 306 по заполнению с данными кэша, принимаемыми из высокоуровневой памяти, в ответ на запрос 304 на заполнение.

[0036] Неспекулятивная кэш-память 114 также включает в себя основной массив 308 данных, который включает в себя множество записей 310(0)-310(M) кэша, каждая из которых выполнена с возможностью сохранять данные 314(0)-314(M) кэша, сохраненные в системе 104 памяти по фиг. 1, в адресе памяти, ассоциированном с соответствующим тегом 312(0)-312(M). Неспекулятивная кэш-память 114 также включает в себя массив 311 тегов, который выполнен с возможностью сохранять множество тегов 312(0)-312(M), соответствующих надлежащим записям 310(0)-310(M) кэша. Основной массив 308 данных также может включать в себя состояние 315(0)-315(M) замещения кэша в каждой соответствующей записи 310(0)-310(M) кэша для того, чтобы указывать состояние замены для ассоциированной записи 310(0)-310(M) кэша, используемой посредством контроллера 300 кэша для того, чтобы определять то, какую запись 310(0)-310(M) кэша следует вытеснить, когда новые данные для неспекулятивного запроса 118 данных должны сохраняться в основном массиве 308 данных. Основной массив 308 данных также может включать в себя допустимый индикатор 316(0)-316(M) в каждой соответствующей записи 310(0)-310(M) кэша для того, чтобы указывать то, являются или нет данные 314(0)-314(M) кэша допустимыми. Неспекулятивная кэш-память 114 в этом примере также включает в себя спекулятивную буферную память 318, которая включает в себя множество записей 320(0)-320(B) буфера, каждая из которых выполнена с возможностью сохранять данные 324(0)-324(B) кэша, сохраненные в системе 104 памяти, в адресе памяти, ассоциированном с соответствующим тегом 322(0)-322(B) буфера. Неспекулятивная кэш-память 114 также включает в себя массив 323 тегов, который выполнен с возможностью сохранять теги 322(0)-322(B) буфера, ассоциированные соответствующей записью 320(0)-320(B) буфера. Например, спекулятивная буферная память 318 может представлять собой заполняющий буфер для неспекулятивной кэш-памяти 114, который выступает в качестве области стадирования для входящих данных в ответе 306 по заполнению в ответ на выданный запрос 304 на заполнение, который должен сохраняться в неспекулятивной кэш-памяти 114 до тех пор, пока запись 310(0)-310(M) кэша в основном массиве 308 данных не становится доступной для того, чтобы сохранять входящие данные.

[0037] С дальнейшей ссылкой на фиг. 3, спекулятивная буферная память 318 также включает в себя идентификатор 326(0)-326(B) инструкции в каждой соответствующей записи 320(0)-320(B) буфера, чтобы сохранять ID инструкции собственно инструкции загрузки, которая выдает запрос 118 данных в неспекулятивную кэш-память 114, чтобы отслеживать то, становится либо нет и когда запрос 118 данных становится неспекулятивным. Контроллер 300 кэша выполнен с возможностью обновлять состояние кэша, ассоциированное с запросом 118 данных, в записи 310(0)-310(M) кэша в основном массиве 308 данных, ассоциированной с запросом 118 данных после того, как инструкция, которая инструктирует выдачу запроса 118 данных, становится неспекулятивной в процессоре 102. Как подробнее поясняется ниже, контроллер 300 кэша выполнен с возможностью выделять запись 320(0)-320(B) буфера в спекулятивной буферной памяти 318 в ответ на принимаемый запрос 118 данных. Контроллер 300 кэша выполнен с возможностью первоначально обновлять соответствующий спекулятивный индикатор 330(0)-330(B) (NS) со спекулятивным состоянием в каждой записи 320(0)-320(B) буфера для принимаемого запроса 118 данных в качестве спекулятивного. Каждая запись 320(0)-320(B) буфера в спекулятивной буферной памяти 318 также включает в себя индикатор 332(0)-332(B) нахождения в кэше, указывающий то, сохраняются или нет данные для ассоциированной записи 320(0)-320(B) буфера в записи 310(0)-310(M) кэша в основном массиве 308 данных, и допустимый индикатор 334(0)-334(B), указывающий то, является или нет запись 320(0)-320(B) буфера допустимой. Неспекулятивная кэш-память 114 выполнена с возможностью принимать индикатор 328 фиксации, выданный посредством процессора 102, содержащий ID инструкции собственно инструкции, которая является неспекулятивной. Контроллер 300 кэша может использовать принимаемый ID инструкции в индикаторе 328 фиксации, чтобы выполнять поиск идентификаторов 326(0)-326(B) инструкций в спекулятивной буферной памяти 318, чтобы обновлять соответствующий неспекулятивный индикатор 330(0)-330(B) (NS) в каждой записи 320(0)-320(B) буфера. Контроллер 300 кэша затем может обновлять состояние кэша для данных, ассоциированных с запросом 118 данных в записи 310(0)-310(M) кэша в основном массиве 308 данных, в ответ на неспекулятивный индикатор 330(0)-330(B) (NS) для запроса 118 данных, который становится неспекулятивным.

[0038] Например, если инструкция 202D загрузки, которая спекулятивно обрабатывается на основе прогнозирования потока управления в процессоре 102 на фиг. 2, инструктирует процессору 102 выдавать запрос 118 данных для данных в неспекулятивную кэш-память 114 на фиг. 3, контроллер 300 кэша выполнен с возможностью выполнять поиск в массиве 311 тегов на предмет тега 312(0)-312(M) в записи 310(0)-310(M) кэша, ассоциированной с целевым адресом запроса 118 данных, чтобы определять то, присутствуют или нет данные для запроса 118 данных. Контроллер 300 кэша также выполнен с возможностью выполнять поиск в спекулятивной буферной памяти 318 на предмет тега 322(0)-322(B) буфера в массиве 323 тегов, соответствующего записи 320(0)-320(B) буфера, ассоциированной с целевым адресом запроса 118 данных, чтобы определять то, присутствуют или нет данные для запроса 118 данных в спекулятивной буферной памяти 318. Если возникает неудачное обращение в кэш, при котором данные для запроса 118 данных не присутствуют в основном массиве 308 данных или в спекулятивной буферной памяти 318, контроллер 300 кэша выдает запрос 304 на заполнение для данных из высокоуровневой памяти и принимает запрашиваемые данные в качестве ответа 306 по заполнению. Контроллер 300 кэша может быть выполнен с возможностью отсрочивать обновление состояния кэша для запроса 118 данных посредством несохранения первоначально принимаемых данных в ответе 306 по заполнению для запроса 118 данных в записи 310(0)-310(M) кэша в основном массиве 308 данных. Вместо этого, принимаемые данные для запроса 118 данных могут сначала сохраняться в качестве данных 324(0)-324(B) кэша в выделяемой записи 320(0)-320(B) буфера в спекулятивной буферной памяти 318, с тем чтобы не загрязнять основной массив 308 данных спекулятивными данными. Когда запрос 118 данных становится неспекулятивным, как указано посредством ID инструкции в индикаторе 328 фиксации, совпадающего с идентификатором 326(0)-326(B) инструкции в записи 320(0)-320(B) буфера в спекулятивной буферной памяти 318, контроллер 300 кэша может инструктировать сохранение данных для запроса 118 данных в выделяемой записи 310(0)-310(M) кэша в основном массиве 308 данных.

[0039] В другом примере, когда целевой адрес запроса 118 данных соответствует совпадающему тегу 312(0)-312(M) в массиве 311 тегов в неспекулятивной кэш-памяти 114, в результате получается удачное обращение в кэш. Это означает то, что данные для запроса 118 данных уже содержатся в записи 310(0)-310(M) кэша в основном массиве 308 данных, соответствующей совпадающему тегу 312(0)-312(M). Данные 314(0)-314(M) кэша для запроса 118 данных, сохраненного в соответствующей записи 310(0)-310(M) кэша, возвращаются в качестве ответа 302 с данными запросчику в процессоре 102. Тем не менее, обновление состояния 315(0)-315(M) замещения кэша для записи 310(0)-310(M) кэша, которая имеет данные 314(0)-314(M) кэша для запроса 118 данных, может отсрочиваться до тех пор, пока запрос 118 данных не станет неспекулятивным. Таким образом, например, политика замещения неспекулятивной кэш-памяти 114 не должна выполняться на основе состояния заменяющего кэша для записи 310(0)-310(M) кэша в основном массиве 308 данных, которая изменена посредством спекулятивного запроса 118 данных, который может сбрасываться в процессоре 102 вследствие ошибочного прогнозирования, что приводит к недопустимости обновления состояния кэша.

[0040] В другом примере, если запрос 118 данных, выданный из процессора 102, неспекулятивная кэш-память 114, не содержится в записи 310(0)-310(M) кэша в основном массиве 308 данных, но содержится в записи 320(0)-320(B) буфера в спекулятивной буферной памяти 318, соответствующие данные 324(0)-324(B) кэша для запроса 118 данных возвращаются запросчику в процессоре 102 в качестве ответа 302 с данными. Тем не менее, контроллер 300 кэша может быть выполнен с возможностью отсрочивать обновление состояния кэша для запроса 118 данных посредством несохранения данных в спекулятивной буферной памяти 318 для запроса 118 данных в записи 310(0)-310(M) кэша в основном массиве 308 данных, с тем чтобы не загрязнять основной массив 308 данных спекулятивными данными. Когда запрос 118 данных становится неспекулятивным, как указано посредством ID инструкции в индикаторе 328 фиксации, совпадающего с идентификатором 326(0)-326(B) инструкции в записи 320(0)-320(B) буфера в спекулятивной буферной памяти 318, контроллер 300 кэша может инструктировать сохранение данных для запроса 118 данных в выделяемой записи 310(0)-310(M) кэша в основном массиве 308 данных. Таким образом, в качестве другого примера, если дальнейшее удачное обращение в кэш возникает в такой выделяемой записи 310(0)-310(M) кэша для нового, последующего запроса 118 данных, то обновление состояния 315(0)-315(M) замещения кэша для записи 310(0)-310(M) кэша в основном массиве 308 данных, которая имеет данные 314(0)-314(M) кэша для запроса 118 данных, должно отсрочиваться до тех пор, пока запрос 118 данных не станет неспекулятивным, как пояснено выше для удачного обращения в кэш для основного массива 308 данных.

[0041] Фиг. 4 является блок-схемой последовательности операций способа, иллюстрирующей примерный процесс 400 отсрочки, посредством контроллера 300 кэша в неспекулятивной кэш-памяти 114 на фиг. 3, обновления состояния кэша данных для принимаемого запроса 118 данных, который является спекулятивным. Процесс 400 на фиг. 4 также включает в себя обновление отсроченного состояния кэша в основном массиве 308 данных для данных, ассоциированных с запросом 118 данных, в ответ то, что запрос 118 данных становится неспекулятивным. В дальнейшем поясняется процесс 400 на фиг. 4 в сочетании с неспекулятивной кэш-памятью 114 на фиг. 3 и процессором 102 на фиг. 1 и 2. В этом отношении, неспекулятивная кэш-память 114 принимает от запросчика запрос 118 данных, содержащий целевой адрес и идентификационные данные (ID) инструкции, идентифицирующие инструкцию загрузки, содержащую целевой адрес, обработанный посредством процессора 102 (этап 402 на фиг. 4). Контроллер 300 кэша выполняет поиск в массиве 311 тегов на предмет тега 312(0)-312(M), ассоциированного с целевым адресом запроса 118 данных (этап 404 на фиг. 4). Контроллер 300 кэша также выполняет поиск в спекулятивной буферной памяти 318 на предмет тега 322(0)-322(B) буфера, ассоциированного с целевым адресом запроса 118 данных (этап 406 на фиг. 4). Контроллер 300 кэша отправляет ответ 302 с данными для запроса 118 данных запросчику в процессоре 102 на основе тега 312(0)-312(M) в записи 310(0)-310(M) кэша в основном массиве 308 данных, ассоциированной с целевым адресом, и тега 322(0)-322(B) буфера в массиве 323 тегов в спекулятивной буферной памяти 318, ассоциированном с целевым адресом запроса 118 данных (этап 408 на фиг. 4). Контроллер 300 кэша принимает индикатор 328 фиксации, содержащий ID инструкции собственно инструкции, которая является неспекулятивной (этап 410 на фиг. 4). В ответ на принимаемый ID инструкции в индикаторе 328 фиксации, указывающий то, что инструкция загрузки запроса 118 данных является неспекулятивной, контроллер 300 кэша обновляет состояние кэша для записи 310(0)-310(M) кэша в основном массиве 308 данных, ассоциированной с целевым адресом запроса 118 данных (этап 412 на фиг. 4).

[0042] Как также подробнее поясняется ниже, неспекулятивная кэш-память 114 также может включать в себя схему 336 регистрации спекулятивных доступов (SAR), чтобы отслеживать то, содержатся или нет данные, ассоциированные с запросом 118 данных, относительно которого еще не известно, что он является неспекулятивным, в основном массиве 308 данных или в спекулятивной буферной памяти 318. Как пояснено выше, данные для принимаемого запроса 118 данных могут уже содержаться в основном массиве 308 данных, что приводит к удачному обращению в кэш, могут уже содержаться в спекулятивной буферной памяти 318, что также приводит к удачному обращению в кэш, либо могут не содержаться ни в одном из них, что приводит к неудачному обращению в кэш. В случае неудачного обращения в кэш, запись 320(0)-320(B) буфера, которая сохраняет данные запроса 118 данных, выделяется в спекулятивной буферной памяти 318. Таким образом, данные для запроса 118 данных могут сохраняться в основном массиве 308 данных или в спекулятивной буферной памяти 318. В ответ на прием индикатора 328 фиксации, указывающего ID инструкции собственно инструкции, которая фиксируется посредством процессора 102, контроллеру 300 кэша требуется способ для того, чтобы определять то, сохраняются либо нет данные, ассоциированные с запросом 118 данных, выданным в качестве результата совпадения инструкции с идентификатором инструкции, в основном массиве 308 данных или в спекулятивной буферной памяти 318, так что состояние кэша может обновляться. Если данные, ассоциированные с зафиксированной инструкцией, идентифицированной посредством ID инструкции в индикаторе 328 фиксации, сохраняются в основном массиве 308 данных, контроллер 300 кэша должен обновлять состояние кэша для записи 310(0)-310(M) кэша в основном массиве 308 данных, сохраняющем данные для зафиксированного запроса 118 данных. Если данные, ассоциированные с зафиксированной инструкцией, идентифицированной посредством ID инструкции в индикаторе 328 фиксации, сохраняются в спекулятивной буферной памяти 318, контроллер 300 кэша должен обновлять неспекулятивный индикатор 330(0)-330(B) (NS) записи 320(0)-320(B) буфера в спекулятивной буферной памяти 318. Контроллер 300 кэша обновляет неспекулятивный индикатор 330(0)-330(B) (NS) записи 320(0)-320(B) буфера, ассоциированной с идентификатором инструкции, в качестве неспекулятивного, так что данные, ассоциированные с зафиксированным запросом 118 данных, записываются в основной массив 308 данных в качестве неспекулятивных данных.

[0043] В этом отношении, как проиллюстрировано на фиг. 3, неспекулятивная кэш-память 114 включает в себя SAR-схему 336, которая выполнена с возможностью сохранять SAR-записи 338(0)-338(S), ассоциированные соответствующим идентификатором 340(0)-340(S) инструкции. Когда запрос 118 данных принимается, контроллер 300 кэша выделяет SAR-запись 338(0)-338(S), выделяемую в SAR-схеме 336, ассоциированной с идентификатором инструкции для инструкции, которая выдает запрос 118 данных. Если данные, ассоциированные с инструкцией, идентифицированной посредством ID инструкции принимаемого запроса 118 данных, уже сохраняются в записи 310(0)-310(M) кэша в основном массиве 308 данных, индекс 342(0)-342(S) основного массива данных (MDA) для выделяемой SAR-записи 338(0)-338(S) обновляется с индексом в записи 310(0)-310(M) кэша в основном массиве 308 данных, которая содержит данные для запроса 118 данных. Если данные, ассоциированные с инструкцией, идентифицированной посредством ID инструкции принимаемого запроса 118 данных, не сохраняются в записи 310(0)-310(M) кэша в основном массиве 308 данных, но сохраняются в записи 320(0)-320(B) буфера в спекулятивной буферной памяти 318, индекс 344(0)-344(S) спекулятивного буфера (SB) для выделяемой SAR-записи 338(0)-338(S) обновляется с индексом в записи 320(0)-320(B) буфера в спекулятивной буферной памяти 318, которая содержит данные для запроса 118 данных. Если данные, ассоциированные с инструкцией, идентифицированной посредством ID инструкции принимаемого запроса 118 данных, не сохраняются в записи 310(0)-310(M) кэша в основном массиве 308 данных или в записи 320(0)-320(B) буфера в спекулятивной буферной памяти 318, что приводит к неудачному обращению в кэш, индекс 344(0)-344(S) спекулятивного буфера (SB) для выделяемой SAR-записи 338(0)-338(S) обновляется с индексом в записи 320(0)-320(B) буфера в спекулятивной буферной памяти 318, которая содержит данные для запроса 118 данных, принимаемого из ответа 306 по заполнению из высокоуровневой памяти в ответ на запрос 304 на заполнение. Как пояснено выше, выделение SAR-записи 338(0)-338(S) для запросов 118 данных в SAR-схеме 336 обеспечивает возможность того, что контроллер 300 кэша определяет то, следует либо нет обновлять состояние кэша данных, ассоциированных с запросом 118 данных, который становится неспекулятивным, в основном массиве 308 данных или в спекулятивной буферной памяти 318.

[0044] Чтобы иллюстрировать пример использования SAR-схемы 336 посредством неспекулятивной кэш-памяти 114, чтобы отслеживать зарегистрированные спекулятивные запросы данных и иметь возможность отсрочивать обновление состояния кэша в неспекулятивной кэш-памяти 114 до тех пор, пока запрос данных не станет неспекулятивным, предоставляются фиг. 5A и 5B. Фиг. 5A иллюстрирует выдачу, посредством процессора 102 на фиг. 1, запроса 118 данных, содержащего ID инструкции и целевой адрес, который принимается посредством неспекулятивной кэш-памяти 114, что приводит к удачному обращению в кэш в основном массиве 308 данных неспекулятивной кэш-памяти 114. В этом примере, ID инструкции в запросе 118 данных, идентифицирующий инструкцию по обработке, которая инструктирует запросу 118 данных выдаваться, представляет собой идентификатор 1 инструкции. Контроллер 300 кэша в неспекулятивной кэш-памяти 114 выполнен с возможностью выполнять поиск в основном массиве 308 данных и в спекулятивной буферной памяти 318, чтобы выполнять поиск данных, соответствующих целевому адресу запроса 118 данных. В этом примере, данные, соответствующие целевому адресу запроса 118 данных, содержатся в основном массиве 308 данных, что приводит к удачному обращению в кэш. Данные для запроса 118 данных в основном массиве 308 данных возвращаются в качестве ответа 302 с данными запросчику в процессоре 102. Тем не менее, инструкция, идентифицированная посредством идентификатора 1 инструкции, которая инструктирует запросу 118 данных выдаваться, считается спекулятивной до тех пор, пока индикатор 328 фиксации не принимается посредством неспекулятивной кэш-памяти 114, указывающий иное, как пояснено выше. Контроллер 300 кэша в неспекулятивной кэш-памяти 114 выполнен с возможностью выделять SAR-запись 338(1) в SAR-схеме 336, показанной на фиг. 5A, ассоциированной с идентификатором 1 инструкции, чтобы регистрировать отсрочку обновления состояния кэша в основном массиве 308 данных для запроса 118 данных. Как показано на фиг. 5A идентификатор 1 инструкции сохраняется в идентификаторе 340(1) инструкции SAR-записи 338(1). Поскольку запрос 118 данных приводит к удачному обращению в кэш для основного массива 308 данных в неспекулятивной кэш-памяти 114, набор/путь кэша "12/4" записи 310(0)-310(M) кэша в основном массиве 308 данных, которая содержит данные для запроса 118 данных, сохраняется в MDA-индексе 342(1). В этом отношении, контроллер 300 кэша может позднее находить запись 310(0)-310(M) кэша в основном массиве 308 данных на основе MDA-индекса 342(1), чтобы обновлять свое состояние кэша, когда идентификатор 1 инструкции указывается в качестве зафиксированного согласно принимаемому индикатору 328 фиксации. Следует отметить, что нуль сохраняется в SB-индексе 344(1) для SAR-записи 338(1), поскольку данные для запроса 118 данных находятся в основном массиве 308 данных, а не в спекулятивной буферной памяти 318. Следует отметить, что в этом примере, SAR-запись 338(0) регистрирует местоположение данных для предыдущего запроса данных 118 в SB-индексе 344(0), соответствующем записи 1, в спекулятивной буферной памяти 318. Также следует отметить, что выделяемая SAR-запись 338(0)-338(S) необязательно может быть дополнена посредством контроллера 300 кэша с информацией, связанной с задержанным обновлением политики замещения кэша. Например, SAR-запись 338(0)-338(S) может помечаться в качестве наименее давно используемой (MRU) записи в политике замещения кэша на основе принципа "наиболее давно использованный" (LRU).

[0045] Фиг. 5B иллюстрирует пример приема, посредством процессора 102 на фиг. 5A, индикатора 328 фиксации, идентифицирующего идентификатор 1 инструкции как зафиксированный. В ответ, контроллер 300 кэша выполнен с возможностью выполнять поиск в SAR-схеме 336, чтобы определять то, содержит или нет SAR-запись 338 идентификатор 1 инструкции в идентификаторе 340(0)-340(S) инструкции, чтобы указывать то, что обновление состояния кэша запроса 118 данных, ассоциированного с идентификатором 1 инструкции, отсрочивается. В этом примере, идентификатор 1 инструкции содержится в SAR-записи 338(1) в ответ на принимаемый запрос 118 данных, вызываемый посредством обработки идентификатора 1 инструкции, как проиллюстрировано на фиг. 5A и описано выше. Контроллер 300 кэша выполнен с возможностью, в ответ на определение того, что идентификатор 1 инструкции содержится в SAR-записи 338(1), обновлять состояние 315(0)-315(M) замещения кэша в записи 310(0)-310(M) кэша в основном массиве 308 данных, индексированной посредством MDA-индекса 342(1). Это обусловлено тем, что запись 310(0)-310(M) кэша в основном массиве 308 данных, индексированная посредством MDA-индекса 342(1) для ID инструкции, более не является спекулятивной согласно принимаемому индикатору 328 фиксации. Контроллер 300 кэша может отменять выделение SAR-записи 338(1) в ответ на прием индикатора 328 фиксации, указывающего то, что идентификатор 1 инструкции зафиксирован, чтобы освобождать пространство для регистрации задержанного состояния обновления кэша будущих принимаемых запросов 118 данных.

[0046] Чтобы иллюстрировать пример использования SAR-схемы 336 и спекулятивной буферной памяти 318 в неспекулятивной кэш-памяти 114, чтобы отслеживать зарегистрированные спекулятивные запросы данных и иметь возможность отсрочивать обновление состояния кэша в неспекулятивной кэш-памяти 114 до тех пор, пока запрос данных не станет неспекулятивным, предоставляются фиг. 6A и 6B. Фиг. 6A иллюстрирует выдачу, посредством процессора 102 на фиг. 1, запроса 118 данных, содержащего ID инструкции и целевой адрес, который принимается посредством неспекулятивной кэш-памяти 114, что приводит к неудачному обращению в кэш для основного массива 308 данных и спекулятивной буферной памяти 318. В этом примере, ID инструкции в запросе 118 данных, идентифицирующий инструкцию по обработке, которая инструктирует запросу 118 данных выдаваться, представляет собой идентификатор 7 инструкции. Контроллер 300 кэша в неспекулятивной кэш-памяти 114 выполнен с возможностью выполнять поиск в основном массиве 308 данных и в спекулятивной буферной памяти 318, чтобы выполнять поиск данных, соответствующих целевому адресу запроса 118 данных. В этом примере, данные, соответствующие целевому адресу запроса 118 данных, не содержатся в основном массиве 308 данных или в спекулятивной буферной памяти 318 неспекулятивной кэш-памяти 114. Инструкция, идентифицированная посредством идентификатора 1 инструкции, которая инструктирует запросу 118 данных выдаваться, считается спекулятивной до тех пор, пока индикатор 328 фиксации не принимается посредством неспекулятивной кэш-памяти 114, указывающий иное, как пояснено выше.

[0047] Контроллер 300 кэша в неспекулятивной кэш-памяти 114 выполнен с возможностью выделять доступную запись 320(7) буфера в спекулятивной буферной памяти 318, как показано на фиг. 6A, которая представляет собой индекс 7 в этом примере. Таким образом, данные для запроса 118 данных, ассоциированные с идентификатором 1 инструкции и сохраненные в спекулятивной буферной памяти 318 в спекулятивном состоянии в ответ на принимаемый ответ 306 по заполнению из высокоуровневой памяти, могут извлекаться и устанавливаться посредством контроллера 300 кэша в основном массиве 308 данных, когда запрос 118 данных становится неспекулятивным. Индикатор 332(7) нахождения в кэше в записи 320(7) буфера задается равным "0" в этом примере, что означает то, что данные, ассоциированные с принимаемым запросом 118 данных, не содержатся в основном массиве 308 данных. Неспекулятивный индикатор 330(7) для записи 320(7) буфера задается равным "0", чтобы указывать спекулятивное состояние в этом примере. Допустимый индикатор 334(7) задается равным "1", чтобы указывать то, что запись 320(7) буфера является допустимой в этом примере. Если запись 320(0)-320(B) буфера не доступна в спекулятивной буферной памяти 318, контроллер 300 кэша может быть выполнен с возможностью отправлять индикатор повторной попытки в запросчик в процессоре 102 в качестве ответа 302 с данными, чтобы указывать для запросчика необходимость повторения попытки запроса 118 данных в последующее время. Это предоставляет больше времени для того, чтобы запросы 118 данных с зарегистрированными отсроченными обновлениями состояний кэша, сохраненными в спекулятивной буферной памяти 318, становились неспекулятивными, что в таком случае приводит к тому, что их соответствующие записи 320(0)-320(B) буфера имеют возможность использоваться и/или повторно выделяться, как подробнее описано ниже относительно фиг. 6B.

[0048] Снова со ссылкой фиг. 6A, контроллер 300 кэша в неспекулятивной кэш-памяти 114 также выполнен с возможностью выделять SAR-запись 338(0) в SAR-схеме 336, ассоциированной с идентификатором 1 инструкции, чтобы регистрировать отсрочку обновления состояния кэша в основном массиве 308 данных для запроса 118 данных. Как показано на фиг. 6A идентификатор 1 инструкции сохраняется в идентификаторе инструкции 340(0) SAR-записи 338(0). Поскольку запрос 118 данных приводит к неудачному обращению в кэш, нуль содержится в MDA-индексе 342(0), поскольку данные для запроса 118 данных не сохраняются в основном массиве 308 данных. SB-индекс "7" сохраняется в SB-индексе 344(0) в этом примере, чтобы указывать на запись 320(7) буфера, выделяемую в спекулятивной буферной памяти 318, которая регистрирует спекулятивное состояние запроса 118 данных, ассоциированного с идентификатором 1 инструкции. В этом отношении, контроллер 300 кэша может позднее выполнять поиск в SAR-схеме 336 идентификатор 1 инструкции, когда его запрос ассоциированных данных 118 становится неспекулятивным, чтобы определять запись 320(0)-320(B) буфера, чтобы обновлять свой соответствующий спекулятивный индикатор 330(7) на неспекулятивное состояние. Следует отметить, что нуль сохраняется в MDA-индексе 342(0) для SAR-записи 338(1), поскольку данные для запроса 118 данных не содержатся в основном массиве 308 данных. Контроллер 300 кэша выполнен с возможностью записывать данные для запросов 118 данных, ассоциированных с идентификаторами инструкций, содержащимися в записи 320(0)-320(B) буфера, в спекулятивной буферной памяти 318, которые имеют спекулятивный индикатор 330(7) в качестве неспекулятивного состояния. Фиг. 6B иллюстрирует пример приема, посредством процессора 102 на фиг. 6A, индикатора 328 фиксации, идентифицирующего идентификатор 1 инструкции как зафиксированный. В ответ, контроллер 300 кэша выполнен с возможностью выполнять поиск в SAR-схеме 336, чтобы определять то, содержит или нет SAR-запись 338 идентификатор 1 инструкции в идентификаторе 340(0)-340(S) инструкции, чтобы указывать то, что обновление состояния кэша запроса 118 данных, ассоциированного с идентификатором 1 инструкции, отсрочивается. В этом примере, идентификатор 1 инструкции содержится в SAR-записи 338(0) в ответ на принимаемый запрос 118 данных, вызываемый посредством обработки идентификатора 1 инструкции, как проиллюстрировано на фиг. 6A и описано выше. Контроллер 300 кэша выполнен с возможностью, в ответ на определение того, что идентификатор 1 инструкции содержится в SAR-записи 338(0), обращаться к SB-индексу 344(0), чтобы определять запись 320(0)-320(B) буфера, ассоциированную с идентификатором 1 инструкции. В этом примере, индекс "7" сохраняется в SB-индексе 344(0), чтобы указывать на запись 320(7) буфера в спекулятивной буферной памяти 318. Неспекулятивный индикатор 330(7) задается в качестве неспекулятивного состояния, которое составляет "1" в этом примере. Таким образом, контроллер 300 кэша может записывать данные, ассоциированные с запросом 118 данных для идентификатора 1 инструкции, зарегистрированного в записи 320(7) буфера, в основном массиве 308 данных. Контроллер 300 кэша может ожидать записи данных, ассоциированных с запросом 118 данных для идентификатора 1 инструкции, зарегистрированного в записи 320(7) буфера в основном массиве 308 данных, до тех пор, пока новая запись 320(0)-320(B) буфера не должна выделяться в спекулятивной буферной памяти 318, и отсутствуют пустые записи 320(0)-320(B) буфера. Данные, ассоциированные с запросом 118 данных для идентификатора 1 инструкции, могут оставаться в записи 320(7) буфера, поскольку последующий запрос 118 данных для идентичных данных на основе его целевого адреса может удовлетворяться в качестве удачного обращения в кэш из спекулятивной буферной памяти 318, как описано выше. Когда контроллер 300 кэша записывает данные, ассоциированные с запросом 118 данных, для идентификатора 1 инструкции, зарегистрированного в записи 320(7) буфера, в основном массиве 308 данных, индикатор 332(7) нахождения в кэше должен задаваться с возможностью указывать то, что данные сохраняются в основном массиве 308 данных, посредством индикатора "1". Таким образом, когда контроллер 300 кэша должен выделять новую запись 320(0)-320(B) буфера в спекулятивной буферной памяти 318 для нового запроса 118 данных, контроллер 300 кэша может выполнять поиск записи 320(0)-320(B) буфера, которая имеет индикатор нахождения в кэше, заданный равным "1" в этом примере. Это означает то, что данные для записи 320(0)-320(B) буфера записаны в основной массив 308 данных в качестве неспекулятивных данных, и в силу этого ассоциированная запись 320(0)-320(B) буфера может подвергаться отмене выделения и/или повторно выделяться.

[0049] Относительно SAR-схемы 336 и спекулятивной буферной памяти 318 на фиг. 3, а также обновления спекулятивного состояния отслеживаемого запроса 118 данных на неспекулятивное состояние в примере на фиг. 6B, то, что идентификатор становится неспекулятивным, в конечном счете инициирует контроллер 300 кэша с возможностью записывать данные для запроса 118 данных, ассоциированного с идентификатором инструкции, в основной массив 308 данных. Как пояснено выше, запись 320(0)-320(B) буфера в спекулятивной буферной памяти 318 для ID инструкции, который становится неспекулятивным, и ее преобразованная ассоциированная SAR-запись 338(0)-338(S) должны подвергаться отмене выделения в спекулятивной буферной памяти 318, с тем чтобы обеспечивать их доступность для другого запроса 118 данных. Тем не менее, другие идентификаторы инструкций могут выделяться в SAR-записях 338(0)-338(S) в SAR-схеме 336, которые преобразуются в идентичную запись 320(0)-320(M) буфера в спекулятивной буферной памяти 318. Например, несколько запросов 118 данных могут иметь идентичный целевой адрес. Если запись 320(0)-320(M) буфера в спекулятивной буферной памяти 318, преобразованная в несколько SAR-записей 338(0)-338(S), подвергается отмене выделения, то оставшиеся SAR-записи 338(0)-338(S), преобразованные в идентичную запись 320(0)-320(M) буфера в спекулятивной буферной памяти 318, не будут обладать сведениями в отношении того, что указывается на запись 320(0)-320(M) буфера, которая была подвергнута отмене выделения. Таким образом, ID инструкции, ассоциированный с такими SAR-записями 338(0)-338(S), который позднее становится неспекулятивным, потеряет свое преобразование в спекулятивную буферную память 318, что приведет к невозможности его обновления, представляет собой ассоциированное состояние кэша. Как пояснено ниже, один способ разрешать эту проблему состоит в том, чтобы предоставлять другой уровень косвенности преобразования между SAR-схемой 336 и спекулятивной буферной памятью 318.

[0050] SAR-схема 336, поясненная выше для отслеживания спекулятивного состояния запросов 118 данных, принимаемых посредством неспекулятивной кэш-памяти 114, также может использоваться в комбинации с виртуальной заполняющей буферной (VFB) схемой. Как пояснено в ниже, виртуальная заполняющая буферная (VFB) схема может использоваться для того, чтобы преобразовывать SAR-записи 338(0)-338(S) в записи 320(0)-320(B) буфера в спекулятивной буферной памяти 318. VFB-схема может использоваться для того, чтобы отслеживать то, данные, ассоциированные с записью 320(0)-320(B) буфера в спекулятивной буферной памяти 318, становятся неспекулятивными и записываются в основной массив 308 данных или нет, так что другие идентификаторы инструкций могут оставаться преобразованными в VFB-схему. VFB-схема может отслеживать то, записана или нет запись 320(0)-320(B) буфера в спекулятивной буферной памяти 318, ассоциированная с идентификатором инструкции, остающимся преобразованным из SAR-схемы 336 в VFB-схему, в основной массив 308 данных, так что обновление состояния кэша для таких других преобразованных идентификаторов инструкций может обновляться прямо в основной массив 308 данных, поскольку ее преобразованная ассоциированная запись 320(0)-320(B) буфера в спекулятивной буферной памяти 318 должна подвергаться отмене выделения.

[0051] Следует отметить снова, со ссылкой на неспекулятивную кэш-память 114 на фиг. 3 и в отношении фиг. 6A и 6B, что когда запись 310(0)-310(M) кэша вытесняется из основного массива 308 данных посредством контроллера 300 кэша, контроллер 300 кэша также может обновлять запись 320(0)-320(B) буфера в спекулятивной буферной памяти 318. Например, если конкретная запись 310(0)-310(M) кэша (например, посредством ее набора/пути) в основном массиве 308 данных идентифицируется в качестве записи-жертвы, которая должна вытесняться посредством контроллера 300 кэша, контроллер 300 кэша может быть выполнен с возможностью выполнять поиск в записях 320(0)-320(B) буфера, чтобы определять то, имеются или нет записи 320(0)-320(B) буфера в спекулятивной буферной памяти 318, которые соответствуют вытесненной записи 310(0)-310(M) кэша. Если да, такая соответствующая запись(и) буфера 320(0)-320(B) может признаваться недопустимой посредством задания ее соответствующего допустимого индикатора 334(0)-334(B) в недопустимое состояние (например, в состояние "0"). Таким образом, если новый запрос 118 данных принимается в неспекулятивной кэш-памяти 114, имеющей целевой адрес, соответствующий вытесненной записи 310(0)-310(M) кэша, которая приводит приводить к неудачному обращению в кэш для основного массива 308 данных, то удачное обращение в кэш не должно ложно возникать в спекулятивной буферной памяти 318. В этом отношении, фиг. 7A-7D иллюстрируют пример выдачи, посредством процессора 102 на фиг. 1, запросов 118 данных, принимаемых посредством неспекулятивной кэш-памяти 114 в системе 106 кэш-памяти. В этом примере, неспекулятивная кэш-память включает в себя альтернативную SAR-схему 700, которая может преобразовываться в записи в виртуальной заполняющей буферной (VFB) схеме 708, которая преобразуется в спекулятивную буферную память 318 для отслеживания спекулятивных запросов 118 данных и обновления состояния кэша таких запросов в основном массиве 308 данных, когда они становятся неспекулятивными. В этом примере, как показано на фиг. 7A, три (3) запроса 118 данных выполняются в неспекулятивную кэш-память 114, идентифицированную посредством трех (3) идентификаторов инструкций в качестве идентификаторов 1, 4 и 8 инструкций. Контроллер 300 кэша в неспекулятивной кэш-памяти 114 выполнен с возможностью выполнять поиск в основном массиве 308 данных и в спекулятивной буферной памяти 318 для того, чтобы выполнять поиск данных, соответствующих целевому адресу этих трех запросов 118 данных. В этом примере, данные, соответствующие целевому адресу запроса 118 данных для идентификатора 1 инструкции, не содержатся в основном массиве 308 данных или в спекулятивной буферной памяти 318 неспекулятивной кэш-памяти 114, что приводит к неудачному обращению в кэш. Контроллер 300 кэша выделяет SAR-запись 702(0) в SAR-схеме 700, показанной на фиг. 7A, которая является аналогичной SAR-схеме 336 на фиг. 3. Идентификатор 1 инструкции сохраняется в идентификаторе 704(0) инструкции в SAR-записи 702(0). Контроллер 300 кэша также выделяет VFB-запись 710(7) в VFB-схеме 708, показанной на фиг. 7A. Индекс "7", соответствующий выделяемой VFB-записи 710(7), сохраняется в VFB-индексе 706(0) в SAR-схеме 700, чтобы преобразовывать SAR-запись 702(0) для идентификатора 1 инструкции в VFB-запись 710(7) в VFB-схеме 708. Индикатор 714(7) нахождения в кэше в SAR-записи 702(7) задается в качестве данных, ассоциированных с запросом 118 данных, инициируемым из идентификатора 1 инструкции как не находящимся в основном массиве 308 данных, поскольку запрос 118 данных, связанный с идентификатором 1 инструкции, приводит к неудачному обращению в кэш. Таким образом, MDA-индекс 716(7) в VFB-записи 710(7) задается равным "0" или нулю как не указывающий на местоположение в основном массиве 308 данных. Тем не менее, индекс 718(7) спекулятивного буфера (SB) в VFB-схеме 708 задается в качестве индекса "4", чтобы преобразовывать VFB-запись 710(7) в запись 320(4) буфера в спекулятивной буферной памяти 318, которая содержит данные, принимаемые из ответа 306 по заполнению на выделяемую запись 320(4) буфера в спекулятивной буферной памяти 318.