Уровень техники

Различные существующие и новые вычислительные устройства используют высокоскоростную энергозависимую память (к примеру, динамическое оперативное запоминающее устройство, или DRAM), чтобы хранить рабочие инструкции и данные. Эти устройства включают в себя мобильные телефоны, телевизионные абонентские приставки, память персонального компьютера и т.п. Вычислительные устройства все в большей степени также включают в себя значительные объемы относительно недорогой энергонезависимой флэш-памяти NAND, чтобы сохранять приложения и данные.

Тем не менее, многие существующие основанные на DRAM вычислительные устройства разрабатываются без надлежащих шинных интерфейсов, чтобы поддерживать флэш-память NAND; поддержка флэш-памяти NAND требует затратного и продолжительного переконструирования набора микросхем устройства. Аналогично, большинство флэш-устройств NAND не могут просто добавлять DRAM. Значительные изменения в физической архитектуре устройства требуются для того, чтобы вводить флэш-память в обновленную модель того, чтобы было, к примеру, основанным на DRAM устройством, или наоборот.

Хотя комбинация энергозависимой и энергонезависимой памяти предоставляет преимущества во многих случаях, зачастую затраты на переконструирование набора микросхем устройства слишком дороги/рискованны для производителя, и в результате производитель отказывается от новых признаков и бизнес-моделей, которые в противном случае были бы задействованы за счет наличия энергозависимой и энергонезависимой памяти в устройстве. Дополнительно, отсутствует простой способ использовать существующие архитектурные модели и, например, обновлять существующее основанное на DRAM устройство флэш-памятью NAND; к примеру, вся печатная плата должна быть переконструирована и заменена вместо простого добавления памяти или замены памяти в существующем устройстве (и обновления программного обеспечения соответствующим образом). Более того, существует значительное различие в скоростях шин между энергозависимой и основанной на DRAM памятью.

Сущность изобретения

Данная сущность предусмотрена для того, чтобы в упрощенной форме представить набор примерных идей, которые дополнительно описываются ниже в подробном описании. Эта сущность не предназначена для того, чтобы идентифицировать ключевые признаки или важнейшие признаки заявляемого предмета изобретения, а также не предназначена для того, чтобы быть использованной таким образом, который ограничивает область применения заявляемого предмета изобретения.

Вкратце, различные аспекты предмета изобретения, описанного в данном документе, направлены на гибридное запоминающее устройство, которое включает в себя первый тип памяти (к примеру, энергозависимую память DRAM-типа) и интерфейс, соответствующий первому типу памяти, и второй тип памяти (к примеру, энергонезависимая память флэш-типа). Запоминающее устройство включает в себя контроллер, который соединен с интерфейсом, первым типом памяти и вторым типом памяти. На основе такой информации, как команды и/или адреса памяти, принимаемой в интерфейсе, контроллер определяет, направлена ли команда, такая как запрос ввода-вывода (к примеру, чтение или запись) на первый тип памяти или второй тип памяти.

Таким образом, посредством приема команд, адресов и данных в контроллере гибридного запоминающего устройства доступ к различным типам памяти может осуществляться посредством программного обеспечения (к примеру, микропрограммного обеспечения устройства или программы) посредством одного интерфейса, заданного для одного типа памяти. Контроллер включает в себя логику, которая определяет, направлена ли команда/адрес, принимаемый по интерфейсу первого типа памяти, на второй тип памяти, ассоциативно связанный с запоминающим устройством, и, если так, выводит сигналы во второй тип памяти, чтобы передавать, по меньшей мере, одну команду во второй тип памяти и/или выполнять, по меньшей мере, одну операцию ввода/вывода (I/O) данных для второго типа памяти.

Другие преимущества могут стать очевидными из последующего подробного описания при рассмотрении совместно с чертежами.

Краткое описание чертежей

Настоящее изобретение проиллюстрировано в качестве примера, а не ограничения на прилагаемых чертежах, на которых аналогичные ссылки обозначают аналогичные элементы и на которых:

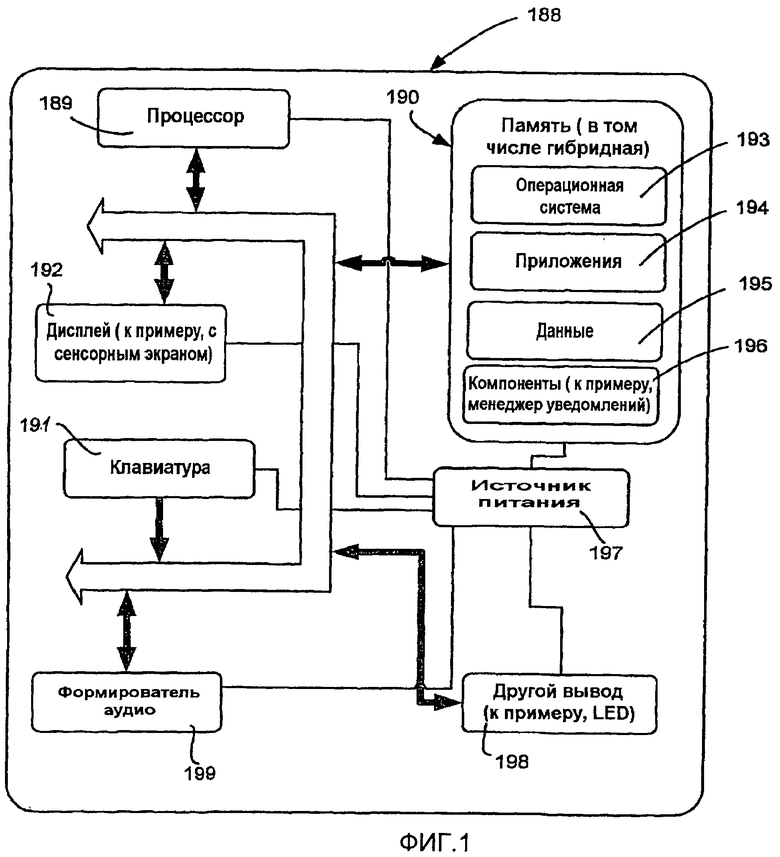

Фиг.1 показывает иллюстративный пример вычислительного устройства, в которое могут быть включены различные аспекты настоящего изобретения.

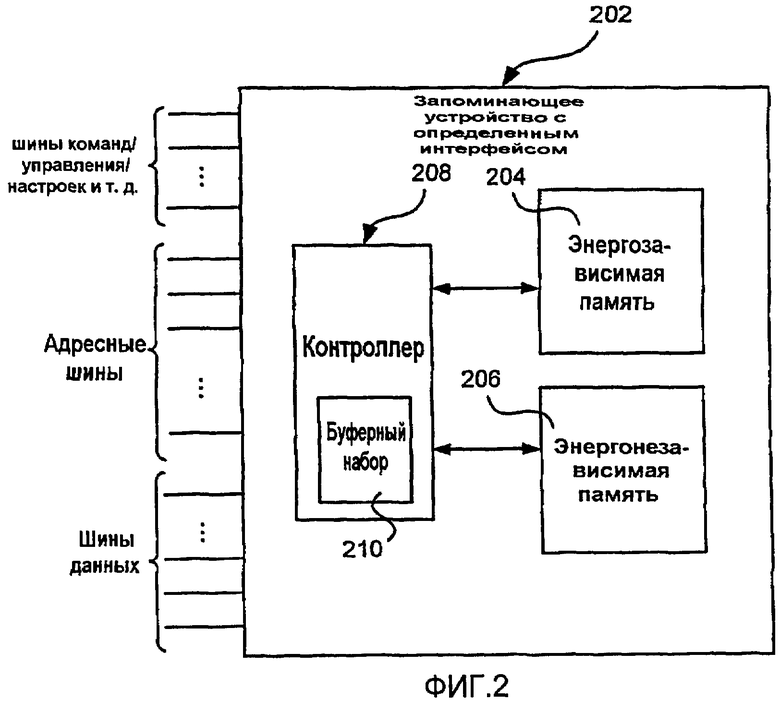

Фиг.2 - это представление примерного гибридного запоминающего устройства, включающего в себя контроллер и два типа памяти, к каждому из которых можно осуществлять доступ посредством единого интерфейса, заданного для одного из типов памяти.

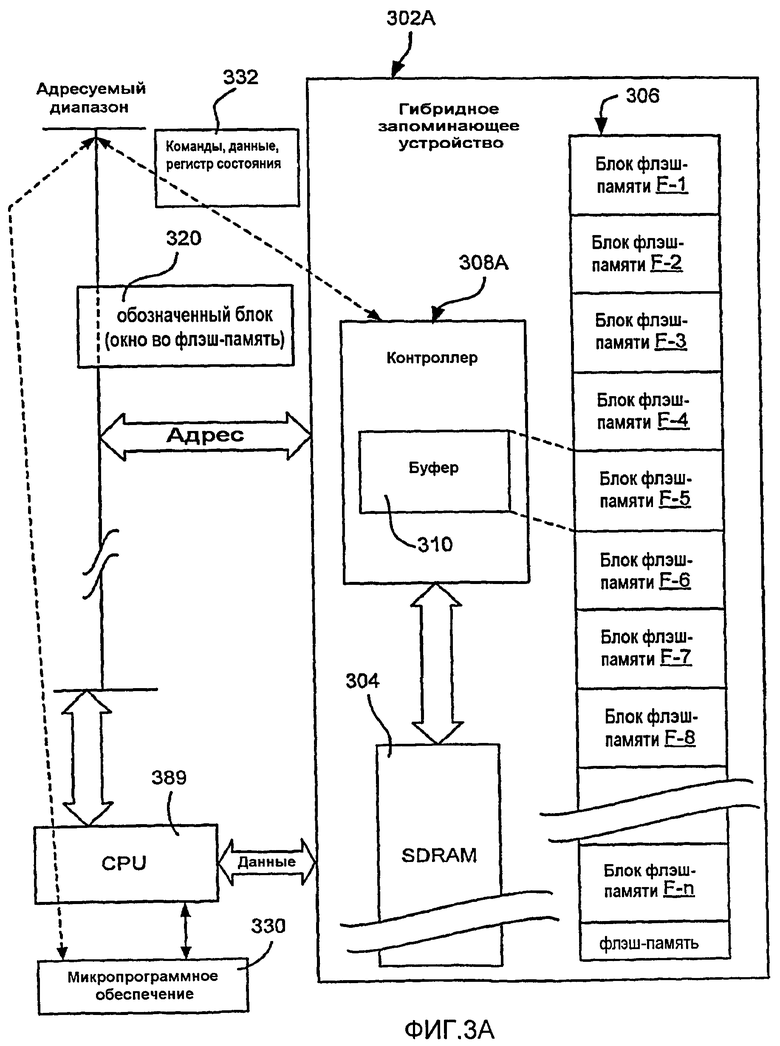

Фиг.3A - это представление примерного гибридного запоминающего устройства с SDRAM-интерфейсом с SDRAM и флэш-памятью, доступ к которому осуществляется посредством обозначенного блока памяти в адресуемом пространстве SDRAM.

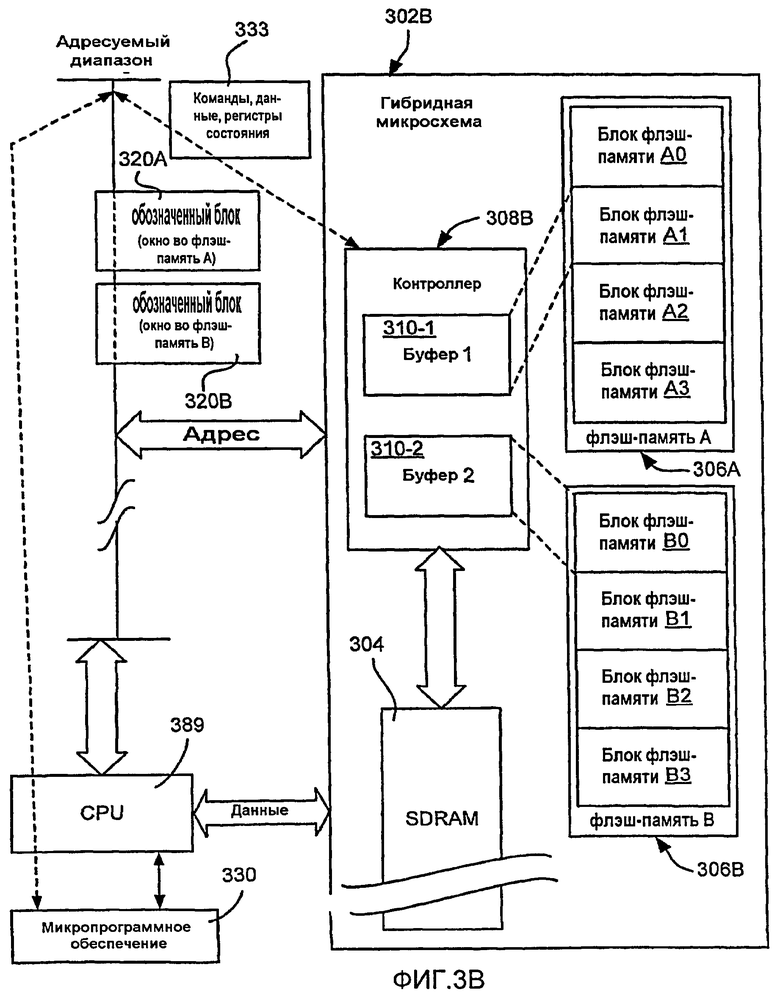

Фиг.3B - это представление примерного гибридного запоминающего устройства с SDRAM-интерфейсом с SDRAM и флэш-памятью, доступ к которому осуществляется посредством множества обозначенных блоков памяти в адресуемом пространстве SDRAM.

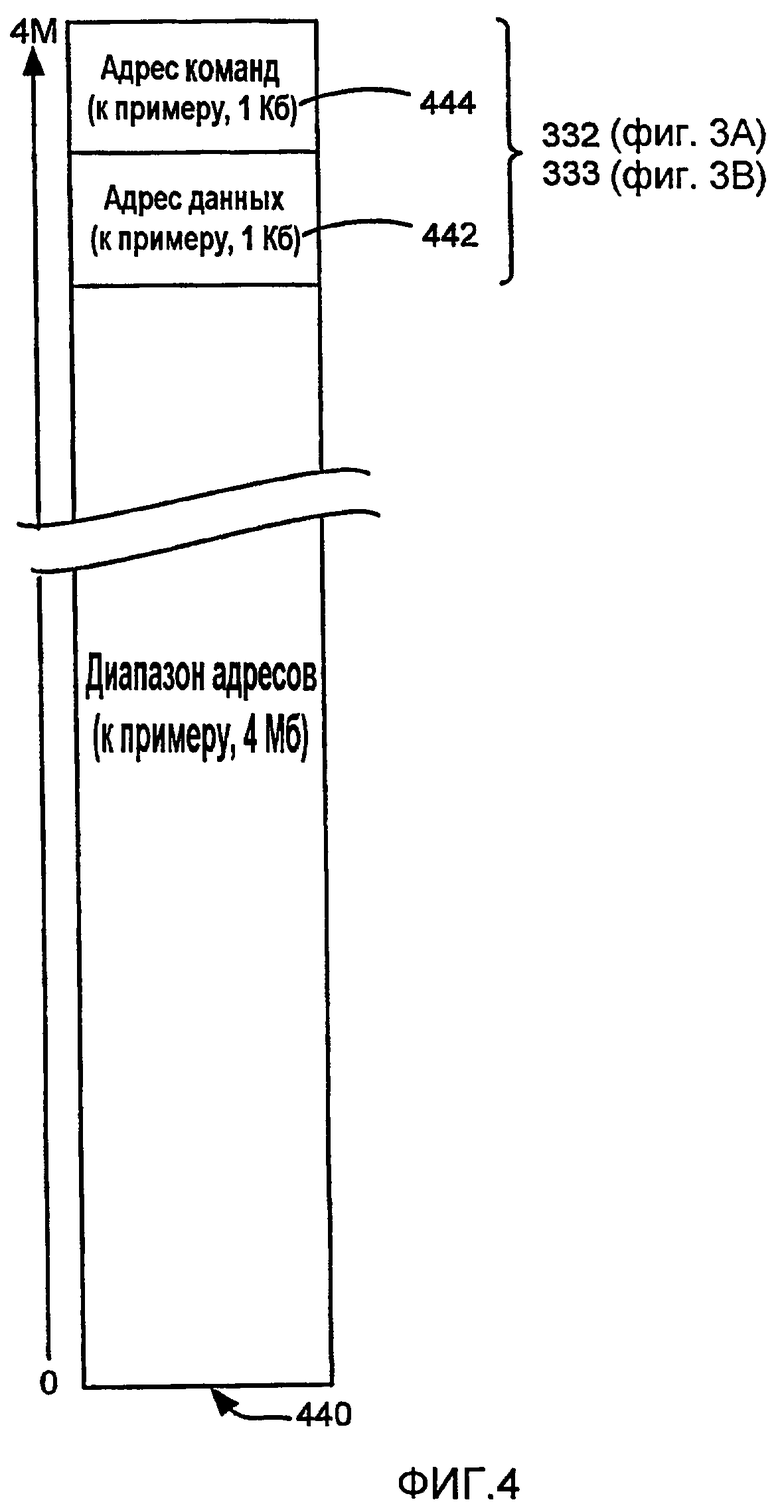

Фиг.4 - это представление адресуемого пространства памяти, соответствующего второму типу памяти, с секциями, используемыми для обмена данными и командами со вторым типом памяти.

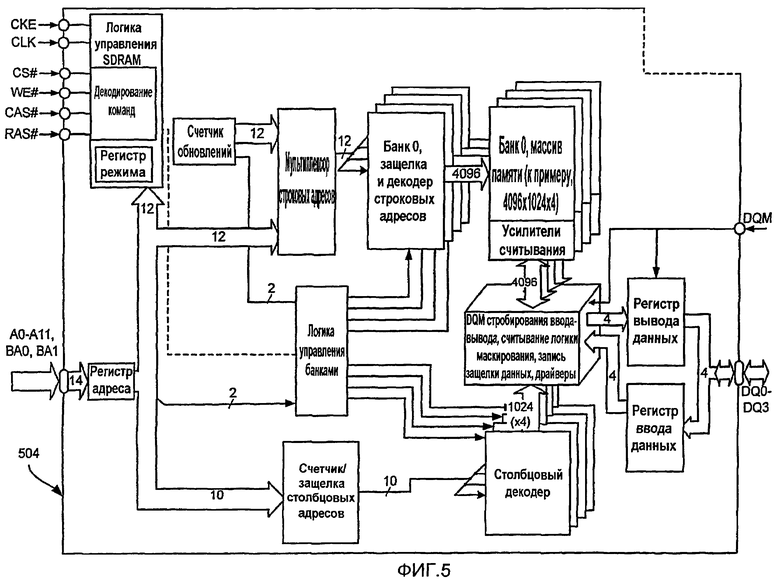

Фиг.5 - это примерное представление одного подходящего типа SDRAM-устройства, которое может быть включено в гибридное запоминающее устройство.

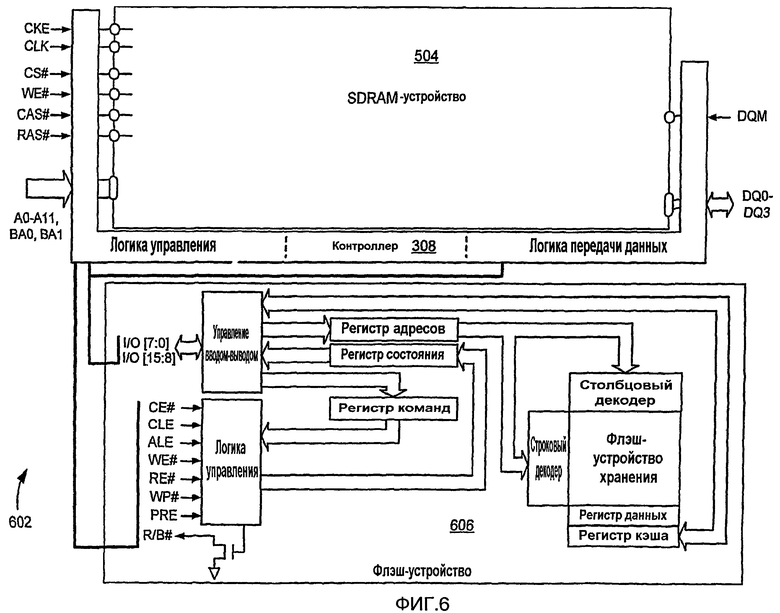

Фиг.6 - это примерное представление гибридного запоминающего устройства с SDRAM-интерфейсом, содержащего SDRAM-устройство, такое как устройство по фиг.5, и флэш-устройство.

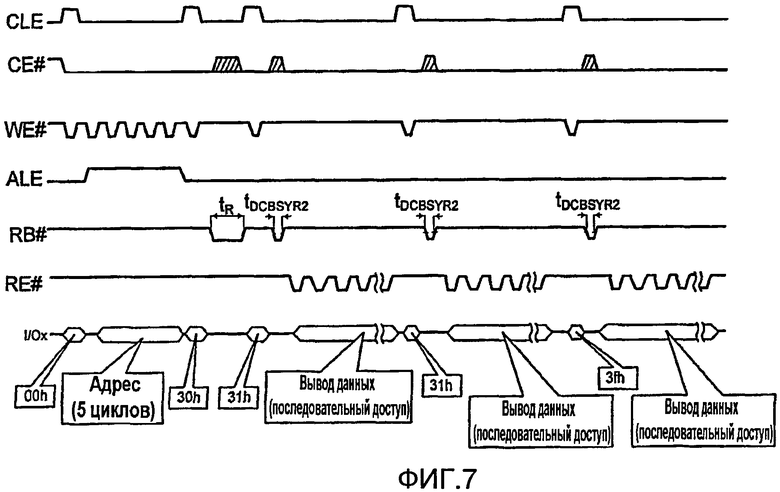

Фиг.7 - это примерное представление временной схемы управления SDRAM-устройством и флэш-устройством.

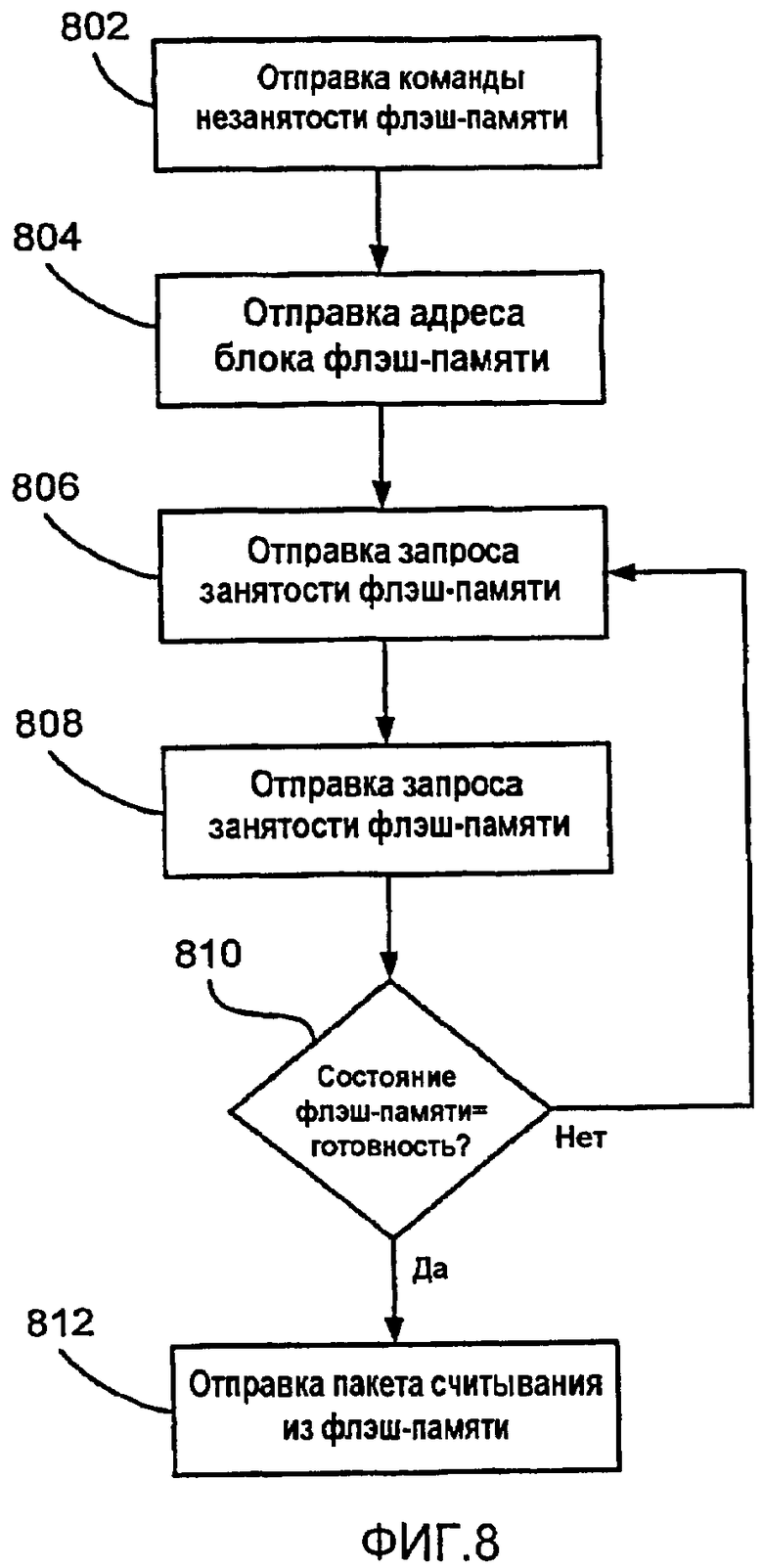

Фиг.8 - это представление примерных этапов, соответствующих тому, как контроллер может выводить флэш-данные в SDRAM-устройство, сконфигурированное для пакетного вывода данных.

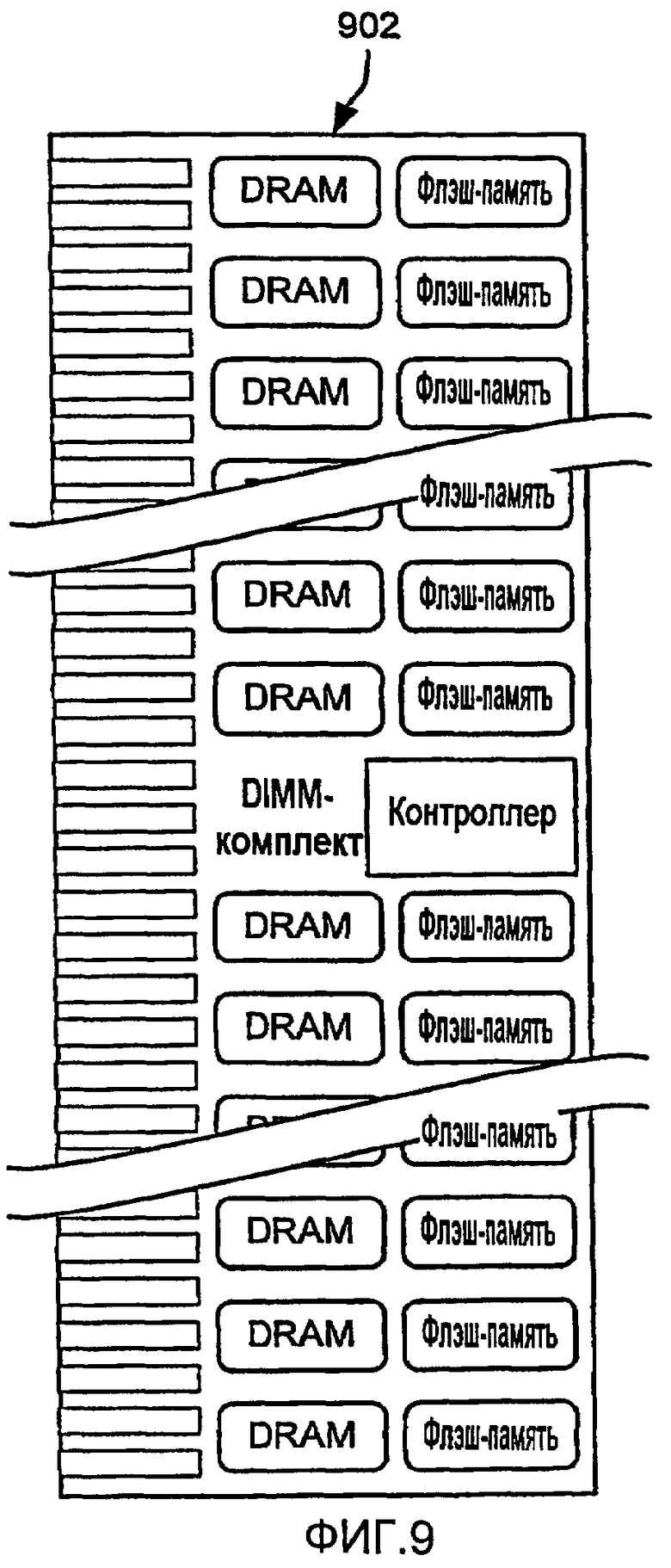

Фиг.9 - это представление того, как флэш-память может быть добавлена в модуль памяти с двухрядным расположением выводов (DIMM) для добавления флэш-памяти в основанную на DRAM (в том числе SDRAM) память персонального компьютера.

Подробное описание изобретения

Примерное операционное окружение

Фиг.1 иллюстрирует пример некоторых подходящих функциональных компонентов вычислительного устройства 188, например, которые могут быть обнаружены в портативном/карманном/планшетном персональном цифровом устройстве, приборе, мобильном телефоне и т.п., включая процессор 189, память 190, дисплей 192 и клавиатуру 191 (которая может быть физической или виртуальной клавиатурой). Память 190, в общем, включает в себя энергозависимую память (к примеру, RAM) и энергонезависимую память (к примеру, ROM, PCMCIA-карты и т.п.). Дополнительно, как описано ниже, примерная память 190 включает в себя гибридное запоминающее устройство (соответствующее одной или более микросхем), которое содержит более одного типа памяти, такой как флэш-память и DRAM или флэш-память и SDRAM (синхронное DRAM), причем один из типов совместно использует интерфейс другого. Операционная система 193 может размещаться в памяти 190 и приводится в исполнение в процессоре 189, например основанная на Microsoft® Windows® операционная система или другая операционная система.

Одна или более прикладных программ 194 и данных 195 могут быть в памяти 190, к примеру, с программами 194, выполняемыми в операционной системе 193. Примеры приложений включают в себя программы электронной почты, программы планирования, программы PIM (персональной информационной системы), программы текстовых процессоров, программы электронных таблиц, программы Интернет-обозревателей и т.п. Вычислительное устройство 188 также может включать в себя другие компоненты 196, такие как менеджер уведомлений, загруженный в память 190, который приводится в исполнение в процессоре 189. Менеджер уведомлений, например, может обрабатывать запрос уведомления, к примеру, от прикладных программ 194.

Вычислительное устройство 188 имеет источник питания 197, к примеру, реализованный как один или более аккумуляторов или система с питанием от источника света. Источник 197 питания дополнительно может включать в себя внешний источник питания, который замещает или перезаряжает встроенные аккумуляторы, такой как адаптер переменного тока или стыковочная станция с питанием.

Примерное вычислительное устройство 188, представленное на фиг.1, показано с тремя примерными типами внешних устройств вывода, включая дисплей 192, другие механизмы 198 вывода (к примеру, один или более светодиодов, или LED) и формирователь 199 аудио, к примеру, подключенный к интегрированной акустической системе и/или к гнезду для наушников. Одно или более из этих устройств вывода может быть напрямую подключено к источнику 197 питания, так что когда активировано, оно остается включенным на продолжительность, диктуемую механизмом уведомлений, даже если процессор 189 и другие компоненты, возможно, отключены для экономии питания аккумуляторов. Например, LED может оставаться включенным (пока некоторая энергия доступна) до тех пор, пока пользователь не выполнит действие. Другие могут быть сконфигурированы так, чтобы отключаться, когда остальная система отключается или через какой-то конечный промежуток времени после активации.

Гибридное запоминающее устройство с единым интерфейсом

Различные аспекты технологии, описанной в данном документе, в общем, направлены на расширение памяти вычислительного устройства (такого, как устройство 188) в отношении наличия относительно больших объемов энергозависимой и энергонезависимой памяти в вычислительном устройстве без необходимости изменений существующей физической архитектуры этого вычислительного устройства. В общем, описание в данном документе предоставляет примеры включения флэш-памяти NAND в основанное на SDRAM устройство посредством добавления или замены гибридного запоминающего устройства (к примеру, содержащего одну или более микросхем), содержащего SDRAM и флэш-память NAND, при этом гибридное запоминающее устройство имеет такой же интерфейс (включая схему расположения выводов, протокол напряжения и протокол доступа), что и традиционный компонент SDRAM. Тем не менее, следует понимать, что эти аспекты и принципы применяются к любому типу или типам энергозависимой и/или энергонезависимой памяти, к примеру, различные типы DRAM (к примеру, EDO) могут быть использованы вместо SDRAM, наоборот, DRAM или SDRAM может быть встроено в флэш-устройство, основанная на NOR флэш-память может быть совмещена с SDRAM и/или с основанной на NAND флэш-памятью, статическое RAM (SRAM) или другие типы RAM могут быть одним из типов памяти, дополнительная энергозависимая память может быть добавлена вместо существующего энергозависимого запоминающего устройства, дополнительная энергонезависимая память может быть добавлена вместо существующего энергонезависимого запоминающего устройства и т.п. Отметим, что включение различных типов памяти в гибридное запоминающее устройство (с интерфейсом, который обычно соответствует исходному типу памяти для данной конструкции) типично добавляет общую память в устройство, необязательно увеличивает (а если требуется посредством конструктора, может уменьшать) объем исходного типа памяти и/или общий объем памяти.

Более того, следует понимать, что принципы, описанные в данном документе, не ограничены тем, что считается традиционными вычислительными устройствами (к примеру, настольные, блокнотные, дорожные или планшетные вычислительные системы, персональные цифровые устройства, карманные персональные компьютеры и т.п.), а, наоборот, могут быть использованы в любом устройстве, которое имеет потребность в хранении данных в энергозависимой или энергонезависимой памяти, включая мобильные телефоны, телевизионные абонентские приставки, гибридные жесткие диски, телевизоры, пульты дистанционного управления, аудиовизуальные устройства, электрические приборы, бытовую технику и т.п. Каждое из этих устройств может добавлять энергонезависимую память в конструкцию энергозависимой памяти или, наоборот, увеличивать память без затратного и рискового переконструирования аппаратных средств. Таким образом, например, устройство с энергозависимой памятью, такое как мобильный телефон, теперь может иметь большие объемы энергонезависимого устройства хранения, включенные в нее с тем, чтобы сохранять программы, музыку, изображения и т.п., просто посредством замены микросхемы памяти (или нескольких микросхем памяти) и обновления определенного микропрограммного обеспечения, чтобы работать с энергонезависимым устройством хранения, как описано ниже.

По сути, настоящее изобретение не ограничено примерами, структурами или функциональностью, описанной в данном документе. Наоборот, любые из примеров, структур или функциональностей, описанных в данном документе, являются неограничивающими, и настоящее изобретение может быть использовано различными способами, которые предоставляют выгоды и преимущества в вычислениях и хранении данных в общем.

Обращаясь к фиг.2 из чертежей, показан общий примерный принцип гибридного запоминающего устройства 202, включающего в себя энергозависимую память 204 (к примеру, SDRAM) и энергонезависимую память 206 (к примеру, флэш-память NAND). Контроллер 208 содержит логику, которая определяет, к какой памяти 204 или 206 осуществлять доступ, на основе адресов и команд, к примеру, исходящих из микропрограммного обеспечения/программного обеспечения и адресуемых посредством CPU.

Как представлено на фиг.2, контроллер 208 может включать в себя или иным образом быть ассоциативно связанным с буферным набором 210, содержащим один или более буферов, которые в одной реализации используются для целей согласования скорости. Например, сегодня SDRAM значительно быстрее, чем флэш-память, и тем самым гибридная микросхема памяти, которая имеет интерфейс, который представляется для внешних компонентов как SDRAM-устройство, должна буферизовать данные в буферном наборе 210 (к примеру, SDRAM, DRAM или SRAM), чтобы соответствовать протоколу SDRAM в отношении требований по скорости и выводу, включая требования пакетного режима. Таким образом, буферный набор 210 типично содержит память, такую как SDRAM или статическое RAM (SRAM), которая является, по меньшей мере, такой же быстрой, как требует данная микросхема SDRAM и ее протокол, в противном случае гибридное устройство иногда представляется для внешних компонентов как дефектная память. Отметим, что гибридному запоминающему устройству, которое добавило быструю память (к примеру, SDRAM) в более медленный (к примеру, флэш) интерфейс, не обязательно требуется такой буфер.

Фиг.3A иллюстрирует примерный принцип того, как, в общем, работает одно гибридное запоминающее устройство 302A, в котором флэш-память 306 скомпонована как определенное число блоков (к примеру, блоки от F-1 до F-n) и доступ к ней осуществляется посредством интерфейса SDRAM. Гибридное запоминающее устройство 302A также включает в себя SDRAM-устройство 304. Как описано ниже, находящийся на микросхеме контроллер 308A (к примеру, соответствующий контроллеру 208 по фиг.2) определяет то, к какой секции SDRAM 304 или флэш-памяти осуществить доступ, относительно текущего адреса, исходящего из CPU 389. В общем, контроллер 308A принимает из CPU 389 команды, данные и адреса, которые выводятся согласно традиционному протоколу SDRAM. Отметим, что CPU не обязательно должен знать что-либо о различных типах памяти на гибридной микросхеме и работает как обычно по текущей основанной на SDRAM шине.

На фиг.3A контроллер 308 включает в себя логику, которая позволяет обнаруживать адреса, отправляемые в адресные шины SDRAM гибридного устройства, которые являются частью его интерфейса. Некоторые из адресов в адресуемом диапазоне адресов соответствуют SDRAM, и для этих адресов контроллер 308A предоставляет возможность обработки адресов, команд и данных посредством SDRAM-устройства 304 (к примеру, перенаправляет эквивалентные единицы и нули или не отключает видимость единиц и нулей посредством устройства). Как результат, для этих адресов гибридное устройство выступает как традиционное SDRAM-устройство.

Тем не менее, определенные адреса в адресуемом диапазоне (типично содержащем непрерывный диапазон, указанный в данном документе как обозначенный блок 320) известны контроллеру 308 как ассоциативно связанные с флэш-памятью и, в сущности, выступают в качестве окна во флэш-память 306. Например, обозначенный блок может соответствовать размеру блока флэш-памяти, к примеру, 128 кб в одном типе флэш-устройства. Когда адреса в пределах обозначенного блока 320 передаются, SDRAM-устройство 304 отключается (фактически или практически) посредством контроллера 308. Контроллер 308 вместо этого отправляет команды в устройство 306 флэш-памяти или контролирует поток данных считывания и записи в устройстве 306 флэш-памяти. В зависимости от конструкции контроллер 308 может отключить SDRAM-компонент 304 посредством изменения соответствующей входной шины (к примеру, активации микросхемы) устройства 304 так, чтобы отключить посредством неперенаправления принимаемых адресов в устройство 304 и/или посредством перенаправления адресов (к примеру, если требуются для обновления), но не разрешения записи данных или возврата каких-либо данных для считывания.

Отметим, что объем флэш-памяти 306 не ограничен размером назначенного блока 320; наоборот, может быть несколько блоков флэш-памяти (или других компоновок флэш-памяти), причем контроллер 308 осуществляет доступ к каждому блоку и т.п. согласно традиционной информации отображения, которая идентифицирует то, к какой части (к примеру, блоку) всей флэш-памяти 306 должен быть осуществлен доступ. Дополнительная информация преобразования может быть записана в другие ячейки памяти, известные контроллеру 308, к примеру в верхнюю часть адресуемой памяти (или, возможно, в качестве дополнения в назначенный блок). Микропрограммное обеспечение 330, уже присутствующее фактически на всех вычислительных устройствах, может быть обновлено так, чтобы считывать и записывать эту информацию в соответствии с надлежащим протоколом посредством CPU 389 (как представлено на фиг.3A посредством пунктирных линий от микропрограммного обеспечения 330 через CPU 389 к контроллеру 308A; таким образом, команды, данные и информация 332 состояния может передаваться между микропрограммным обеспечением 330 устройства (и/или другим запрашиваемым кодом, далее для простоты упоминаемым как микропрограммное обеспечение 330) и гибридным запоминающим устройством 302A.

Фиг.3B - это представление принципа, аналогичного принципу по фиг.3A за исключением того, что на фиг.3B альтернативный контроллер 308B может иметь несколько буферов 310-1 и 310-2, соответствующих нескольким окнам 320A и 320B, отдельно преобразуемых в несколько блоков флэш-памяти (к примеру, в данный момент в блок флэш-памяти A1 и блок флэш-памяти B0 на фиг.3B). Можно легко принять во внимание, что, хотя только два таких параллельных (и тем самым типично более быстрых) доступа к устройствам флэш-памяти показаны на фиг.3B, может быть использовано любое осуществимое число.

В качестве примера того, как контроллер преобразует окно (фиг.3A) или окна (фиг.3B) в корректную секцию или секции флэш-памяти, фиг.4 иллюстрирует линейно представляемый диапазон 440 адресов, соответствующий диапазону традиционного SDRAM-устройства, который в данном примере составляет 4 Мслова по 16 битов. Для простоты отображение описывается относительно одного назначенного блока 320 по фиг.3A, тем не менее, можно легко понять, что отдельное отображение может быть выполнено фактически таким же образом.

В примере по фиг.4 последние два блока, соответствующие адресному пространству SDRAM, используются посредством контроллера 308 и микропрограммного обеспечения 330 в качестве канала 444 команд и канала 442 данных в устройстве 306 флэш-памяти. Информация отображения и другая информация 332 (фиг.3) в этих блоках 442 и 444 может считываться и записываться посредством контроллера 308 посредством любого надлежащего протокола, понимаемого контроллером 308 и источником этой дополнительной информации (к примеру, кодом 330 микропрограммного обеспечения). Таким образом, посредством осуществления доступа к дополнительной информации 332 (или 333 на фиг.3B) в контроллере 308, к примеру, последним двум блокам слов по одному килобайту устанавливаются пути команд и данных для связи с флэш-устройством 306. Другая информация также может быть в этих областях. Например, микропрограммное обеспечение 330 устройства может использовать эту секцию памяти для того, чтобы использовать протокол самозагрузки, посредством которого микропрограммное обеспечение 330 может определять, является ли запоминающее устройство истинно гибридным устройством, поскольку, в общем, гибридное запоминающее устройство 302A по фиг.3 в иных отношениях должно быть не отличимым от традиционного SDRAM-устройства. Другие возможные данные, передаваемые посредством этих блоков, могут, к примеру, информировать контроллер 308A о том, где назначенный блок 320 (или блоки на фиг.3B) размещается в пределах адресуемой памяти; к примеру, таким образом, назначенные блоки могут перемещаться, в том числе динамически, при необходимости.

Обращаясь к пояснению работы одного примерного запоминающего устройства, один надлежащий протокол команд содержит последовательный протокол, используемый для того, чтобы передавать блок адресов и информацию команд (к примеру, 332 на фиг.3A) для флэш-устройства. Отметим, что, поскольку контроллер 308A отвечает за трансляцию информации команд и адресов, протокол конфигурируется так, чтобы осуществлять доступ к различным типам флэш-устройств; к примеру, один тип устройства NAND использует интерфейс NOR SRAM, посредством которого управляющая логика осуществляет доступ к блокам данных, которые затем переводятся в последовательную форму, чтобы соответствовать протоколу доставки SDRAM-данных. Запись данных во флэш-память 306 аналогично должна быть преобразована посредством контроллера 308A так, как требуется посредством флэш-протокола, к примеру, 2 кб записываются единовременно в одно такое флэш-устройство.

Можно легко принимать во внимание, что, поскольку SDRAM в настоящее время на один или более порядков быстрее флэш-памяти, протокол включает в себя способ для контроллера 308A сообщать в микропрограммное обеспечение 330, когда запрос считывания или записи занят, а когда запрос готов. Может быть использован регистр состояния в ячейке 332. Например, микропрограммное обеспечение 330 отправляет команду считывания или записи через блок 332 команд; состояние, которым может быть бит, который является частью команды, задается посредством контроллера при приеме запроса флэш-памяти равным нулю, чтобы указать занятость. Отметим, что контроллер 308A не должен переключать состояние на занятость, если при запросе считывания контроллер 308A знает, что назначенный блок уже содержит корректные данные для текущего отображения.

В типичной ситуации контроллер 308A задает состояние как "занятость" и "для считывания" и начинает заполнение буфера 310 запрошенными данными. Когда буфер содержит корректные данные (которых может быть больше запрошенных в ожидании последующего запроса считывания), контроллер 308A переключает состояние на готовность. Микропрограммное обеспечение 330, которое опрашивает состояние, поскольку оно отправляет запрос, в таком случае знает, что могут быть считаны запрошенные данные, которые контроллер 308A далее выводит из буфера 310. Например, в соответствии с протоколом SDRAM контроллер должен выводить один набор данных (к примеру, байт) для запрошенного адреса, если один вывод запрошен, или временной пакетный вывод нескольких наборов данных, начиная с этого адреса, при этом число выводимых наборов соответствует текущему пакетному режиму. Отметим, что текущий пакетный режим может быть установлен через аппаратно реализованную настройку, в том числе настройку, которая указывает то, что пакетный режим управляется программно; в любом случае режим известен контроллеру 308A через SDRAM-эквивалентные настроечные шины и/или команду (для программно управляемого пакета).

Записи обрабатываются аналогично, при этом данные в назначенном блоке копируются посредством контроллера 308A в буфер 310, при этом контроллер предоставляет сигнал занятости, который опрашивается посредством микропрограммного обеспечения до тех пор, пока запрос записи не будет фактически выполнен посредством записи в более медленную флэш-память. Как в случае запроса считывания, для запроса записи гибридное запоминающее устройство 302A представляется для CPU 389 как работающее на корректных скоростях SDRAM, и CPU не знает ни о каких опрашиваниях состояний, осуществляемых между микропрограммным обеспечением 330 и контроллером 308A. Посредством протокола синхронная память, таким образом, управляется корректно с точки зрения CPU, но фактически управляется асинхронно с точки зрения запрашивающего объекта.

Таким образом, посредством добавления контроллера памяти в гибридное запоминающее устройство, содержащее SDRAM и флэш-память со стандартным SDRAM-интерфейсом, флэш-память накладывается на адресное пространство SDRAM. Протокол команд (к примеру, последовательный) используется для того, чтобы управлять отображением флэш-блоков/страниц в адресное пространство SDRAM. Это дает возможность одному совместимому по выводам комплекту многокристальной интегральной микросхемы заменять существующее SDRAM-устройство в любом вычислительном устройстве, которое хочет предоставлять флэш-устройство хранения, но при этом с помощью только изменений в микропрограммном обеспечении устройства. Например, буфер традиционного дискового накопителя может быть заменен с помощью одного обновления микросхемы, которое предоставляет флэш-устройство хранения, посредством чего флэш-устройство хранения может быть использовано с новым микропрограммным обеспечением, чтобы модернизировать существующие накопители до гибридных накопителей. Дополнительные примеры включают в себя добавление энергонезависимого устройства хранения в конструкцию телевизионной абонентской приставки или в конструкцию мобильного телефона, который в свое время был сконструирован без встроенного устройства хранения большой емкости, но сегодня оно желательно вследствие определенного нового варианта применения бизнес-модели.

В качестве примера конкретной архитектуры фиг.5 и 6 демонстрируют использование фактических флэш-устройств SDRAM и NAND с интерфейсом и внутренними компонентами, сконфигурированными для одного примерного протокола напряжения SDRAM и протокола доступа SDRAM, в которых требуются только изменения в программном обеспечении (к примеру, в микропрограммном обеспечении устройства) для того, чтобы применять энергонезависимую память в комплекте. Тем не менее, следует понимать, что может быть использовано, в сущности, любое устройство с заданными характеристиками адресации. Отметим, что архитектура на фиг.5 и 6 показывает применение 16-битовых путей данных, что является стандартным вариантом использования, хотя легко можно принять во внимание, что другая ширина путей данных работает таким же образом. В этом примере описывается комплект многокристальной интегральной микросхемы, который может физически заменить микросхему SDRAM в вычислительном устройстве и при этом включает в себя как энергозависимую SDRAM-память, так и энергонезависимую флэш-память NAND.

SDRAM-устройство 504, представленное на фиг.5, содержит устройство пакетного режима (к примеру, устройство Micron MT48LC4M16A2), поддерживающее 1-байтовые, 2-байтовые, 8-байтовые или постраничные передачи, и, например, может быть использовано в гибридном запоминающем устройстве 602 (фиг.6), которое включает в себя два гигабита флэш-памяти 606 NAND. Как представлено в этой примерной архитектуре для SDRAM-устройства по фиг.5, как в случае с традиционным SDRAM-устройством, гибридное запоминающее устройство допускает сигналы RAS/CAS (хорошо известный строб строкового доступа и строб столбцового доступа) по адресным шинам (к примеру, A0-A11, BA0-BA1) и для отличных от однобайтовых считываний и записей считывает или записывает данные последовательно с начального адреса RAS/CAS. Отметим, что вычислительное устройство, которое использует этот тип памяти, буферизует данные с последовательным доступом, что типично выполняется посредством встроенного кэша во многих вычислительных устройствах.

Поскольку данные предоставляются последовательно на основе начального адреса, контроллер 308 памяти (с относительно небольшой задержкой) между узловым устройством (к примеру, CPU) и SDRAM 504 может обнаруживать адреса, отправляемые в микросхему. Посредством обнаружения конкретных диапазонов адресов CE# (активировать) для интерфейса SDRAM может быть использована, чтобы перевести устройство 504 в цикл обновления с данными, предоставляемыми посредством другого источника.

На фиг.5 управляющая логика контроллера 308 обнаруживает адреса, отправляемые в SDRAM. Как описано выше, когда адреса в обозначенном блоке передаются, контроллер знает, что запрос предназначен для флэш-памяти; отметим, что в этой примерной архитектуре SDRAM-устройство отключено посредством предотвращения передачи CE# в устройство. Управляющая логика контроллера затем может либо отправлять команды во флэш-устройство 606, либо через логику передачи данных управлять потоком данных считывания и записи во флэш-устройство. Отметим, что поток команд в SDRAM-устройство не прерывается, и инициализация устройства с комплектом многокристальной интегральной микросхемы требует только того, чтобы управляющая логика обнаруживала работающий пакетный режим, чтобы SDRAM понимала пакеты данных, которые должны быть использованы при передаче данных флэш-памяти в шину данных памяти.

Таким образом, в этой архитектуре, в которой адреса отправляются в SDRAM посредством передач RAS/CAS по отдельной адресной шине, посредством обнаружения циклов RAS/CAS в управляющей логике команды и данные могут передаваться в и из флэш-памяти 606 соответствующим образом. Последовательный протокол записей в командный блок для флэш-памяти 606 дает возможность поддержки протокола флэш-устройства.

Флэш-устройство, представленное на фиг.6 (к примеру, устройство Micron MT29F2G16AABWP) имеет мультиплексированную шину, посредством которой ввод-вывод данных, адреса и команды совместно используют одни контакты. Отметим, что контакты ввода-вывода I/O[15:8] используются только для данных в конфигурации xl6, причем адреса и команды предоставляются по I/O[7:0]. Командная последовательность обычно включает в себя цикл командной защелки, цикл адресной защелки и цикл данных, считывания или записи. Управляющие сигналы CE#, WE#, RE#, CLE, ALE и WPP# управляют операциями считывания и записи флэш-устройства. Отметим, что в другой флэш-памяти, к примеру, в устройстве Micron Gb MT29F8G08FAB, CE# и CE2#, каждый, управляют независимыми 4-гигабайтными массивами. CE2# функционирует так же, как CE#, для собственного массива, и операции, описанные в CE#, также применяются к CE2#.

CE# используется для того, чтобы активировать устройство. Когда CE# небольшое и устройство не находится в состоянии занятости, флэш-память принимает команды, данные и информацию адресов. Когда устройство не совершает операции, контакт CE# типично переводится в высокое состояние и устройство переходит в режим ожидания. Память переходит в режим ожидания, если CE# переходит в высокое состояние в то время, когда передаются данные, и устройство не занято. Это помогает уменьшить энергопотребление.

Операция CE# "Don't Care" позволяет флэш-памяти NAND размещаться на той же шине асинхронной памяти, что и другая флэш-память или SRAM-устройства. Доступ к другим устройствам на шине памяти затем может осуществляться в то время, когда флэш-память NAND занята внутренними операциями. Это возможность предназначена для конструкций, которые требуют нескольких NAND-устройств на одной шине, к примеру, одно устройство может программироваться в то время, когда другое считывается. Высокий сигнал CLE указывает то, что осуществляется командный цикл. Высокий сигнал ALE означает, что происходит цикл ввода адреса. Команды записываются в регистр команд по переднему фронту WE#, когда CE# и ALE низкие, а CLE высокий и устройство не занято. Исключениями в это является команды считывания состояния и сброса.

С помощью этого конкретного компонента команды передаются в регистр команд по переднему фронту WE#; команды вводятся только в шины I/O[7:0]. Для устройств с интерфейсом xl6 в шины I/O[15:8] должны быть записаны нули при выдаче команды. Адреса записываются в регистр адресов по переднему фронту WE#, когда CE# и CLE низкие, а ALE высокий и устройство не занято. Адреса вводятся только в I/O[7:0]; для устройств с интерфейсом xl6 в I/O[15:8] должны быть записаны нули при выдаче адреса. В общем, все пять адресных циклов записываются в устройство. Исключением из этого является команда стирания блока, которая требует только три адресных цикла.

Флэш-устройство, приведенное в качестве примера в данном документе, является мультиплексированным устройством, в котором адреса, команды и данные протекают по простому 16-битовому интерфейсу последовательным образом. Фиг.7 иллюстрирует последовательный характер распределения во времени протокола передачи адресов, команд и данных в примерное флэш-устройство. Отметим, что адреса, команды и данные отправляются из SDRAM-интерфейса (который не мультиплексируется) посредством записи последовательно в блоки команд и данных.

Как описано выше, посредством обнаружения операций записи в блок команд адресного пространства SDRAM, требуемые данные могут передаваться во флэш-устройство посредством контроллера 308. Показанная выше передача адресов может быть расширена, чтобы показать передачу информации адресов во флэш-устройство. Как также описано выше, информация адресов для флэш-памяти передается посредством выполнения нескольких операций записи в адрес блока команд SDRAM. Данные SDRAM в этой области недоступны, поскольку выбор устройства для этих записей должен быть отменен. Таким последовательным образом данные адресов и информация команд могут быть записаны и считаны из флэш-устройства. Управляющая логика реализует дополнительные командные протоколы, как описано выше, к примеру, чтобы дать возможность изолировать флэш-устройство от вопросов скорости SDRAM-устройства. Например, посредством буферизации состояния флэш-устройства в управляющей логике дополнительная команда отвечает, что указание состояния занятости и приведения в исполнение может быть добавлено в последовательный протокол. Данные и состояние, возвращаемые из флэш-устройства, буферизуются в небольшой блок SRAM логики передачи данных, так что скорости считывания и записи во флэш-память соответствуют скоростям SDRAM.

Типичный пример последовательной передачи во флэш-устройство представлен на фиг.8, который представляет примерные операции считывания и записи посредством микропрограммного обеспечения 330 в адресное пространство 332 SDRAM (фиг.3), которое зарезервировано для управления флэш-памятью 306. В общем, микропрограммное обеспечение отправляет команду флэш-памяти на этапе 802 посредством записи команды IDLE в адресное пространство 332, которое обнаруживает контроллер.

На этапе 804 микропрограммное обеспечение отправляет запрос адресов блока флэш-памяти, содержащий пять записей адресов, которые указывают то, какой блок использовать и какой адрес, наряду с одной командой записи в адресное пространство команд. Контроллер затем имеет информацию, которая ему требуется для того, чтобы выполнить запись.

На каждом из этапов 806 и 808 микропрограммное обеспечение 330 опрашивает состояние посредством выдачи команды записи пакетного считывания, циклически проходящего через этап 810 до тех пор, пока состояние готовности не обнаружено, и пакет считывания из флэш-памяти (этап 812) отправляется.

В альтернативной реализации основанный на регистрах протокол предоставляет доступ к флэш-памяти посредством загрузки последовательности регистров, включающей в себя запись в регистр слова занятости, заданного так, чтобы начинать приведение в исполнение команды. Это дает возможность одной страничной записи инициировать запись или выборку блока либо блоков флэш-памяти. В этой альтернативе слово занятости переключается посредством контроллера, когда команда выполнена. Поддерживаемые команды включают в себя выборку адреса/блока (или выборку диапазона адресов), запись адреса/блока (или запись диапазона адресов) и удаление адреса/блока (или удаление диапазона адресов).

Более того, поскольку контроллер включает в себя логику, контроллер может выполнять управление флэш-памятью. Например, флэш-память изнашивается после определенного числа считываний и записей, и тем самым контроллер может переназначить доступ так, чтобы сбалансировать различные доступные блоки флэш-памяти, что упоминается как сглаживание срабатывания. Логика контроллера также может выполнять обнаружение и коррекцию ошибок и выполнять управление дефектными блоками посредством логического удаления известных дефектных блоков из доступных.

Фиг.9 - это примерное представление модуля памяти с двухрядным расположением выводов (DIMM) 902, иллюстрирующее то, как флэш-память может быть добавлена в традиционную системную память персонального компьютера. Физические микросхемы флэш-памяти могут быть на той же стороне, что и микросхемы SDRAM, на противоположной стороне или и там, и там. Контроллер может быть на самом DIMM либо альтернативно может быть внешним для него с возможностью деактивировать SDRAM и заменять флэш-данные при необходимости.

Когда персональный компьютер включается, BIOS (микропрограммное обеспечение) проверяет наличие гибридной DIMM-памяти и, если присутствует, загружает, по меньшей мере, часть SDRAM-памяти (ее код) из флэш-памяти. Наличие энергонезависимой флэш-памяти обеспечивает возможность операций загрузки или возобновления из данных, сохраненных во флэш-памяти. Например, доступ к данным осуществляется из кэш-памяти CPU, который преобразуется в блоки памяти и разрешается либо из SDRAM, либо из флэш-памяти. Если достаточно имеется флэш-памяти, вся SDRAM может быть сохранена для состояния ожидания либо вся операционная система загружается без необходимости осуществлять доступ к периферийным устройствам, таким как жесткий диск.

Хотя изобретение допускает различные модификации и альтернативные конструкции, его конкретные проиллюстрированные варианты осуществления показаны на чертежах и подробно описаны выше. Тем не менее, необходимо понимать, что отсутствует намерение ограничить изобретение конкретными раскрытыми формами, а наоборот, намерение состоит в том, чтобы охватить все модификации, альтернативные конструкции и эквиваленты, подпадающие под дух и область применения изобретения.

| название | год | авторы | номер документа |

|---|---|---|---|

| ГИБРИДНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 2014 |

|

RU2627100C2 |

| ПРОГРЕССИВНАЯ НАЧАЛЬНАЯ ЗАГРУЗКА ДЛЯ БЕСПРОВОДНОГО УСТРОЙСТВА | 2008 |

|

RU2456663C2 |

| УПРАВЛЕНИЕ ПАМЯТЬЮ | 2014 |

|

RU2643499C2 |

| КОМПЬЮТЕРНАЯ СИСТЕМА | 2014 |

|

RU2579949C2 |

| ИСПОЛЬЗОВАНИЕ ЭНЕРГОЗАВИСИМОЙ ПАМЯТИ В КАЧЕСТВЕ ЭНЕРГОНЕЗАВИСИМОЙ ПАМЯТИ | 2017 |

|

RU2739722C2 |

| СИСТЕМА ХРАНЕНИЯ ДАННЫХ В СООТВЕТСТВИИ С ПРОФИЛЕМ ХРАНЕНИЯ ДАННЫХ | 2020 |

|

RU2768615C1 |

| ОПЕРАТИВНОЕ РЕГУЛИРОВАНИЕ ПРОИЗВОДИТЕЛЬНОСТИ ТВЕРДОТЕЛЬНЫХ ЗАПОМИНАЮЩИХ УСТРОЙСТВ | 2014 |

|

RU2624563C2 |

| СИСТЕМА НА КРИСТАЛЛЕ ДЛЯ ВЫПОЛНЕНИЯ БЕЗОПАСНОЙ ЗАГРУЗКИ, УСТРОЙСТВО ФОРМИРОВАНИЯ ИЗОБРАЖЕНИЙ, ИСПОЛЬЗУЮЩЕЕ ЕЕ, И СПОСОБ ДЛЯ НЕГО | 2013 |

|

RU2651213C2 |

| ИСПОЛЬЗОВАНИЕ АУТЕНТИФИЦИРОВАННЫХ МАНИФЕСТОВ ДЛЯ ОБЕСПЕЧЕНИЯ ВНЕШНЕЙ СЕРТИФИКАЦИИ МНОГОПРОЦЕССОРНЫХ ПЛАТФОРМ | 2014 |

|

RU2599340C2 |

| Накопитель магнитный с разделёнными областями | 2020 |

|

RU2757659C1 |

Изобретение относится к вычислительной технике, а именно к гибридным запоминающим устройствам. Техническим результатом является расширение памяти компьютерного устройства в отношении наличия относительно больших объемов энергозависимой и энергонезависимой памяти без изменений существующей физической архитектуры этого компьютерного устройства. В запоминающем устройстве система для обработки операций с данными в едином интерфейсе для двух типов памяти содержит первый тип памяти, второй тип памяти, причем первый и второй типы памяти являются типами аппаратной памяти, интерфейс, соответствующий первому типу памяти, контроллер, который соединен с интерфейсом, с первым типом памяти и со вторым типом памяти, при этом на основе информации, принятой в интерфейсе, контроллер определяет, направлена ли другая информация, принятая через интерфейс, в первый тип памяти или второй тип памяти. Способ описывает работу данной системы. 3 н. и 14 з.п. ф-лы, 10 ил.

1. Реализуемый в запоминающем устройстве способ обработки операций с данными в едином интерфейсе для по меньшей мере двух типов памяти без каких-либо изменений по отношению к физическому запоминающему устройству, содержащий этапы, на которых:

принимают в контроллере команды, адреса и данные в запоминающем устройстве через интерфейс, ассоциированный с запоминающим устройством, при этом запоминающее устройство включает в себя, по меньшей мере, первый тип памяти и второй тип памяти, причем интерфейс определен для первого типа памяти и устройство памяти включает в себя только программные изменения относительно запоминающего устройства, имеющего только первый тип памяти, так что никаких физических изменений не требуется по отношению к запоминающего устройству для работы с первым типом памяти и вторым типом памяти;

определяют в контроллере, соответствует ли информация, принятая в запоминающем устройстве, первому типу памяти, ассоциированному с запоминающим устройством, и если да, то выводят сигналы в первый тип памяти для передачи по меньшей мере одной команды в первый тип памяти; и

определяют в контроллере, соответствует ли информация, принятая в запоминающем устройстве, второму типу памяти, ассоциированному с запоминающим устройством, и если да, то выводят сигналы во второй тип памяти для передачи по меньшей мере одной команды во второй тип памяти.

2. Способ по п.1, дополнительно содержащий этап, на котором, когда принятая информация соответствует второму типу памяти, отключают первый тип памяти.

3. Способ по п.1, дополнительно содержащий этапы, на которых, когда принятая информация соответствует второму типу памяти, выводят индикатор занятности, выполняют операцию ввода/вывода данных во втором типе памяти и выводят индикатор готовности, когда операция ввода/вывода завершена.

4. Способ по п.1, дополнительно содержащий этап, на котором, когда принятая информация соответствует второму типу памяти, осуществляют доступ к информации команд и/или информации адресации данных в другом наборе из одной или более ячеек запоминающего устройства.

5. Способ по п.4, в котором принятая информация соответствует информации адресации данных, при этом способ дополнительно содержит этап, на котором считывают информацию адресации данных, чтобы отобразить принятый адрес на одну секцию из множества возможных секций второго типа памяти.

6. В запоминающем устройстве система для обработки операций с данными в едином интерфейсе для двух типов памяти, содержащая:

первый тип памяти;

второй тип памяти, причем первый и второй типы памяти являются типами аппаратной памяти;

интерфейс, соответствующий первому типу памяти так, что запоминающее устройство работает с протоколом доступа первого типа памяти, и так, что только программные изменения требуются для работы интерфейса как с первым типом памяти, так и со вторым типом памяти и без каких-либо физических изменений запоминающего устройства относительно запоминающего устройства, имеющего только первый тип памяти; и

контроллер, который соединен с интерфейсом, с первым типом памяти и со вторым типом памяти, при этом на основе информации, принятой в интерфейсе, контроллер определяет, направлена ли другая информация, принятая через интерфейс, в первый тип памяти или второй тип памяти.

7. Система по п.6, в которой первый тип памяти содержит энергозависимую память, второй тип памяти содержит энергонезависимую память, при этом, по меньшей мере, часть информации, принимаемой в интерфейсе, посредством которой контроллер определяет, направлена ли соответствующая информация, принимаемая через интерфейс, в первый тип памяти или второй тип памяти, принимается по адресу памяти, соответствующему первому типу памяти.

8. Система по п.7, в которой энергозависимая память содержит память SDRAM-типа или DRAM-типа, при этом адрес памяти и соответствующая информация, принятая посредством интерфейса, содержит строб строкового доступа, строб столбцового доступа и управляющую информацию.

9. Система по п.7, в которой энергонезависимая память содержит флэш-память, при этом система дополнительно содержит ассоциированный с контроллером буфер для буферизации операций ввода/вывода данных, выполняемых с помощью флэш-памяти.

10. Система по п.9, дополнительно содержащая индикатор состояния, при этом контроллер сообщает через индикатор состояния, занята ли или завершена операция ввода/вывода данных.

11. Система по п.6, в которой запоминающее устройство включено в модуль памяти с двухрядным расположением выводов.

12. Система по п.6, в которой контроллер осуществляет доступ к информации команд и/или информации адресации данных в наборе из одной или более ячеек, соответствующих первому типу памяти.

13. Система по п.6, в которой контроллер сообщается непосредственно с первым типом памяти и содержит набор буферов для сообщения со вторым типом памяти.

14. В вычислительном устройстве система для обработки операций с данными для двух типов памяти, содержащая:

центральный процессор;

гибридное запоминающее устройство, включающее в себя:

основывающуюся на DRAM-память

память типа флэш, имеющую скорость ниже, чем скорость основывающейся на DRAM-памяти,

микропрограммное обеспечение,

физическую архитектуру, которая включает в себя только изменения микропрограммного обеспечения относительно запоминающего устройства, имеющего только основывающуюся на DRAM-память, так что никакие физические изменения не выполняются для размещения памяти типа флэш в гибридном запоминающем устройстве,

интерфейс, соответствующий основывающейся на DRAM-памяти, и

контроллер, имеющий набор буферов согласования скорости для, по меньшей мере, скорости, основывающейся на DRAM-памяти; и

компонент, который

инициирует операции ввода/вывода (I/O) в контроллер через интерфейс, в том числе посредством записи связанных с I/O данных по одному или более адресам основывающейся на DRAM-памяти,

предписывает контроллеру отобразить упомянутые один или более адресов основывающейся на DRAM-памяти на память типа флэш, тем самым указывая, что упомянутые связанные с I/O данные должны использоваться в памяти типа флэш,

предписывает контроллеру устанавливать состояние в занятость, причем данное состояние указывает состояние занятости контроллера для микропрограммного обеспечения,

заполняет набор буферов согласования скорости данными,

когда в наборе буферов согласования скорости имеется достаточно данных для компенсации разницы в скорости в основывающейся на DRAM-памяти, устанавливает состояние в готовность, и,

когда микропрограммным обеспечением выполняется опрос на предмет состояния и определяется, что состояние установлено в готовность, выводит данные из набора буферов согласования скорости, при этом центральный процессор не осведомлен об опросе на предмет состояния со стороны микропрограммного обеспечения.

15. Система по п.14, в которой упомянутые связанные с I/O данные ассоциированы с командой считывания, при этом заполнение набора буферов согласования скорости данными включает в себя получение этих данных из памяти типа флэш, причем при выводе данных выводятся данные, полученные из памяти типа флэш.

16. Система по п.14, в которой упомянутые связанные с I/O данные ассоциированы с командой записи, при этом заполнение набора буферов согласования скорости данными включает в себя получение этих данных из микропрограммного обеспечения, причем вывод данных включает в себя запись данных в память типа флэш.

17. Система по п.14, в которой центральный процессор не осведомлен о памяти типа флэш.

| Способ обработки целлюлозных материалов, с целью тонкого измельчения или переведения в коллоидальный раствор | 1923 |

|

SU2005A1 |

| Пломбировальные щипцы | 1923 |

|

SU2006A1 |

| Способ и приспособление для нагревания хлебопекарных камер | 1923 |

|

SU2003A1 |

| СЧИТЫВАЮЩАЯ СХЕМА ДЛЯ ФЛЭШ-ПАМЯТИ С МНОГОУРОВНЕВЫМИ ЯЧЕЙКАМИ | 1995 |

|

RU2190260C2 |

Авторы

Даты

2012-02-10—Публикация

2007-06-01—Подача