Настоящее изобретение относится к области обеспечения защиты от несанкционированного доступа к информации, а именно к способам идентификации аппаратной архитектуры исполняющего устройства по бинарным данным из образа памяти аппаратно-программных средств с целью проведения последующего поиска уязвимостей, программных закладок и недекларированных возможностей в управляющих программах.

Уровень техники

Известны способы идентификации аппаратной архитектуры исполняющего устройства на основе применения нейронных сетей, вычисления энтропии данных, использования нормированного расстояния по сжатым данным, полноценного дизассемблирования.

Способы, построенные на базе нейронных сетей, требуют наличие обучающей выборки, представляющей собой множество существенных по объему экземпляров машинного кода для определенной архитектуры [1]. Процесс получения такой выборки может представлять из себя определенную проблему для модифицированных или малораспространенных аппаратных архитектур. Это объясняется отсутствием соответствующих экземпляров машинного кода с открытой лицензией и высокой стоимостью проприетарных компиляторов. В случае нейронных сетей увеличение количества идентифицируемых аппаратных архитектур приводит к увеличению вероятностей ошибок первого и второго рода. Также негативное влияние на качество идентификации оказывает наличие различных модификаций аппаратных архитектур (например, добавление новых команд).

Способы, основанные на вычислении энтропии данных и на метрике сжатия [2-4], так же как и способы на базе нейронных сетей, снижают качество идентификации при увеличении количества идентифицируемых аппаратных архитектур. Еще одним общим свойством этих способов является необходимость наличия эталонных экземпляров программ для соответствующей аппаратной архитектуры - аналога обучающей выборки. Следует отметить, что для энтропийных способов требования к ее объему существенно меньше. Однако, в случае нормированного расстояния по сжатым данным размер эталонных экземпляров программ должен быть близок к анализируемому образу памяти. Неотъемлемым недостатком данного класса способов является довольно существенный уровень вероятностей ошибок первого и второго рода [3], что связано с полным игнорированием особенностей конкретной аппаратной архитектуры вследствие простоты используемых математических моделей.

В патенте [5] предлагается аппаратура, система и метод для динамического анализа графов потока управления, при этом система предполагает использование полного дизассемблирования, так как исходные листинги недоступны. В настоящем изобретении также используется анализ графов потока управления, однако в отличии от [5], в заявляемом способе предлагается ограничится лишь декодированием двух типов инструкций (условного и безусловного переходов), что позволяет значительно снизить трудоемкость его адаптации для поддержки новой аппаратной архитектуры по сравнению с данным аналогом.

В патенте [6] предлагается способ обнаружения шаблонов кода с помощью эмуляции исполнения машинного кода. Этот метод также может использоваться для идентификации аппаратной архитектуры через перебор всех доступных эмуляторов. В этом отношении, он аналогичен настоящему изобретению, где также предполагается перебор вариантов принадлежности к известным архитектурам. Однако реализация эмулятора для новой аппаратной архитектуре значительно сложнее и требует гораздо больше затрат даже по сравнению реализацией полноценного дизассемблера. По данному критерию способ [6] существенно проигрывает заявляемому способу, ограничивающимся лишь декодированием двух типов инструкций (условного и безусловного переходов).

В патенте [7] предлагается метод дизассемблирования образа памяти аппаратно-программных средств автоматизированных систем управления технологическими процессами (АСУ ТП) с целью проведения последующего поиска уязвимостей в управляющих программах. Идентификация аппаратной архитектуры исполняющего устройства является предпоследним этапом этого метода. Настоящее изобретение предназначено для проведения идентификация аппаратной архитектуры и может быть непосредственно использовано для выполнения задач указанного этапа. В отличии от заявляемого способа, для реализации данного этапа в методе [7] использован способ на основе нормированного расстояния по сжатым данным, описанный в [2]. Как отмечалось выше, по сравнению с проведением дизассемблирования такой способ имеет множество недостатков: необходимость наличия эталонных экземпляров программ для соответствующей аппаратной архитектуры, существенный уровень вероятностей ошибок первого и второго рода, снижение качества идентификации при увеличении количества поддерживаемых аппаратных архитектур [3].

Наиболее близким к заявленному изобретению является способ идентификации машинного кода и данных в исполняемом программном модуле на основе дизассемблирования с рекурсивным обходом (англ. recursive traversal disassembly), описанный в патенте [8]. Однако, в этом случае требуется наличие полноценного декодера системы команд (дизассемблера) идентифицируемых аппаратных архитектур, реализация которого требует как значительных материальных затрат, так и доступа к соответствующей технической документации, что не всегда возможно. Кроме того, модификации системы команд аппаратных архитектур (в том числе наличие дополнительных команд) приводит к существенным проблемам при проведении идентификации и увеличению вероятности ошибок второго рода. При этом положительный результат дизассемблирования не всегда достигается в автоматическом режиме даже при известной аппаратной архитектуре исполнительного устройства, что связано с необходимостью правильного задания адресов сегментов, знанием особенностей формирования таблиц переходов, особенностями вычисления адресов, форматом образа памяти и т.д.

Количество команд условных и безусловных переходов по относительному смещению ограничено, что позволяет сильно упростить реализацию дешифратора команд. Использование относительного смещения, вместо абсолютного, исключает зависимость от загрузочного адреса. Для предлагаемого метода требуется лишь описание команд условных и безусловных переходов по относительному смещению, которые являются консервативными элементами системы команд аппаратных архитектур, остающиеся неизменными при модификации последних.

Задачей, на решение которой направлено заявляемое изобретение, является устранение недостатков аналогов и прототипа [1-8], заключающихся в уменьшении трудоемкости и снятии ограничений, связанных с необходимостью наличия обучающей выборки или декодера полной системы команд, при решении практических задач, требующих проводить идентификацию аппаратной архитектуры.

Техническим результатом изобретения является снижение трудоемкости по расширению идентифицированных аппаратных архитектур с сохранением высокой избирательности и специфичности.

Указанный технический результат достигается за счет того, что в заявленном способе экспресс-идентификации аппаратной архитектуры исполняющего устройства на основе анализа бинарных данных характеризующимся тем, что получают немодифицированный образ памяти исследуемого устройства, включающий машинный код управляющей программы, исключают из образа памяти исследуемого устройства области высокоэнтропийных и низкоэнтропийных данных, осуществляют поиск команд условных и безусловных переходов по относительному смещению в соответствии с предположительной аппаратной архитектурой, формируют и анализируют графы передачи управления, после чего принимают решение о правильности идентификации аппаратной архитектуры.

В частности, исключение из образа памяти исследуемого устройства области высокоэнтропийных данных определяют по значению параметра энтропии по крайней мере в 0,9.

В частности, исключение из образа памяти исследуемого устройства области низкоэнтропийных данных определяют по значению параметра энтропии менее 0,3 при размере окна оценки не более 5000 байт.

В частности, поиск команд условных и безусловных переходов по относительному смещению в соответствии с предположительной аппаратной архитектурой осуществляют посредством сплошного декодирования бинарных данных.

В частности, анализ графов передачи управления выполняют посредством расчета гистограммы количества ребер, заканчивающихся на одном и том же адресе, причем первые три столбца с индексами 0, 1 и 2 отбрасывают.

В частности, анализ графов передачи управления выполняют посредством расчета общего количества непосредственно примыкающих друг другу в адресном пространстве ребер и количества ребер, начинающихся непосредственно перед окончанием условного перехода.

В частности, на этапе принятия решения о правильности идентификации аппаратной архитектуры проводится параллельное декодирование команд нескольких архитектур и характеристики графов передачи управления анализируют для всех доступных архитектур одновременно, после чего выбирают ту архитектуру, для которой выполняется два условия: гистограмма количества ребер не соответствует экспоненциальному закону распределения, т.е. отношения между соседними столбцами значительно меньше 10; отношение количества ребер, начинающихся непосредственно перед окончанием условного перехода, к общему количеству непосредственно примыкающих друг другу в адресном пространстве ребер больше 0,01.

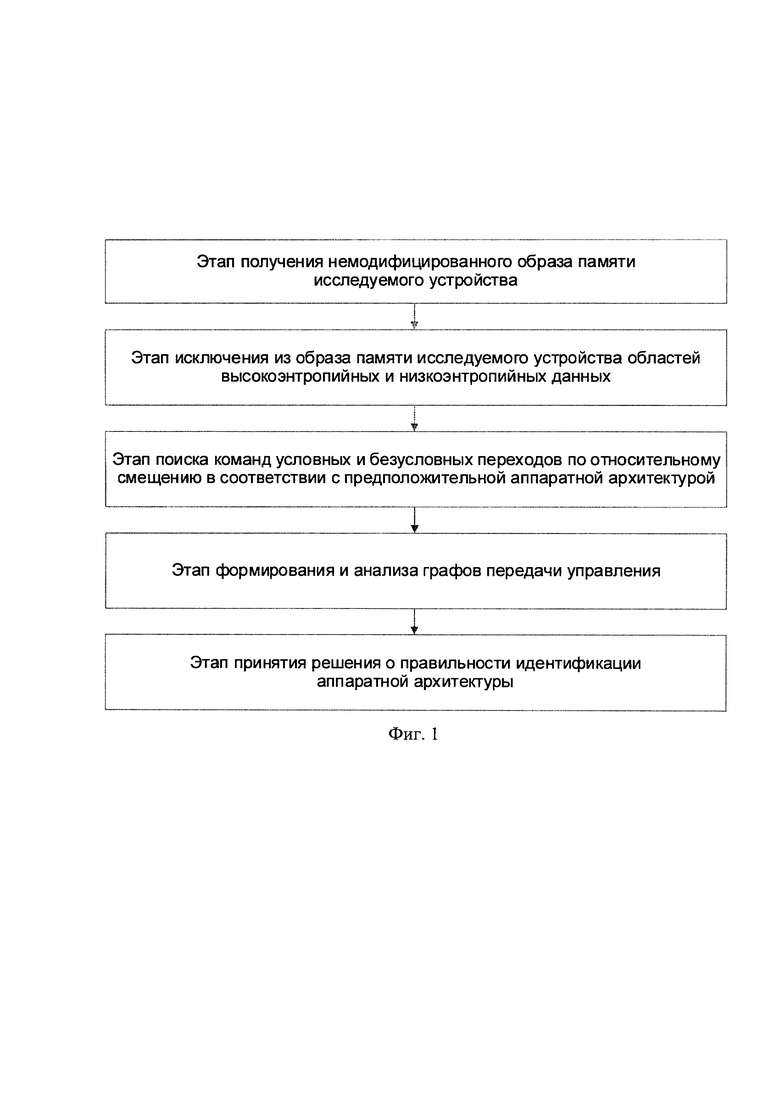

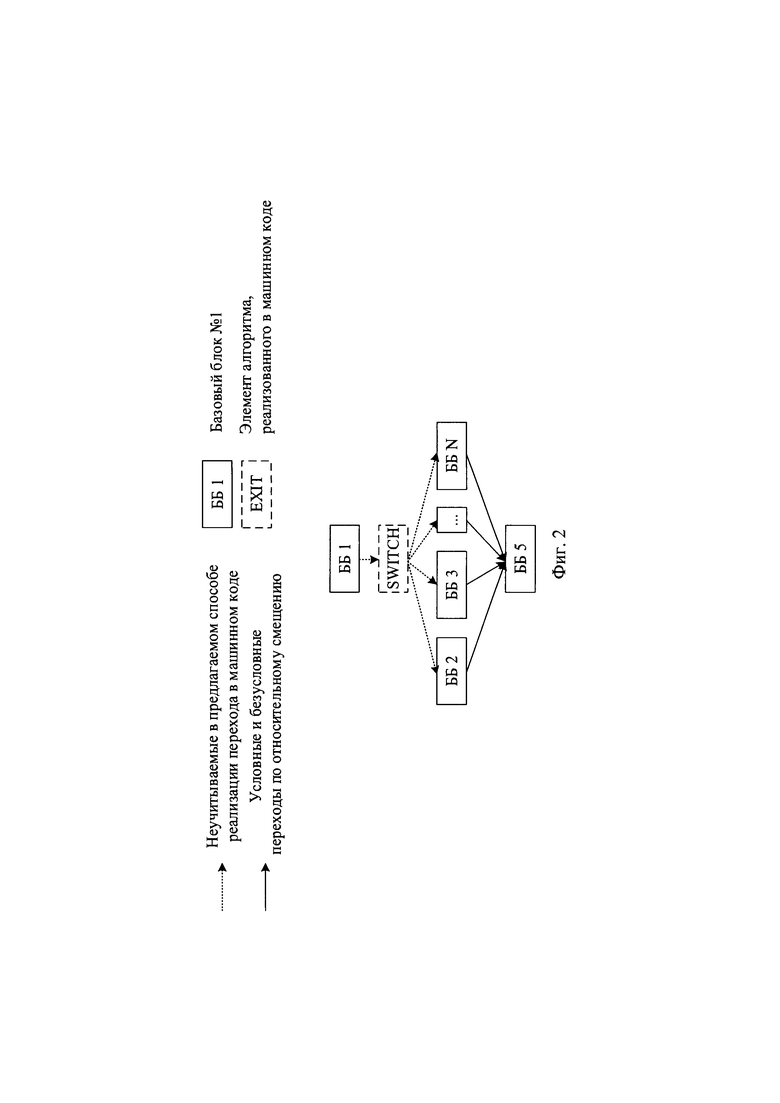

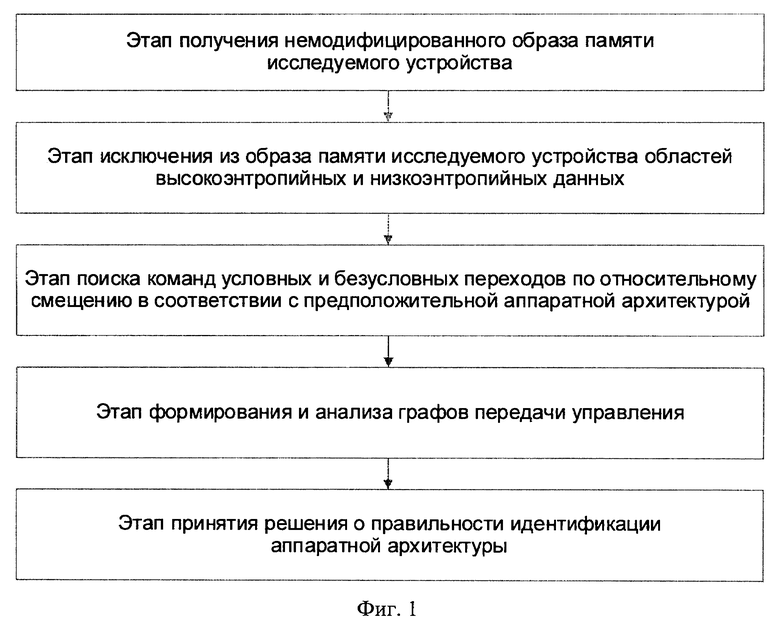

Сущность изобретения поясняется чертежами, на которых изображено:

Фиг. 1 - блок-схема, иллюстрирующая способ экспресс-идентификации аппаратной архитектуры исполняющего устройства на основе анализа бинарный данных.

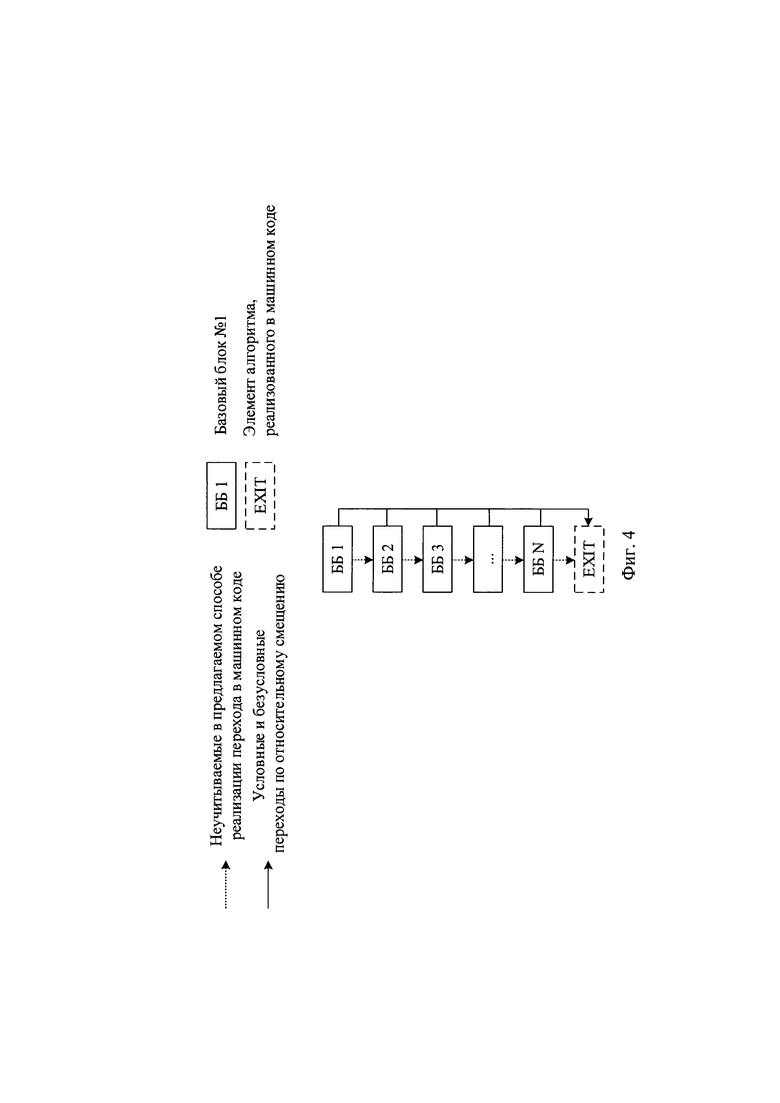

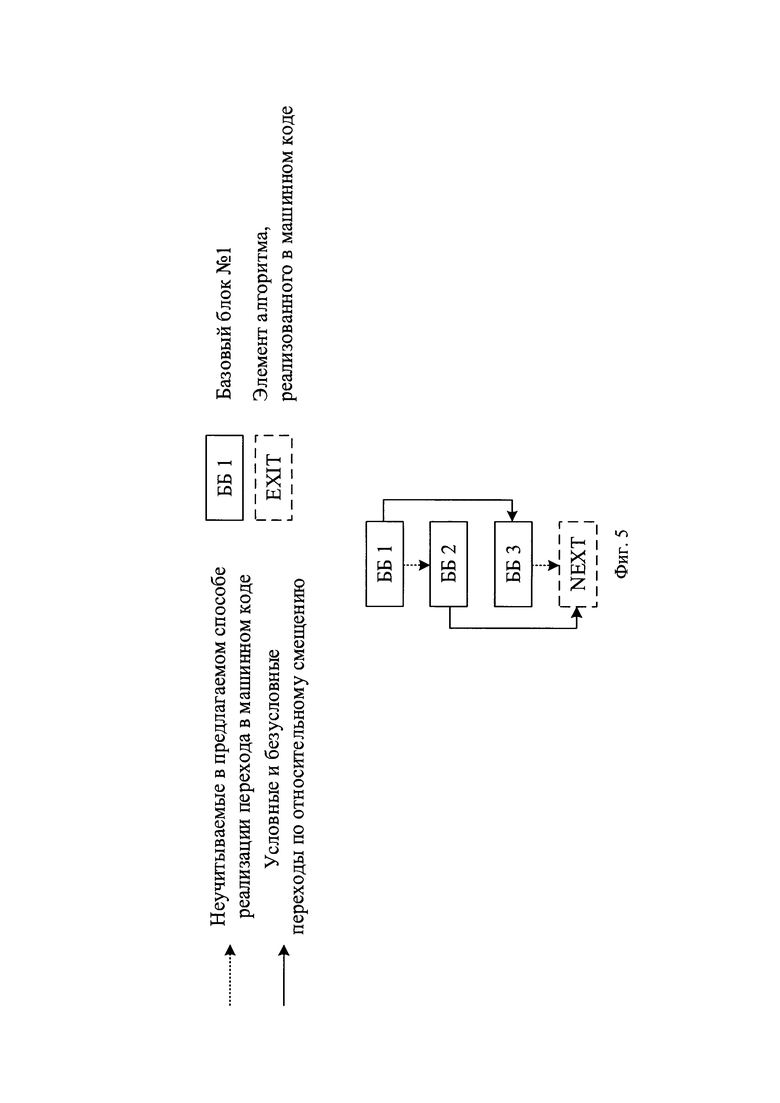

Фиг. 2, фиг. 3, фиг. 4, фиг. 5 - модели графов передачи управления в машинном коде, которые используются для задания условий идентификации аппаратной архитектуры.

Фиг. 2, фиг. 3, фиг. 4, фиг. 5 иллюстрируют различные модели графов передачи управления в машинном коде, используемые в настоящем способе: оператор множественного выбора (фиг. 2); принудительный выход из цикла (фиг. 3); досрочный выход из процедуры обработки (фиг. 4); условный оператор с двумя альтернативами (фиг. 5).

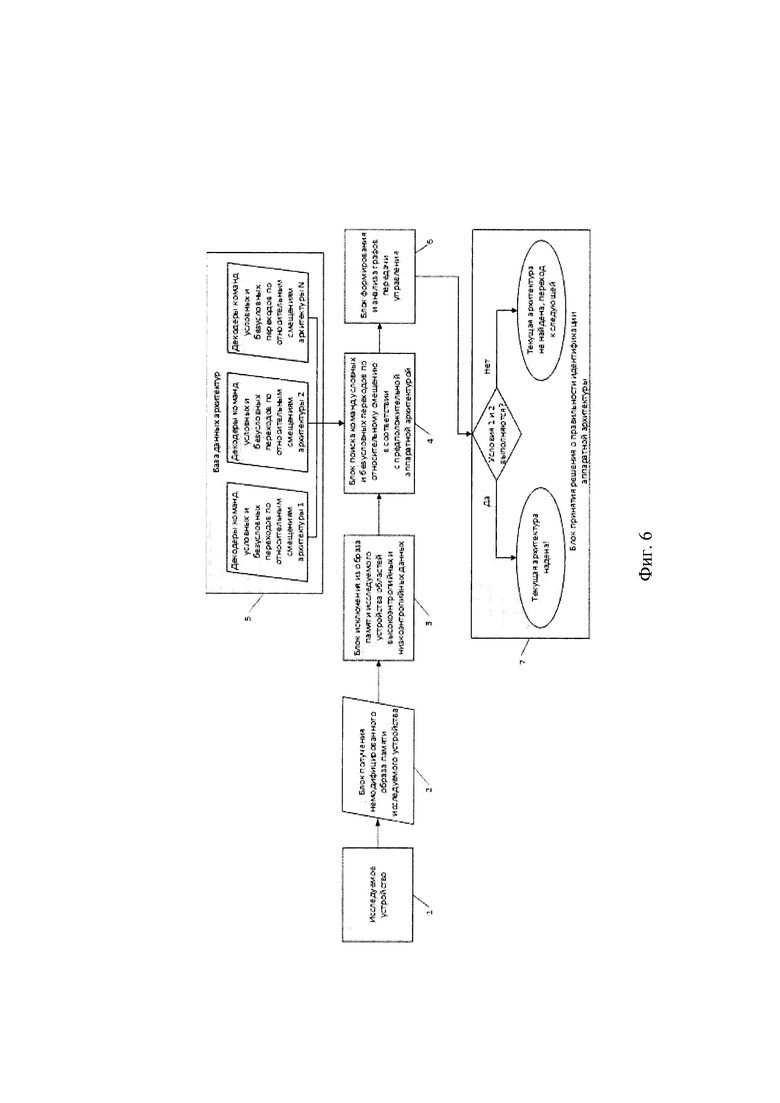

Фиг. 6. - схема устройства, реализующего описываемый способ.

На фигурах изображено: 1 - исследуемое устройство; 2 - блок получения немодифицированного образа памяти исследуемого устройства; 3 - блок исключения из образа памяти исследуемого устройства области высокоэнтропийных и низкоэнтропийных данных; 4 - блок поиска команд условных и безусловных переходов по относительному смещению в соответствии с предположительной аппаратной архитектурой; 5 - база данных архитектур; 6 - блок формирования и анализа графов передачи управления 7 - блок принятие решения о правильности идентификации аппаратной архитектуры.

Осуществление изобретения

Осуществление настоящего изобретения предусматривает способ экспресс-идентификации аппаратной архитектуры исполняющего устройства на основе анализа бинарных данных из образа памяти аппаратно-программных средств, который включает в себя последовательное выполнение следующих этапов:

- получение немодифицированного (несжатого, незашифрованного и т.д.) образа памяти исследуемого устройства, включающего машинный код управляющей программы;

- исключение из образа памяти исследуемого устройства области сжатых и шифрованных данных, определяемых по высокому значению параметра энтропии 0,9, а также однородных данных с энтропией меньше 0,3 при размере окна 5000 байт;

- поиск команд условных и безусловных переходов по относительному смещению в соответствии с предположительной аппаратной архитектурой, осуществляющийся посредством сплошного декодирования бинарных данных;

- формирование и анализ графов передачи управления:

1) расчет гистограммы количества ребер, заканчивающихся на одном и том же адресе, причем первые три столбца с индексами 0, 1 и 2 отбрасываются;

2) расчет общего количества непосредственно примыкающих друг другу в адресном пространстве ребер и количества ребер, начинающихся непосредственно перед окончанием условного перехода;

- проверку правильности идентификации аппаратной архитектуры, при которой проводится параллельное декодирование команд нескольких архитектур и характеристики графов передачи управления анализируются для всех доступных архитектур одновременно, после чего выбирается та архитектура, для которой выполняется два условия:

1) гистограмма количества ребер не соответствует экспоненциальному закону распределения, т.е. отношения между соседними столбцами значительно меньше 10;

2) отношение количества ребер, соответствующих модели условного оператора с двумя альтернативами, к общему количеству непосредственно примыкающих друг другу в адресном пространстве ребер больше 0,01.

Таким образом, использование исследуемого технического решения позволяет увеличить оперативность идентификации аппаратной архитектуры исполняющего устройства.

Технический результат изобретения, состоящий в снижении трудоемкости по расширению идентифицированных аппаратных архитектур, что достигается за счет подготовки декодера только для команд условных и безусловных переходов по относительному смещению без необходимости наличия обучающей выборки. Сохранение высокой избирательности и специфичности достигается за счет высокого уровня автоматизации и малой вероятности получения программоподобной структуры графов передачи управления в произвольных данных.

Пример достижения технического результата

Из исследуемого устройства 1 с неизвестной аппаратной архитектурой выгружается немодифицированный образ памяти 2, который подается на вход блока исключения из образа памяти области высокоэнтропийных и низкоэнтропийных данных 3, по результатам которого выбираются области памяти со значением энтропии от 0,3 до 0,9 при размере окна анализа 5000 байт. Оставшиеся (неисключенные) в результате предыдущего шага области памяти передаются на вход блоку поиска команд условных и безусловных переходов 4, который находит посредством сплошного декодирования бинарных данных команды условных и безусловных переходов по относительному смещению в соответствии с предположительной аппаратной архитектурой и запоминает их, причем, для получения декодеров машинных кодов условных и безусловных переходов используется накопленная в базе данных архитектур 5 информация. Данный набор условных и безусловных переходов из анализируемой предположительной архитектуры передается на вход блоку формирования и анализа графов передачи управления 6, в ходе работы которого рассчитываются следующие характеристики графов передачи управления:

1) гистограмма количества ребер, заканчивающихся на одном и том же

адресе, причем первые три столбца с индексами 0, 1 и 2 отбрасываются, - эта

характеристика отражает особенности моделей досрочного выхода

из процедуры обработки (фиг. 3 и фиг. 4) и оператора множественного выбора

(фиг. 2);

2) количество ребер, определяемых безусловными переходами, начинающимися непосредственно перед окончанием условного перехода, причем данный параметр выбран исходя из модели условного оператора с двумя альтернативами (фиг. 5).

Для принятия решения о правильности определения вычислительной архитектуры используется блок принятия решения 7, который производит параллельное декодирование команд нескольких архитектур и характеристики графов передачи управления анализируются для всех доступных архитектур одновременно, после чего выбирается та архитектура, для которой выполняется два условия:

1) гистограмма количества ребер не соответствует экспоненциальному закону распределения, т.е. отношения между соседними столбцами значительно меньше 10;

2) отношение количества ребер, соответствующих модели условного оператора с двумя альтернативами (фиг. 5), к общему количеству непосредственно примыкающих друг другу в адресном пространстве ребер больше 0,01.

Если условия не выполняются, на этапе 3 начинается новый поиск с помощью набора машинных команд условных переходов, характерных для другой аппаратной архитектуры.

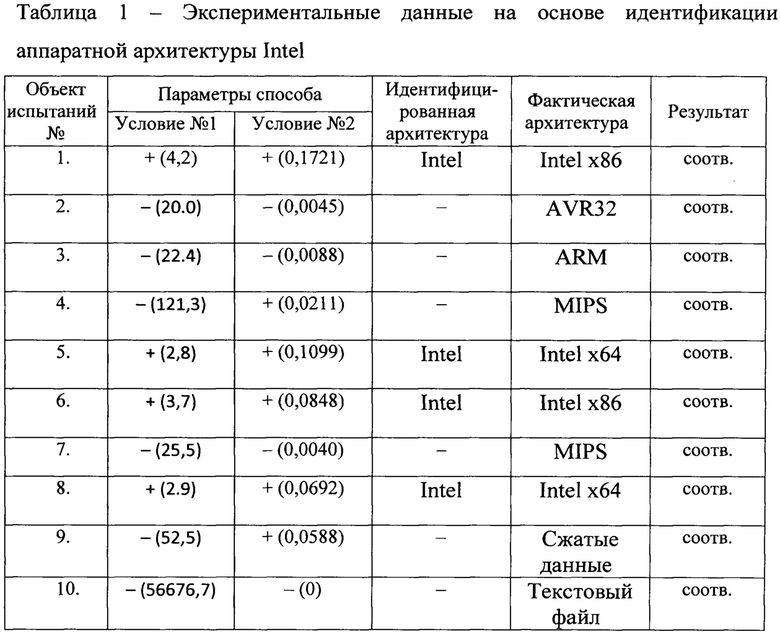

Экспериментальные данные на основе идентификации аппаратной архитектуры Intel для 10 образцов с различными аппаратными архитектурами приведены таблице 1. В рамках эксперимента ошибочных решений не выявлено.

Выше описан лишь иллюстративный вариант осуществления настоящего изобретения, который не призван как-либо ограничивать объем изобретения. Любые модификации, эквиваленты и усовершенствования, отвечающие принципам изобретения, подлежат включению в объем изобретения.

ИСТОЧНИКИ ИНФОРМАЦИИ

1. R. Aristov, A. Gladkikh Artificial Recurrent Neural Networks (ARNN) for Reverse-Engineering of ASIC-based Device Firmware // Zeronight 2015.

2. S. Axelsson, «Using Normalized Compression Distance for Classifying File Fragments)), 2010 International Conference on Availability, Reliability and Security, Krakow, 2010, c. 641-646.

3. Raff E., Nicholas. C. An Alternative to NCD for Large Sequences, Lempel-Ziv Jaccard Distance // Proceedings of 23 International Conference on Knowledge Discovery and Data Mining (KDD)// 2017// 1007-1015.

4. Würtemberg T. Applying normalised compression distance for architecture classification. NCC Group Publication. URL: https://www.nccgroup.com/globalassets/our-research/uk/whitepapers/2017/applying-normalised-compression-distance-for-architecture-classification.pdf.

5. US 8381185 от 19.02.2013 Apparatus, system, and method for dynamic module flow analysis, заявка №4541571309 от 31.09.2009.

6. US 2006/0101435 A1 от 11.05.2006 Detection of code patterns, заявка №4596438904 от 13.10.2004.

7. US 2015/0248556 A от 03.09.2015 Firmware disassembly system заявка №61/945859 от 28.02.2014.

8. US 6014513 от 11.01.2000 Discovering code and data in a binary executable program, заявка №4599683997 от 23.12.1997.

Изобретение относится к способу экспресс-идентификации аппаратной архитектуры исполняющего устройства на основе анализа бинарных данных. Технический результат заключается в повышении эффективности идентификации аппаратной архитектуры исполняющего устройства. В способе получают немодифицированный образ памяти исследуемого устройства, включающий машинный код управляющей программы, исключают из образа памяти исследуемого устройства области высокоэнтропийных и низкоэнтропийных данных, в полученной области памяти осуществляют поиск команд условных и безусловных переходов по относительному смещению в соответствии с предположительной аппаратной архитектурой посредством сплошного декодирования бинарных данных, при этом вышеупомянутый поиск осуществляется на основании декодированных машинных кодов условных и безусловных переходов предположительной аппаратной архитектуры, полученных из базы данных аппаратных архитектур, формируют и анализируют графы передачи управления на основании вышеуказанных найденных команд, после чего принимают решение о правильности идентификации аппаратной архитектуры на основании полученных характеристик графов передачи управления. 6 з.п. ф-лы, 6 ил., 1 табл.

1. Способ экспресс-идентификации аппаратной архитектуры исполняющего устройства на основе анализа бинарных данных, характеризующийся тем, что

получают немодифицированный образ памяти исследуемого устройства, включающий машинный код управляющей программы,

исключают из образа памяти исследуемого устройства области высокоэнтропийных и низкоэнтропийных данных,

в полученной области памяти осуществляют поиск команд условных и безусловных переходов по относительному смещению в соответствии с предположительной аппаратной архитектурой посредством сплошного декодирования бинарных данных,

при этом вышеупомянутый поиск осуществляется на основании декодированных машинных кодов условных и безусловных переходов предположительной аппаратной архитектуры, полученных из базы данных аппаратных архитектур,

формируют и анализируют графы передачи управления на основании вышеуказанных найденных команд,

после чего принимают решение о правильности идентификации аппаратной архитектуры на основании полученных характеристик графов передачи управления.

2. Способ по п. 1, отличающийся тем, что исключают из образа памяти исследуемого устройства области высокоэнтропийных данных, определяемых по значению параметра энтропии по крайней мере в 0,9.

3. Способ по п. 1, отличающийся тем, что исключают из образа памяти исследуемого устройства области низкоэнтропийных данных, определяемых по значению параметра энтропии менее 0,3 при размере окна оценки не более 5000 байт.

4. Способ по п. 1, отличающийся тем, что поиск команд условных и безусловных переходов по относительному смещению в соответствии с предположительной аппаратной архитектурой осуществляют посредством сплошного декодирования бинарных данных.

5. Способ по п. 1, отличающийся тем, что анализ графов передачи управления выполняют посредством расчета гистограммы количества ребер, заканчивающихся на одном и том же адресе, причем первые три столбца с индексами 0, 1 и 2 отбрасываются.

6. Способ по п. 1, отличающийся тем, что анализ графов передачи управления выполняют посредством расчета общего количества непосредственно примыкающих друг другу в адресном пространстве ребер и количества ребер, начинающихся непосредственно перед окончанием условного перехода.

7. Способ по п. 1, отличающийся тем, что на этапе принятия решения о правильности идентификации аппаратной архитектуры происходит параллельное декодирование команд нескольких архитектур и характеристики графов передачи управления анализируются для всех доступных архитектур одновременно, после чего выбирают ту архитектуру, для которой выполняется два условия: гистограмма количества ребер не соответствует экспоненциальному закону распределения, т.е. отношения между соседними столбцами значительно меньше 10; отношение количества ребер, начинающихся непосредственно перед окончанием условного перехода, к общему количеству непосредственно примыкающих друг другу в адресном пространстве ребер больше 0,01.

| СПОСОБ И СИСТЕМА ОПРЕДЕЛЕНИЯ ПРИНАДЛЕЖНОСТИ ПРОГРАММНОГО ОБЕСПЕЧЕНИЯ ПО ЕГО МАШИННОМУ КОДУ | 2019 |

|

RU2728497C1 |

| US 6014513 A1, 11.01.2000 | |||

| US 20150248556 A1, 03.09.2015 | |||

| US 20060101435 A1, 11.05.2006 | |||

| US 8381185 B2, 19.02.2013 | |||

| KR 101754720 B1, 19.07.2017 | |||

| US 9135442 B1, 15.09.2015 | |||

| WO 2016049373 A1, 31.03.2016 | |||

| Edward Raff, "An Alternative to NCD for Large Sequences, Lempel-Ziv Jaccard Distance", 22.09.2018, URL: | |||

Авторы

Даты

2024-04-26—Публикация

2022-07-05—Подача