импульсов, длительность которых и паузы между ними являются случайными. Целью изобретения является расширение функциональных возможностей за счет обеспечения возможности задержки апериодической последовательности импульсов, средний период следования которых меньше времени задержки. Для достижения указанной цели в устройстве в каждый канал задержки фронта импульса введены первый регистр памяти 6, блок вычитания 7, первьй блок памяти 8, первый коммутатор кодов 9, второй реве сивный счетчик 10, элемент И 12, второй триггер 13, блок выделения фронта импульса, первый адресный

1

Изобретение относится к импульсной технике и может быть использовано в устройствах различного назначения, где необходимо получение большого регулируемого цифровым кодом времени задержки последовательности импульсов, длительность которых и па узы между ними являются случайными.

Цель изобретения - расширение функциональных возможностей за счет обеспечения возможности задержки апериодической последовательности импульсов, средний период следования которых меньше времени задержки..

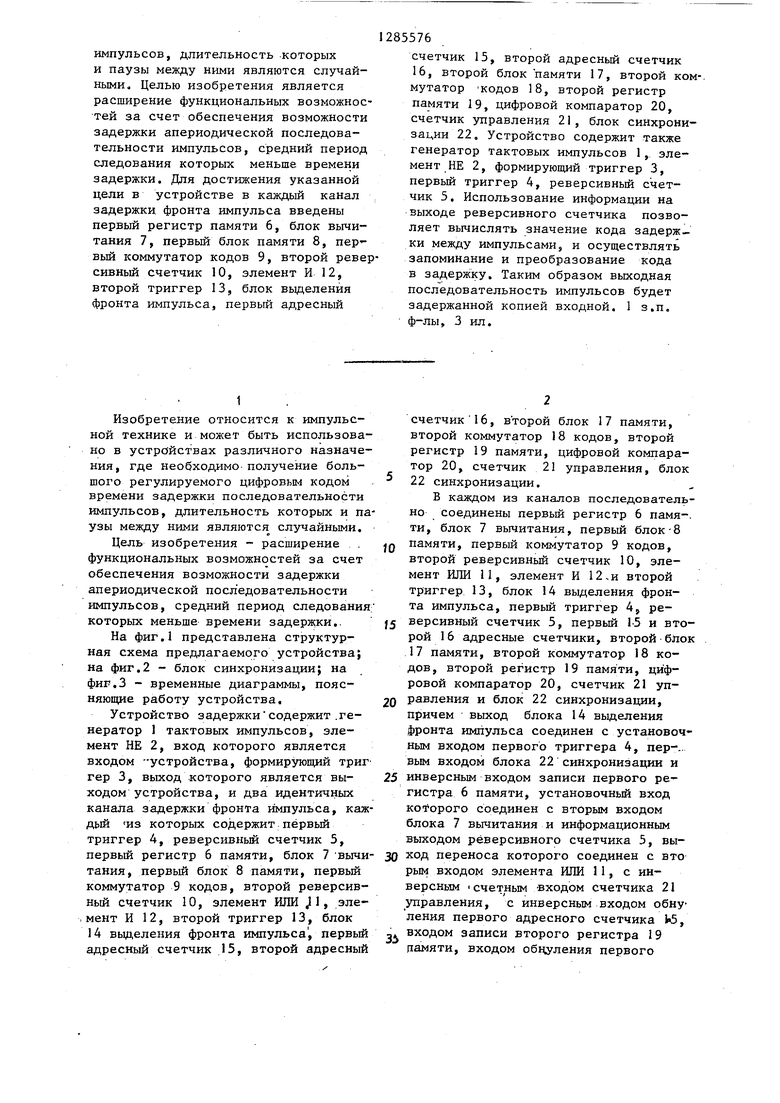

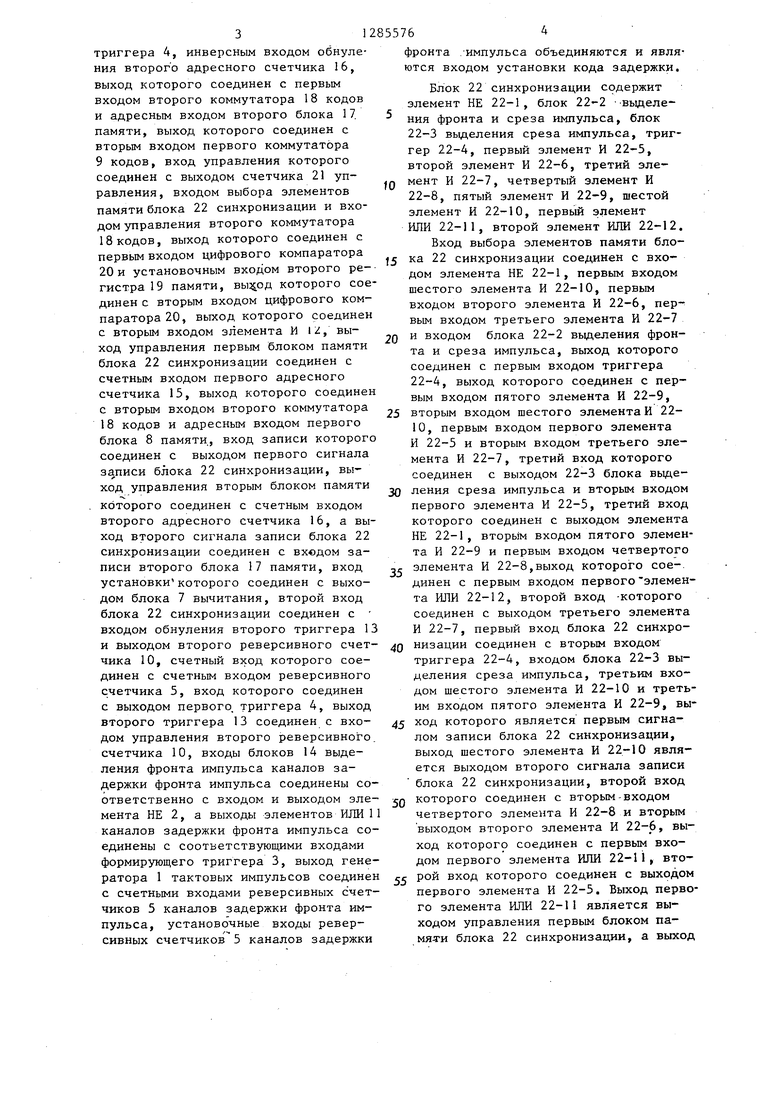

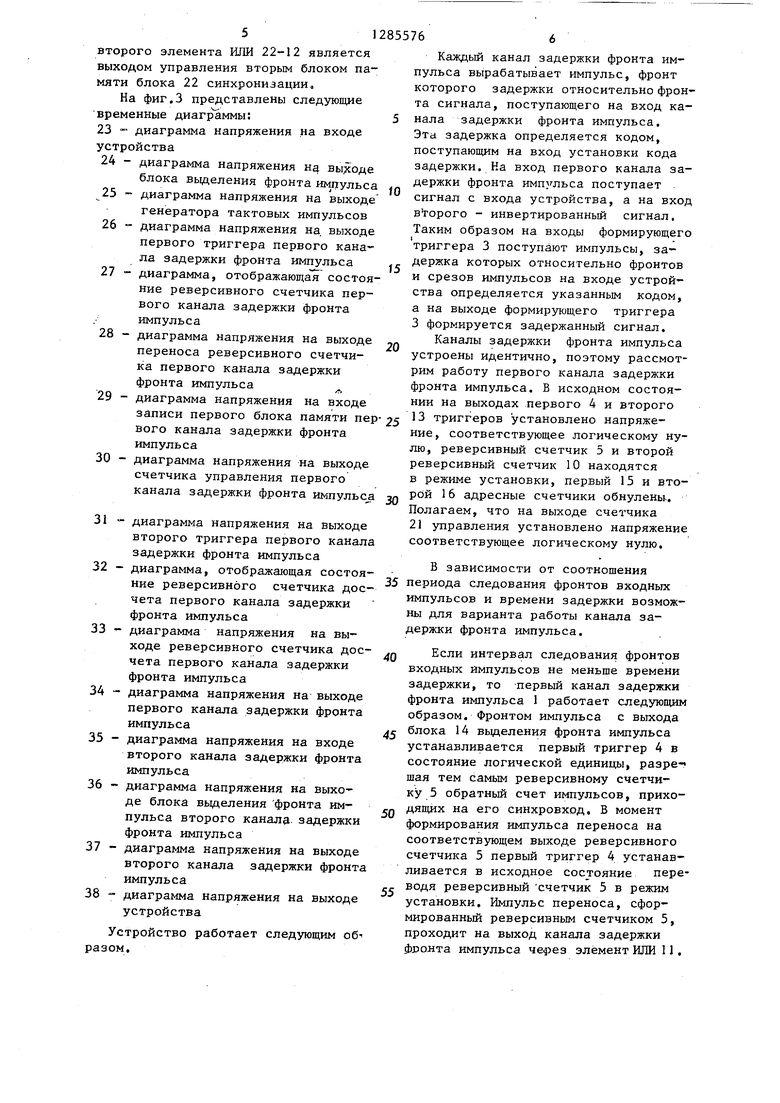

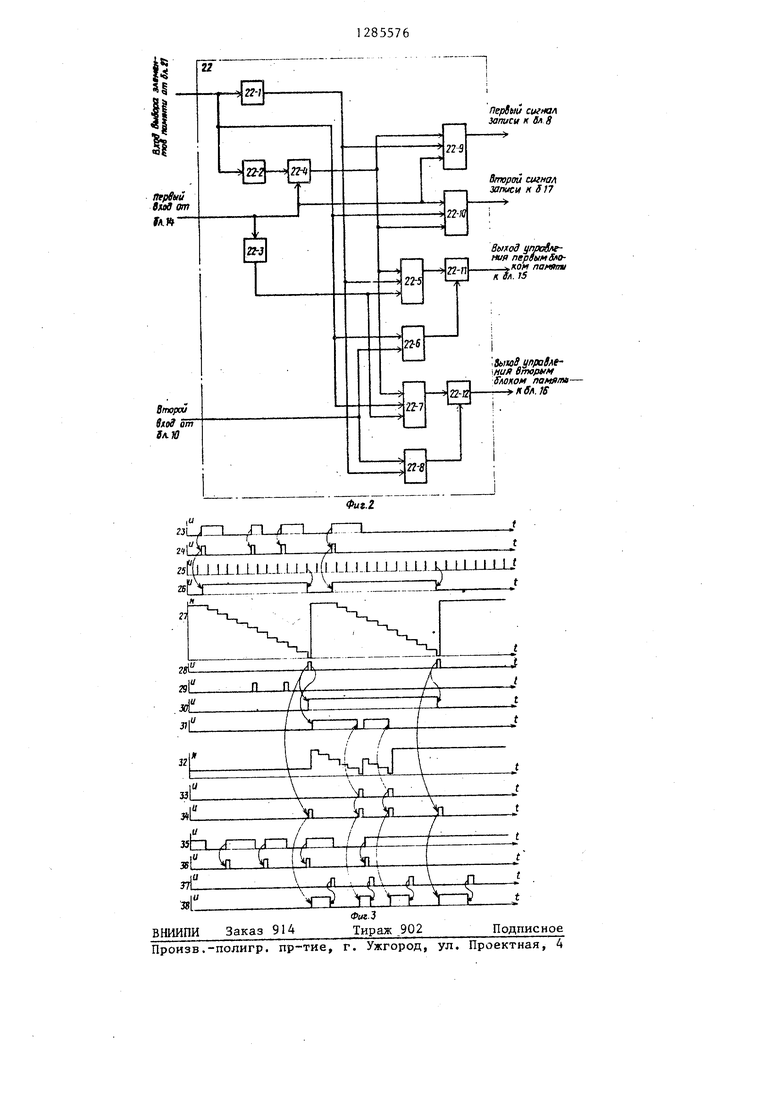

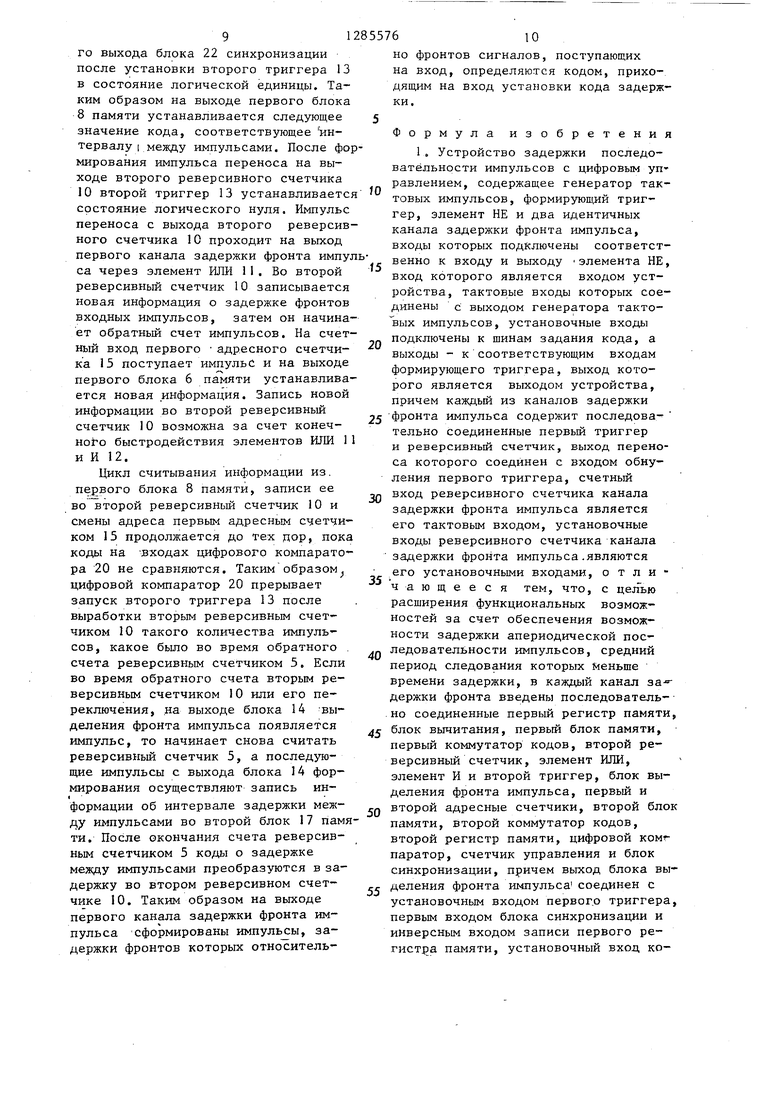

На фиг.1 представлена структурная схема предлагаемого устройства; на фиг.2 - блок синхронизации; на фир.З - временные диаграммы, поясняющие работу устройства.

Устройство задержки содержит .генератор 1 тактовых импульсов, элемент НЕ 2, вход которого является входом устройства, формирующий триг гер 3, выход которого является выходом устройства, и два идентичных канала задержки фронта импульса, каж дьй ИЗ которых содержит первый триггер 4, реверсивный счетчик 5, первый регистр 6 памяти, блок 7 вычитания, первьй блок 8 памяти, первьй коммутатор 9 кодов, второй реверсив- ньй счетчик 10, элемент ИЛИ J1, элемент И 12, второй триггер 13, блок 14 выделения фронта импульса , первьй адресный счетчик 15, второй адресный

285576

счетчик 15, второй адресный счетчик 16, второй блок памяти 17, второй коммутатор КОДОВ 18, второй регистр памяти 19, цифровой компаратор 20, счетчик управления 21, блок синхронизации 22, Устройство содержит также генератор тактовых импульсов 1, элемент НЕ 2, формирующий триггер 3, первый триггер 4, реверсивный счетчик 5, Использование информации на выходе реверсивного счетчика позволяет вычислять значение кода задержки между импульсами, и осуществлять запоминание и преобразование кода в задержку. Таким образом выходная последовательность импульсов будет задержанной копией входной, 1 з,п, ф-лы, 3 ил.

счетчик 16, второй блок 17 памяти, второй коммутатор 18 кодов, второй регистр 19 памяти, цифровой компаратор 20, счетчик 21 управления, блок

22 синхронизации,

В каждом из каналов последовательно соединены первьй регистр 6 памя-. ти, блок 7 вычитания, первьй блок-8

памяти, первьй коммутатор 9 кодов, второй реверсивньй счетчик 10, элемент ИЛИ 11, элемент И 12,и второй триггер 13, блок 14 выделения фронта импульса, первьй триггер 4, реверсивньй счетчик 5, первьй 1-5 и второй 16 адресные счетчики, второй-блок 17 памяти, второй коммутатор 18 кодов, второй регистр 19 памяти, ци ф- ровой компаратор 20, счетчик 21 управления и блок 22 синхронизации, причем выход блока 14 вьщеления фронта импульса соединен с установочным входом первого триггера 4, пер-.. вым входом блока 22 синхронизации и

инверсньш входом записи первого регистра 6 памяти, установочньй вход которого соединен с вторым входом блока 7 вычитания и информационным выходом реверсивного счетчика 5, выход переноса которого соединен с вто рым входо1м элемента ИЛИ 11, с инверсным Счетным -входом счетчика 21 управления, с инверсным входом обнуления первого адресного счетчика , входом записи второго регистра 19 дамяти, входом обнуления первого

триггера 4, инверсным входом обнуления второго адресного счетчика 16, выход которого соединен с первым входом второго коммутатора 18 кодов и адресным входом второго блока 17. памяти, выход которого соединен с вторым входом первого коммутатора 9 кодов, вход управления которого соединен с выходом счетчика 21 управления, входом выбора элементов памяти блока 22 синхронизации и входом управления второго коммутатора 18 кодов, выход которого соединен с первым входом цифрового компаратора 20 и установочным входом второго регистра 19 памяти, которого соединен с вторым входом цифрового компаратора 20, выход которого соединен с вторым входом элемента И I/, выход управления первым блоком памяти блока 22 синхронизации соединен с счетным входом первого адресного счетчика 15, выход которого соединен с вторьш входом второго коммутатора 18 кодов и адресным входом первого блока 8 памяти., вход записи которого соединен с выходом первого сигнала записи блока 22 синхронизации, выход управления вторым блоком памяти которого соединен с счетным входом второго адресного счетчика 16, а выход второго сигнала записи блока 22 Синхронизации соединен с вхвдом записи второго блока 17 памяти, вход установки которого соединен с выходом блока 7 вычитания, второй вход блока 22 синхронизации соединен с входом обнуления второго триггера 13 и выходом второго реверсивного счетчика 10, счетный вход которого соединен с счетным входом реверсивного счетчика 5, вход которого соединен с выходом первого, триггера 4, выход второго триггера 13 соединен с входом управления второго реверсивного, счетчика 10, входы блоков 14 выделения фронта импульса каналов задержки фронта импульса соединены соответственно с входом и выходом элемента НЕ 2, а выходы элементов ШШ 1 каналов задержки фронта импульса соединены с соответствующими входами формирующего триггера 3, выход генератора 1 тактовых импульсов соединен с счетными входами реверсивных счетчиков 5 каналов задержки фронта импульса, установочные входы реверсивных счетчиков 5 каналов задержки

фронта -импульса объединяются и являются входом установки кода задержки.

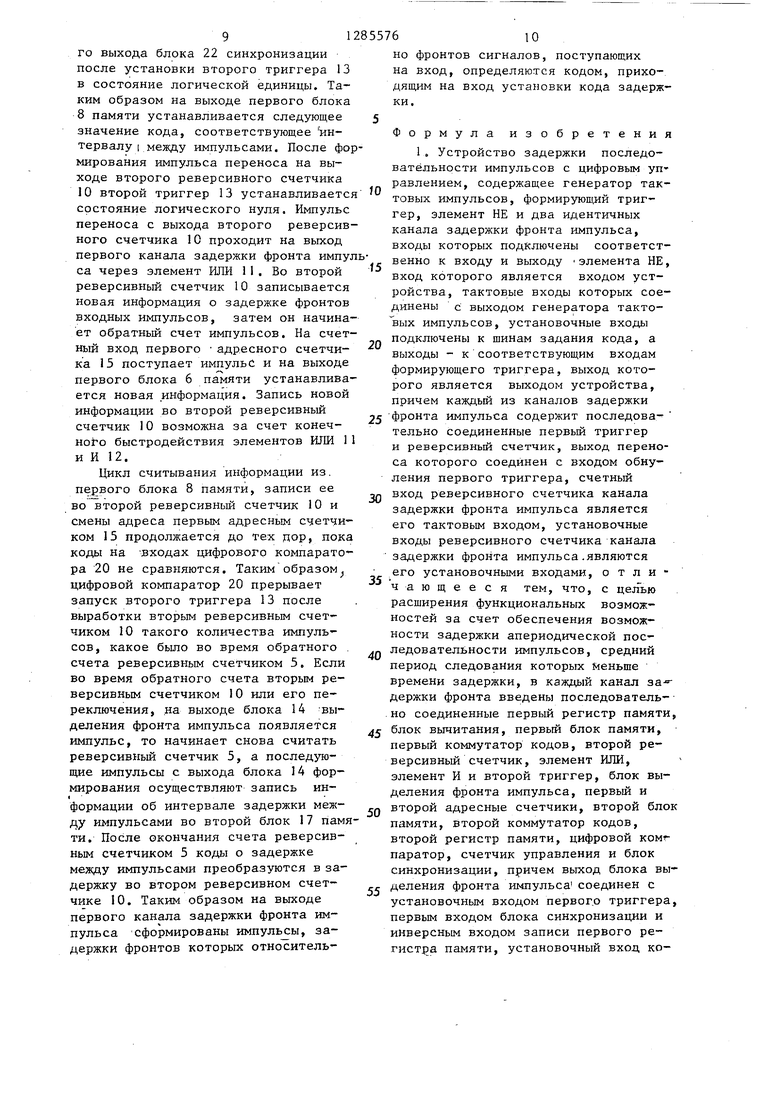

Блок 22 синхронизации содержит элемент НЕ 22-1, блок 22-2 --выделе ния фронта и среза импульса, блок 22-3 выделения среза импульса, триггер 22-4, первый элемент И 22-5, второй элемент И 22-6, третий элемент И 22-7, четвертый элемент И 22-8, пятый элемент И 22-9, шестой элемент И 22-10, первый элемент ИЛИ 22-11, второй элемент ИЛИ 22-12. Вход выбора элементов памяти блока 22 синхронизации соединен с входом элемента НЕ 22-1, первым входом шестого элемента И 22-10, первым входом второго элемента И 22-6, пер- вым входом третьего элемента И 22-7

и входом блока 22-2 выделения фронта и среза импульса, выход которого соединен с первым входом триггера 22-4, выход которого соединен с первым входом пятого элемента И 22-9,

вторым входом шестого элемента И 22- 10, первым входом первого элемента И 22-5 и вторым входом третьего элемента И 22-7, третий вход которого соединен с выходом 22-3 блока выделения среза импульса и вторым входом первого элемента И 22-5, третий вход которого соединен с выходом элемента НЕ 22-1 , BTopbiM входом пятого элемента И 22-9 и первым входом четвертого

элемента И 22-8,выход которого сое-. динен с первым входом первого элемента ИЛИ 22-12, второй вход -которого соединен с выходом третьего элемента И 22-7, первый вход блока 22 синхронизации соединен с вторым входом

триггера 22-4, входом блока 22-3 выделения среза импульса, третьим входом шестого элемента И 22-10 и третьим входом пятого элемента И 22-9, выход которого является первым сигналом записи блока 22 синхронизации, выход шестого элемента И 22-10 является выходом второго сигнала записи блока 22 синхронизации, второй вход

которого соединен с вторым-входом четвертого элемента И 22-8 и вторым выходом второго элемента И 22-6, выход которого соединен с первым входом первого элемента ИЛИ 22-11, вто- рой вход которого соединен с выходом первого элемента И 22-5. Выход первого элемента ИЛИ 22-11 является выходом управления первь№1 блоком памяти блока 22 синхронизации, а выход

25

26

27 28 29 30 to

5

торого элемента ИЛИ 22-12 является ыходом управления вторьш блоком паяти блока 22 синхронизации.

На фиг.З представлены следующие ременные диаграммы: 3 - диаграмма напряжения на входе стройства

24 - диаграмма напряжения на выводе блока выделения фронта им пульса диаграмма напряжения на выходе генератора тактовых импульсов диаграмма напряжения на. выходе первого триггера первого канала задержки фронта импульса диаграмма, отображающа я состояние реверсивного счетчика первого канала задержки фронта импульса

диаграмма напряжения на выходе переноса реверсивного счетчика первого канала задержки фронта импульса диаграмма напряжения на входе записи первого блока памяти пер- 25 вого канала задержки фронта импульса

диаграмма напряжения на выходе счетчика управления первого канала задержки фронта импульса

f5

12855

20

30

диаграмма напряжения на выходе второго триггера первого канала задержки фронта импульса диаграмма, отображающая состояние реверсивного счетчика дос- чета первого канала задержки фронта импульса диаграмма напряжения на выходе реверсивного счетчика дос- чета первого канала задержки фронта импульса диаграмма напряжения на выходе первого канала задержки фронта импульса

диаграмма напряжения на входе второго канала задержки фронта импульса

диаграмма напряжения на выходе блока выделения фронта импульса второго канала задержки фронта импульса

диаграмма напряжения на выходе второго канала задержки фронта импульса

диаграмма напряжения на выходе устройства

стройство работает следующим об- ом.

to

- 25

f5

2855766

Каждый канал задержки фронта импульса вырабатывает импульс, фронт которого задержки относительно фронта сигнала, поступающего на вход канала задержки фронта импульса. Эта задержка определяется кодом, поступающим на вход установки кода задержки. На вход первого канала задержки фронта имп}шьса поступает сигнал с входа устройства, а на вход второго - инвертированный сигнал.

Таким образом на входы формирующего 1 „

триггера 3 поступают импульсы, задержка которых относительно фронтов и срезов импульсов на входе устройства определяется указанным кодом, а на выходе формирующего триггера 3 формируется задержанный сигнал.

Каналы задержки фронта импульса устроены идентично, поэтому рассмотрим работу первого канала задержки фронта импульса. В исходном состоянии на выходах первого 4 и второго 13 триггеров установлено напряжение, соответствующее логическому нулю, реверсивный счетчик 5 и второй реверсивный счетчик 10 находятся в режиме установки, первый 15 и второй 16 адресные счетчики обнулены. Полагаем, что на выходе счетчика 21 управления установлено напряжение соответствующее логическому нулю.

20

30

В зависимости от соотношения 35 периода следования фронтов входных импульсов и времени задержки возможны для варианта работы канала задержки фронта импульса.

Если интервал следования фронтов входных импульсов не меньше времени задержки, то первьш канал задержки фронта импульса 1 работает следующим образом. Фронтом импульса с выхода блока 14 выделения фронта импульса устанавливается первый триггер 4 в состояние логической единицы, разре- шая тем самым реверсивному счетчику 5 обратньй счет импульсов, приходящих на его синхровход. В момент формирования импульса переноса на соответствующем выходе реверсивного счетчика 5 первый триггер 4 устанавливается в исходное состояние переводя реверсивный счетчик 5 в режим установки. Импульс переноса, сформированный реверсивным счетчиком 5, проходит на выход канала задержки фвонта импульса элемент ИЛИ 11.

71

В том случае, если интервал следования фронтов входных импульсов меньше времени задержки, первый канал задержки фронта импульса работает следующим образом. Фронтом импульса с выхода блока 14 выделения фронта импульса первый триггер 4 устанавливается в состояние логической единицы, разрешая тем самым обратный счет импульсов, приходящих на счетный вход реверсивного счетчика 5 срезом импульса с выхода блока 14 выделения фронта импульса. Значение кода на информационном выхО|Де реверсивного счетчика 5 заносится в первый регистр 6 памяти. При этом фронтом следующего импульса с выхода блока 14 вьщеления фронта импульса код, соответствующий интервалу задержки между фронтами импульсов, поступающих на вход первого канала задердки фронта импульса, записывается в соответствующую ячейку первого блока 8 памяти. Импульс для записи информации в первый блок 8 памяти поступает от блока 22 синхронизации. По срезу импульса с выхода блока 14 выделения фронта импульса, блок 22 синхронизации вырабатывает импульс, который поступает на счетный вход первого адресного счетчика 15 для подготовки к записи следующей ячейки первого блока 8 памяти.

Срезом импульса с выхода блока

14выделения фронта импульса код с информационного выхода реверсивного счетчика 5 переписывается в первый регистр 6 памяти. Б момент формирования фронта следующего импульса на выходе блока 14 выделения фронта импульса код, соответствующий интервалу задержки между фронтами импульсов на входе первого канала задержки фронта импульса, записывается в следующую ячейку первого бло-- ка 8 памяти. Затем вновь меняется адрес для записи новой информации

В первый блок 8 памяти. Цикл, состоящий из записи соответствующего кода в первый блок 8 памяти, смены адреса первого адресного счетчика

15и записи информации в первый регистр 6 памяти повторяется каждый раз после формирования импульса на выходе блока 14 выделения фронта

импульса во время обратного счета реверсивного счетчика 5. Таким образом коды, соответствующие интервалу

8

задержки между фронтами входных импульсов, записываются в первый блок 8 памяти, а этот код вычисляется в блоке 7 вычитания как разность кодов предыдущего и текущего кодов на информационном выходе реверсивного счетчика 5.

0

NH

Np - N..

5

0

5

0

5

0

5

0

где N|,| - код на выходе блока вычитания ;

N код, хранящийся.в первом регистре памяти, который соответствует коду на информационном выходе реверсивного счетчика в момент прихода фронта предыдущего импульса с выхода блока выделения фронта импульса; N - текущий код на, информационном выходе реверсивного счетчика.

После окончания счета на выходе переноса реверсивного счетчика 5 вырабатывается импульс, который устанавливает первый триггер в исходное состояние. Этот же импульс цроходит на выход первого канала задержки фронта импульса через элемент ИЛИ 11. Фронтом и шyльca переноса во второй регистр 19 памяти ззписывает- ся код с выхода первого адресного счетчика 15. Таким образом, во втором регистре 19 памяти хранится код, соответствующий количеству входных импульсов, приходящих за время обратного счета реверсивного счетчика 5. Спадом импульса переноса с соответствующего выхода реверсивного счетчика 5 счетчик 21 управления устанавливается в состояние логической единицы. При этом выход первого блока 8 памяти подключается через первый коммутатор кодов к соответствующему входу второго ревер- сивного счетчика 10 Таким .образом во второй реверсивньй счетчик 10 записывается код из первой ячейки первого блока 8 памяти.

После этого на вход второго триггера 13 поступает импульс, устанавли вая его в состояние логической еди- ницы, И второй реверсивный счетчик 10 начинает обратный счет импульсов, приходящих на счетный вход. На счетный вход первого адресного счетчика , 15 приходит импульс с соответствующего выхода блока 22 синхронизации после установки второго триггера 13 в состояние логической единицы. Таким образом на выходе первого блока 8 памяти устанавливается следующее значение кода, соответствующее интервалу i между импульсами. После формирования импульса переноса на выходе второго реверсивного счетчика 10 второй триггер 13 устанавливается состояние логического нуля. Импульс переноса с выхода второго реверсивного счетчика 10 проходит на выход первого канала задержки фронта импул са через элемент ИЛИ II. Во второй реверсивный счетчик 10 записывается новая информация о задержке фронтов входных импульсов, затем он начинает обратный счет импульсов. На счетный вход первого адресного счетчика 15 поступает импульс и на выходе первого блока 6 памяти устанавливается новая информация. Запись новой информации во второй реверсивный счетчик 10 возможна за счет конечного быстродействия элементов ИЛИ 11 и И 12.

Цикл считывания информации из. первого блока 8 памяти, записи ее во второй реверсивный счетчик Ю и смены адреса первым адресным счетчиком 15 продолжается до тех дор, пока коды на -входах цифрового компаратора 20 не сравняются. Таким образом цифровой компаратор 20 прерывает запуск второго триггера 13 после выработки вторым реверсивным счетчиком 10 такого количества импульсов, какое бьшо во время обратного . счета реверсивным счетчиком 5. Если во время обратного счета вторым реверсивным счетчиком 10 ши его переключения, на выходе блока 14 -выделения фронта импульса появляется импульс, то начинает снова считать реверсивный счетчик 5, а последующие импульсы с выхода блока 14 формирования осуществляют запись информации об интервале задержки меж- l,y импульсами во второй блок 17 памяти. После окончания счета реверсивным счетчиком 5 коды о задержке между импульсами преобразуются в задержку во втором реверсивном счетчике 10. Таким образом на выходе первого канала задержки фронта импульса сформированы импуль сы, задержки фронтов которых относительO

5

0

5

но фронтов сигналов, поступающих на вход, определяются кодом, прихо-, дящим на вход установки кода задержки.

Формула изобретения

1. Устройство задержки последовательности импульсов с цифровым управлением, содержащее генератор тактовых импульсов, формирующий триггер, элемент НЕ и два идентичных канала задержки фронта импульса, входы которых подключены соответственно к входу и выходу Элемента НЕ, вход которого является входом устройства, тактовые входы которых соединены с выходом генератора такто- Ъых импульсов, установочные входы подключены к шинам задания кода, а выходы - к соответствующим входам формирующего триггера, выход которого является выходом устройства, причем каждый из каналов задержки фронта импульса содержит последова- тельно соединенные первый триггер и реверсивный счетчик, выход переноса которого соединен с входом обнуления первого триггера, счетный вход реверсивного счетчика канала задержки фронта импульса является его тактовым входом, установочные входы реверсивного счетчика канала задержки фронта импульса.являются его установочными входами, отличающееся тем, что, с целью расширения функциональных возможностей за счет обеспечения возможности задержки апериодической последовательности импульсов, средний период следования которых меньше времени задержки, в каждый канал держки фронта введены последователь- .но соединенные первый регистр памяти, 5 блок вычитания, первый блок памяти, первый коммутатор кодов, второй реверсивный счетчик, элемент ИЛИ, элемент И и второй триггер, блок выделения фронта импульса, первый и второй адресные счетчики, второй блок памяти, второй коммутатор кодов, второй регистр памяти, цифровой комг паратор, счетчик управления и блок синхронизации, причем выход блока вы деления фронта импульса соединен с установочным входом первог.о триггера, первым входом блока синхронизации и инверсным входом записи первого регистра памяти, установочный вход ко0

5

0

0

5

и12

торого соединен с вторым входом блока вычитания и информационным выходом реверсивного счетчика, выход переноса которого соединен с вторым входом элемента ИЛИ, с инверсным счетчиком входа счетчика управления, с инверсным входом обнуления первого адресного счетчика, входом записи второго регистра памяти, инверсным входом обнуления второго адресного счетчика, выход которого соединен с первым входом второго коммутатора кодов и адресным входом второго блока памяти, выход которого соединен с вторым входом первого коммутатора кодов, вход управления которого соединен с выходом счетчика управления, входом выбора элементов памяти блока синхронизации и входом управления второго коммутатора кодов, выход которого соединен с первым входом цифрового компаратора и установочным входом второго регистра памяти, выход которого соеди

нен с вторым входом цифрового компа- выходом элемента НЕ, вторым-входом

ратора, выход которого соединен с вторым входом . элемента И, первый выход управления блока синхронизации соединен с счетным входом первого адресного счетчика, выход которого соединен с вторым входом второго коммутатора кодов и адресным входом первого блока памяти, вход записи которого соединен с выходом первого сигнала записи блока синхронизации, выход управления вторым блоком памяти которого соединен с счетным входом второго адресного счетчика, а выход- второго сигнала записи блока синхро- низации соединен с входом записи второго блока памяти, вход установ ки которого соединен с выходом блока вычитания, второй вход блока синхронизации соединен с входом обну- ления второго триггера и выходом второго реверсивного счетчика, -счетный, вход которого соединен с счетньм входом реверсивного счетчика, выход второго триггера соединен с входом управления второго реверсивного счетчика, вход блока выделения фронта импульса является входом первого и второго канала задержки фронта

30

пятого элемента И и первь1М входом четвертого элемента И, выход которого соединен с первым входом второго элемента ИЛИ, второй вход которого соединен с выходом третьего элемента И, первый вход блока синхронизации соединен с вторым входом тригге ра, входом блока выделению среза импульса, третьим входом шестого элемента И и третьим входом пятого элемента И, выход которого является первым сигналом записи блока синхронизации, выход шестого элемента И является выходом второго сигнала записи блока синхронизации, второй вход которого соединен с вторым входом четвертого элемента И и вторым выходом второго элемента И, выход которого соединен с первым входом первого элемента ИЛИ, второй вход которого соединен с выходом первого элемента И, выход первого элемента И является выходоц управ- ления первым блоком памяти блока

40

45

50

синхронизации, а выход второго элемента ИЛИ является выходом управления вторым блоком памяти блока синхронизации.

6

12

импульса, а выход элементов ИЛИ канала задержки фронта импульса является его выходом.

2. Устройство поп.1,отлича- ю щ е е с я тем, что блок синхрони ;

зации содержит элемент НЕ, вход ко-. торого является входом выбора элементов памяти блока синхронизации, соединенным с первым входом второго элемента И, первым входом третьего элемента И и входом блока выделения фронта и среза импульса, выход которого соединен с первым входом триггера, выход которого соединен с первым входом пятого элемента И, вторым входом шестого элемента И, первым входом первого элемента И и вторым входом третьего элемента И, третий вход которого соединен с выходом блока выделения среза импульса и вторым входом первого элемента И, третий вход которого соединен с

пятого элемента И и первь1М входом четвертого элемента И, выход которого соединен с первым входом второго элемента ИЛИ, второй вход которого соединен с выходом третьего элемента И, первый вход блока синхронизации соединен с вторым входом триггера, входом блока выделению среза импульса, третьим входом шестого элемента И и третьим входом пятого элемента И, выход которого является первым сигналом записи блока синхронизации, выход шестого элемента И является выходом второго сигнала записи блока синхронизации, второй вход которого соединен с вторым входом четвертого элемента И и вторым выходом второго элемента И, выход которого соединен с первым входом первого элемента ИЛИ, второй вход которого соединен с выходом первого элемента И, выход первого элемента И является выходоц управ- ления первым блоком памяти блока

синхронизации, а выход второго элемента ИЛИ является выходом управления вторым блоком памяти блока синхронизации.

N

22

22-2- гм

Пгрвни вив от

Л -

22-3

Второй вхоУ от Ул.Ю

сигнал записи к 8л 8

Smopou сигнал записи к S17

22-ю

Выкод unpaSflf- пия первым5т мн пампт

кал. 15

ЗыюВ unpaSAf- ния BmofjtfM SwxoM памяам- -..lS

22-7

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство ввода информации | 1985 |

|

SU1273936A2 |

| Устройство для ретрансляции речевых сигналов | 1990 |

|

SU1830627A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Цифровой функциональный преобразователь | 1983 |

|

SU1098006A1 |

| Мажоритарное декодирующее устройство | 1986 |

|

SU1372627A1 |

| Устройство для коррекции программ | 1990 |

|

SU1751768A1 |

| Устройство для упорядочивания чисел | 1983 |

|

SU1144103A1 |

| Устройство для моделирования радиотелеграфного канала связи | 1981 |

|

SU1034053A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| УСТРОЙСТВО ДЛЯ ОТОБРАЖЕНИЯ ИНФОРМАЦИИ НА ЭКРАНЕ ТЕЛЕВИЗИОННОГО ИНДИКАТОРА | 1991 |

|

RU2018977C1 |

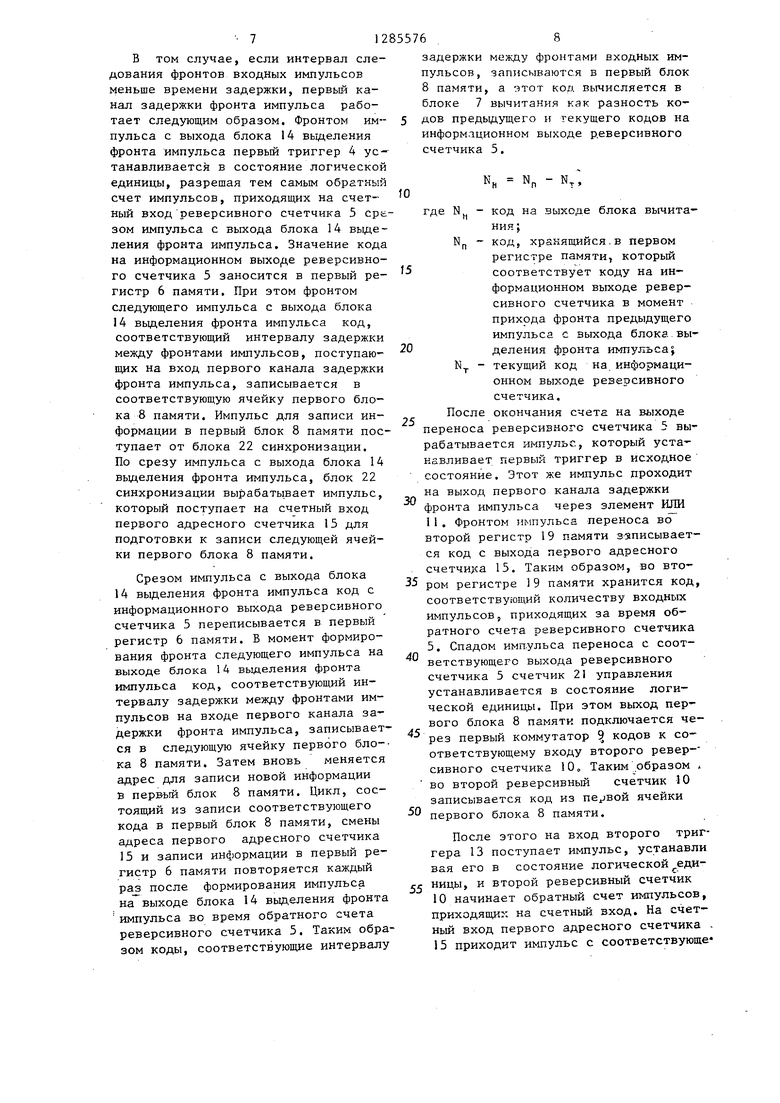

Изобретение относится к импульсной технике и может быть ,использовано в устройствах различного назначения, где необходимо получение большого регулируемого цифровым кодом времени задержки последовательности Первый канал задержки (йоонта импульса Вход установки кода эодер)кг (Л с Второй канал фронта умпульсо (риг. }

33 У

ВНИИПИ Заказ 914

Произв.-полигр. пр-тие, г. Ужгород, ул. Проектная, 4

Фиг.З Тираж ,902

Подписное

| Устройство для задержки прямоугольных импульсов | 1979 |

|

SU855977A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-01-23—Публикация

1985-07-12—Подача