Область техники

Изобретение относится к электронной технике и может использоваться при разработке микросхем, выполненных по комплементарной метал-окисел-полупроводник (КМОП) технологии, для создания переключающих схем с повышенным уровнем изоляции сигнала.

Предшествующий уровень техники

Из уровня техники известны технические решения, направленные на увеличение уровня изоляции переключателей, выполненных по КМОП технологии.

В зарубежной литературе приводятся способы увеличения изоляции переключателя с помощью следующих методов:

- использование шунтирующих транзисторов;

- включение последовательно нескольких транзисторов (Stacked Transistor Configuration);

- использование параллельной индуктивности для закрытого транзистора с целью получения параллельного контура.

Эти технические решения позволяют обеспечить изоляцию в диапазоне частот свыше 10 ГГц в пределах 20-30 дБ в зависимости от применяемого метода и технологического процесса и часто связаны с увеличением потерь при прямом прохождении сигнала.

Метод использования шунтирующих транзисторов представлен в [1, 2] и приводит к существенному увеличению потерь при попытках улучшить изоляционные свойства переключателя на высоких частотах за счет наличия паразитной емкости шунтирующего транзистора.

Включение нескольких последовательных транзисторов [3] также приводит к ослаблению сигнала в открытом состоянии переключателя за счет увеличения последовательного сопротивления в канале.

Метод использования параллельной индуктивности [4] с целью получения параллельного контура может работать только в узкой полосе частот и требует увеличения площади переключателя.

Раскрытие изобретения

Задачей предлагаемого изобретения является расширение функциональных возможностей КМОП переключающих схем.

Техническим результатом, на достижение которого направлено заявленное изобретение, является уменьшение и подавление на выходе паразитного сигнала, значительное увеличение уровня изоляции переключателя в выключенном состоянии при сохранении малых потерь во включенном состоянии за счет вариантов подключения МОП транзисторов, коммутирующих и компенсирующих сигнал.

Указанный технический результат достигается тем, что переключатель с высокой изоляцией по первому варианту содержит генератор дифференциального сигнала, МОП транзисторы, выходные порты, в котором две пары МОП транзисторов, коммутирующих сигнал (2-5), соединены напрямую с генератором, при этом пара МОП транзисторов 2, 5 соединена напрямую с выходным портом 11, а пара МОП транзисторов 3, 4 соединена напрямую с выходным портом 10, а одна пара МОП транзисторов, компенсирующих сигнал 7, 6, соединена от неинвертирующего вывода генератора к инвертирующим выводам первого 10 и второго 11 выходных портов соответственно, а другая пара МОП транзисторов, компенсирующих сигнал 8, 9, от инвертирующего вывода генератора к неинвертирующим выводам первого 10 и второго 11 выходных портов соответственно, причем все МОП транзисторы выполнены с одинаковой шириной канала; а переключатель с высокой изоляцией по второму варианту содержит также генератор дифференциального сигнала, МОП транзисторы, выходные порты, в котором две пары МОП транзисторов, коммутирующих сигнал (2-5), соединены напрямую с генератором, при этом пара МОП транзисторов 2, 5 соединена напрямую с выходным портом 11, а пара МОП транзисторов 3, 4 соединена напрямую с выходным портом 10, при этом они выполнены с одинаковой шириной канала, первый МОП транзистор, компенсирующий сигнал 6, соединен перекрестно от неинвертирующего вывода первого выходного порта 11 к инвертирующему выводу второго выходного порта 10, второй МОП транзистор, компенсирующий сигнал 7, соединен от инвертирующего вывода первого выходного порта 11 к неинвертирующему выводу второго выходного порта 10, кроме того, коммутирующие и компенсирующие МОП транзисторы выполнены с различной между собой шириной канала.

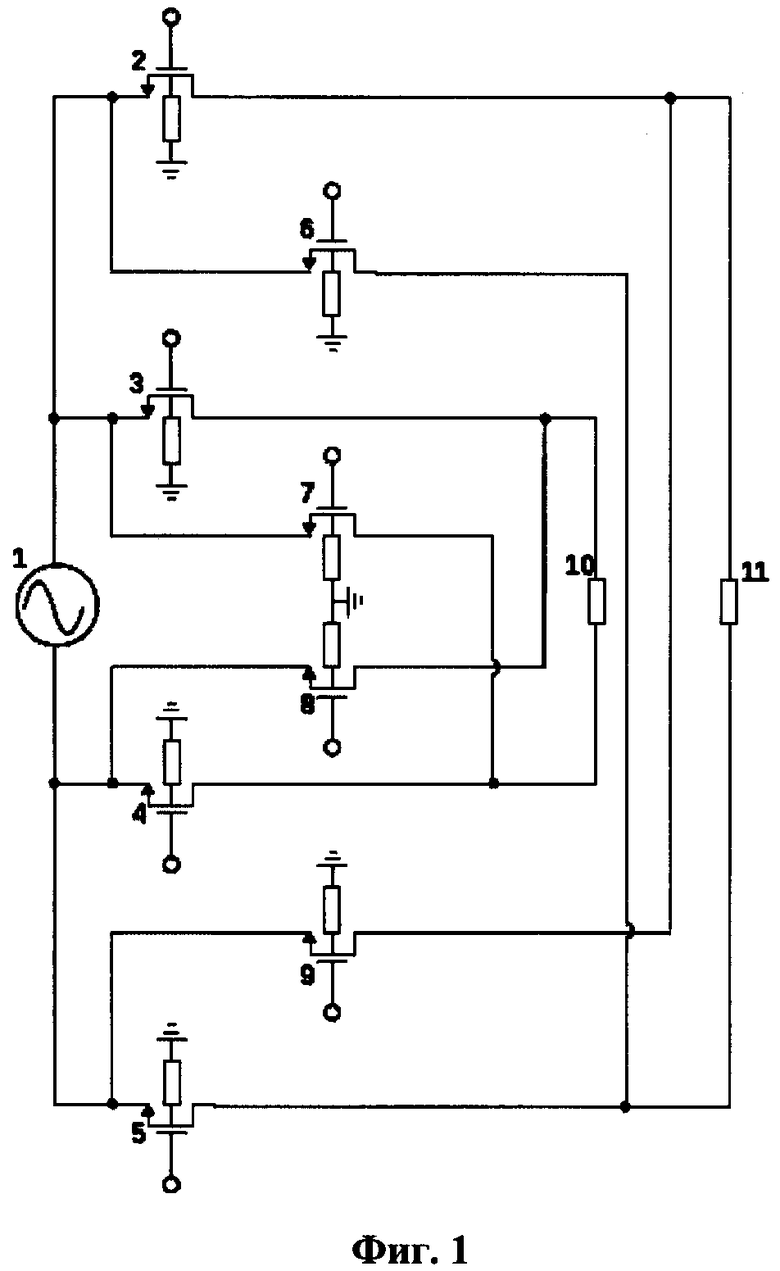

Предлагается два варианта переключателя типа «один в два» (Single Port Duble Throu - SPDT). Первый вариант - фиг. 1, позволяет осуществить максимальное подавление сигнала в выключенном состоянии, используя одинаковые структуры МОП ключей, второй вариант - фиг. 2, предполагает меньшие потери во включенном состоянии, но при этом используются структуры МОП ключей с различной геометрией, что в реальном исполнении приводит к неполной компенсации сигналов, а следовательно, меньшей изоляции.

Краткое описание чертежей

Сущность изобретения поясняется чертежами.

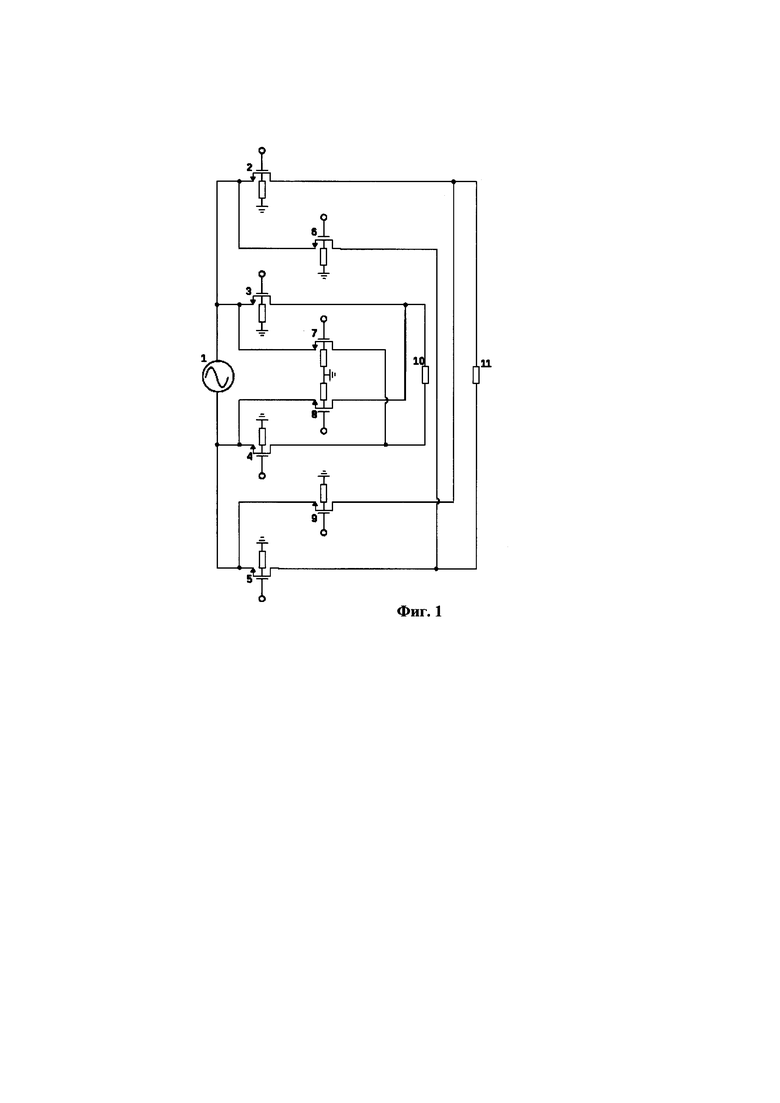

На фиг. 1 представлена принципиальная схема первого варианта заявляемого переключателя, выполненного на МОП структурах одинаковых размеров и конструкции, где:

1 - генератор дифференциального сигнала;

2, 3, 4, 5 - МОП транзисторы, коммутирующие сигнал;

6, 7, 8, 9 - МОП транзисторы, компенсирующие сигнал;

10 - первый выходной порт;

11 - второй выходной порт.

Переключатель содержит две пары МОП транзисторов, коммутирующих сигнал 2, 5 и 3, 4. Транзисторы в каждой паре находятся в одинаковом состоянии, т.е. каждая пара может находиться в открытом (низкоомном) или закрытом (высокоомном) состоянии. Обе пары транзисторов подключены к генератору дифференциального сигнала. МОП транзисторы, компенсирующие сигнал 6, 9 и 7, 8, всегда находятся в закрытом состоянии и имеют такую же структуру, как и МОП транзисторы, коммутирующие сигнал, а следовательно, и такую же паразитную проходную емкость в закрытом состоянии, поэтому паразитный сигнал на закрытом выходе полностью компенсируется сигналом противоположной полярности.

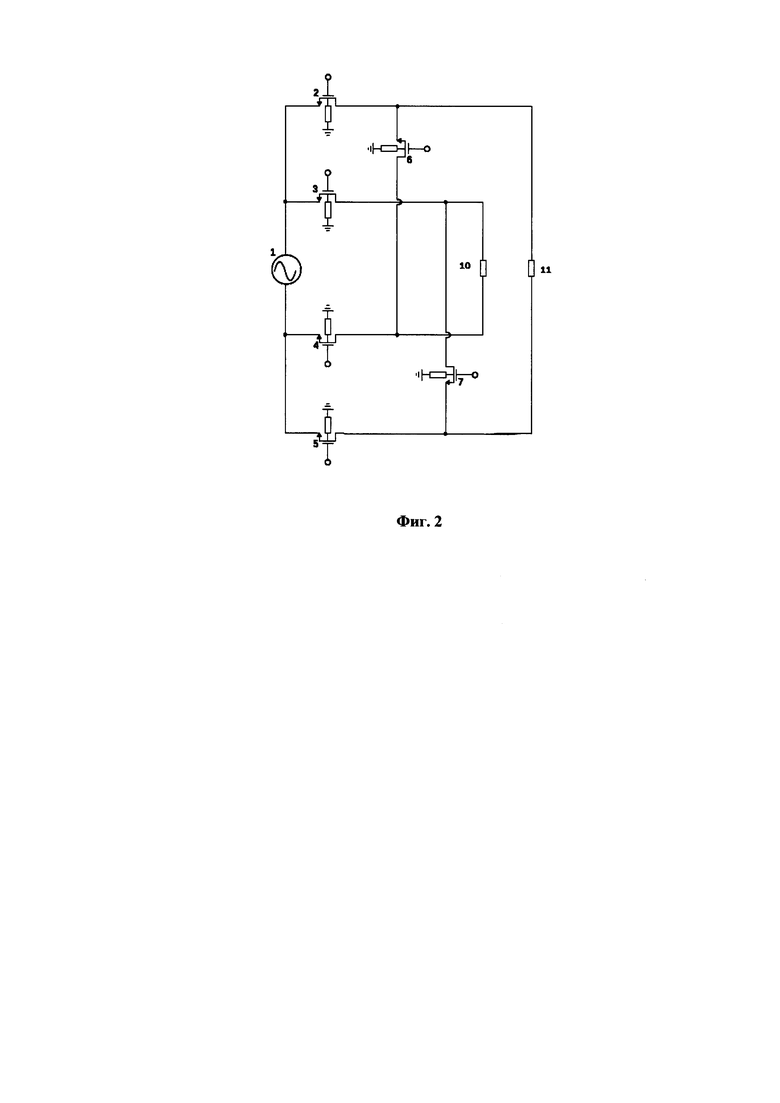

На фиг. 2 представлена принципиальная схема второго варианта заявляемого переключателя, выполненного на МОП структурах разных размеров и конструкции, где:

1 - генератор дифференциального сигнала;

2, 3, 4, 5 - МОП транзисторы, коммутирующие сигнал;

6, 7 - МОП транзисторы, компенсирующие сигнал;

10 - первый выходной порт;

11 - второй выходной порт.

Переключатель содержит две пары МОП транзисторов, коммутирующих сигнал 2, 5 и 3, 4. Транзисторы в каждой паре находятся в одинаковом состоянии, т.е. каждая пара может находиться в открытом (низкоомном) или закрытом (высокоомном) состоянии. Обе пары транзисторов подключены к генератору дифференциального сигнала. МОП транзисторы, компенсирующие сигнал 6 и 7, всегда находятся в закрытом состоянии и имеют ширину канала, отличающуюся от ширины канала транзисторов 2, 5, ширина каналов в транзисторах 6, 7 выбрана оптимально для достижения максимального уровня изоляции.

Осуществление изобретения

Работа устройства осуществляется следующим образом.

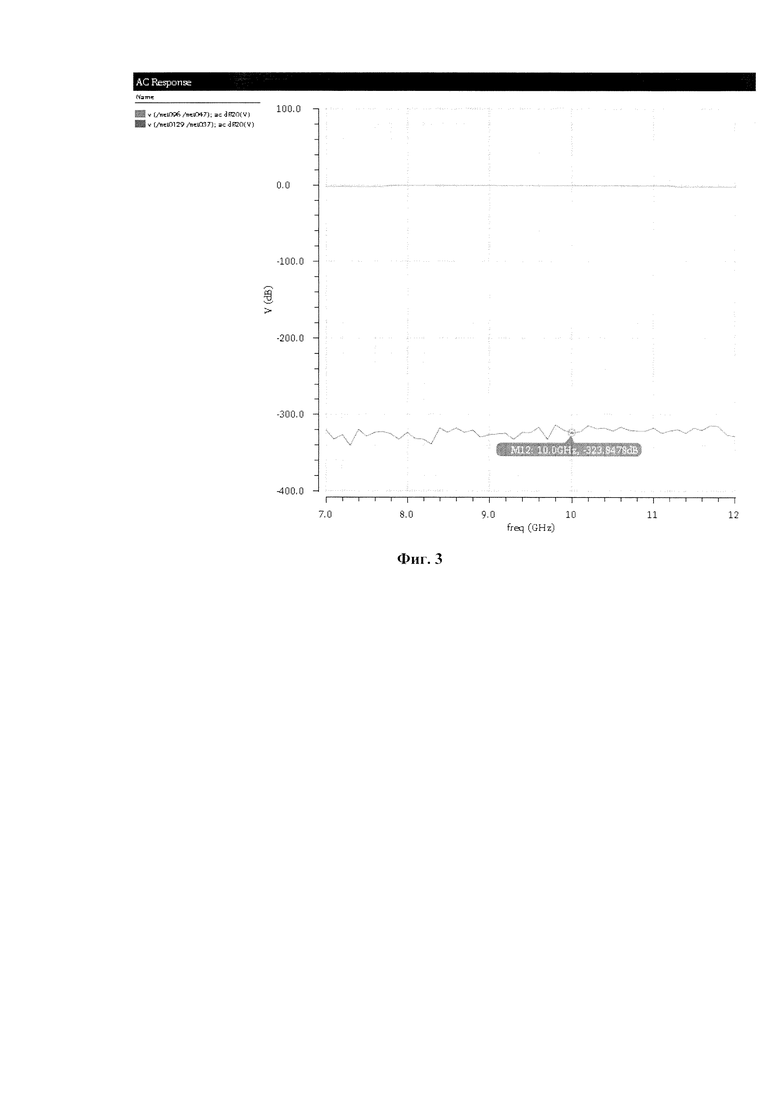

Схема, представленная на фиг. 1, работает таким образом, что сигнал от дифференциального генератора 1 поступает на две пары МОП транзисторов, коммутирующих сигнал (2-5), при этом пара МОП транзисторов 2, 5 находится в открытом состоянии, а пара МОП транзисторов 3, 4 в закрытом состоянии. Полезный сигнал через открытую пару МОП транзисторов, коммутирующих сигнал 2, 5 будет поступать на выходной порт 11. Паразитный сигнал через пару МОП транзисторов, коммутирующих сигнал 3, 4, которые находятся в закрытом состоянии, поступает на выходной порт 10. Сигнал, равный по величине паразитному сигналу и противоположный полярности через закрытую пару МОП транзисторов, компенсирующих сигнал 7, 8, также поступает на выходной порт 10. Паразитный и компенсирующий сигналы, поступающие на выходной порт 10, вычитаются и тем самым обеспечивается высокий уровень изоляции. На фиг. 3 представлены результаты расчета коэффициента передачи и изоляции в частотном диапазоне для схемы фиг. 1.

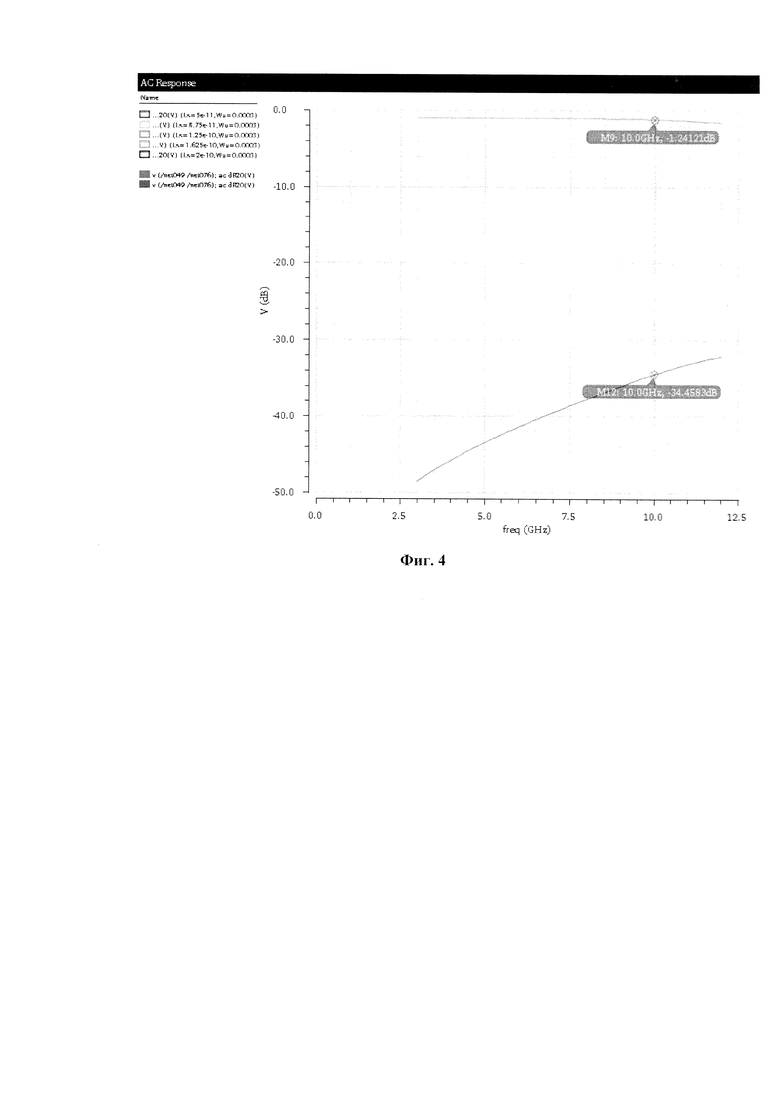

Схема, представленная на фиг. 2, работает таким образом, что сигнал от дифференциального генератора 1 поступает на пару МОП транзисторов, коммутирующих сигнал 2, 5, которые для определенности, будем полагать, находятся в открытом состоянии, и на пару МОП транзисторов, коммутирующих сигнал 3, 4, которые находятся в закрытом состоянии. Полезный сигнал через открытые МОП транзисторы 2, 5 будет поступать на выходной порт 11. Паразитный сигнал через МОП транзисторы 3, 4, которые находятся в закрытом состоянии, поступает на выходной порт 10. Сигнал, равный по величине паразитному сигналу и противоположный полярности через закрытые МОП транзисторы, компенсирующие сигнал 6, 7, также поступает на выходной порт 10. Паразитный и компенсирующий сигналы, поступающие на выходной порт 10, вычитаются и тем самым обеспечивается высокий уровень изоляции. Ширина затвора МОП транзисторов, компенсирующих сигнал 6, 7, выбирается таким образом, чтобы получить максимальное ослабление паразитного сигнала. На фиг. 4 представлены результаты расчета коэффициента передачи и изоляции в частотном диапазоне для схемы фиг. 2.

Источники информации

1. «А 2.4-GHz-Band 1.8-V Operation Single-Chip Si-CMOS T/R-MMIC Front-End with a Low Insertion Loss Switch», K. Yamamoto, T. Heima, A. Furukawa, M. Ono, et al., IEEE Journal Of Solid-State Circuits, Vol. 36, No. 8, August 2001, pp. 1186-1196.

2. «A 0.5-mk CMOS T/R Switch for 900-MHz Wireless Applications», F-J Huang, and Kenneth O, IEEE Journal Of Solid-State Circuits, Vol. 36, No. 3, March 2001, pp. 486-492.

3 «21.5-dBm Power-Handling 5-GHz Transmit/Receive CMOS Switch Realized by Voltage Division Effect of Stacked Transistor Configuration With Depletion-Layer-Extended Transistors (DETs)», T. Ohnakado, S. Yamakawa, T. Murakami, A. Furukawa, E. Taniguchi, Hiro-omi Ueda, N. Suematsu, and T. Oomori, IEEE Journal Of Solid-Sate Circuits, Vol. 39, no. 4, April 2004, pp. 577-584.

4. «A High-Power CMOS Switch Using A Novel Adaptive Voltage Swing Distribution Method in Multistack FETs» Minsik Ahn, Chang-Ho Lee, Byung Sung Kim and Joy Laskar, IEEE Transactions On Microwave Theory And Techniques, Vol. 56, No. 4, April 2008 pp. 849-857.

| название | год | авторы | номер документа |

|---|---|---|---|

| ИНТЕГРАЛЬНЫЙ ПЕРЕКЛЮЧАТЕЛЬ | 2024 |

|

RU2835384C1 |

| Интегральный аттенюатор | 2016 |

|

RU2642538C1 |

| Интегральный аттенюатор с дискретным управлением | 2022 |

|

RU2792262C1 |

| Усилитель заряда | 1983 |

|

SU1148003A1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ КМОП КОМПАРАТОР НАПРЯЖЕНИЯ | 1992 |

|

RU2019913C1 |

| Интегрирующий электрометр | 1982 |

|

SU1104426A1 |

| ИСТОЧНИК ЭЛЕКТРИЧЕСКОГО СИГНАЛА, ПРОПОРЦИОНАЛЬНОГО АБСОЛЮТНОЙ ТЕМПЕРАТУРЕ | 1993 |

|

RU2115099C1 |

| Устройство для управления двигателем переменного тока | 1983 |

|

SU1104635A1 |

| ИНДИКАТОР ЭЛЕКТРОМАГНИТНОГО ИЗЛУЧЕНИЯ | 1992 |

|

RU2060508C1 |

| ПОЛУПРОВОДНИКОВАЯ ИНТЕГРАЛЬНАЯ СХЕМА | 1991 |

|

RU2104601C1 |

Изобретение относится к электронной технике. Технический результат - уменьшение и подавление на выходе паразитного сигнала, значительное увеличение уровня изоляции переключателя в выключенном состоянии при сохранении малых потерь во включенном состоянии за счет вариантов подключения коммутирующих и компенсирующих МОП транзисторов. Переключатель с высокой изоляцией по первому варианту содержит генератор дифференциального сигнала, выходные порты, две пары МОП транзисторов, коммутирующих сигнал (2-5), и одну пару МОП транзисторов, компенсирующих сигнал 7, 6, причем все МОП транзисторы выполнены с одинаковой шириной канала. Переключатель с высокой изоляцией по второму варианту содержит генератор дифференциального сигнала, выходные порты, две пары МОП транзисторов, коммутирующих сигнал (2-5), при этом они выполнены с одинаковой шириной канала, два МОП транзистора, компенсирующих сигнал (6, 7), причем МОП транзисторы, коммутирующие и компенсирующие сигналы, выполнены с различной между собой шириной канала. 2 н.п. ф-лы, 4 ил.

1. Переключатель с высокой изоляцией, включающий генератор дифференциального сигнала, МОП транзисторы, выходные порты, отличающийся тем, что две пары МОП транзисторов, коммутирующих сигнал (2-5), соединены напрямую с генератором, при этом пара МОП транзисторов 2, 5 соединена напрямую с выходным портом 11, а пара МОП транзисторов 3, 4 соединена напрямую с выходным портом 10; одна пара МОП транзисторов, компенсирующих сигнал 7, 6, соединена от неинвертирующего вывода генератора к инвертирующим выводам первого 10 и второго 11 выходных портов соответственно, а другая пара МОП транзисторов, компенсирующих сигнал 8, 9, от инвертирующего вывода генератора к неинвертирующим выводам первого 10 и второго 11 выходных портов соответственно, причем все МОП транзисторы выполнены с одинаковой шириной канала.

2. Переключатель с высокой изоляцией, включающий генератор дифференциального сигнала, МОП транзисторы, выходные порты, отличающийся тем, что две пары МОП транзисторов, коммутирующих сигнал (2-5), соединены напрямую с генератором, при этом пара МОП транзисторов 2, 5 соединена напрямую с выходным портом 11, а пара МОП транзисторов 3, 4 соединена напрямую с выходным портом 10, при этом они выполнены с одинаковой шириной канала, первый МОП транзистор компенсирующий сигнал 6, соединен перекрестно от неинвертирующего вывода выходного порта 11 к инвертирующему выводу выходного порта 10, второй МОП транзистор, компенсирующий сигнал 7, соединен от инвертирующего вывода выходного порта 11 к неинвертирующему выводу выходного порта 10, кроме того, МОП транзисторы, коммутирующие и компенсирующие сигналы, выполнены с различной между собой шириной канала.

| МОП-УСТРОЙСТВО ВКЛЮЧЕНИЯ ВЫСОКИХ НАПРЯЖЕНИЙ НА ПОЛУПРОВОДНИКОВОЙ ИНТЕГРАЛЬНОЙ СХЕМЕ | 1995 |

|

RU2137294C1 |

| ЭЛЕКТРОННЫЙ КЛЮЧ С ТРАНСФОРМАТОРНОЙ РАЗВЯЗКОЙ | 2004 |

|

RU2257007C1 |

| Способ приготовления лака | 1924 |

|

SU2011A1 |

| Способ защиты переносных электрических установок от опасностей, связанных с заземлением одной из фаз | 1924 |

|

SU2014A1 |

Авторы

Даты

2016-10-27—Публикация

2015-04-03—Подача