(54) УСТРОЙСТВО ПРИОРИТЕТА

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обслуживания запросов | 1988 |

|

SU1571588A1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ПРИОРИТЕТА | 1992 |

|

RU2108618C1 |

| Приоритетное устройство | 1989 |

|

SU1651286A1 |

| Устройство для прерывания программ | 1985 |

|

SU1256029A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1136162A1 |

| Управляемое устройство приоритета | 1984 |

|

SU1182519A1 |

| Устройство для обработки запросов | 1988 |

|

SU1580365A1 |

| Устройство для обработки запросов | 1984 |

|

SU1213478A1 |

| Устройство для сопряжения процессоров в мультипроцессорной системе | 1984 |

|

SU1188747A1 |

| Устройство для прерывания программ | 1982 |

|

SU1072045A1 |

Изобретение относится к вычислитель ной технике и может найти применение в системах, использующих изменяемую дисштлину обслуживания. Известно устройство приоритета, содержащее регистр прерываний, элементы И, элемент ИЛИ, дешифратор, счетчик, элемент НЕ 1 . Устройство вследствие ограниченных функциональных возможностей не обеспе чивает управления дисштяиной обслуживания путем изменения ранее приведенных приоритетов источников. Наиболее близким к предлагаемому является устройство приоритета, содержащее регистр прерываний, элементы И, элемент ИЛИ, дешифратор, счетчик, дешифратор адреса и регистры адреса 2 Известное устройство, вследствие ограниченных функциональных возможносте не обеспечивает управления дисшшлиной обслуживания из-за отсутствия дальнейшего поиска запросов на обслуживание ОТ источников во время обработки предествующего запроса. Цель изобретения - расширение функциональных Возможностей устройства за счет обеспечения дальнейшего поиска запросов со старшим приоритетом на обслуживание от источников во время обработки предшествующего запроса и исключения возможности выдачи адреса менее приоритетного источника при одновременном приходе нескольких запросов на обслуживание. Поставленная цель достигается тем, что в устро IcTBo приоритета, содержащее регистр прерываний, дешифратор адреса, регистры адреса по числу разрядов регистра прерываний, дешифратор, первый счетчик, первый элемент ИЛИ, первый элемент НЕ, группу элементов И, причем выходы регистра прерьюаний поразрядно соединены с первыми входами соответствующих элементов И группы, подключенных выходами к соответствутощим входам первого элемента ИЛИ информационные входы регистров адреса подключены к соответствующим адресным входам устройства, выходы регистров адреса соединены с соответствующими входами дешифратора адреса, каждый выход которого подключен к второму входу соответствующего элемента И группы, каждый выход дешифратора подключен к соответствующему управляющему входу регистра адреса, выход первого элемента ИЛИ подключен к входу nepv вого элемента НЕ, выход которого соединен с первым входом первого элемента И, выход которого соединен со счетным входом первого счетчика, : вход сброса которого соединен с входом сфоса устройс тва, информационные входы устройства соединены с группой входов регистра прерываний, введены сдвигающий регистр, два триггера, второй элемент НЕ, второй счетчик, схема сравнения, второй и третий элементы ИЛИ, шесть элементов И, причем вход сдвигающего регистра соединен с выходом первого элемента ИЛИ, а.выходы подключены соответственно к входам второго элемента ИЛИ, единичный вход первого триггера соединен с выходом первого . элемента ИЛИ, а выход подключен соответственно через второй элемент НЕ к второму входу первого элемента И и непосредственно к первому входу второго элемента И, тактовый вход устройства соединен с третьим входом первого и вторым входом второго элементов И, выход второго элемента И подключен к счетному входу второго счетчика и к первому входу третьего элемента И, выход которого соединен с первым входом дешифратора, второй вход которого соединен с выходом четвертого элемента И, первый вход которого соединен со счетным входом первого счетчика, выход которого соединен с Ьторым входом четвертого элемента И и с первым входом схемы сравнения, второй вход которой соединен с выходом второго счетчика, с первым входом пятого элемента И и с вторым входом третьего элемента И, выход схемы сравнения соединен с входом сброса второго счетчика и с единичньп входом второго триггера, вход сброса которого соединен с входом сброса устройства, с входом сфоса первого триггера и с вторым входом пятого элемента И, выходы регистров адресов соединены с входами третьего элемента ИЛ выход которого соединен с первым вэсо-

дом шестого элемента И, второй вход и выход которого соединены соответственно с выходом второго триггера и с информа1шонным выходом устройства, выход второго элемента ИЛИ соединен с третьим входом пятого элемента И, выход которого соединен с информационным входом второго счетчика.

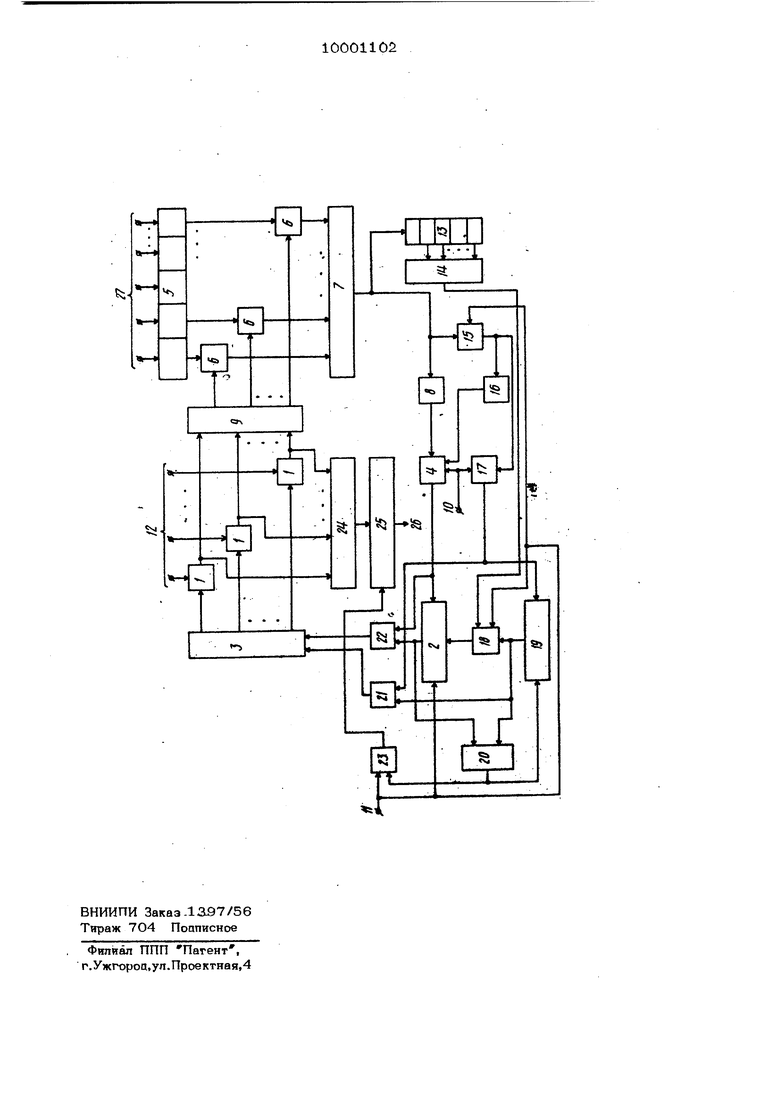

На чертеже приведена структурная схема устройства.

Устройство содержит регистры 1 адреса, счетчик 2, дешифратор 3, элемент И 4, регистр 5 прерываний, группу элементов И 6, элемент ИЛИ 7, элемент НЕ 8, дешифратор 9 адреса, тактовый вход 10 устройства, вход сброса 11 устройства, адресные входы 12 устройсва, сдвигающий регистр 13, элемент ИЛИ 14, триггер 15, элемент НЕ 16, элементы И 17 и 18, счетчик 19, схему 2О сравнения, элементы И 21 и 22, триггер 23, элемент ИЛИ 24, элемент И 25, информационный выход 26 устройства, информационные нходы 27 устройства.

Устройство работает следующим образом.

Запросы на обслуживание от источников фиксируются регистром 5 прерываний по индивидуальным для каждого источника входам 27. Во время обслуживания очередного запроса имеется возможность поступления запроса на обслуживание с более высоким приоритетом. Если на обслуживании запросы от источников отсутствуют, счетчик 2 через элемент И 4 получает с тактового входа 1О импульсы переключения и через элемент И 22, стробируемый тактовыми импульсами с выхода первого элемента И 4, дешифратор 3 осуществляет опрос регистров 1 адреса. В регистрах 1 записаны адреса источников в порядке присвоенных им приоритетов При получении регистром 1 строба опроса от дешифратора 3 код адреса источника, записанный в нем,подается на вход дешифратора 9, который щ.щает сигнал на соответствующий источнику элемент из групп элементов И 6.

При наличии запроса на обслуживание от одного из источников единичный сигнал соответствуквдего разряда регистра 5 проходит через открытый элемент из группы элементов И 6, через элементы ИЛИ 7, НЕ 8 и И 4, останавливаясчетчик 2. Сигналом элемента ИЛИ 7 в младший разряд сдвигакхиего регистрpa 13 записывается единика, устанавливается в единичное состояние триггер 1 5, сигнал с выхода которого открывае элемент ИЛИ 7 для прохождения тактовых импульсов на вход счетчика 19 и через элемент НЕ 16 запирает элемент И 4, Счетчик 19 через элемент И 17 получает с. тактового входа Ю импульсы переключения и через элемент И 21 стробируемый тактовыми импульсами с выхода второго элемента И 17, и, дешифратор 3 осуществляет опрос регис ров 1 по описанному выше циклу работы устройства. Одновременно сигнал с выхода рторого счетчика 19 поступает на вход схемы 20 сравнения, на второй вход которой подается сигнал с выхода остановленного счетчика 2. При совпадении кодов импульс с выхода схемы2О сравнения обнуляет счетчик 19 и устанавливает в единичное состояние триггер 23. Единичный сигнал с выхода триггера открывает элемент И 25 и с выхода 26 устройства снимается адрес выбранного источника. Таким офазом, наличие сигнала с выхода схемы 2О ср нения свидетельствует об отсутствии запроса с более высоким приоритетом чем запрос,поставленный на обслуживание. При обнаружении заявки со старшим приоритетом на выходе первого элемента ИЛИ 7 возникает единичный сигнал, сдвигающий единицу в младшем разря- . де сдвигакщего регистра 13 в следующий разряд и поступает через элемент ИЛИ 14 на второй вход элемента И 18 Сигнал с выхода элемента ИЛИ 7 посту пает непосредственно на третийксод элемента И 18 на нулевой вход триг гера 23. Нулевой сигнал блокирует выдачу адреса с меньшим приоритетом на адресный выход 26 устройства. Одновременно содержимое счетчика 19 через открытый элемент И 18 переписывается на первый счетчик 2 и счетчик 19 обнуляется. Далее происходит аналогичный процесс поиска заявки с приоритетом более высоким, чем последний. При отсутствии такового, т,, е. при получении единичного сигнала с выхода схемы 20 сравнения, устанавливае ся в единичное состояние триггер 23 и адрес последней об1аруженной заявки снимается с выхода 26 устройства. По завершении обслуживания последней заявки со старшим приоритетом поступивший по входу 11 сигнал сбрасывает счетчик 2, счетчик 19, сдвигающий регистр 13, устанавливает в исходное состояние триггер 15 и триггер 23. Триггер соответствукяпего разряда ре- гистра 5, запрос которого обслужился, устанавливается в нулевое состояние. Далее начинается очередной цикл работы устройства приоритета. При необходимости изменения порядка опроса истошиков по входам 12 в регистр 1 записываются соответствующие адреса источников. Применение предлагемого изофетения позволяет расширить функциональные возможности устройства. Формула изобретения Устройство приоритета, содержащее регистр прерьтаний, дешифратор адреса, регистры адреса по числу разрядов регистра прерываний, дешифратор , первый счетчик, первый элемент ИЛИ, первый элемент НЕ, группу элементов И, при- ,, .чем выходы регистра прерываний поразрядно соединены с первыми .входами соответствующих элементов И группы, подключенных выходами к соответствующим входам первого элемента ИЛИ, информа ционные входы регистров адреса подклк}чены к соответствукшим адресным входам устройства, выходы регистров адреса соединены с соответствующими входами дешифратора адреса, каждый выход .которого подключен к второму входу соответствующего элемента И группы, каждый выход дешифратора подключен к соответствующему управляюшему входу регистра адреса, выход первого элемента ИЛИ подключен к входу первого элемента НЕ, выход которого соединен с первым входом первого элемента И, выход которого соединен со счетным входом первого счетчика, вход сброса которого соединен с входом сброса устройства информационные входы устройства соединены с группой входов регистра прерываний, отличаюш еся тем, что, с целью расширения функциональных возможностей устройства за счет обеспечения дальнейшего поиска запросов со старшим приоритетом на обслуивание от источников во время об|заботки прюдществующего запроса н исключения возможности выдачи адреса менее приоритетного источника при одновременном приходе нескольких запросов на обслуживание, в него введены сдвигающий

регистр, два триггера, второй элемент НЕ, второй счетчик, схема сравнения, второй и Третий Элементы ИЛИ, шесть элекюнтов И, причем вход сдвигающего регистра соея11нен с выходом первого

элемента ИЛИ, а выходы подключены соответственно к входам второго элемента ИЛИ, единичный вход первого триггера соединен с выходом первого элемента ИЛИ, а выход подключен соответственно через второй элемент НЕ к второму входу первого элемента И и непосредственно к первому входу втотрого элемента И, тактовый вход устройства соединен с третьим входом первого и вторым входом второго элементов И, выход второго элемента И подключен к счетному входу второго счетчика и к первому входу третьего элемента И, выход которого соединен с первым входом дешифратора, второй .которого сое-. динен с выходом четвертого элемента И первый вход которого соединен со счетным входом первого счетчика, выход которого соединен с вторым входом четвертого элемента И и с первым Входом схемы сравнения, второй вход которой соединен с выходом второго счетчика, с первым входом пятого элемента И и с вторым входом третьего элемента И, выход схемы сравнения соединен с входом сброса второго счетчика и с единичным входом второго триггера, вход сброса которого соединен с входом сброса устройства, с входом сброса первого триггера и с вторым входом пятого элемента И, выходы регистров адресов соединены с входами третьего элемента.ИЛИ, выход которого соединен с первым входом шестого элемента И, второй вход и выход которого соединены соответственно с выходом второго триггера и с информационным выходом устроства, выход второго элемента ИЛИ сое. динен с третьим входом пятого элемента И, выход которого соединен с информационным входом второго счетчика.

Источники информации, принятые во внимание при экспертизе

-

ч

3:

ty.

IT

9&

ss

u

Авторы

Даты

1983-02-28—Публикация

1981-10-12—Подача