Изобретение относится к .вычислительной технике и может быть использовано в цифровых вычислительных устройствах с несколькими активными, независимыми абонентами.

Цель изобретения - расширение функциональных возможностей устройства за счет обеспечения режима обслуживания независимых абонентов,

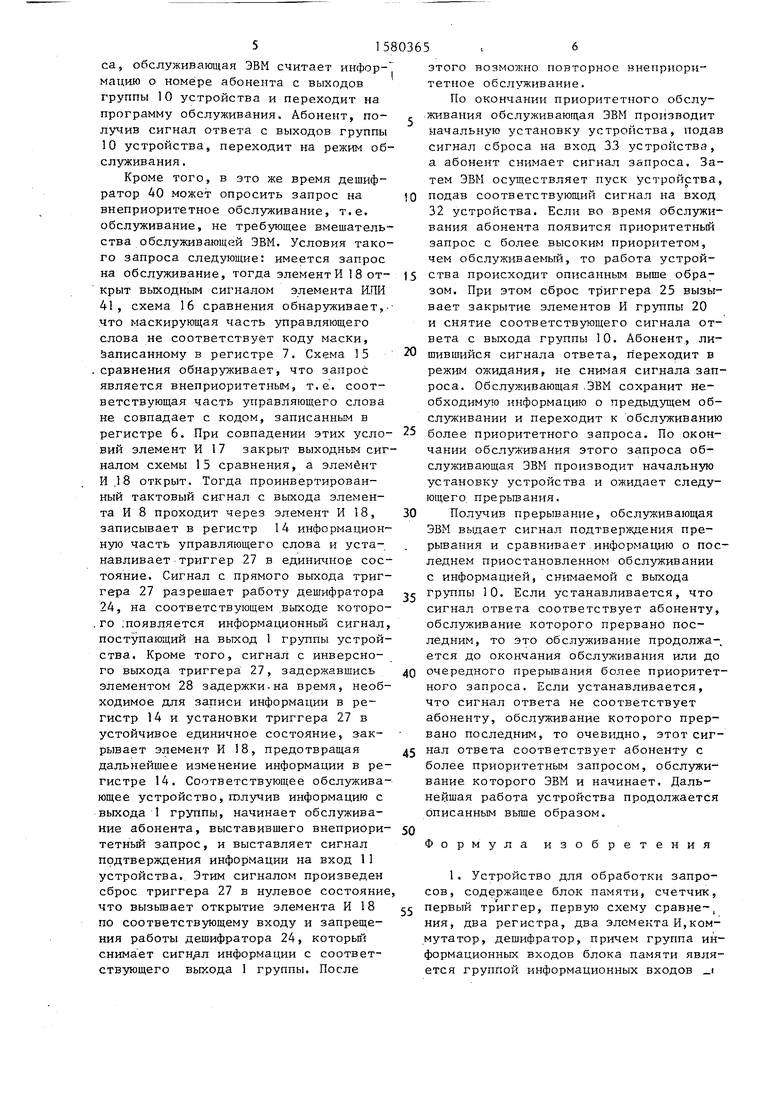

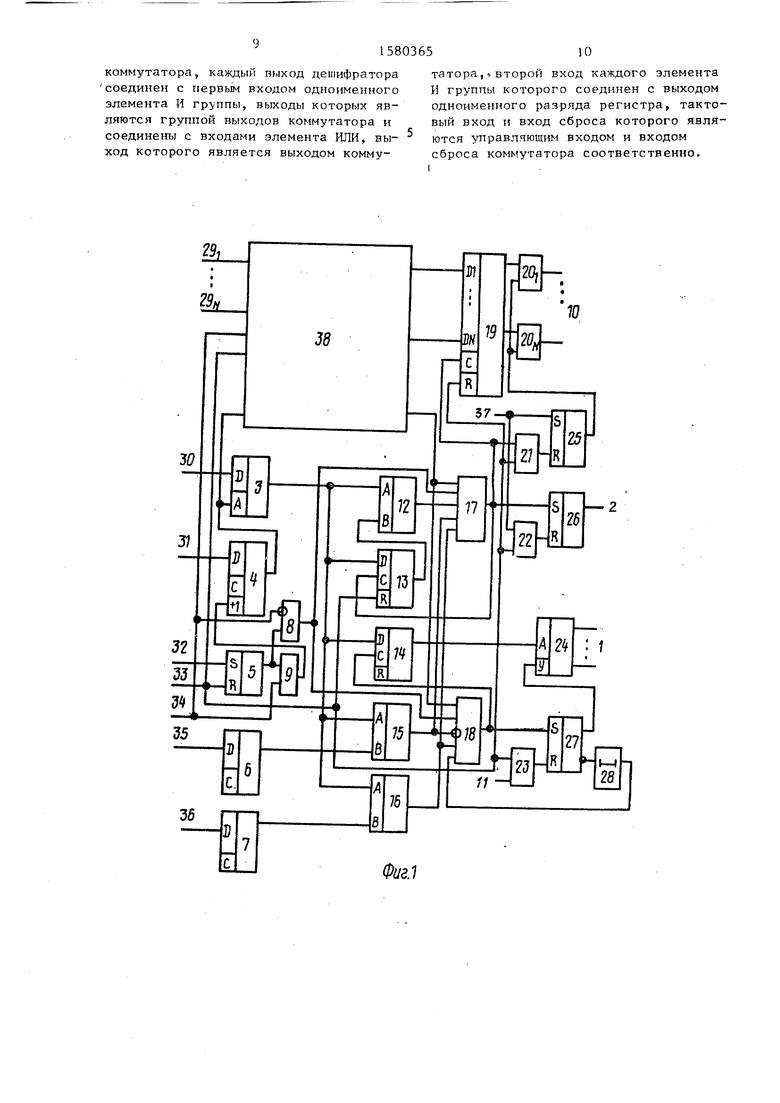

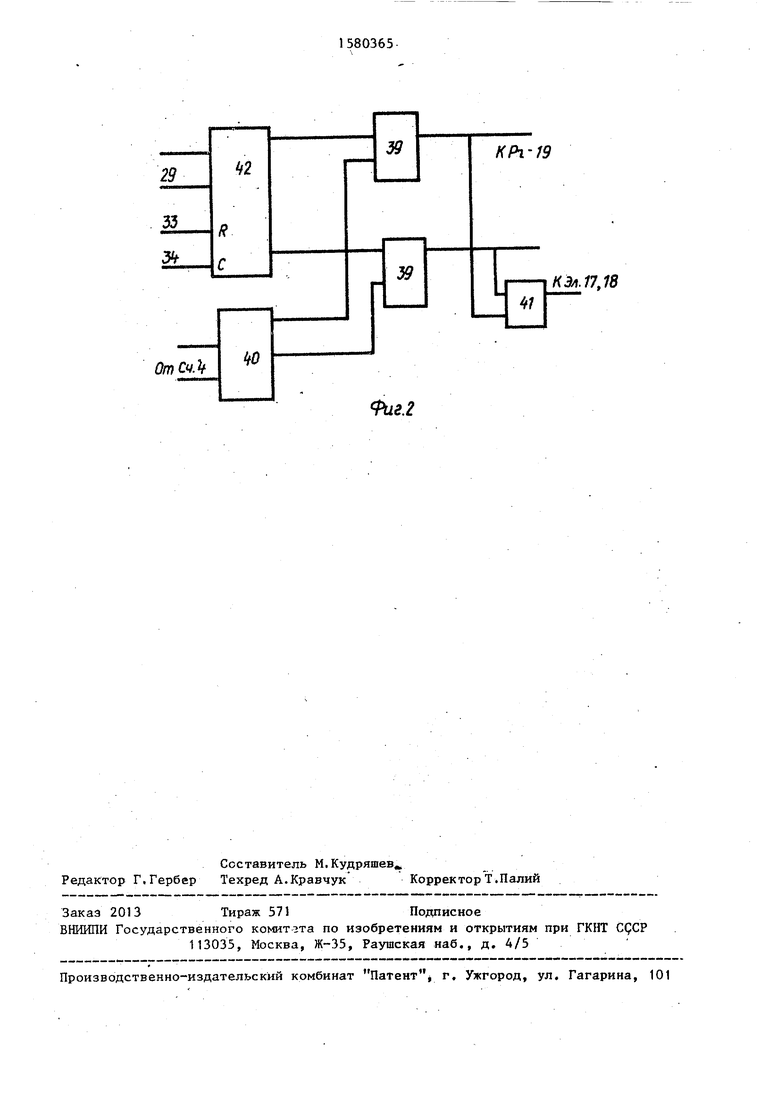

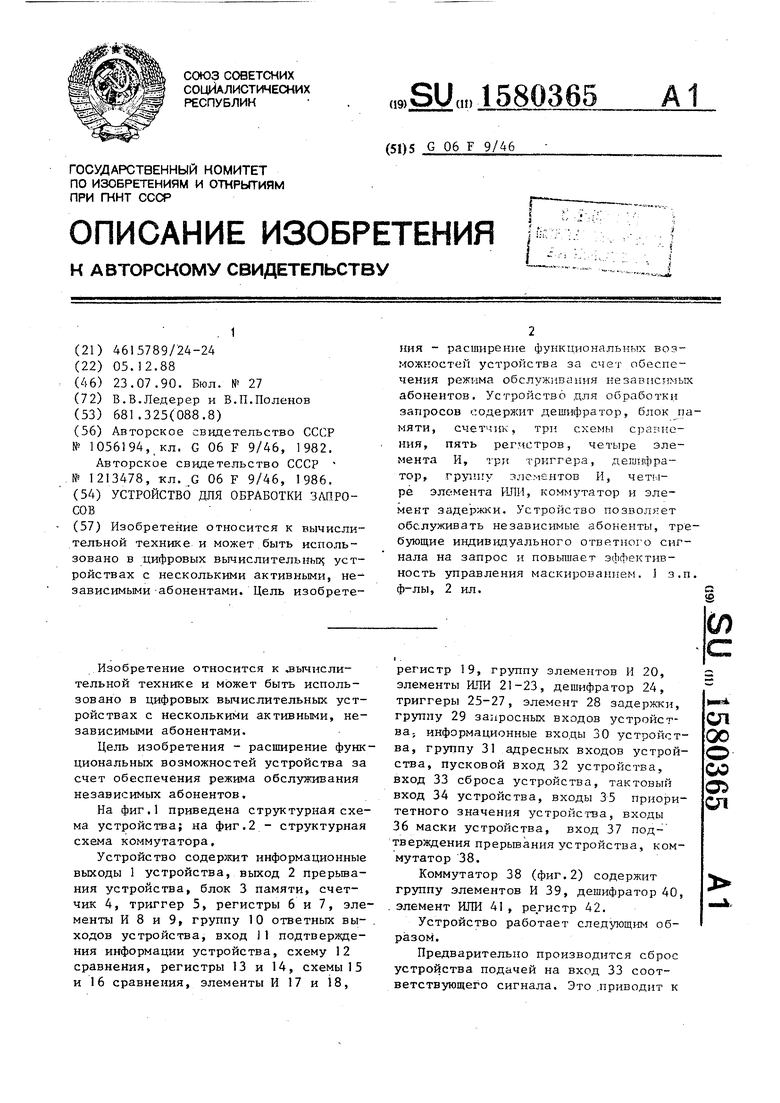

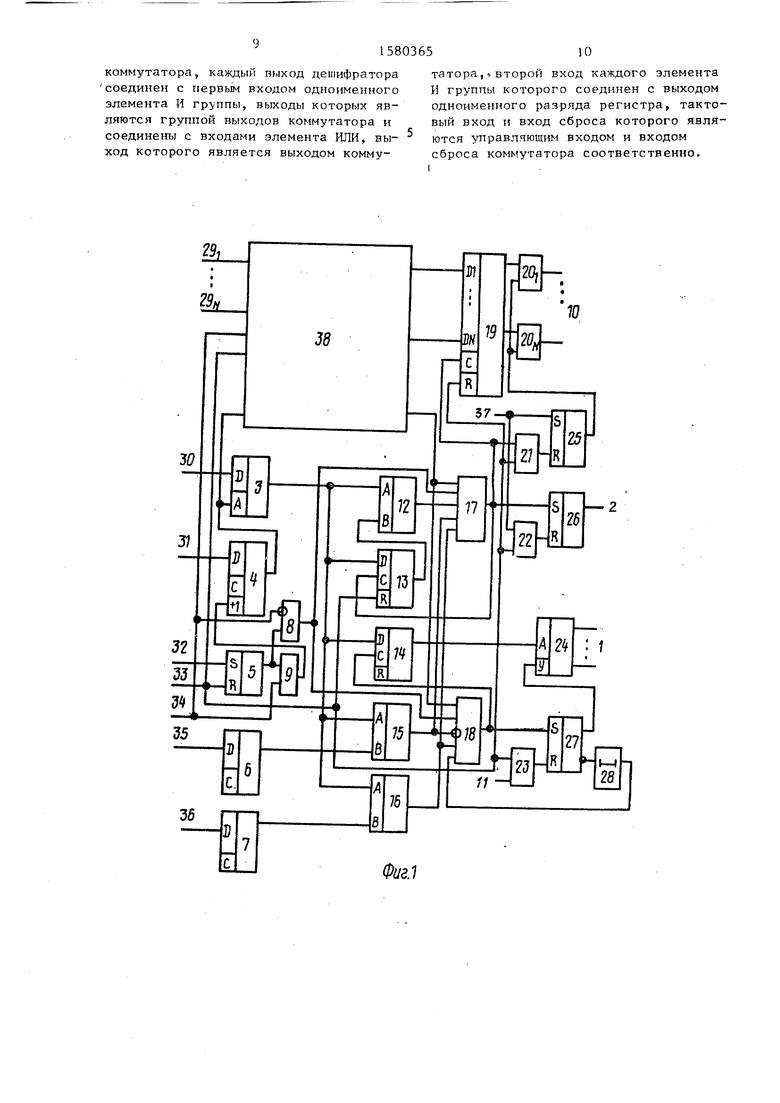

На фиг.1 приведена структурная схема устройства; на фиг.2 - структурная схема коммутатора.

Устройство содержит информационные выходы 1 устройства, выход 2 прерывания устройства, блок 3 памяти, счетчик 4, триггер 5, регистры 6 и 7, элементы И 8 и 9, группу 10 ответных выходов устройства, вход 11 подтверждения информации устройства, схему 12 сравнения, регистры 13 и 14, схемы 15 и 16 сравнения, элементы И 17 и 18,

регистр 19, группу элементов И 20, элементы ИЛИ 21-23, дешифратор 24, триггеры 25-27, элемент 28 задержки, группу 29 запросных входов устройс - ва; информационные входы 30 устройства, группу 31 адресных входов устройства, пусковой вход 32 устройства, вход 33 сброса устройства, тактовый вход 34 устройства, входы 35 приоритетного значения устройства, входы 36 маски устройства, вход 37 подтверждения прерывания устройства, коммутатор 38.

Коммутатор 38 (фиг.2) содержит группу элементов И 39, дешифратор 40, элемент ИЛИ 41, регистр 42.

Устройство работает следующим образом.

Предварительно производится сброс устройства подачей на вход 33 соответствующего сигнала. Это приводит к

СП

оо

со

О

ел

тому, что в нулевое состояние переходят регистры 42, 13 и 19 и триггеры 5,25-27. Сброшенный триггер 5 своим выходным сигналом закрывает элементы И 8 и 9, предотвращая прохождение через них тактовых сигналов. В этом случае опроса абонентов не происходит. Однако сигналы запросов, поступающие на группу 29 запросных входов, записываются в регистр 42 тактовыми сигналами, поступающими на тактовый вход 34. Сброшенный триггер 25 закрывает своим выходным сигналом элементы И группы 20, предотвращая прохождение ответных сигналов на группу 10 ответных выходов устройства. Сброшенный триггер 26 не выдает сигнала прерывания на выход 2 прерывания устройства. Сброшенный триггер 27 предотвращает поступление информации с выходов дешифратора 24 на группу выходов 1 устройства. Кроме того, триггер 27 сигналом со своего инверсного выхода открывает по соответствующему входу элемент И 18. После сброса устройства производится запись соответствующей информации в блок 3 памяти. В этом случае адрес ячейки блока 3 памяти задается через счетчик 4, запись в него соответствующего кода - через группу 31 адресных входов устройства, информация о приоритетах, маскирующие коды и пр. подается в виде одного слова данных на информационные входы 30 устройства. Затем производится запись соответствующей информации в регистры 6 и 7 через входы 35 и 36.

После указанных процедур производится пуск устройства подачей соответствующего сигнала на пусковой вход 32 устройства. В этом случае триггер 5 устанавливается в единичное состояние, открьюая своим выходным сигналом элементы И 8 и 9, и тактовые сигналы через тактовый вход 34 устройства начинают поступать на входы элементов И 8 и 9 и регистр 42 коммутатора 38.

Тактовые сигналы, проходя через открытый элемент И 9, поступают на счетный вход счетчика 4, переводя его в очередное состояние. Таким образом, счетчик производит последовательный опрос ячеек блока 3 памяти, информация с выхода которого поступает на входы схем 12, 15 и 16 сравнения и регистров 13 и 14. Кроме того, код с выхода счетчика 4 поступает на вход

5

0

5

0

5

5

0

5

дешифратора 40, который производит последовательный опрос выходов регистра 42 запросов, открывая соответствующие элементы И 39.

При наличии запросов соответствующие -сигналы с выходов регистра 42 поступают через соответствующие элементы И 39 и через элемент ИЛИ 41 на входы элементов И 17 и 18, открывая последний по-соответствующим входам. Элемент И 17 также открыт по другим входам, если выполняются следующие условия: схема 16 сравнения обнаруживает, что маскирующая часть управляющего слова не соответствует коду маски, записанному в регистре 7, схема 12 сравнения обнаруживает, что приоритет опрашиваемого абонента, находящегося в соответствующей части управляющего слова, выше приоритета, записанного в регистре 13, схема 15 сравнения обнаруживает, что запрос является приоритетным. Т.е. соответствующая часть управляющего слова совпадает с кодом, записанным в регистр 6. При совпадении этих условий тактовый сигнал, про- инвертировавшись и пройдя через элемент И 8, проходит, а затем через элемент И 17 записывает сигнал запроса в регистр 19, сбрасывает триггер 25 или подтверждает его нулевое состояние, записывает в регистр 13 приоритет нового запроса и устанавливает триггер 26 в единичное состояние, выходной сигнал которого формирует на выходе 2 сигнал прерывания.

Счетчик 4 продолжает перебор запросов абонентов, не дожидаясь реакции обслуживающей ЭВМ. Если до прихода от обслуживающей ЭВМ сигнала подтверждения прерывания на вход 37 обнаружен еще один незамаскированный запрос на прерывание с более высоким приоритетом, то в регистр 13 записан этот приоритет. Запросы с меньшим приоритетом игнорируют.

После того, как обслуживающее устройство выставляет на вход 37 сигнал подтверждения прерывания, триггер 26 сброшен и сигнал прерывания с выхода 2 снят. Кроме того, сигналом подтверждения прерывания установлен в единичное состояние триггер 25, выходной сигнал которого открывает элементы И группы 20. Это приводит к формированию сигнала ответа на соответствующем выходе группы 10 устройства из запи- ганного в регистре 19 сигнала запроса, обслуживающая ЭВМ считает инфор- мацию о номере абонента с выходов группы 10 устройства и переходит на программу обслуживания. Абонент, получив сигнал ответа с выходов группы 10 устройства, переходит на режим обслуживания.

Кроме того, в это же время дешифратор АО может опросить запрос на внеприоритетное обслуживание, т.е. обслуживание, не требующее вмешательства обслуживающей ЭВМ. Условия такого запроса следующие: имеется запрос на обслуживание, тогда элемент И 1 8 от- крыт выходным сигналом элемента ИЛИ 41, схема 16 сравнения обнаруживает,- что маскирующая часть управляющего слова не соответствует коду маски, записанному в регистре 7. Схема 15 сравнения обнаруживает, что запрос является внеприоритетным, т.е. соответствующая часть управляющего слова не совпадает с кодом, записанным в регистре 6. При совпадении этих уело- вий элемент И 17 закрыт выходным сигналом схемы 15 сравнения, а элемент И .18 открыт. Тогда проинвертирован- ный тактовый сигнал с выхода элемента И 8 проходит через элемент И 18, записывает в регистр 14 информационную часть управляющего слова и устанавливает триггер 27 в единичное состояние. Сигнал с прямого выхода триггера 27 разрешает работу дешифратора 24, на соответствующем выходе которо- . го .появляется информационный сигнал, поступающий на выход 1 группы устройства. Кроме того, сигнал с инверсного выхода триггера 27, задержавшись элементом 28 задержки-на время, необходимое для записи информации в регистр 14 и установки триггера 27 в устойчивое единичное состояние, закрывает элемент И 18, предотвращая дальнейшее изменение информации в регистре 14. Соответствующее обслуживающее устройство,голучив информацию с выхода 1 группы, начинает обслуживание абонента, выставившего внеприори- тетный запрос, и выставляет сигнал подтверждения информации на вход 1 1 устройства. Этим сигналом произведен сброс триггера 27 в нулевое состояние что вызывает открытие элемента И 18 по соответствующему входу и запрещения работы дешифратора 24, который снимает сигндл информации с соответствующего выхода 1 группы. После

этого возможно повторное внеприорн- тетное обслуживание.

По окончании приоритетного обслуживания обслуживающая ЭВМ производит начальную установку устройства, подав сигнал сброса на вход 33 устройства, а абонент снимает сигнал запроса. Затем ЭВМ осуществляет пуск устройства, подав соответствующий сигнал на вход 32 устройства. Если во время обслуживания абонента появится приоритетный запрос с более высоким приоритетом, чем обслуживаемый, то работа устройства происходит описанным выше образом. При этом сброс триггера 25 вызывает закрытие элементов И группы 20 и снятие соответствующего сигнала ответа с выхода группы 10. Абонент, лишившийся сигнала ответа, переходит в режим ожидания, не снимая сигнала запроса. Обслуживающая ЭВМ сохранит необходимую информацию о предыдущем обслуживании и переходит к обслуживанию более приоритетного запроса. По окончании обслуживания этого запроса обслуживающая ЭВМ производит начальную установку устройства и ожидает следующего прерывания.

Получив прерывание, обслуживающая ЭВМ выдает сигнал подтверждения прерывания и сравнивает информацию о последнем приостановленном обслуживании с информацией, снимаемой с выхода группы 10. Если устанавливается, что сигнал ответа соответствует абоненту, обслуживание которого прервано последним, то это обслуживание продолжа-, ется до окончания обслуживания или до очередного прерывания более приоритетного запроса. Если устанавливается, что сигнал ответа не соответствует абоненту, обслуживание которого прервано последним, то очевидно, этот сигнал ответа соответствует абоненту с более приоритетным запросом, обслуживание которого ЭВМ и начинает. Дальнейшая работа устройства продолжается описанным выше образом.

Формула изобретения

1. Устройство для обработки запросов, содержащее блок памяти, счетчик, первый триггер, первую схему сравне-, ния, два регистра, два элемента И,коммутатор, дешифратор, причем группа информационных входов блока памяти является группой информационных входов (

устройства, группа информационных входов.счетчика является группой адресных входов устройства, выходы счетчика соединены с группой адресных входов коммутатора и блока памяти, выходы которого соединены первой группой входов первой схемы сравнения и с информационными входами первого и второго регистров, выходы первого регистра соединены с вторыми входами первой схемы сравнения, выход которой соединен с первым входом первого элемента И, второй вход которого соединен с выходом коммутатора и с первым прямым входом второго элемента И, второй прямой вход которого соединен с третьим входом первого элемента И, четвертый вход которого соединен с инверсным входом второго элемента И, вход запи- си первого регистра соединен с входом установки в 1 первого триггера, выход которого является выходом прерывания устройства, выходы второго регистра соединены с входами дешифрато- ра, группа выходов которого является группой информационных выходов устройства, группа информационных входов коммутатора является запросными входами устройства, отличающе- е с я тем, что, с целью расширения функциональных возможностей устройства за счет обеспечения режима обслуживания независимых абонентов, в него введены третий, четвертый и пятый регистры, второй и третий триггеры, третий и четвертый элементы И, группа элементов И, четыре элемента ИЛИ, вторая и третья схемы сравнения, элемент задержки, причем группа выходов ком- мутатора соединена с группой информационных входов третьего регистра, каждый выход группы выходов которого соединен с первым входом одноименного элемента И группы, выходы которых яв- ляются группой ответных выходов устройства, вход установки в I11 второго триггера является входом запуска устройства, выход второго триггера соединен с прямым входом третьего элемента И и с первым входом четвертого элемента И, выход которого соединен со счетным входом счетчика, тактовый вход устройства соединен с управляющим входом коммутатора, с пря- мым входом третьего элемента И и с вторым входом четвертого элемента И, выход третьего элемента И соединен с пятым входом первого элемента И и с

третьим прямым входом второго элемента И, выход которого соединен с входом записи второго регистра и с входом установки в 1 третьего триггера, прямой выход которого соединен с входом управления дешифратора, выход первого элемента И соединен с входом записи третьего регистра, с первым входом первого элемента ИЛИ и с входом установки в 1 первого триггера, вход сброса устройства соединен с входами сброса коммутатора, второго триггера, первого и третьего регистров, с вторым входом первого и с первыми входами второго и третьего элементов ИЛИ, выход третьего элемента ИЛИ соединен с входом сброса третьего триггера, инверсный выход которого через элемент задержки соединен с четвертым прямым входом второго элемента И, второй вход третьего элемента ИЛИ является входом подтверждения информации устройства, вход подтверждения прерывания устройства соединен с входом установки в 1 четвертого триггера и с вторым входом второго элемента ИЛИ, выход которого соединен с входом сброса первого триггера, выход второго элемента ИЛИ соединен с входом сброса первого триггера, выход четвертого триггера соединен с вторыми входами элементов И группы, информационные входы четвертого регистра являются группой входов приоритетного значения устройства, выходы блока памяти соединены с первыми входами второй и третьей схем сравнения, выходы четвертого регистра соединены с вторыми входами второй схемы сравнения, выход которой соединен с инверсным входом второго элемента И, выходы пятого регистра соединены с вторыми входами третьей схемы сравнения, выход которой соединен с вторым прямым входом второго элемента И, информационные входы пятого регистра являются группой входов маски устройства, вхо1- ды записи счетчика и четвертого и пятого регистров включены в группу адресных входов устройства.

2, Устройство по п.1, отличающееся тем, что коммутатор содержит регистр, дешифратор, группу элементов И, элемент ИЛИ, причем группа информационных входов регистра является группой информационных входов коммутатора, группа входов дешифратора является группой адресных входов

коммутатора, каждый выход дешифратора соединен с первым входом одноименного элемента И группы, выходы которых являются группой выходов коммутатора и соединены с входами элемента ИЛИ, выход которого является выходом коммутатора, .второй вход каждого элемента И группы которого соединен с выходом одноименного разряда регистра, тактовый вход и вход сброса которого являются управляющим входом и входом сброса коммутатора соответственно.

| название | год | авторы | номер документа |

|---|---|---|---|

| Приоритетное устройство | 1989 |

|

SU1651286A1 |

| Устройство для обработки запросов | 1984 |

|

SU1213478A1 |

| Устройство для сопряжения двух ЭВМ с абонентами | 1988 |

|

SU1529237A1 |

| Приоритетное устройство | 1985 |

|

SU1411744A1 |

| Приоритетное устройство | 1982 |

|

SU1056194A1 |

| Устройство многоуровневого прерывания | 1985 |

|

SU1287158A1 |

| Устройство для сопряжения ЭВМ с синхронными каналами передачи данных | 1986 |

|

SU1347083A1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ДЛЯ ОБСЛУЖИВАНИЯ ЗАПРОСОВ | 2000 |

|

RU2157561C1 |

| Устройство для сопряжения ЭВМ с абонентом | 1990 |

|

SU1702380A1 |

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1989 |

|

SU1734098A1 |

Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных устройствах с неколькими активными, независимыми абонентами. Цель изобретения - расширение функциональных возможностей за счет обеспечения режима обслуживания независимых абонентов. Устройство для обработки запросов содержит дешифратор, блок памяти, счетчик, три схемы сравнения, пять регистров, четыре элемента И, три триггера, дешифратор, группу элементов И, четыре элемента ИЛИ, коммутатор и элемент задержки. Устройство позволяет обслуживать независимые абоненты, требующие индивидуального ответного сигнала на запрос и повышает эффективность управления маскированием. 1 з.п.ф-лы, 2 ил.

21

25

-2

Фиг Л

К Эл. 17,18

Фиг2

| Приоритетное устройство | 1982 |

|

SU1056194A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для обработки запросов | 1984 |

|

SU1213478A1 |

| ,G 06 F 9/46, 1986. | |||

Авторы

Даты

1990-07-23—Публикация

1988-12-05—Подача