пы информационных входов шинного формирователя, выходы которого соединены с первой группой информационных входов мультиплексора адреса, выходы разрядов микроопераций блока памяти микропрограмм соединены с соответствующими входами группы информационных входов регистра микрокоманд, выход первого разряда второй группы выходов которого соединены с вторым входом блока синхронизации, третий .вход которого соединен с входом пуска устройства, выход второго разряда второй группы выходов регистра микрокоманд соединен с вторым входом первого элемента И, выход которого соединен с управляющим входом шинного формирователя и является управляюш,им выходом устройства, выходы третьего и четвертого разрядов второй группы выходов регистра микрокоманд соединены с вторыми входами второго и третьего элементов И соответственно, выход третьего элемента И соединен с нулевым входом триггера прерывания, третья группа выходов регистра микрокоманд соединена с группой управляющих входов мультиплексора адреса, четвертая группа выходов регистра микрокоманд соединена с группой управляющих входов мультиплексора логических условий, группа выходов которого соединена с соответствующими разрядами группы информационных входов шинного формирователя и с входами модифицируемых разрядов адреса третьей группы информационных входов мультиплексора адреса, выходы .разрядов номера объекта и выход управляющего разряда пятой группы выходов регист-ра микрокоманд соединены соответственно с группой информационных входов дешифратора и вторым входом четвертого элемента И, выход которого соединен с входами установки в нулевое состояние триггера запроса и регистра выбора и с управляющим входом дешифратора, выходы которого соединены с соответствующими нулевыми входами регистра запросов и с выходом сигнализации устройства, входы приоритетных логических условий группы входов логических условий устройства соединены с соответствующими входами группы входов блока приоритета условий, выходы которого соединены с соответствующими входами второй группы информационных входов мультиплексора логических условий.

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор | 1983 |

|

SU1213485A1 |

| Устройство для сопряжения эвм с абонентами | 1984 |

|

SU1215114A1 |

| Микропрограммное устройство для приоритетного обслуживания группы абонентов | 1984 |

|

SU1302277A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1134936A1 |

| Устройство для программного управления | 1988 |

|

SU1500994A1 |

| Микропрограммное устройство с контролем | 1984 |

|

SU1208556A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1156073A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1124299A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1065855A1 |

| Мультимикропрограммное устройство для контроля и управления | 1984 |

|

SU1249513A1 |

МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ С КОНТРОЛЕМ, содержащее блок памяти микропрограмм, регистр адреса микрокоманд, регистр микрокоманд, мультиплексор адреса, мультиплексор логических условий, дешифратор и первый элемент И, причем группа выходов мультиплексора адреса соединена с группой информационных входов регистра адреса микрокоманд, выходы которого соединены с входами блока памяти микропрограмм, выходы модифицируемых разрядов адреса группы выходов блока памяти микропрограмм соединены с первой группой информационных входов мультиплексора .логических условий группы, входы бесприоритетных логических условий устройства соединены с соответствующими входами второй группы информационных входов мультиплексора логических условий, выход первого элемента И соединен с управляющим входом мультиплексора адреса, первая группа информационных входов которого является группой адресных входов устройства, первая группа выходов регистра микрокоманд является первой группой управляющих выходов устройства, отличающееся тем. что, с целью повышения быстродействия контроля к расширения области применения, в него вве.хенй блок синхронизации, регистр за.просов, регистр выбора, шифратор, шинный формирователь, блок приоритета запросов, блок приоритета условий, триггер запроса, триггер прерывания, второй, третий и четвертый элементы И, и элемент HJiii, причем единичные входы регистра запросов соединены с соответствующими входами группы входов запросов устройства, выходы регистра запросов соединены с соответствующими входами блока приоритета запросов к зле.чента ИЛИ, вы.ход которого соединен с информационным входом триггера запроса, единичный выход триггера запроа са соединен с первым входом блока синх(С ронизации, первый выход которого соединен с первыми входами второго, третьего и четвертого элементов И и входо.м синхронир.ТЛЖ зации регистра микрокоманд, второй выход Ькгк блока синхронизации соединен с входом синхронизации регистра адреса микрокоманд, группа выходов блока приоритета запросов соединена с группой информационных вхоSlErA дов регистра выбора, вход запросов наивыс№ шего приоритета которого соединен с втоо рым входом второго элемента И, выход которого соединен с единичным входом тригIssei гера прерывания, единичный выход которо го соединен с первым входом первого элемента И и с управляющим входом мультиплексора логических условий, вход подтверждения прерывания устройства соединен с входами синхронизации триггера запроса и регистра выбора, выходы которого соединены с входами шифратора, выходы шифратора as. соединены с входак5и второй группы информационных входов мультиплексора адреса, В.ЫХОДЫ немодулируемых разрядов адреса блока памяти микропрограмм соединены с соответствующи.ми входами третьей группы информационных входов мультиплексора адреса и с соответствующими входами груп

1

Изобретение относится к автоматике и вычислительной технике и может быть использовано для управления контролем объектов распределенной вычислительной системы.

Известно устройство, применяемое для контроля ЭВМ, содержащее блоки памяти, регистры, дешифраторы 1.

Недостатком этого устройства является низкая оперативность контроля.

Известно устройство диагностики ЭВМ, содержащее счетчик, регистры, дешифратор, блок памяти 2.

Недостатками устройства являются узкие функциональные возможности и низкая оперативность контроля.

Наиболее близким к предлагаемому по технической сущности и достигаемому эффекту является устройство, содержащее блок памяти микропрограммы, регистр микрокомадн, регистр адреса, дешифратор адреса, дешифратор, мультиплексор логических условий, первый и второй мультиплексоры адреса, первый и второй мультиплексоры микроопераций, элемент И, причем первая группа выходов блока памяти микропрограмм соединена с группой управляющих входов мультиплексора логических условий.

группа информационных входов которого является группой входов логических условий устройства, выходы первого и второго разрядов первой группы выходов блока памяти микропрограмм соединены соответственно с прямым и инверсным входами элемента И, выход которого соединен с входом синхронизации регистра микрокоманд и управляющими входами первого и второго мультиплексоров адреса, вторая группа выходов блока памяти микропрограмм соединена с первой группой информационных входов первого мультиплексора микроопераций и первой группой информационных входов второго мультиплексора микроопераций, группа выходов которого соединена с первой группой, информационных входов регистра микрокоманд и первой группой информационных входов второго мультиплексора логических условий, третья группа выходов блока памяти микрокоманд соединена с второй группой информационных входов второго мультиплексора микроопераций и с второй группой информационных входов первого мультиплексора микроопераций, группа выходов которого соединена с второй группой информационных входов регистра микрокоманд и первой группой информационных входов первого мультиплексора адреса, группа выходов которого соединена с первой группой входов регистра адреса, выход мультиплексора логических условий соединен с управляющими входами первого и второго мультиплексоров микроопераций, вторые группы информационных входов первого и второго мультиплексоров адреса соединены с выходом .стековой памяти (шины адреса), группа выходов второго мультиплексора адреса соединена с второй группой входов регистра адреса, выходы которого соединены с входами дешифратора, выход дешифратора соединен с входом блока памяти микропрограмм 3.

Недостатками известного устройства являются низкая оперативность контроля объектов и узкая область применения.

Это устройство может быть использовано для выполнения проверок различных объектов контроля, потребность в проверке которых возникает асинхронно. При этом оно должно последовательно производить опрос объектов контроля с целью выявления объекта, требующего проведения проверки, осуществлять проверку и далее снова переходить к опросу объектов. Кроме дого, если в системе имеется объект, обладающий наивысшим приоритетом по запросу на выполнение проверки, например, такой, который чрезвычайно критичен ко времени отключения от основного режима функционирования, то устройство должно периодически включать .микроподпрограмму опроса такого объекта. Такая дисциплина обслуживания объектов контроля снижает оперативность контроля за счет увеличения времени ожидания проверки объектами контроля.

Указанные недостатки обуслоливают снижение быстродействия контроля объектов данным устройством.

Область применения известного устройства сужается из-за невозможности реализации обслуживания объектов контроля по запросам, наиболее приоритетного в порядке, определяемом дисциплиной обслуживания с абсолютными приоритетами, и объектов низших приоритетов в порядке, определяемом дисциплиной обслуживания с относительными приоритетами.

Целью изобретения является повышение быстродействия контроля и расширение области применения.

Поставленная цель достигается тем, что в микропрограммное устройство управления с контролем, содердащее блок памяти микропрограмм, регистр адреса микрокоманд, регистр микрокоманд, мультиплексор адреса, мультиплексор логических условий, де шифратор и первый элемент И, причем группа выходов мультиплексора адреса соединена с группой информационных входов регистра адреса микрокоманд, выходы которого соединены с входами блока памяти микропрограмм, выходы модифицируемых разрядов, адреса группы выходов блока памяти микропрограмм соединены с первой 5 группой информационных входов мультиплексора логических условий группы, входы бесприоритетных логических условий устройства соединены с соответствующими входами второй группы информационных входов мультиплексора логических условий; выход первого элементаИ соединен с управляющим входом мультиплексора адреса, первая группа информационных входов которого является группой адресных входов устройства, первая группа выходов регистра .микрокоманд является первой группой управляющих выходов устройства, введены .блок (,i :.(i :. чтисгп запросов, регистр ЗЫПОр;;. :;:: ir ,: гор. ОПИЙНЫЙ фОрМЧроватсл1, боок niinvinirrcTa запросов, блок

приоритета VL.ii.s:;, гср запроса, триг гер прерЬ;ВЛ111;ч, ;.:;) тротий и четвер t и : lJiH. причем елитый элеме; ;ь; 1.г .-лшросов соединень, ничные входы

с COOTsereТЬ;:

.V4;:;:aMi группы ВХО:ч1:-::. вы.-чоды регистру

дов запросе-; i, соответствующими запросов сое.

входами блок; iipii-ji iivera запросов и элемента ИЛИ. выло.1 которого соединены с инфop aLu On;iь 4i).i;;.; триггера запроса, единичный выход триггера запроса соединен с перв:з;м пхолом плока синхронизации,

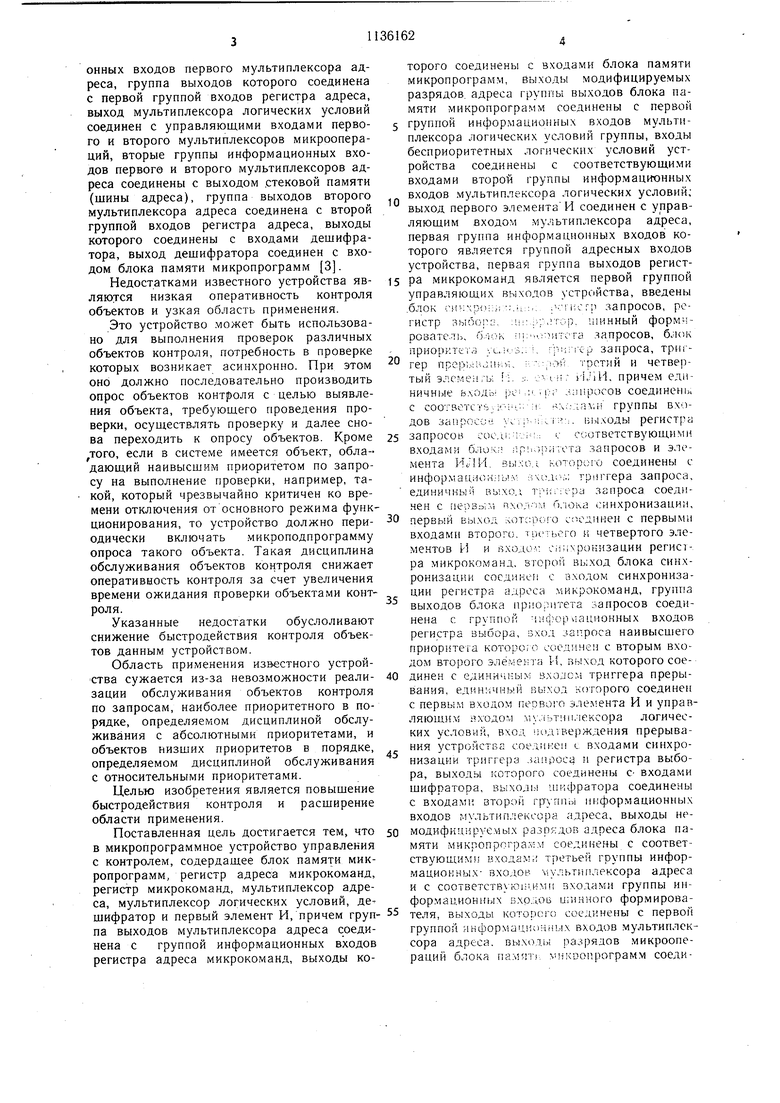

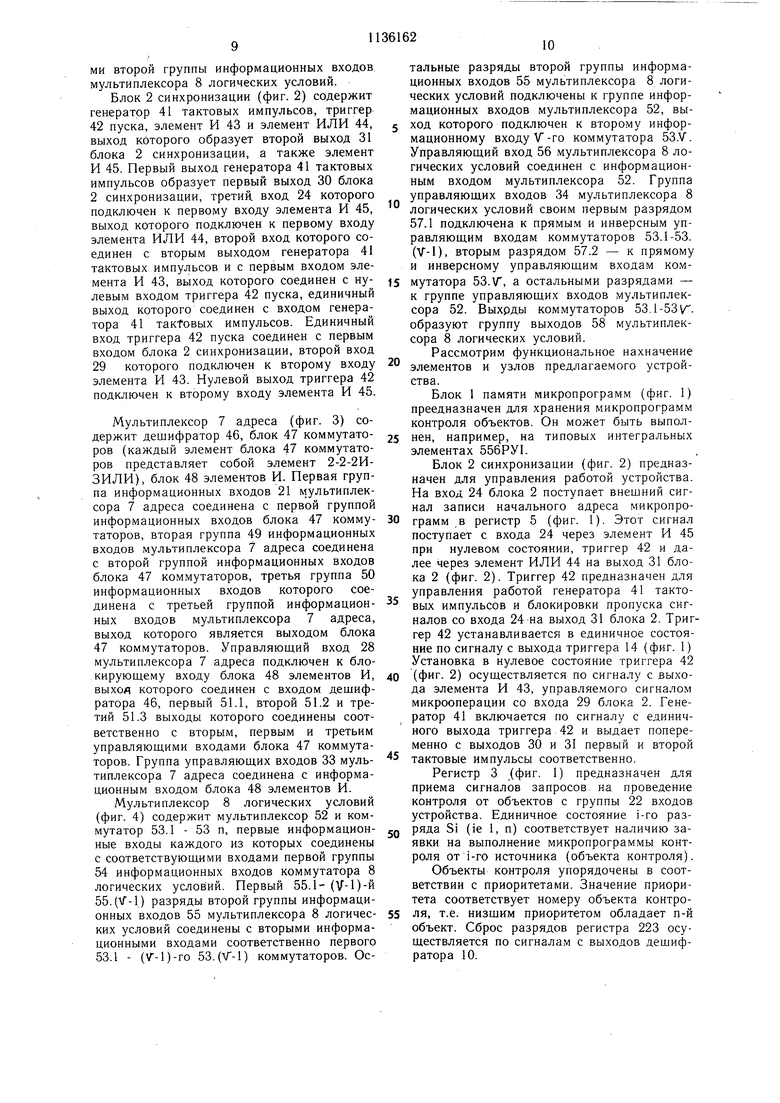

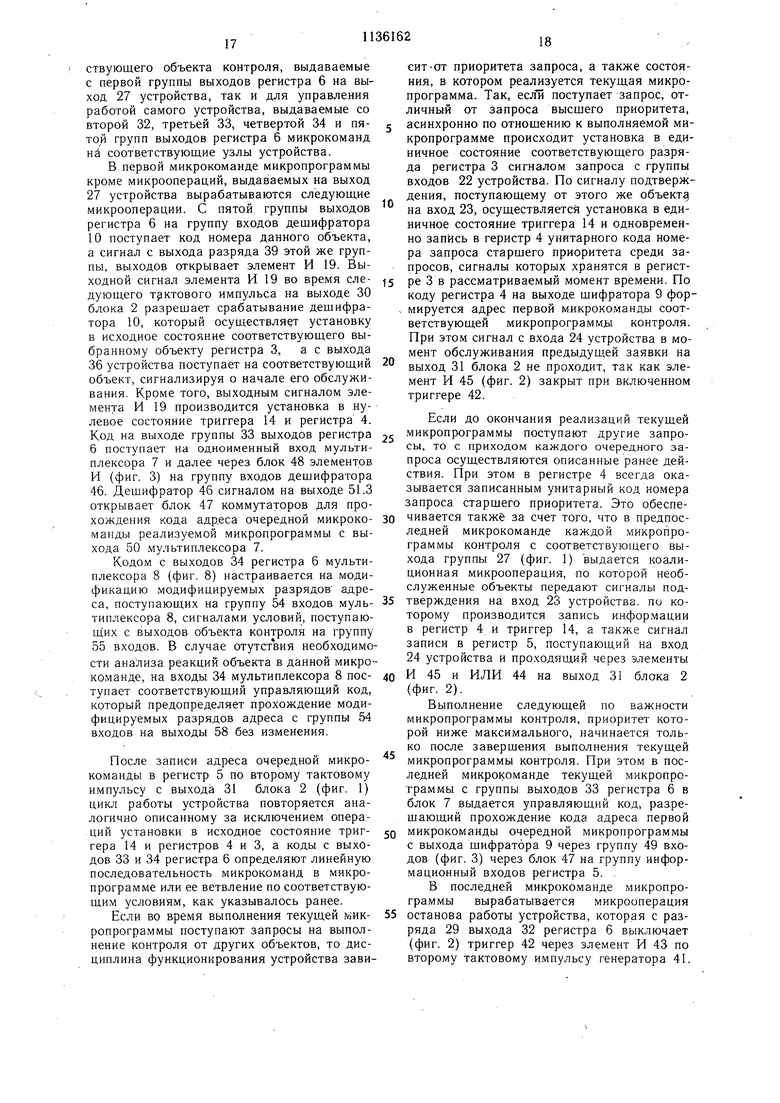

0 первый выход лотсгоого еосдииен с первыми входами второго, тг,етьсго и, четвертого э.лементов И и 8xo,:io- симхрокизации регистра микрокоманд, зторой выход блока синхронизации соедикеп с входом синхронизации регистра адреса .микрокоманд, группа выходов блока iipiiopirrera запросов соединена с группой информационных входов регистра выбора, зход ai-poca наивысшего приоритега которого соединен с вторым входом второго элемента И, ныход которого сое0 дивен с единичным зхолсл триггера прерывания, еднн:гчнын выход которого соединен с первым входом пеово -о элемента И и управляющим г Ходом .мудьтнп.чексора логических условий, вход подтверждения прерывания устройства coe.iiiHeH с входами синхронизации триггера -uiHpoca и регистра выбора, выходы которого соединены С входами шифратора, выходгч шифратора соединены с входами второй гругпгы информационных входов мультиплексора адреса, выходы немодифицируемых разрядов адреса блока памяти микропрограж.м соединены с соответствующим вxoдa i,; третьей группы информациоккь х- входов мультиплексора адреса и с соответствующими входами группы информационных входов и:ииного формирователя, выходы котор01Ч) соединены с первой группой информаци;)нных входов мультиплексора адреса, выходы разрядов микроопераций блока ). икпоирограмм соедийены с соответствующими входами группы информационных входов регистра микрокоманд, выход первого разряда второй группы выходов которого соединен с вторым входом блока- синхронизации, третий вход которого соединен с входом пуска устройства, выход второго разряда второй группы выходов регистра микрокоманд соединен с вторым входом первого элемента И, выход которого соединен с управляющим входом шинного формирователя и является управляющим выходом устройства, выходы третьего и четвертого разрядов второй группы выходов регистра микрокоманд соединены с вторыми входами второго и третьего элементов И соответственно, выход третьего элемента И соединен с нулевым входом триггера прерывания, третья группа выходов регистра микрокоманд соединена с группой управляющих входов мультиплексора адреса, четвертая группа выходов регистра микрокоманд соединена с группой управляющих входов мультиплексора логических условий, группа выходов которого соединена с соответствующими разрядами группы информационных входов щинного формирователя и с входами модифицируемых разрядов адреса третьей группы информационных входов мультиплексора адреса, выходы разрядов номера объекта и выход управляющего разряда пятой группы выходов регистра микромоканд соединены соответственно с группой информационных входов дещифратора и вторым входом четвертого элемента И, выход которого соединен с входами установки в нулевое состояние триггера запроса и регистра выбора и с управляющим входом дешифратора, выходы которого соединены с соответствующими нуле, выми входами регистра запросов и с выходом сигнализации устройства, входы приоритетных логических условий группы входов логических условий устройства соединены с соответствующими входами группы входов блока приоритета условий, выходы которого соединены с соответствующими входами второй группы информационных входов мультиплексора логических условий. Сущность изобретения состоит в повышении быстродействия контроля за счет снижения времени ожидания объектами проведения контроля путем реализации новой дисциплины обслуживания запросов на проверку. Суть этой новой дисциплины состоит в обслуживании низкс1приоритетных объектов по относительным приоритетам и в обслуживании высокоприоритетного объекта по абсолютному приоритету. Причем, в отличие от известного устройства, опрос низкоприоритетных объектов осуществляется не циклически последовательно, а одновременно всех, что позволяет сразу выбирать для проверки объект с наибольщими приоритетом среди выдавших запросы. Таким образом удается снизить время ожидания контроля для низкоприоритетных объектов благодаря исключению времен опроса объектов, расположенных в цепи опроса до рассматриваемого объекта, а также опроса объекта, обладающего максимальным приоритетом. Кроме того, время ожидания высокоприоритетного объекта снижается до величины, определяемой средней длительностью непрерываемых (критических) участков низкоприоритетных микропрограмм контроля. Введение регистра запросов позволяет воспринимать запросы на контроль непосредственно в момент их выдачи объектами. Введением элемента ИЛИ и триггера запроса позволяет осуществлять включение устройства при поступлении первого запроса на выполнение микропрограммы контроля. Введение блока приоритета запросов и регистра запросов позволяет осуществлять выбор приоритетного запроса на обслуживание. Введение щифратора - формировать адрес первой микрокоманды выполняемой микропрограммы, шинного формирователя осуществлять перемедачу адреса прерываемой микропрограммы во внешнюю память, триггера прерывания - управлять обработкой запроса наивысщего приоритета и, кроме того, осуществлять прирывание текущей низкоприоритетной микропрограммы. Кроме того, введение второго - четвертого элементов И позволяет осуществлять управление режимами работы устройства, а введение блока приоритета логических условий осуществлять приоритетную градацию подмножества приоритетных логических условий. Таким образом, введение указанных новых элементов и обусловленных ими связей позволяет повысить быстродействие контроля и расщирить область применения устройства. На фиг. 1 представлена функциональная схема предлагаемого устройства; на фиг. 2 - функциональная схема блока синхронизации; на фиг. 3 - функциональная схема мультиплексора адреса; на фиг. 4 функциональная схема мультиплексора логических условий. Устройство содержит блок i памяти микропрограмм, блок 2 синхронизации, регистр 3 запросов, регистр 4 выбора, регистр 5 адреса микрокоманд, регистр 6 микрокоманд мультиплексор 7 адреса, мультиплексор 8 логических условий, шифратор 9, дешифратор 10, шинный формирователь 11, блок 12 приоритетов запросов , блок 13 приоритетов условий, триггер 14 запроса, триггер 15 прерывания, второй 16, третий 17, первый 18 и четвертый 19 элементы И, элемент ИЛИ 20, щину 21 адреса, группу 22 входов запро- сов устройства, вход 23 подтверждения

устройства, вход 24 пуска устройства, группу 25 адресных входов устройства, группу 26 входов логических условий устройства, группу 27 управляющих выходов устройства, управляющий выход 28 устройства, второй вход 29 блока 2, первый выход 30 блока 2, второй выход 31 блока 2, вторую 32, третью 33 и четвертую 34 группы выходов регистра 6, выход 35 сигнализации устройства, третий 36, четвертый 37 и второй 38 соответственно разряды второй группы 32 выходов регистра 6, управляющий разряд 39 пятой группы выходов регистра 6, выход 40 старщего приоритета сх-емы 12.

Группа выходов мультиплексора 7 адреса соединена с группой информационных входов регистра 5 адреса микрокоманд, выходы которого соединены с входами блока 1 памяти микропрограммы, выходы модифицируемых разрядов адреса группы выходов блока 1 памяти микропрограмм соединены с первой группой информационных входов мультиплексора 8 логических условий группы, входы бесприоритетных логических условий устройства соединены с соответствующими входами в торой группы информационных входов мультиплексора 8 логических условий, выход первого элемента И 18 соединен с управляющим входом мультиплексора 7 адреса, первая группа информационных входов которого является группой 25 адресных входов устройства, первая группа выходов регистра 6 микрокоманд является первой группой 27 управляющих выходов устройства.

Единичные входы регистра 3 запросов соединены с соответствующими входам группы 22 входов запросов устройства. Выходы регистра 3 запросов соединены с соответствующими входами блока 12 приоритета запросов и элемента ИЛИ 20 , выход которого соединен с информационным входом триггера 14 запроса, единичный выход триггера 14 запроса соединен с первым входом блока 2 синхронизации, первый выход 30 которого соединен с первыми входами второго 16, третьего 17 и четвертого 19 элементов И и входом синхронизации регистра 6 микрокоманд, второй выход 31 блока 2 синхронизации соединен с входом синхронизации регистра 5 адреса микрокоманд, группа выходов блока 12 приоритета запросов соединена с группой информационных входов регистра 4 выбора, вход 40 запроса наивысщего приоритета которого соединен с вторым входх)м 40 второго элемента И 16, выход которого соединен с единичным входом триггера 15 прерывания, единичный выход которого соединен с первым входом первого элемента И 18 с управляющим входом мультиплексора 8 логических условий. Вход 23 подтверждения прерывания устройства соединен с входами синхронизации триггера 14 запроса и регистра 4 выбора, выходы которого соединены с входами щифратора 9, выходы которого соединены с входами второй группы информационных .входов мультиплексора 7 адреса, «выходы немодифицируемых разрядов адреса блока 1 памяти микропрограмм соединены с соответствующими входами третьей группы информационных входов мультиплексора 7 адреса и с соответствующими входами группы информационных входов щинного формирователя 11, выходы которого соединены с первой группой информационных в.кодов мультиплексора 7 адреса, выходы разрядов микроопераций блока 1 памяти микропрограмм соединены с соответствующими входами группы информационных входов регистра 6 микрокома гл, выход 29 первого разряда второй группы 32 выходов которого соединен с вторым входом 29 блока 2 синхронизаци11, ipeiiiK вход 24 которого соединен с входом 24 пуска устройства, выход 38 второго разряда BTOpoii группы 32 выходов регистра б микрокоманд соединен с вторым входом первого лемента 18 И, выход которого соединен с управляющим входом шинного формирователя 11 и является управляющим выходом 28 устройства , выходы третьего 36 и четвертого 37 разрядов второй группы 32 выходов регистра 6 микрокоманд соединены с вторыми входами второго 16 и третьего 7 элементов И соответственно, выход третьего элемента И 17 соединен с нулевым входом триггера 15 прерывания, третья группа 33 выходов регистра 6 микрокоманд соединена с группой управляющих входов мультиплексора 7 адреса, четвер-. тая группа 34 выходов регистра 6 микрокоманд соединена с группой упраатяющих входов мультиплексора 8 логических условий, группа выходов которого соединена с соответствующими разрядами группы информационных входов шинного формирователя 11 с входами модифицируемых разрядов адреса третьей группы информационных входов мультиплексора 7 адреса, выходы разрядов номера объекта и выход 39 управляющего разряда пятой группы выходов регистра 6 микрокоманд соединены соответственно с группой информационных входов дешифратора 10 и вторым входом четвертого элемента И 19, выход которого соединен с входами установки в нулевое . состояние триггера 14 запроса и регистра 4- выбора и с управляющим входом дешифратора 10, выходы которого соединены с соответствующими нулевыми входами регистра 3 запросов и выходом 35 сигнализации устройства, входы разрядов приоритетных логических условий группы 26 входов логических условий устройства соединены с соответствующими входами группы входов блока 13 приоритета условий, выходы которого соединены с соответствующими входами второй группы информационных входов мультиплексора 8 логических условий.

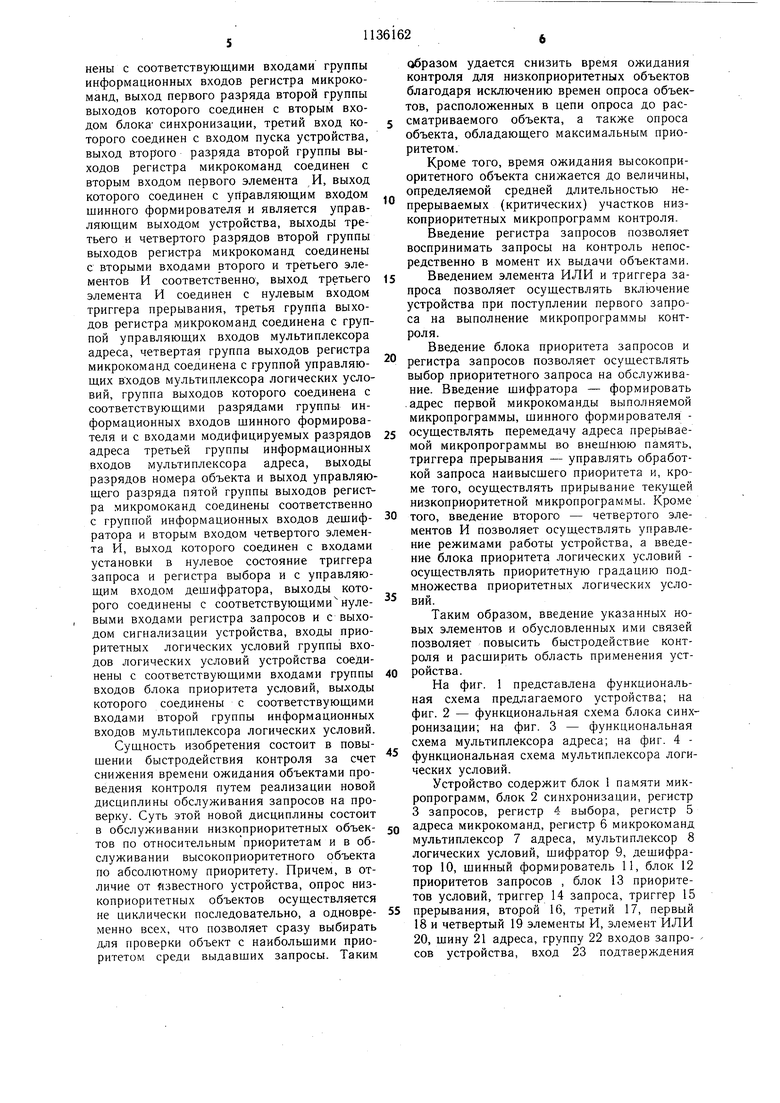

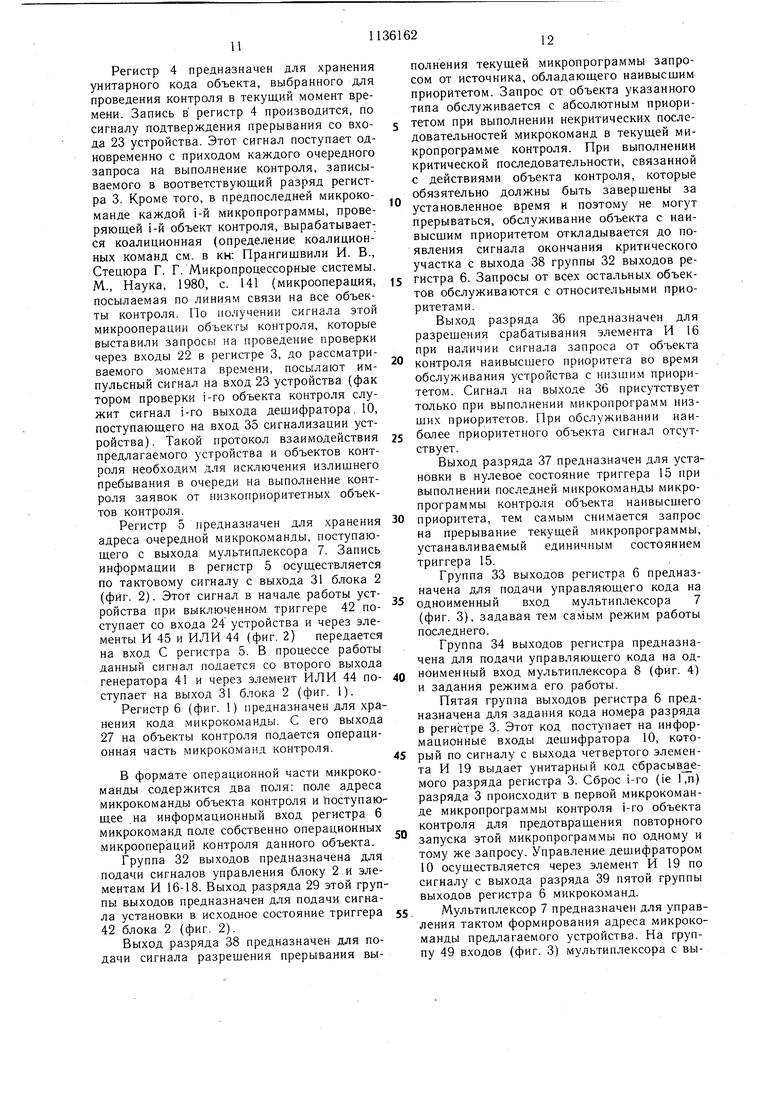

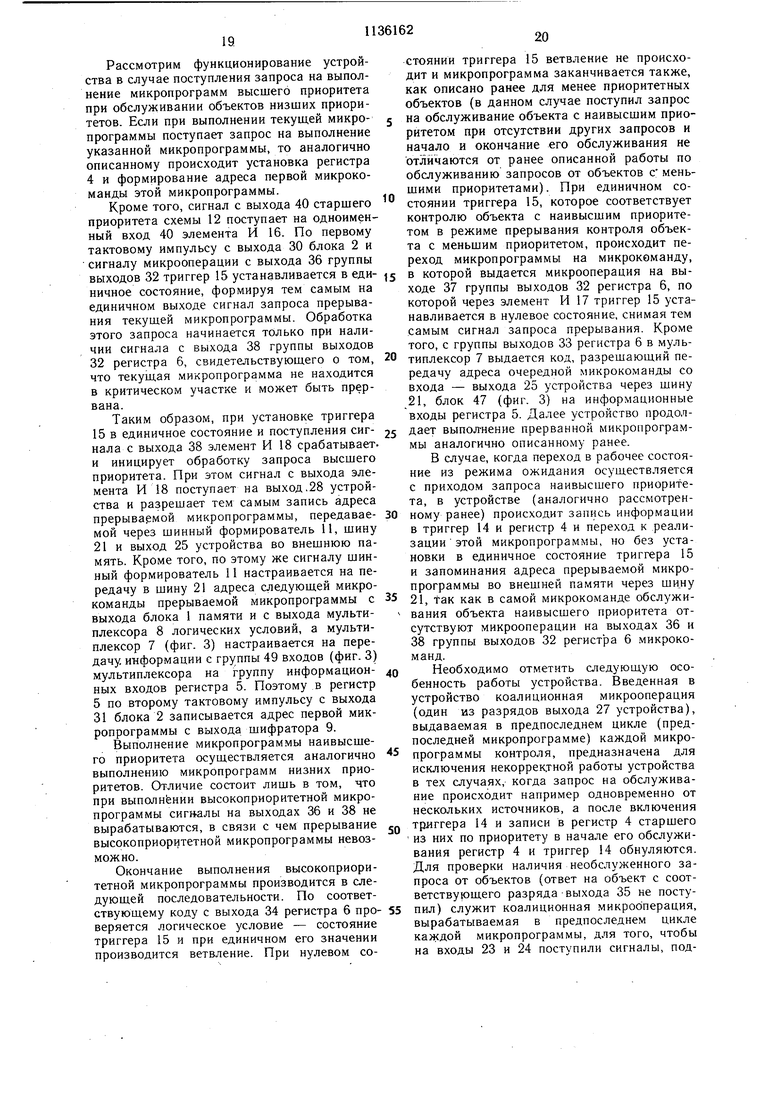

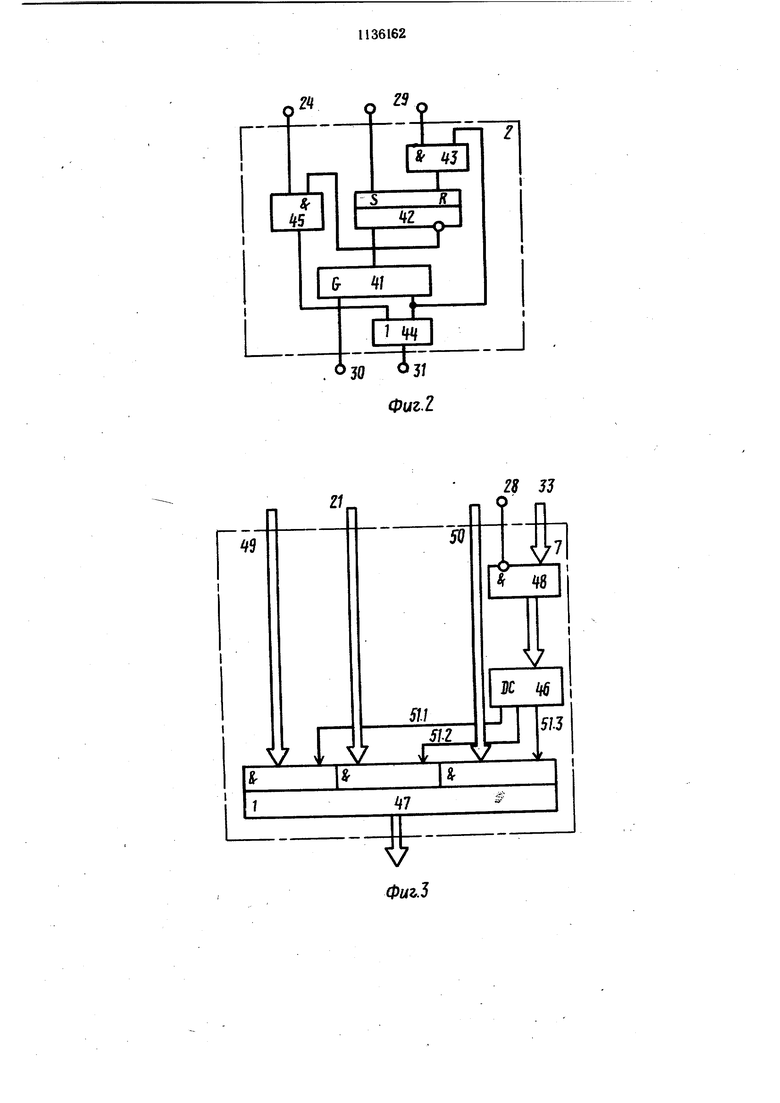

Блок 2 синхронизации (фиг. 2) содержит генератор 41 тактовых импульсов, триггер 42 пуска, элемент И 43 и элемент ИЛИ 44, выход которого образует второй выход 31 блока 2 синхронизации, а также элемент И 45. Первый выход генератора 41 тактовых импульсов образует первый выход 30 блока 2 синхронизации, третий, вход 24 которого подключен к первому входу элемента И 45, выход которого подключен к первому входу элемента ИЛИ 44, второй вход которого соединен с вторым выходом генератора 41 тактовых импульсов и с первым входом элемента И 43, выход которого соединен с нулевым в.ходом триггера 42 пуска, единичный выход которого соединен с входом генератора 41 тактовых импульсов. Единичный вход триггера 42 пуска соединен с первым входом блока 2 синхронизации, второй вход 29 которого подключен к второму входу элемента И 43. Нулевой выход триггера 42 подключен к второму входу элемента И 45.

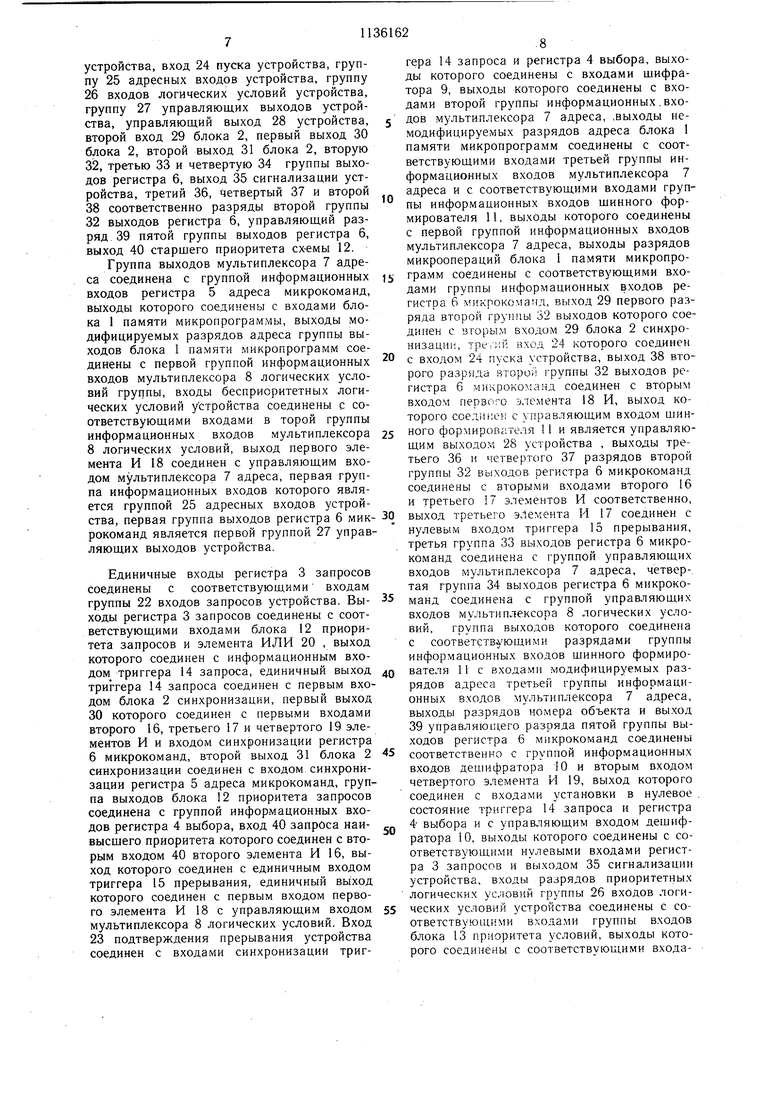

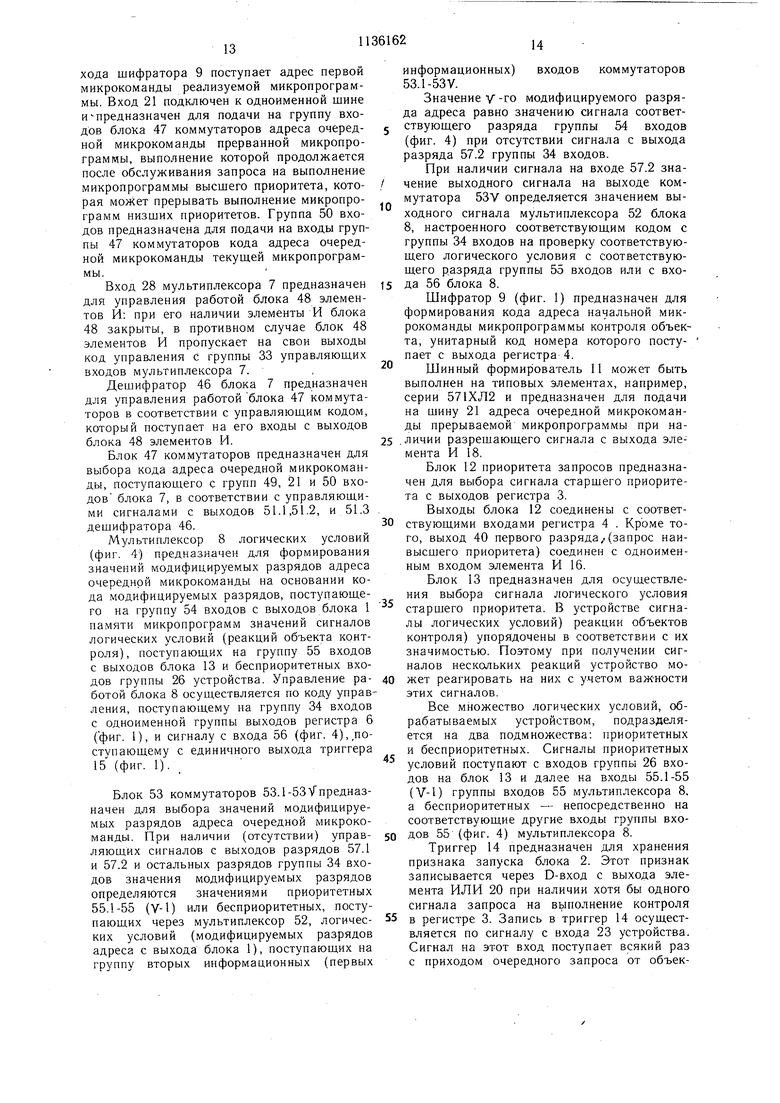

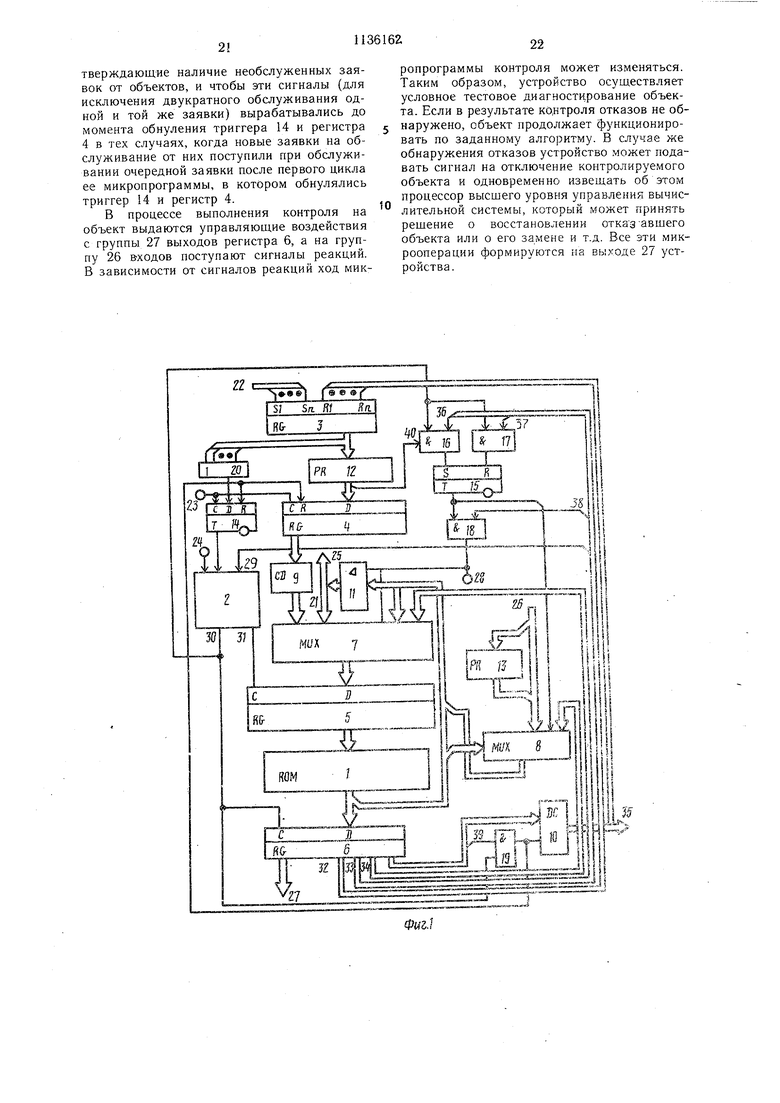

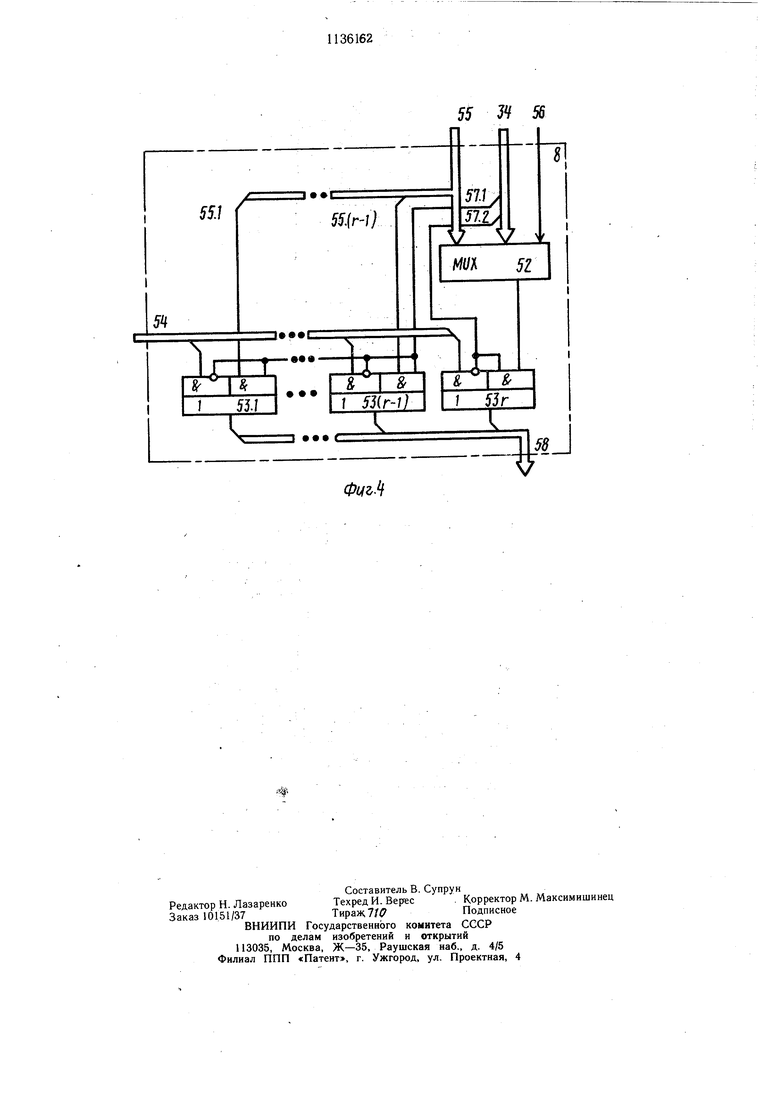

Мультиплексор 7 адреса (фиг. 3) содержит дешифратор 46, блок 47 коммутаторов (каждый элемент блока 47 коммутаторов представляет собой элемент 2-2-2ИЗИЛИ), блок 48 элементов И. Первая группа информационных входов 21 мJльтиплeксора 7 адреса соединена с первой группой информационных входов блока 47 коммутаторов, вторая группа 49 информационных входов мультиплексора 7 адреса соединена с второй группой информационных входов блока 47 коммутаторов, третья группа 50 информационных входов которого соединена с третьей группой информационных входов мультиплексора 7 адреса, выход которого является выходом блока 47 коммутаторов. Управляющий вход 28 мультиплексора 7 адреса подключен к блокирующему входу блока 48 элементов И, выхоя которого соединен с входом дешифратора 46, первый 51.1, второй 51.2 и третий 51.3 выходы которого соединены соответственно с вторым, первым и третьим управляющими входами блока 47 коммутаторов. Группа управляющих входов 33 мультиплексора 7 адреса соединена с информационным входом блока 48 элементов И.

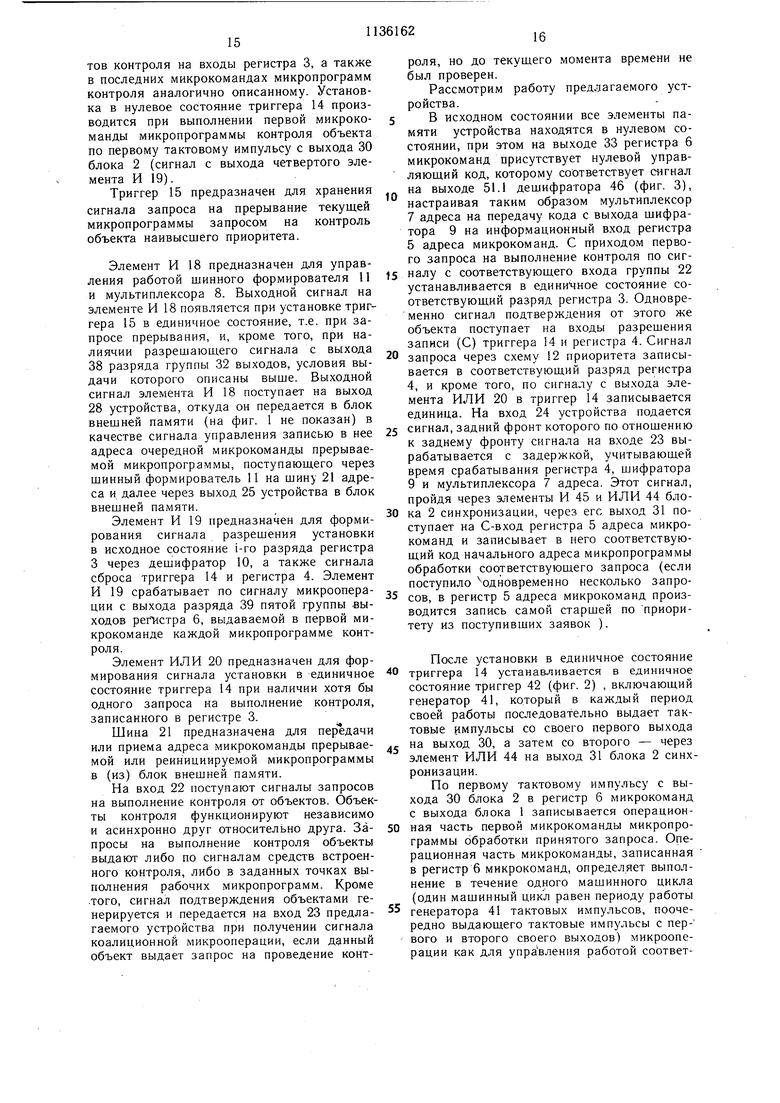

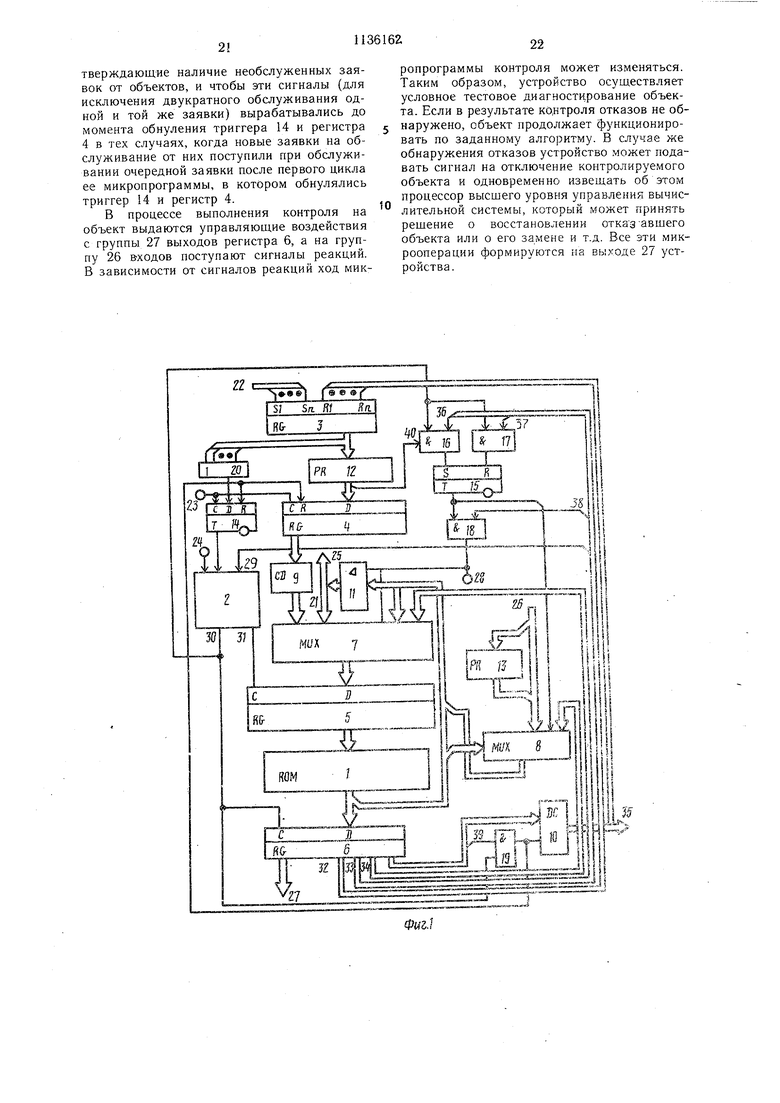

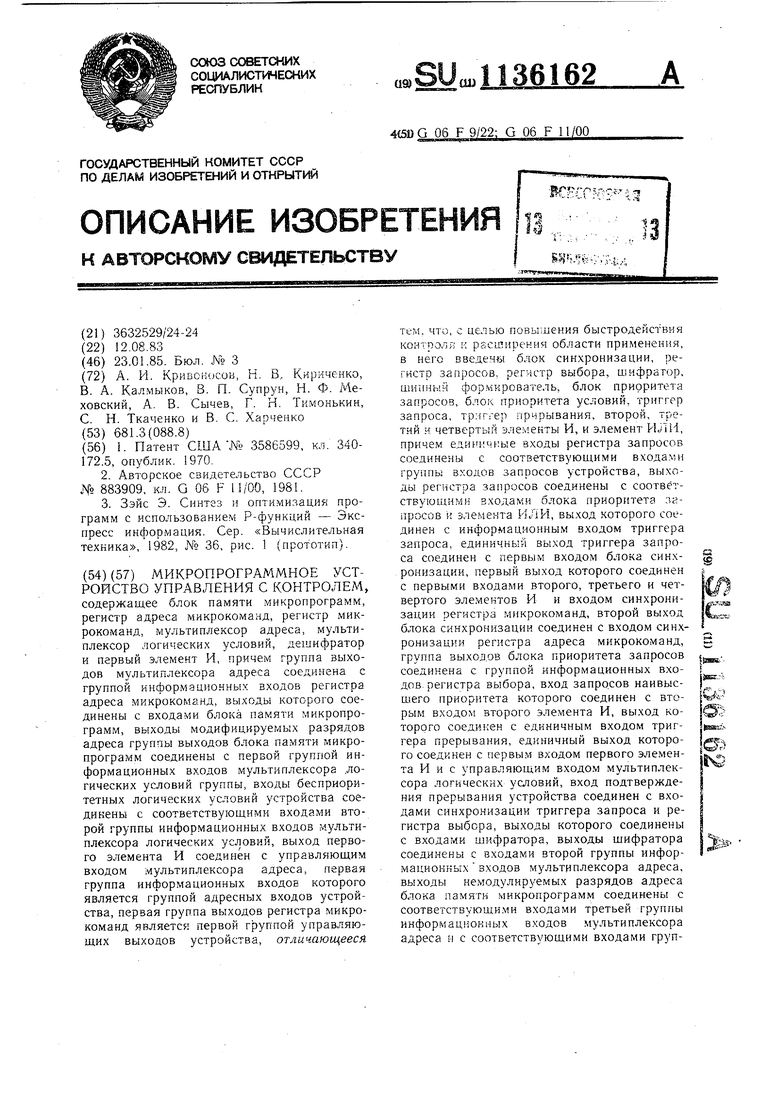

Мультиплексор 8 логических условий (фиг. 4) содержит мультиплексор 52 и коммутатор 53.1 - 53 п, первые информационные входы каждого из которых соединены с соответствующими входами первой группы 54 информационных входов коммутатора 8 логических условий. Первый 55.1- (У-1)-й 55.(Г-1) разряды второй группы информационных входов 55 мультиплексора 8 логических условий соединены с вторыми информационными входами соответственно первого 53.1 - (V-l)-ro 53.(V-1) коммутаторов. Остальные разряды второй группы информационных входов 55 мультиплексора 8 логических условий подключены к группе информационных входов мультиплексора 52, выход которого подключен к второ.му информационному входу V-го коммутатора 53.. Управляющий вход 56 мультиплексора 8 логических условий соединен с информационным входом мультиплексора 52. Группа управляющих входов 34 мультиплексора 8 логических условий своим первым разрядом 57.1 подключена к прямым и инверсным управляющим входам коммутаторов 53.1-53. (Г-1), вторым разрядом 57.2 - к прямому и инверсному управляющим входам коммутатора 53.V, а остальными разрядами - к группе управляющих входов мультиплексора 52. Выхрды коммутаторов 53-l-53v. образуют группу выходов 58 мультиплексора 8 логических условий.

Рассмотрим функциональное нахначение элементов и узлов предлагаемого устройства.

Блок 1 памяти микропрограмм (фиг. 1) преедназначен для хранения микропрограмм контроля объектов. Он может быть выполнен, например, на типовых интегральных элементах 556РУ1.

Блок 2 синхронизации (фиг. 2) предназначен для управления работой устройства. На вход 24 блока 2 поступает внешний сигнал записи начального адреса микропрограмм ,в регистр 5 (фиг. 1). Этот сигнал поступает с входа 24 через элемент И 45 при нулевом состоянии, триггер 42 и далее через элемент ИЛИ 44 на выход 31 блока 2 (фиг. 2). Триггер 42 предназначен для управления работой генератора 41 тактовых импульсов и блокировки пропуска сигналов со входа 24 на выход 31 блока 2. Триггер 42 устанавливается в единичное состояние по сигналу с выхода триггера 14 (фиг. 1) Установка в нулевое состояние триггера 42

0 (фиг. 2) осуществляется по сигналу с выхода элемента И 43, управляемого сигналом микрооперации со входа 29 блока 2. Генератор 41 включается по сигналу с единичного выхода триггера 42 и выдает попеременно с выходов 30 и 31 первый и второй

5 тактовые импульсы соответственно.

Регистр 3 (фиг. 1) предназначен для приема сигналов запросов на проведение контроля от объектов с группы 22 входов устройства. Единичное состояние i-ro разQ ряда Si (ie 1, п) соответствует наличию заявки на выполнение микропрограммы контроля от i-ro источника (объекта контроля). Объекты контроля упорядочены в соответствии с приоритетами. Значение приоритета соответствует номеру объекта контроля, т.е. низщкм приоритетом обладает п-й объект. Сброс разрядов регистра 223 осуществляется по сигналам с выходов дешифратора 10.

Регистр 4 предназначен для хранения унитарного кода объекта, выбранного для проведения контроля в текущий момент времени. Запись в регистр 4 производится, по сигналу подтверждения прерывания со входа 23 устройства. Этот сигнал поступает одновременно с приходом каждого очередного запроса на выполнение контроля, записываемого в воответствующий разряд регистра 3. Кроме того, в предпоследней микрокоманде каждой i-й микропрограммы, проверяющей i-й объект контроля, вырабатывается коалиционная (определение коалиционных команд см. в кн: Прангищвили И. В., Стецюра Г. Г. Микропроцессорные системы. М., Наука, 1980, с. 141 (микрооперация, посылаемая по линиям связи на все объекты контроля. По получении сигнала этой микрооперации объекты контроля, которые выставили запросы на проведение проверки через входы 22 в регистре 3, до рассматриваемого момента времени, посылают импульсный сигнал на вход 23 устройства (фак тором проверки i-ro объекта контроля служит сигнал i-ro выхода дешифратора. 10, поступающего на вход 35 сигнализации устройства). Такой протокол взаимодействия предлагаемого устройства и объектов контроля необходим для исключения излишнего пребывания в очереди на .выполнение контроля заявок от низкоприоритетных объектов контроля.

Регистр 5 предназначен для хранения адреса очередной микрокоманды, поступающего с выхода мультиплексора 7. Запись информации в регистр 5 осуществляется по тактовому сигналу с выхода 31 блока 2 (фиг. 2). Этот сигнал в начале работы устройства при выключенном триггере 42 поступает со входа 24 устройства и через элементы И 45 и ИЛИ 44 (фиг. 2) передается на вход С регистра 5. В процессе работы данный сигнал подается со второго выхода генератора 41 и через элемент ИЛИ 44 поступает на выход 31 блока 2 (фиг. 1).

Регистр 6 (фиг. 1) предназначен для хранения кода микрокоманды. С его выхода 27 на объекты контроля подается операционная часть микрокоманд контроля.

В формате операционной части микрокоманды содержится два поля: поле адреса микрокоманды объекта контроля и поступающее .на информационный вход регистра 6 микрокоманд поле собственно операционных микроопераций контроля данного объекта.

Группа 32 выходов предназначена для подачи сигналов управления блоку 2 и элементам И 16-18. Выход разряда 29 этой группы выходов предназначен для подачи сигнала установки в исходное состояние триггера 42 блока 2 (фиг. 2).

Выход разряда 38 предназначен для подачи сигнала разрешения прерывания выполнения текущей микропрограммы запросом от источника, обладающего наивысшим приоритетом. Запрос от объекта указанного типа обслуживается с абсолютны.м приоритетом при выполнении некритических последовательностей микрокоманд в текущей микропрограмме контроля. При выполнении критической последовательности, связанной с действиями объекта контроля, которые обязятельно должны быть завершены за

0 установленное время и поэтому не могут прерываться, обслуживание объекта с наивысшим приоритетом откладывается до появления сигнала окончания критического участка с выхода 38 группы 32 выходов регистра 6. Запросы от всех остальных объектов обслуживаются с относительными приоритетами.

Выход разряда 36 предназначен для разрешения срабатывания элемента И 16 при наличии сигнала запроса от объекта

0 контроля наивысшего приоритета во время обслуживания устройства с низшим приоритетом. Сигнал на выходе 36 присутствует только при выполнении микропрограмм низших приоритетов. При обслуживании наиболее приоритетного объекта сигнал отсутствует.

Выход разряда 37 предназначен для установки в нулевое состояние триггера 15 при выполнении последней микрокоманды микропрограммы контроля объекта наивысшего 0 приоритета, тем самым снимается запрос на прерывание текущей микропрограммы, устанавливаемый единичным состоянием триггера 15.

Группа 33 выходов регистра 6 предназначена для подачи управляющего кода на 5 одноименный вход мультиплексора 7 (фиг. 3), задавая тем самым режим работы последнего.

Группа 34 выходов регистра предназначена для подачи управляющего кода на одQ ноименный вход мультиплексора 8 (фиг. 4) и задания режима его работы.

Пятая группа выходов регистра 6 предназначена для задания кода номера разряда в регистре 3. Этот код поступает на информационные входы дешифратора 10, который по сигналу с выхода четвертого элемента И 19 выдает унитарный код сбрасыва емого разряда регистра 3. Сброс i-ro (ie l,n) разряда 3 происходит в первой микрокоманде микропрограммы контроля i-ro объекта контроля для предотвращения повторного запуска этой микропрограммы по одному и тому же запросу. Управление дешифратором 10 осуществляется через элемент И 19 по сигналу с выхода разряда 39 пятой группы выходов регистра 6 микрокоманд. 5. Мультиплексор 7 предназначен для управления тактом формирования адреса микрокоманды предлагаемого устройства. На группу 49 входов (фиг. 3) мультиплексора с выхода шифратора 9 поступает адрес первой микрокоманды реализуемой микропрограммы. Вход 21 подключен к одноименной шине ипредназначен для подачи на группу входов блока 47 коммутаторов адреса очередной микрокоманды прерванной микропрограммы, выполнение которой продолжается после обслуживания запроса на выполнение микропрограммы высшего приоритета, которая может прерывать выполнение микропрограмм низших приоритетов. Группа 50 входов предназначена для подачи на входы группы 47 коммутаторов кода адреса очередной микрокоманды текущей микропрограммы. Вход 28 мультиплексора 7 предназначен для управления работой блока 48 элементов И: при его наличии элементы И блока 48 закрыты, в противном случае блок 48 элементов И пропускает на свои выходы код управления с группы 33 управляющих входов мультиплексора 1., Дешифратор 46 блока 7 предназначен для управления работой блока 47 коммутаторов в соответствии с управляющим кодом, который поступает на его входы с выходов блока 48 элементов И. Блок 47 коммутаторов предназначен для выбора кода адреса очередной микрокоманды, поступаюш,его с групп 49, 21 и 50 входов блока 7, в соответствии с управляющими сигналами с выходов 51.1,51.2, и 51.3 дещифратора 46. Мультиплексор 8 логических условий (фиг. 4) предназначен для формирования значений модифицируемых разрядов адреса очередной микрокоманды на основании кода модифицируемых разрядов, поступающего на группу 54 входов с выходов блока 1 памяти микропрограмм значений сигналов логических условий (реакций объекта контроля), поступающих на группу 55 входов с выходов блока 13 и бесприоритетных входов группы 26 устройства. Управление работой блока 8 осуществляется по коду управ ления, поступающему на группу 34 входов с одноименной группы выходов регистра 6 (фиг. 1), и сигналу с входа 56 (фиг. 4),,поступающему с единичного выхода триггера 15 (фиг. 1). Блок 53 коммутаторов 53.1-53 1предназначен для выбора значений модифицируемых разрядов адреса очередной микрокоманды. При наличии (отсутствии) управляющйх сигналов с выходов разрядов 57.1 и 57.2 и остальных разрядов группы 34 входов значения модифицируемых разрядов определяются значениями приоритетных 55.-55 (V-1) или бесприоритетных, поступающих через мультиплексор 52, логических условий (модифицируемых разрядов адреса с выхода блока 1), поступающих на группу вторых информационных (первых информационных) входов коммутаторов 53.1-53V. Значение модифицируемого разряда адреса равно значению сигнала соответствующего разряда группы 54 входов (фиг. 4) при отсутствии сигнала с выхода разряда 57.2 группы 34 входов. При наличии сигнала на входе 57.2 значение выходного сигнала на выходе коммутатора 53V определяется значением выходного сигнала мультиплексора 52 блока 8, настроенного соответствующим кодом с группы 34 входов на проверку соответствующего логического условия с соответствующего разряда группы 55 входов или с входа 56 блока 8. Шифратор 9 (фиг. 1) предназначен для формирования кода адреса начальной микрокоманды микропрограммы контроля объекта, унитарный код номера которого поступает с выхода регистра 4. Щинный формирователь 11 может быть выполнен на типовых элементах, например, серии 571ХЛ2 и предназначен для подачи на шину 21 адреса очередной микрокоманды прерываемой микропрограммы при наличии разрещающего сигнала с выхода элемента И 18. Блок 12 приоритета запросов предназначен для выбора сигнала старшего приоритета с выходов регистра 3. Выходы блока 12 соединены с соответствующими входа.ми регистра 4 . Кроме того, выход 40 первого разряда/(запрос наивысшего приоритета) соединен с однои.менным входом элемента И 16. Блок 13 предназначен для осуществления выбора сигнала логического условия старшего приоритета. В устройстве сигналы логических условий) реакции объектов контроля) упорядочены в соответствии с их значимостью. Поэтому при получении сигналов нескольких реакций устройство может реагировать на них с учетом важности этих сигналов. Все множество логических условий, обрабатываемых устройством, подразделяется на два подмножества: приоритетных и бесприоритетных. Сигналы приоритетных условий поступают с входов группы 26 входов на блок 13 и далее на входы 55.1-55 (V-1) группы входов 55 мультиплексора 8, а бесприоритетных - непосредственно на соответствующие другие входы группы входов 55 (фиг. 4) мультиплексора 8. Триггер 14 предназначен для хранения признака запуска блока 2. Этот признак записывается через D-вход с выхода элемента ИЛИ 20 при наличии хотя бы одного сигнала запроса на вь1полнение контроля в регистре 3. Запись в триггер 14 осуществляется по сигналу с входа 23 устройства. Сигнал на этот вход поступает всякий раз с приходом очередного запроса от объектов контроля на входы регистра 3, а также в последних микрокомандах микропрограмм контроля аналогично описанному. Установка в нулевое состояние триггера 14 производится при выполнении первой микрокоманды микропрограммы контроля объекта по первому тактовому импульсу с выхода 30 блока 2 (сигнал с выхода четвертого элемента И 19).

Триггер 15 предразначен для хранения сигнала запроса на прерывание текущей микропрограммы запросом на контроль объекта наивысшего приоритета.

Элемент И 18 предназначен для управления работой шинного формирователя 11 и мультиплексора 8. Выходной сигнал на элементе И 18 появляется при установке триггера 15 в единичное состояние, т.е. при запросе прерывания, и, кроме того, при налиячии разрешающего сигнала с выхода 38 разряда группы 32 выходов, условия выдачи которого описаны выше. Выходной сигнал элемента И 18 поступает на выход 28 устройства, откуда он передается в блок внешней памяти (на фиг. 1 не показан) в качестве сигнала управления записью в нее адреса очередной микрокоманды прерываемой микропрограммы, поступающего через шинный формирователь 11 на шину 21 адреса и далее через выход 25 устройства в блок внешней памяти.

Элемент И 19 предназначен для формирования сигнала разрешения установки в исходное состояние i-ro разряда регистра 3 через дешифратор 10, а также сигнала сброса триггера 14 и регистра 4. Элемент И 19 срабатывает по сигналу микрооперации с выхода разряда 39 пятой группы выходов регистра 6, выдаваемой в первой микрокоманде каждой микропрограмме контроля.

Элемент ИЛИ 20 предназначен для формирования сигнала установки в единичное состояние триггера 14 при наличии хотя бы одного запроса на выполнение контроля, записанного в регистре 3.

Шина 21 предназначена для передачи или приема адреса микрокоманды прерываемой или реинициируемой микропрограммы в (из) блок внешней памяти.

На вход 22 поступают сигналы запросов на выполнение контроля от объектов. Объекты контроля функционируют независимо и асинхронно друг относительно друга. Запросы на выполнение контроля объекты выдают либо по сигналам средств встроенного контроля, либо в заданных точках выполнения рабочих микропрограмм. Кроме .того, сигнал подтверждения объектами генерируется и передается на вход 23 предлагаемого устройства при получении сигнала коалиционной микрооперации, если данный объект выдает запрос на проведение контроля, но до текущего момента времени не был проверен.

Рассмотрим работу предлагаемого устройства.

5 В исходном состоянии все элементы памяти устройства находятся в нулевом состоянии, при этом на выходе 33 регистра 6 микрокоманд присутствует нулевой управляющий код, которому соответствует сигнал на выходе 51.1 дешифратора 46 (фиг. 3), настраивая таким образом мультиплексор 7 адреса на передачу кода с выхода шифратора 9 на информационный вход регистра 5 адреса микрокоманд. С приходом первого запроса на выполнение контроля по сигналу с соответствующего входа группы 22 устанавливается в единичное состояние соответствующий разряд регистра 3. Одновременно сигнал подтверждения от этого же объекта поступает на входы разрешения записи (С) триггера 14 и регистра 4. Сигнал

0 запроса через схему 12 приоритета записывается в соответствующий разряд регистра 4, и кроме того, по сигналу с выхода элемента ИЛИ 20 в триггер 14 записывается единица. На вход 24 устройства подается

5 сигнал, задний фронт которого по отношению к заднему фронту сигнала на входе 23 вырабатывается с задержкой, учитывающей время срабатывания регистра 4, шифратора 9 и мультиплексора 7 адреса. Этот сигнал, пройдя через элементы И 45 и ИЛИ 44 блока 2 синхронизации, через егс выход 31 поступает на С-вход регистра 5 адреса микрокоманд и записывает в него соответствующий код начального адреса микропрограммы обработки соответствующего запроса (если поступило одновременно несколько запросов, в регистр 5 адреса микрокоманд производится запись самой старшей по приоритету из поступивших заявок ).

После установки в единичное состояние

0 триггера 14 устанавливается в единичное состояние триггер 42 (фиг. 2) , включающий генератор 41, который в каждый период своей работы последовательно выдает тактовые импульсы со своего первого выхода

, на выход 30, а затем со второго - через элемент ИЛИ 44 на выход 31 блока 2 синхро.низации.

По первому тактовому и.мпульсу с выхода 30 блока 2 в регистр 6 микрокоманд с выхода блока 1 записывается операционная часть первой микрокоманды микропрограммы обработки принятого запроса. Операционная часть микрокоманды, записанная в регистр 6 микрокоманд, определяет выполнение в течение одного машинного цикла (один машинный цикл равен периоду работы

генератора 41 тактовых импульсов, поочередно выдающего тактовые импульсы с первого и второго своего выходов) микрооперации как для управления работой соответствующего объекта контроля, выдаваемые с первой группы выходов регистра 6 на выход 27 устройства, так и для управления работой самого устройства, выдаваемые со второй 32, третьей 33, четвертой 34 и пятой групп выходов регистра 6 микрокоманд на соответствующие узлы устройства.

В первой микрокоманде микропрограммы кроме микроопераций, выдаваемых на выход 27 устройства вырабатываются следующие микрооперации. С пятой группы выходов регистра 6 на группу входов дешифратора 10 поступает код номера данного объекта, а сигнал с выхода разряда 39 этой же группы, выходов открывает элемент И 19. Выходной сигнал элемента И 19 во время еледующего тактового импульса на выходе 30 блока 2 разрешает срабатывание дешифратора 10, который осуществляет установку в исходное состояние соответствующего выбранному объекту регистра 3, а с выхода 36 устройства поступает на соответствующий объект, сигнализируя о начале его обслуживания. Кроме того, выходным сигналом элемента И 19 производится установка в нулевое состояние триггера 14 и регистра 4. Код на выходе группы 33 выходов регистра 6 поступает на одноименный вход мультиплексора 7 и далее через блок 48 элементов И (фиг. 3) на группу входов дешифратора 46. Дешифратор 46 сигналом на выходе 51.3 открывает блок 47 коммутаторов для прохождения кода адр,еса очередной микрокоманды реализуемой микропрограммы с выхода 50 мультиплексора 7.

Кодом с выходов 34 регистра 6 мультиплексора 8 {фиг. 8) настраивается на модификацию модифицируемых разрядов адреса, поступаюн1,их на группу 54 входов мультиплексора 8, сигналами условий, поступаюпХих с выходов объекта контроля на группу 55 входов. В случае отутствия необходимости реакций объекта в данной микрокоманде, на входы 34 мультиплексора 8 поступает соответствующий управляющий код, который предопределяет прохождение модифицируемых разрядов адреса с группы 54 входов на выходы 58 без изменения.

После записи адреса очередной микрокоманды в регистр 5 по второму тактовому импульсу с выхода 31 блока 2 (фиг. 1) цикл работы устройства повторяется аналогично описанному за исключением операций установки в исходное состояние триггера 14 и регистров 4 и 3, а коды с выходов 33 и 34 регистра 6 определяют линейную последовательность микрокоманд в микропрограмме или ее ветвление по соответствующим условиям, как указывалось ранее.

Если во время выполнения текущей микропрограммы поступают запросы на выполнение контроля от других объектов, то дисциплина функционирования устройства зависит-от приоритета запроса, а также состояния, в котором реализуется текущая микропрограмма. Так, еслТ5 поступает запрос, отличный от запроса высшего приоритета, асинхронно по отношению к выполняемой микропрограмме происходит установка в единичное состояние соответствующего разряда регистра 3 сигналом запроса с группы входов 22 устройства. По сигналу подтверждения, поступающему от этого же объекта на вход 23, осуществляется установка в единичное состояние триггера 14 и одновременно запись в геристр 4 унитарного кода номера запроса старщего приоритета среди запросов, сигналы которых хранятся в регистре 3 в рассматриваемый момент времени. По коду регистра 4 на выходе шифратора 9 формируется адрес первой микрокоманды соответствующей микропрогра.ммъ контроля. При этом сигнал с входа 24 устройства в момент обслуживания предыдущей заявки на выход 31 блока 2 не проходит, так как элемент И 45 (фиг. 2) закрыт при включенном триггере 42.

Если до окончания реализаций текущей микропрограммы поступают другие запросы, то с приходом каждого очередного запроса осуществляются описанные ранее действия. При этом в регистре 4 всегда оказывается записанным унитарный код номера запроса старщего приоритета. Это обеспечивается также за счет того, что в предпоследней микрокоманде каждой микропрограммы контроля с соответствуюЕцего выхода группы 27 (фиг. 1) выдается коалиционная микрооперация, по которой необслуженные объекты передают сигналы подтверждения на вход 23 устройства, по которому производится запись инфор.мации в регистр 4 и триггер 14, а также сигнал записи в регистр 5, поступающий на вход 24 устройства и проходящий через элементы

И 45 и ИЛИ 44 на выход 31 блока 2 (фиг. 2).

Выполнение следующей по важности микропрограммы контроля, приоритет которой ниже максимального, начинается только после завершения выполнения текущей микропрограммы контроля. При этом в последней микрокоманде текущей микропрограммы с группы выходов 33 регистра 6 в блок 7 выдается управляющий код, разрешающий прохождение кода адреса первой микрокоманды очередной микропрограммы с выхода щифратора 9 через группу 49 входов (фиг. 3) через блок 47 на группу информационный входов регистра 5. .

В последней микрокоманде микропрограммы вырабатывается микрооперация останова работы устройства, которая с разряда 29 выхода 32 регистра 6 выключает (фиг. 2) триггер 42 через элемент И 43 по второму тактовому импульсу генератора 41.

Рассмотрим функционирование устройства в случае поступления запроса на выполнение микропрограмм высшего приоритета при обслуживании объектов низших приоритетов. Если при выполнении текуш,ей микропрограммы поступает запрос на выполнение указанной микропрограммы, то аналогично описанному происходит установка регистра

4и формирование адреса первой микрокоманды этой микропрограммы.

Кроме того, сигнал с выхода 40 старшего приоритета схемы 12 поступает на одноименный вход 40 элемента И 16. По первому тактовому импульсу с выхода 30 блока 2 и сигналу микрооперации с выхода 36 группы выходов 32 триггер 15 устанавливается в единичное состояние, формируя тем самым на единичном выходе сигнал запроса прерывания текущей микропрограммы. Обработка этого запроса начинается только при наличии сигнала с выхода 38 группы выходов 32 регистра 6, свидетельствующего о том, что текущая микропрограмма не находится в критическом участке и может быть прервана.

Таким образом, при установке триггера 15 в единичное состояние и поступления сигнала с выхода 38 элемент И 18 срабатывает и иницирует обработку запроса высшего приоритета. При этом сигнал с выхода элемента И 18 поступает на выход.28 устройства и разрешает тем самым запись адреса прерываемой микропрограммы, передаваемой через шинный формирователь И, шину 21 и выход 25 устройства во внешнюю память. Кроме того, по этому же сигналу шинный формирователь 11 настраивается на передачу в шину 2 адреса следующей микрокоманды прерываемой микропрограммы с выхода блока 1 памяти и с выхода мультиплексора 8 логических условий, а мультиплексор 7 (фиг. 3) настраивается на передачу, информации с группы 49 входов (фиг. 3) мультиплексора на группу информационных входов регистра 5. Поэтому в регистр

5по второму тактовому импульсу с выхода 31 блока 2 записывается адрес первой микропрограммы с выхода шифратора 9.

Выполнение микропрограммы наивысшего приоритета осуществляется аналогично выполнению микропрограмм низних приоритетов. Отличие состоит лишь в том, что при выполнении высокоприоритетной микропрограммы сигналы на выходах 36 и 38 не вырабатываются, в связи с чем прерывание высокоприор1 тетной микропрограммы невозможно.

Окончание выполнения высокоприоритетной микропрограммы производится в следующей последовательности. По соответствующему коду с выхода 34 регистра 6 проверяется логическое условие - состояние триггера 15 и при единичном его значении производится ветвление. При нулевом состоянии триггера 15 ветвление не происходит и микропрограмма заканчивается также, как описано ранее для менее приоритетных объектов (в данном случае поступил запрос на обслуживание объекта с наивысшим приоритетом при отсутствии других запросов и начало и окончание его обслуживания не отличаются от ранее описанной работы по обслуживанию запросов от объектов с меньшими приоритетами). При единичном состоянии триггера 15, которое соответствует контролю объекта с наивысшим приоритетом в режиме прерывания контроля объекта с меньшим приоритетом, происходит переход микропрограммы на микрокоманду, в которой выдается микрооперация на выходе 37 группы выходов 32 регистра 6, по которой через элемент И 17 триггер 15 устанавливается в нулевое состояние, снимая тем самым сигнал запроса прерывания. Кроме того, с группы выходов 33 регистра 6 в мультиплексор 7 выдается код, разрешающий передачу адреса очередной микрокоманды со входа - выхода 25 устройства через шику 21, блок 47 (фиг. 3) на информационные входы регистра 5. Далее устройство продолдает выпол-нение прерванной микропрограммы аналогично описанному ранее.

В случае, когда переход в рабочее состояние из режима ожидания осуществляется с приходом запроса наивысшего приоритета, в устройстве (аналогично рассмотренному ранее) происходит запись информации в триггер 14 и регистр 4 и переход к реализации этой микропрограммы, но без установки в единичное состояние триггера 15 и запоминания адреса прерываемой микропрограммы во внешней памяти через 21, так как в самой микрокоманде обслуживания объекта наивысшего приоритета отсутствуют микрооперации на выходах 36 и 38 группы выходов 32 регистра 6 микрокоманд.

Необходимо отметить следующую особенность работы устройства. Введенная в устройство коалиционная микрооперация (один из разрядов выхода 27 устройства), выдаваемая в предпоследнем цикле (предпоследней микропрограмме) каждой микропрограммы контроля, предназначена для исключения некоррек,тной работы устройства в тех случаях, когда запрос на обслуживание происходит например одновременно от нескольких источников, а после включения триггера 14 и записи в регистр 4 старшего из них по приоритету в начале его обслуживания регистр 4 и триггер 14 обнуляются. Для проверки наличия необслуженного запроса от объектов (ответ на объект с соответствующего разряда выхода 35 не поступил) служит коалиционная микрооперация, вырабатываемая в предпоследнем цикле каждой микропрограммы, для того, чтобы на входы 23 и 24 поступили сигналы, подтверждающие наличие необслуженных заявок от объектов, и чтобы эти сигналы (для исключения двукратного обслуживания одной и той же заявки) вырабатывались до момента обнуления триггера 14 и регистра 4 в тех случаях, когда новые заявки на обслуживание от них поступили при обслуживании очередной заявки после первого цикла ее микропрограммы, в котором обнулялись триггер 14 и регистр 4.

В процессе выполнения контроля на объект выдаются управляющие воздействия с группы 27 выходов регистра 6, а на группу 26 Входов поступают сигналы реакций. В зависимости от сигналов реакций ход микропрограммы контроля может изменяться. Таким образом, устройство осуществляет условное тестовое диагностирование объекта. Если в результате контроля отказов не обнаружено, объект продолжает функционировать по заданному алгоритму. В случае же обнаружения отказов устройство может подавать сигнал на отключение контролируемого объекта и одновременно извещать об этом процессор высщего уровня управления вычислительной системы, который может принять решение о восстановлении откаЗавщего объекта или о его замене и т.д. Все эти микрооперации формируются на вру.ходе 27 устройства.

ги

Sf W

Zf

79

-i

Plj

iT

HI

& 4/I

i

ЕД

050 Ajl Фиг. 2

f Л

Ф«г.5

55 JV 56

0б/г.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США№ 3586599, кл | |||

| 0 |

|

SU340172A1 | |

| Кинематографический аппарат | 1923 |

|

SU1970A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Синтез и опти.мизация программ с использование | |||

| Р-функций - Экспресс информация | |||

| Сер | |||

| «Вычислительная техника, 1982, № 36, рис | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1985-01-23—Публикация

1983-08-12—Подача