ляются одноименньми входами устройства, первый и второй выходы формирователя управляющих сигналов являются соответственно выходами Неисправность устройства прерывания программ и Прерывание устройства, третий, четвертый, пятый и шестой выходы формирователя управляющих сигналов соединены соответственно с входом записи регистра прерываний, регистра кода прерываний, с управляющий входом дешифратора и с входом элемента ИЛИ, формирователь управляющих сигналов содержит D-триггеры, элементы И, элементы ИЛИ, элементы НЕ и элемент И-НЕ, причем вход Прерывание фоС мирователя управляющих сигналов соединен с информационным входом первого D-триггера, с первыми входами первого и второго элементов И и с входом первого элемента НЕ, выход которого соединен с первьм входом третьего элемента И, вход Ошибка Формирователя управляющих сигналов соединен с информационным входом второго D-триггера, прямой коход которого , соединен с первыми входами четвёртого и пятого элементов И, с вторым входом третьего эпемен-га- и и является первым выходом формирователя управляющих сигналов, вход Опрос прерывания формирователя управляющих сигналов соединен с входе .второго элемента И, с третьим входом третьего элемента И и с тактовым входом первого D-триггера, прямой выход которого соединен с первым входом элемента И-НБ, с вторым входом четвертого элемента И и является вторым аиходом формирователя управляющих сигналов , инверсный выхрд первого р-тритгера соединен с первым входом первого элемента ИЛИ и со вторым входом первого элемента И, выход которого

соединен с первым входом второго элемента ИЛИ, вход Сброс прерывания формирователя управлякяцих сигналов соединен с входом установки в ноль первого и третьего Ь-триггеров и с пятым выходом формирователя управляющих сигналов, тактовый вход формирователя управляющих сигналов соединен с тактовым входом второго и третьего D-триггеров, с вторым входом пятого

элемента И, с первым входом шестого элемента И и с входом второго элемента НЕ, выход которого соединен с первым входом седьмого элемента И, с третьим входом первого элеменоа И и с BTOESjiiM входом элемента И-НЕ, прЯЕмой выход D-триггера соединен с втоЕвлм входом первого элемента :ИЛИ, входом седьмого элемента И, с третьим входом пятого элемента И и с третьим входом элемента И-НЕf выход которого соединен с вхрддм установки в ноль второго D-триггера, выход первого элемента ИЛИ соединен с вторвлм входом шестого элемента И, вых:од которого является третьим вь ходрм формирователя управляющих сигналов, выход второго эл емента И соеинен с вторь 4 входом второго элемента ИЛИ, выход которого является четверть выходом ФОЕ гарова;телй управлякицих сигналовувыход третьего элемента И соединен с первым входом

третьего элемента ИЛИ,; выход которр го является шестым выходом ф ормйррвателя управляющих (Сигналов выход четертогчэ элемента И соединен с инфорационным входом тЬетье1: о D-триггера, выход пятого элемента И соединен с втс«ж входом третьего эле : ИЛИ,: щаход сед|ьмого элемента И ; соединен с третьим входом второго элемена ИЛИ-,; ,.; . :;, . ;,;:. , .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для прерывания программ | 1978 |

|

SU744575A1 |

| Устройство для сопряжения датчиков с ЭВМ | 1983 |

|

SU1129600A1 |

| Многоканальное устройство для обмена информацией | 1984 |

|

SU1359781A1 |

| Устройство для прерывания программ | 1978 |

|

SU736101A1 |

| Устройство для сопряжения датчиков с ЭВМ | 1985 |

|

SU1282108A1 |

| Многоканальное устройство ввода информации | 1988 |

|

SU1529238A1 |

| Устройство для прерывания резервированной вычислительной системы | 1984 |

|

SU1218385A1 |

| Устройство для сопряжения | 1980 |

|

SU962906A2 |

| Устройство для обмена информацией | 1982 |

|

SU1048468A1 |

| Устройство для прерывания программ | 1981 |

|

SU1001103A1 |

УСТРОЙСТВО ДЛЯ ПРЕРЫВАНИЯ ПРОГРАММ, содержащее N-разрядные регистр прерываний и регистр маски, блок анализа приоритета прерываний, шифратор и блок анализа состояния устройства, причем выходы регистра -прерываний и регистра маски соединены соответственно с входами блока анализа приоритета прерываний, выходы которого соединены с входами шифратора, блок-анализа состояния устройства содержит элемент четности, схему сравнения и элемент ИЛИ, причем выход элемента четности соединен с первым входом схемы сравнения, отличающееся тем, что, с целью повышения надежности устройства, введены буферный регистр, регистр кода прерывания, регистр готовности, дешифратор, счетчик, эле мент ИЛИ, формирователь управляющих сигналов и группа из Н элементов И, блок анализа состояния устройства дополнительно содержит второй и третий элементы четности и вторую схему сравнения, причем группа информаци- . онных входов устройства соединена соответственно с информационными входами регистра маски, регистра готовности и буферного регистра, выходы которого соединены соответственно с информационными входами регистра прерываний, выходы регистра готовности соединены соответственно с входами блока анализа приоритета прерываний и с первыми входами элементов И группы, выход блока анализа приоритета прерываний соединен с | входом Прерывание формирователя управляющих сигналов, с первым входом второй схемы сравнения и с вторым входом первой схемы сравнения блока анализа состояния устройства, ; группа выходов блока анализа прйбритета прерываний, относящаяся тк четньл прерываниям, соединена соответственно с группой входов первого элемента четности блока анал1рза состояния устройства и с первой группой входов шифратора, группа выходов блока анализа приоритета прерываний, относящаяся к нечетным прерываниям, § соединена соответственно с группой (О входов второго элемента четности блока анализа состояния устройства и со второй группой входов шифратора выходы, которого соединены соответственно с информационными входами регистра кода прерывания, выходы регис тра кода прерывания образуют выход Код номера прерывания устройства и соединены соответственно с информаци-, | онными входами дешифратора и с группой входов .третьего элемента четнос O Э { ти блока анализа состояния устройства, выход которого соединен с входом Ошибка формирователя управляющих сигналов, выходы дешифратора соединеЛ ны с группой входов элемента ИЛИ и с вторыми входами элементов И группы, выходы которых соединены соответственно с входами установки в ноль буферного регистра и регистра прерываний, выход элемента ИЛИ соединен со счетным входом счетчика, выход старшего разряда которого является выходом Переход ЦВМ на резерв устройства, установочный вход устройства соединен с установочным входом счетчика, входы Опрос прерывания, Сброс прерывания и тактовый фор- , мирователя управляющих сигналов яв

. ,.

Изобретение относится к вычислительной технике и может быть использовано в системах прерывания цифровых вычислительных машин.

Известно устройство для обработки запросов : контролем очередности, содержащее блок памяти, датчик окончания обслуживания, записывающий и считывающий кольцевые счетчики, блок синхронизации кольцевых .счетчиков, схемы запрета, фО1 1Иррватель импульсов, соединенный с шифратором, первые схемы И, nepBEJe входы которых соединены с шифратором, вторые входы соединены с выходами записывающего счетчика, схемы ИЖ,

соединенные с входами Дешифратора, вторые схемы .И, первые входы которых соединены с выходами ячеек памяти, вторые - с выходами считывающего 5 счетчика, а эыходда - с соответствуют щими входами сзс ИЛИ, третьи схемы И и блок контроля «аЛичия информации/ входы которого соединены с выхсщами ячеек йашти, а выходы - с

ti первыми входами схем запрета и третьих, схем И и с входами блока синкронизации, первый и второй выходы , которого соединены с входами соответствующих счетчико ву вторые входы

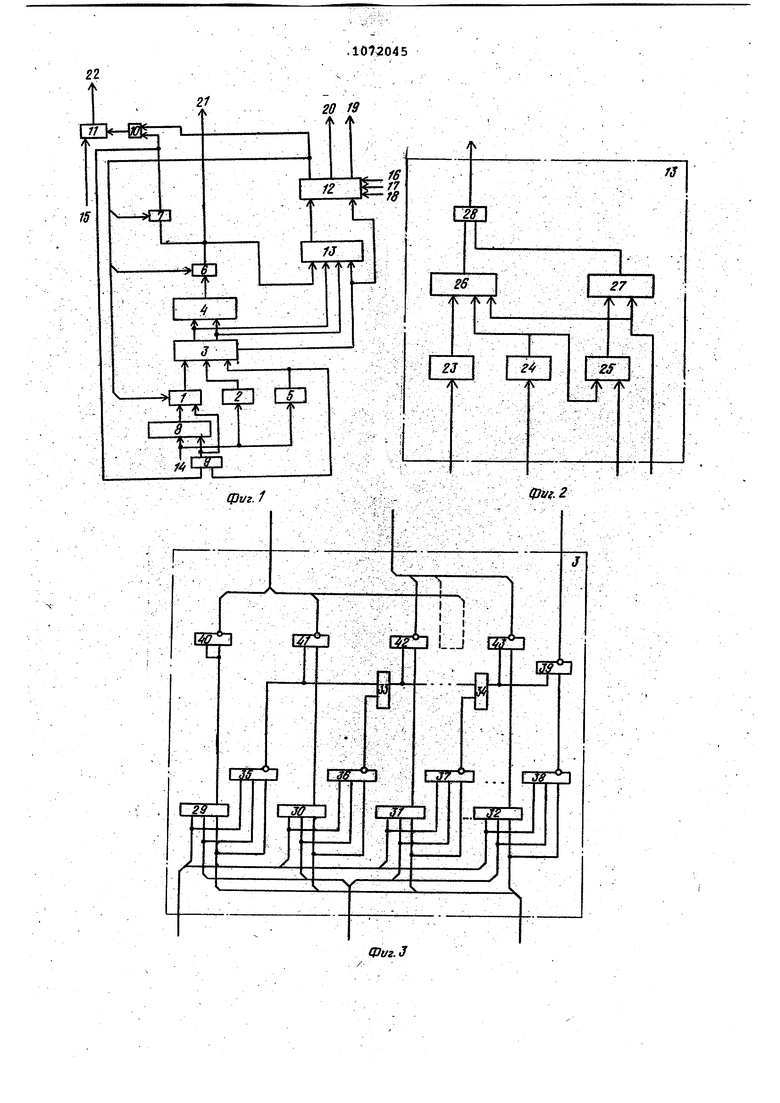

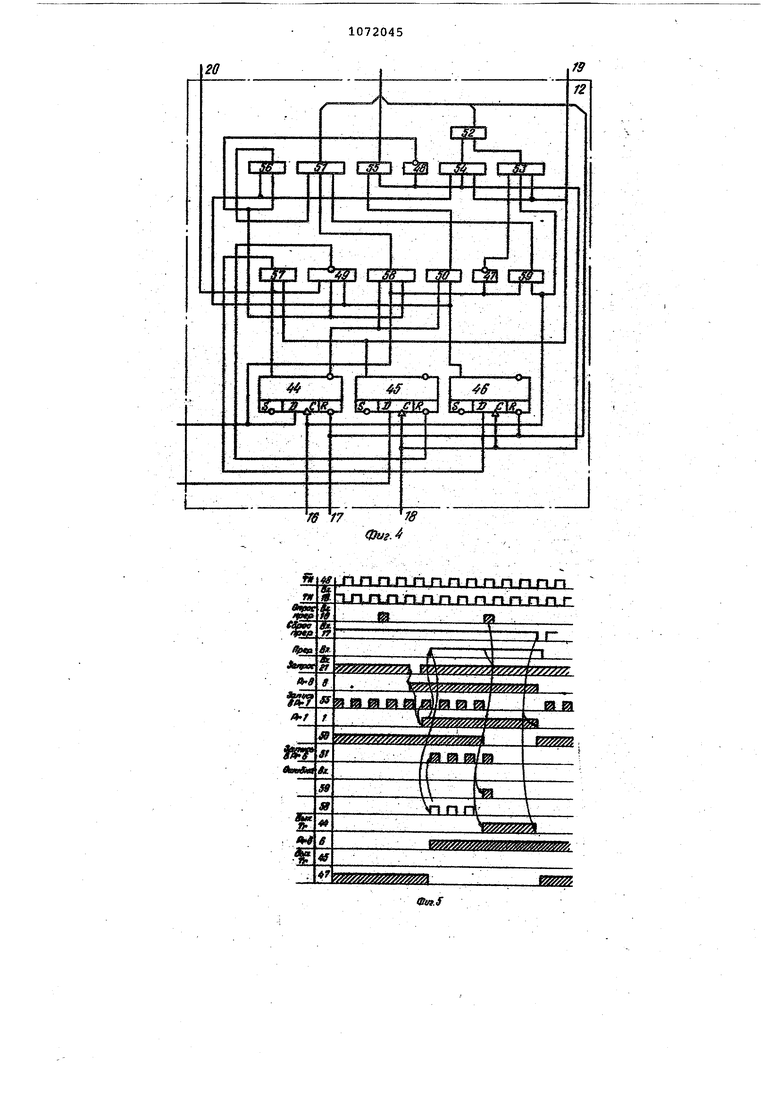

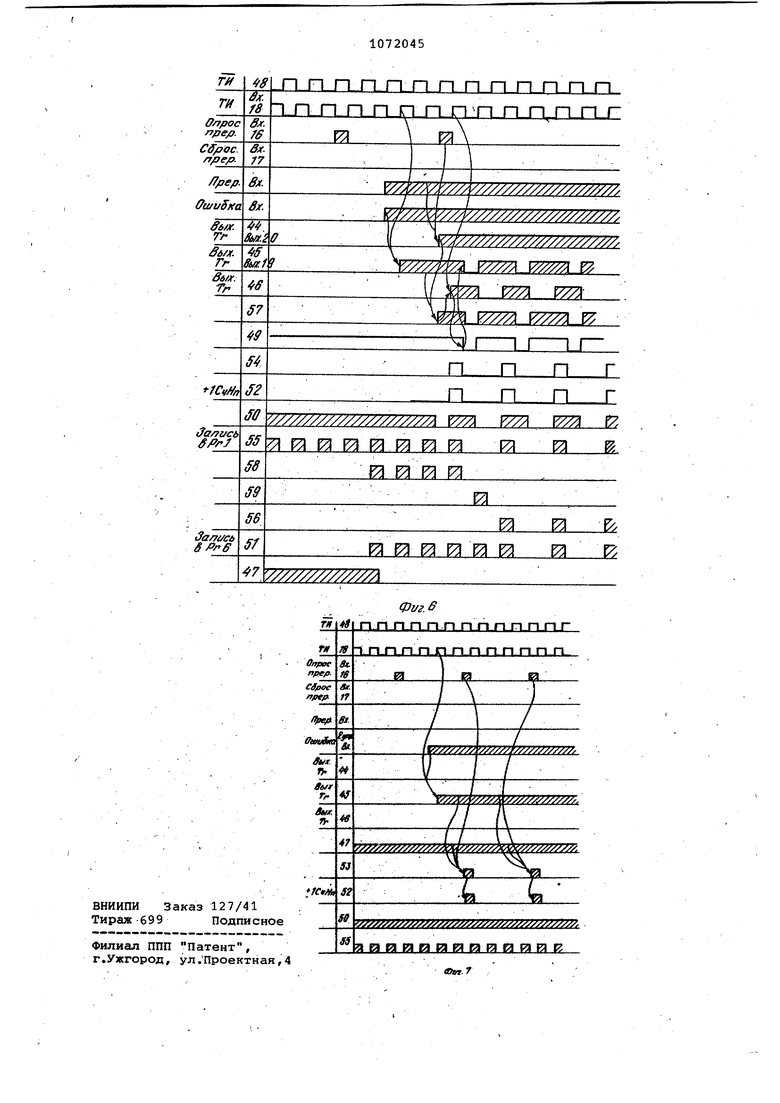

5 схем И соединены с выходами записывающего счетчика и с вторыми входами схем запрета, а выходы третьих схем И через схему ИЛИ соедине ны со счетным входом записывающего счетчика, счетный вход считывающего счетчика соединен с выходом датчика окончания обслуживания и с третьими входс ми вторых схем И l . Недостаток этого устройства - ни кая надежность. Наиболее близким к предлагаемому является устройство для прерывания {программ, содержащее Н-разрядные ре гистр прерываний и регистр маски, выходы которых соединены с соответс вующими входами узла приоритета, управляющий выход которого является выходом наличия прерывания, а информационный выход соединен с входом шифратора, выход которого является выходом кода прерывания, содержащее также узел анализа состояния регистров, дешифратор нечетности кода и схему сравнения, образующие вме сте с шифратором блок анализа .состояния устройства, причем выходы регистра прерываний подключены к соответствующим входам первой группы входов узла анализа состояния регистров, вторая группа входов которого соединена с соответствующими выходами регистра маски, а выход - с первым входом схемы сравнения, второй вход которой подключен через дешифратор нечетности кода к выхйду шифратора, выход схемы сравнения является контрольным выходом устройства 2 . Недостатком известного устройства является низкая надежность его работы, обусловленная неполным охватом контроля работы узла приоритета вследствие чего некоторый класс ояиночных ошибок в работе этого узла не выявляется контролем. Например, неисправность в цепи формирования сигнала Прерывание может привести либ к снятию сигнала Прерывание,.-либо к появлению, двух сигналов на информационном выходе узла при6|ритета. В первом случае, если прерывание относится к четной группе, оно как бы оказьшается замаскированным, а so . втором случае, если оба сигнала принадлежат к разным группам (четной , и нечетной), может привести к формированию фиктивного кода прерывания, что обусловливает неправильную работу цифровой вычислительной машины/ а именно - выполнение прерывающей программы, когда запроса прерывания не поступало, или несанкционированно включению участков программ, выполнение которых в данном режиме работы не предусмотрено, или зацикливание вызова прерывающей программы по несуществующему прерыванию. Аналогичная ситуация с появлением двух сигналов на информационном выходе узла приоритета может возникнуть в случае неисправности выходного элемента узла приоритета, если этот элемент формирует сигнал, относящийся к группе четных прерываний. Цель изобретения - повышение надежности устройства. . Поставленная -цель достигается тем, что в устройство для прерывания программ, содержащее N-разрядные регистр прерываний и регистр-маски, блок анализа приоритета прерываний, шифратор и блок анализа состояния устройства, причем выходы регистра прерываний , и регистра маски соединены соответственно с входами блока анализа приоритета прерываний, выходы которого соединены с входами шифратора, блок анализа состояния устройства содержит элемент четности, схему сравнения и элемент ИЛИ, причем выход элемента четности соединен с первым входом схемы сравнения, введены буферный регистр, регистр кода прерывания, регистр готовности, дешифратор, счетчик, элемент ИЛИ, формирователь управляющих сигналов и группа из N элементов И, а блок анализа состояния устройства дополнительно содержит второй и третий элементы четности и вторую схему сравнения, причем группа информационных входов устройства соединена соответственно с информационными входами регистра маски, регистра готовности и буферного регистра, выходы которого соединены соответственно с информационными входами регистра прерываний, выходы регистра готовности соединены соответственно с входами блока анализа приоритета прерываний и с первыми входами элементов И группы, выход блока анализа приоритета прерываний соединен с входом Прерывание формирователя управляющих сигналов, с первым входом второй схемы сравнения и с вторым входом первой схемы сравнения блока анализа состояния устройства, труппа выходов блока анализа приоритета прерываний, ототносящаяся к четным прерьаваниям, соединена соответственно с группой входов первого.элемента четности блока анализа состояния устройства и с первой группой входов шифратора, группа выходов блока анализа приоритета прерываний, относящаяся к нечетным прерываниям, соединена соответственно с группой входов второго элемента четности блока анализа состояния устройства и с второй группой входов шифратора, выходы которого соединены соответственно с информационными входами регистра кода прерывания, выходы регистра кода прерывания образуют выход Код номера преривания устройства и соединены соответственно с информационныМИ входами дешифратора и с группой входов третьего элемента четности блока анализа состояния устройства, выход которого соединен с входом Ошибка формирователя управляющих сигналов, выходы дешифраторасоединены с группой входов элемента ИЛИ и с вторыми входами элементов И группы, выходы КОТО15ЫХ соединены соответственно с входами установки в ноль буферного регистра и регистр прерываний, выход элемента ИЛИ соединен со счетным входом счетчика, выход старшего разряда которого является выходом Переход ЦВМ на ре. устройства, установочный вход устройства соединен с установочным входом счетчика, рходы Опрос преры вания, Сброс прерывания и тактовый формирователя управляющих сигналов являются одноименными входами устройства, первый и второй выходы формирователя управляющих сигналов являются соответственно выходами Неисправность устройства прерьюания программ и Прерывание устрой ства, третий, четвертый, пятый и шестой выходы формирователяуправля ющих сигналов соединены соответстве но с входом записи регистра прерыва ний, регистра кода прерывания, с управляющими входом дешифратора и с входом элемента ИЛИ, формирователь управляющих сигналов содержит D-три геры, элементы И, элементы ИЛИ, элементы НБ и э емент И-НЕ, причем вход Прерывание формирователя управляющих сигналов соединен с инфор мационным входом D-триггера с первыми входами первого и второго элементов И и с входом первого элемента НЕ, ВЫХОД которого соединен с первым входом третьего элемента И, вход Ошибка формирователя управля ющих сигналов соединен с информацион ным входом второго D-трйггера, прямой выход которого соединен с первы ми входами четвертого и пятого элементов И, с вторым входом третьего элемента И; и является выхо-. дом формирователя управляющих-сигна лов, вход Опрос прерывания формирователя управляияцих сигналов соединен с вторым входом второго элемента И, с третьим входом третьего элемента И и с тактовым входом первого D-триггера, прямой выход которого соединен с первым входсж элемента ,И-ДЕ, с вторым входом четвертого элемента И и является вторым дом формирователя управляющих, сигна лов, инверсный выход первого D-триг .гера . соединен с первым входом пер- вого элемента ИЛИ и с вторым входом первого элемента И, выход которого соединен с первым входом второго элемента ИЛИ, вход Сброс прерывания формирователя управляющих сигналов соединен с входом установки в ноль первого и третьего D-триггеров и с пятым выходом формирователя управляющих сигналов, тактовый вход формирователя управляющих сигналов соединен с тактовым входом второго и третьего р-триггеров, с вторым, входом пя,того элемента И, с первым входом шестого элемента И и с входом второго элемента НЕ, выход которого соединен с перВЕлм входом седь-. мого элемента И, с третьим входом первого элемента И и р вторым входом элемента И-НЕ, прямой выход в-триггера соединён с вторым входом первого элемента ИЛИ, вторым входом седьмого элемента И, с третьим входом пятого элемента И и с третьим входом элемента И-НЕ, выход которого соединен с входом установки в ноль второго D-триггера, выход первого элемента ИЛИ соединен с вторым входом шестого элемента И, ыход которого является третью выходом формирователя управляющих сигналов., выход второго элемента И соединен с вторым входом второго элемента ИЛИ, выхс|Д которого является четвертым выходом формирователя управляющих -сигналов, выход третьего элемента И соединен с первым входом третьего элемента ИЛИ выход которого является шестым выходом фО1ллироватёля управляющих сигналов, выход четвертого элемента И соединен с. информационым входом третьего D-триггера, выход пятого элемента.И соединен с вторым входом третьего элемента ИЛИ, выход седьмого элемента И соединен с третьим входом второго элемента ИЛИ. На фиг.1 представлена блок-схема устройства для прерывания программ; на фиг.2 - схема блока анализа состояния устройства/ на фиг.З - пример выполнения схемы блока анализа приоритета прерываний, на фиг.4 схема формирователя управляющих сигналов, на фиг.5 - врем ргная диаграмма работы устройства при поступлении запроса на прерывание / на фиг.б и 7 - временные диаграммы работы фор; мирователя управляющих сигналов при поступлении на его входы сигналов Прерывание, Ошибка и Ошибка соответственно. Устройство для прерывания программ (фиг.1) содержит регистр 1 прерываний, регистр 2 маски, блок 3 анализа приорите.та прерываний, шифратор 4, регистр 5 готовности, регистр 6 кода прерывания, дешифратор 7, буферный регистр 8, N элементов И 9, элемент ИЛИ 10, счетчик 11, формирователь 12 управляющих сигналов, блок 13 анализа состояния устройста. Убтройство имеет группу инфорационных входов 14, установочный вход 15 и управляющие входы 16 Опрос прерывания, Сброс прерывания 17, тактовый 18; а также выходы неисправность устройства прерывания программ 19, Прерывание 20, Код номера прерывания 21, Переход ЦВМ на резерв 22. Блок 13 анализа состояния устрой ства (фиг.2) содержит элементы 23-2 четности, схемы 26 и 27 сравнения и .элемент ИЛИ 28. Блок Занализа приоритета прерываний (фиг.З) содерясит элементы 2934 И и элементы 35-43 И-НЕ. Формирователь 12 управляющих сиг налов (фиг.4) содержит D-триггеры 44-46, элементы НЕ 47 и 48, элемент И-НЕ 49, элементы ИЛИ 50-52 и элементы И 53-59. Устройцтво работает следующим образом. Привилегированными командами управляющей программы по входу 14 за носятся соответственно запросы на прерывание, код маски и код готовности. Код маски определяет приоритет прерывающим программам, вызыва емым сигналами запросов на прерыва |ние, относительно выполняемой программы, причем единичное значение разряда регистра 2 соответствует разрешению прерывания при поступлеНИН соответствующего запроса. .Код готовности устройства отраж ет состояние зоны прерывания в памяти ЦВМ, в которой хранится инфор мация, -используемая при реагирован на прерь вание. . ; Единичное значение разряда ре. гистра 5 указывает, что прерывание разрешенб и в соответствующих этому разряду ячейках зоны прерывания записана метка (начальный адрес) прерываввдей программы и маска, с которой эта программа должна выполнятьс Нулевое значение регистра 5 указывает, что соответствующее 9тому разряду прерывание отменено (запреnjeHo). . Перезапись поступивших запросов из регистра 8 в регистр 1 осуществляется .по сигналу записи формирователя 12 управляющих сигналов (фиг.-5 7). Блок 3 анализа приоритета прерываний при получении содержимого регистра 1 вьщеляет сигнал прерывания с более- высоким приоритетом, ко торый определяется слева направоиз числа запросов, разрешенных соответ ственно кодом регистора 2 маски и ко дом регистра 5 готовности. В случае незамаскированного прерывания блок анализа приоритета формирует сигнал Прерывание, поступающий на вход формирователя 12 управляющих сигналов и блока 13 анализа состояния ус ройства, а также формирует унитарный код номера прерывания, который после преобразования шифратором 4 в двоичный код поступает на вход реги- стра 6 кода прерывания. Код номера прерывания передается на выход 21 устройства, на вход блока 13 анализа состояния устройства и информационный вход дешифратора 7. Контроль функционирования производится блоком 13 анализа состояния устройства параллельно с работой устройства. Для осуществления контроля прерывание разделено на две группы четные и нечетные. Разделение осуществляется по количеству единиц, содержащихся в двоичном коде номера прерывания. Контроль основан на проверке следующих условий: совпадение четности кода номера прерывания на регистре 6 с четностью, определяемой по унитарному коду блока 3, проверка четности должна совпадать с появлением Сигнала Прерывание на выходе блока 3. Элемент 2.3 четности путем суммирования по модулю 2 разрядов кода прерывания, поступающих с регистра 6, формирует четность кода номера прерывания. . Элемент 24 четности путем сумми.рования по модулю 2 формирует четность рязрядов унитар ного кода,, относящихся к нечетнымпрерываниям, поступающим из блока 3 анализа приоритета прерываний. Элемент 25 четности путем суммирования по модулю 2 формирует четность разрядов унитарного кода, относящихся к четным прерываниям, с учетом, результата, полученного при формировании четности элементом 24.. В случае неправильной работы устройства, когда на выходе блока 3 формируется .неверный унитарный код, или не формируется сигнал Прерывание, или неправильно формирует код шифратор 4, или неверно производится за.пись кода в регистр 6, нарушаются условия, проверяемые блоком 13 айаЛиза состояния устройства. При нарушении этих условий схемы 26 и 27 сравнения вырабатывают сигнал ошибки, который через элемент ИЛИ 28 поступает на выход блока 13 и формирователь 12 управляющих сигналов формирует, сигнал Неисправность устройства прерывания программ поступающий на выход 19 устройства. При отсутствии нарушений перечисленных условий, т.е. при отсутствии сигнала ошибки на выходе блока 13 . анализа состояния устройства и наичия разрешенного прерывания на выходе 20 устройства появляется сигнал Прерывание. Сигналами с выходов дешифратора 7 через группу элементов И 9 устанавлив1аются в ноль те разряды регистров 8 и 1, которые соответствуют но меру обрабатываемого прерывания«Кро ме того, сигналы с выходов дешиф-ратора 7, относящиеся к аппаратным и программным неисправностям, через элемент ИЛИ 10 подаются на вход счетчика 11, который подсчитывает число обращений к программе анализа неисправностей. Формирование сигнала неисправности прерывает выполнение программы анализа неисправности и счетчик 11 необнуляется, а через устройство прерывания программ осуществляется очередной вызов програм мы анализа неисправности и, следова тельно, добавление в счетчик 11 еди ницы. Это повторяется до тех пор, пока очередное добавление не приведет к формированию сигнала переполнения счетчика 11 и появлению на вы ходе 22 устройства сигнала, по которому осуществляется переключение, цифровой вычислительной машины на резерв. После выяснения и устранени причины неисправности по входу 15 устройства счетчик 11 устанавливает ся в исходное состояние. Блок 3 анализа приоритета прерываний работает следующим образом. Сигналы о состоянии регистра 1 . прерываний, регистра 2 маски и регистра 5 готовности поступают на элементы И 29-32 и И-НЕ 35-38,где осуществляется их поразрдцное логическое умножение. ч На элементах 33,34 и 39 формируется сигнал Прерывание, а на элементах И-НЕ 40-43 осуществляется формирование унитарного кода номера прерывания. При одновременном поступлении нескольких сигналов запроса на прерывание блок 3 анализа приоритета выделяет сигнал прерывания с наиболее высоким приоритетом, который, определяется слева направо из числа запросов, разрешенных соответственно сигналами с регистра 2 маски и регистра 5 готовности. Работа формирователя12 управляю щих сигналов поясняется временным диаграммами (фиг.б и 7) и определяется сигналами Ошибка и Прерывание, поступающими на одноименные входы формирователя, а также управЛЯЮ.ЩКМИ сигналами Опрос прерьтвания (вход 16) и Сброс прерывания (вход 17), сопроволщаемых тактовыми импульсами, поступающими на вход 18 Формирователь 12 управляющих сигналов обеспечивает выработку, сигнала: Прерывание, вьщаваемого с .-единичного плеча триггера 44 на выход 20, выдача сигнала осуществляет ся по переднему фронту сигнала Опр прерывания при поступлении сигнала Прерывание с выходаблока 3 анали за приоритета прерываний, сигнала Неисправность устройства прерывания программ , выдаваемого с единичн ного плеча триггера 45 на выход 19, выдача сигнала осуществляется по переднему фронту тактового импульса при поступлении с выхода блока 13 анализа состояния устройства сигнала Ошибка, сигналов записи в регистр 1 прерываний (с выхода элемента И 55) записи в регистр 6 кода прерывания (с выхода .элемента ИЛИ 51),управления дешифратором 7 (одновременно с установкой в ноль триггеров 44 и 46), и сигнала -fl на счетчик 11 (с вы- хода элемента 52 ИЛИ). Формирование Сигнала записи в регистр 1 прерываний осуществляется на элементах ИЛИ 50 и ИГ55, когда триггер 46 находится в единичном состоянии или триггер 44 - в нулевом состоянии. Формирование сигнала записи в регистр б кода прерывания ос5таествляется на элементе И 59 при совпадении сигналов Опрос прерывания и Прерывание, поступающих на входы формирователя управляющих сигналов,или элементах И 58 и 56 при снятии тактовых импульсов, когда триггер 46 находится в нулевом состоянии, а на вход формирователя поступает .сигнал Прерывание, а также когда триггер 46 находится .в единичном состоянии. Сформированные на элементах И 59, 58 и 56 сигналы через йлемевт ИЛИ 51 поступают на четвертый выход блока.Формирование сигнала +1 счетчику 11 осуществляется на элементе И 54 по сигналу тактового импульса, когда триггеры 45 и 46 находятся в единичном состоянии, или на элементе И 53 по сигналу Опрос прерывания, когда триггер 45 находится в единичном состоянии, а на вход формирователя Прерывание сигнал не поступает. Сигналы с элементов И 54 и 53 через элемент ИЛИ 53 поступают на шестой выход формирователя 12 управляющих сигналов. По сигналу Сброс прерывания, поступающего на вход 17, триггеры 44 и 46 устанавливаются в нулевое состояние, а в-цепь управления дешифратором по пятому выходу вьвдается сигнал. Таким образом, путем увеличения. полноты контроля устройства повысилась его надежность того, расширились функциональные возможности устройства за счет сброса признака прерывания при его отмене или по окончании реакции на прерывание, а также за счет формирования сигнала, который может бнть использован для переключения ЦВМ на |: еэерв.

V7-/

f

iTJT n4TJTj-%jTjtJTjn rTJTri

TJT|JTjrtj /TJUT,,

e

in.

M/ V jCMy jW yjMMK.

ЕЯ 0

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| УСТРОЙСТВО для ОБРАБОТКИ ЗАПРОСОВ С КОНТРОЛЕМ ОЧЕРЕДНОСТИ | 0 |

|

SU350005A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для прерывания программ | 1978 |

|

SU744575A1 |

Авторы

Даты

1984-02-07—Публикация

1982-04-28—Подача