(54) УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ИНФОРМАЦИИ О КОМПЛЕКТОВАНИИ ПАРТИИ ДЕТАЛЕЙ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обработки информации о комплектовании партии деталей | 1986 |

|

SU1425718A1 |

| Устройство для сортировки деталей на группы | 1987 |

|

SU1418758A1 |

| Устройство для сортировки | 1989 |

|

SU1633428A1 |

| Устройство для обработки информации о комплектовании пар деталей | 1982 |

|

SU1080150A1 |

| Устройство для сортировки | 1986 |

|

SU1322319A1 |

| Устройство для контроля параметров | 1990 |

|

SU1728869A1 |

| Устройство для сортировки | 1982 |

|

SU1084816A1 |

| Устройство для моделирования систем массового обслуживания | 1981 |

|

SU962970A1 |

| Многоканальное устройство для сопряжения источников информации с вычислительной машиной | 1986 |

|

SU1381523A2 |

| Многоканальное устройство для сопряжения | 1985 |

|

SU1282142A1 |

1

Изобретение относится к вычислительной технике и может быть использовано для обработки информации при реализации технологического процесса однопарамет- рического селективного кся плектования деталей.

Известно устройство для обработки информации о комплектовании партии деталей, содержащее агрегаты кзмерения, преобразователь аналоговых значений в цифровые, вь1числительное устройство для оценки ожидаемых параметров, схему сравнения с контрольными значениями, память ва магнитных дисках, печатаи щее устройство Cl .

Данное устройство не позволяет оп твмапьвым образам комплектовать партии деталей.

Наиболее близким к предлагаемому по технической сушности является устройство, содержащее элементы И и ИЛИ, счетчик, регистры, электропривс д, вход которого подкгаочен к первому выходу блока упр 1вления, а выходы соединены

соответственно с входами блока сепек-. ции и преобразователя числа оборотов в импульсы, выход которого соединен с первым входом блока управления, входы счетчика подключены к второму и третьему вьгходам блока управления и «ходам датчика чисел, а выходы - к второму входу блока управления и одним входам элементов И, другие входы которых через, первые элементы ИЛИ соединены

10 с выходами блока селекции, выходы перрвого регистра подключены к второму выходу блока управления и выходам элементов И, входы второго регистра ср&дввевы с третьим и четвертым выходами

«5 блока управления, а выходы регистров через вторые элементы ИЛИ соединены с. входами блока индикации и непосредственно выход второго регистра - с третьим входом блока управления, выхо-

20 ды элементов И п шключеньт к четвертсжсу входу блока управления 2 }

Недостатки известного устройства I является большое число механических 3 1 эпементов и неоптимальное составление комплектов, что ведет к низкой надежности и большому объему незавершенного производства. Цель изобретения - повышение надеж- носги и сокращение непроизводительных з затрат времени. Поставленная цель достигается тем, что в устройство, содержащее счетчик, регистр, И, ИЛИ, блок вывода данных на печать, введены сумматор, четыре блока памяти, элементы задержки, переключатель, дешифратор, схема сравнения и генератор тактовых импульсов, первый выход которого соединен с первым входом первого элемента И, второй выход - подключен к первым входам второго и третьего элементов И, третий выход подключен к первому входу четвертого элемента И, четвертый выход генератора тактовых импульсов соединен с первыми входами первого и второго эл ментов ИЛИ и с вторым входом третьего элемента И, вход первого элемента НЕ и вторые входы первого, второго и чет- вертого элементов И че{юз переключател соединены с источником питания, третий вход третьего элемента И соединен с выходом первого элемента НЕ, выход первого элемента И соединен с входами считывания с первого по четвертый блоков памяти, группы инфор«(ационны}1: входов первого и второго блоков памяти яв ляются соответственно первой и второй группами информационных входов устройства, выход второго элемента И подключен к первым входам пятого и шестого элементов И и к управляющему входу блока вывода данных на печать, выход третьего элемента И соединен с первым входами третьего и четвертого элементо ИЛИ и с входами записи первого и втор го блоков памяти, выход четвертого эле мента И соединен с первыми входами седьмого и восьмого элементов И и с втор.1м входом второго элемента ИЛИ, выход которого подключен к счетному входу счетчика, выходы которого соединены с входами дешифратора и с первой группой входов схемы сравнения, выход которой соединен с вторым входом первого элемента ИЛИ, выход которого под ключен к тактовому входу регистра, вто рые входы шестого и седьмого элементов И и вход второго элемента НЕ подключены к выходу знакового разряда сумматора, выход второго элемента НЕ подключен к вторым входам пятого и восьмого элементов И, выход пятого эле 124 ента И соединен с вторыкт входом третьего элемента ИЛИ, выход шестого элемента И соединен с вторым входом четвертого элемента ИЛИ, шиход которого соединен с входом первого элемента задержки и с первыми входами элементов И группы, входы которых соединены соответственно с выходами четвертого блока памяти, выход третьего элемента ИЛИ соединен с входом второго элемента зе держки и с первыми входами элементов И второй группы, вторые входы которых соединены соответственно с выходами третьего блока памяти, выход седьмого элемента И подключен к установочному входу четвертого блока памяти, выход восьмого элеменга И соединен с с установочным входом третьего блока памяти, вторая группа входов схемы сравнения соединена с выходами второго блока памяти, установочные входы счетчика соединены соответственно с выходами первого блока памяти, выхо.ды регистра подключены соответственно к управляющим входам первого, второго и третьего блоков памяти и к пе{жой группе входов блока вывода данных на печать, дешифратора подключены соответсгвенно к управляющим входам четвертого блока памяти и к второй группе входов блока вывода данных на печать, третья группа входов которого соединена с выходами элементов ИЛИ первой группы, входы которых соединены соответственно с выходами элементов И первой и второй групп, входы сумматора соединены . соответственно с выходами третьего и четвертого блоков памяти, информационные выходы сумматора соединены соответственно с первыми входами элементов ИЛИ второй и третьей групп, вторые входы элементов ИЛИ второй группы являются третьей группой информационных входов устройства, вторые входы элементов ИЛИ третьей группы являются четвертой группой, информационных входов устройства, информационные входы третьего блока памяти соединены соответственно с выходами элементов ИЛИ второй группы, вход записи подключен к выходу первого элемента задержки, информационные входы четвертого блока памяти соединены соответственно с выходами элементов ИЛИ третьей группы, вход записи подключен к выходу второго элемента задержки. На фиг. 1 изображена схема устройства; на фиг. 2 - диаграмма, поясняющая принцип оптшу1ального комплектования.

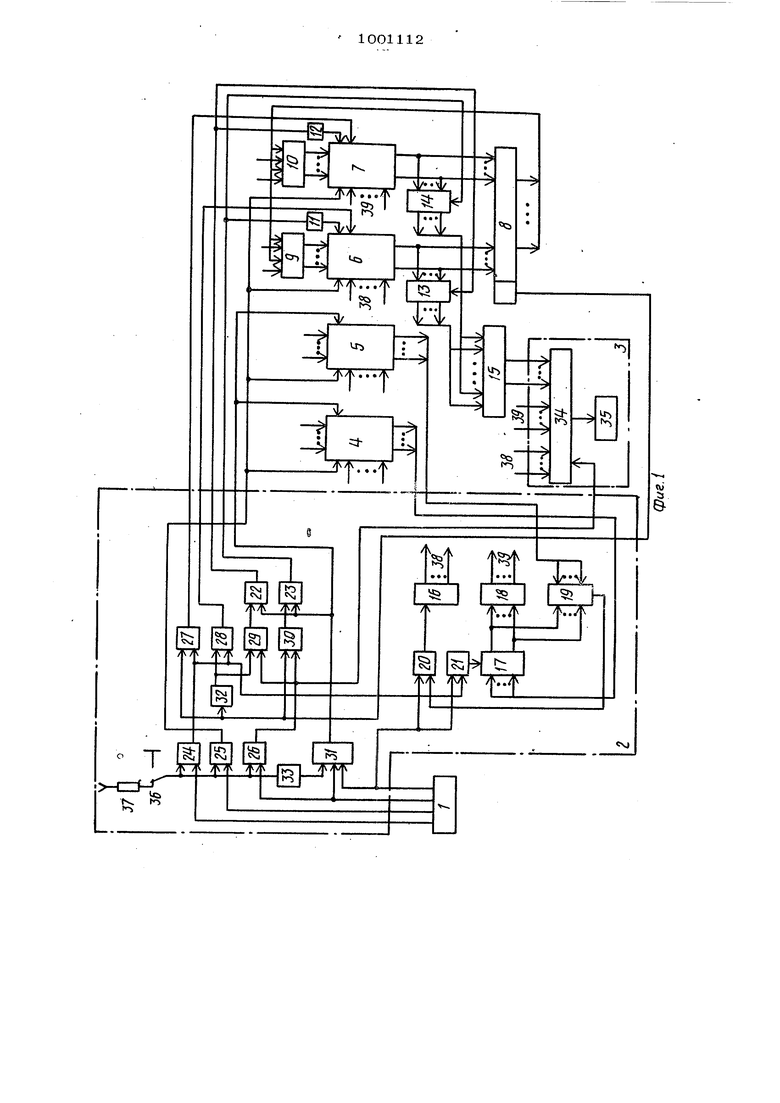

Устройство содержит генератор 1 тактовых импульсов, блок 2 управления, блок 3 вывода данных на печать, блоки 4-7 памяти, сумматор 8, группы 9 и 10 элементов ИЛИ, элементы 11 и 12 задержк группы 13 и 14,элементов-и, группу 15 элементов ИЛИ, регистр 16, счетчик 17 дешифратор 18, схему 19 сравнения, эле менты 2О - 23 ИЛИ, элементы 24 - 31 И, элементы 32 и 33 НЕ, узел 34 управления ци фопечатью, цифропечать 35, переключатель 36, источник 37 питания, линии 38 и 39 связи. В блоке 4 памяти хранятся величины минимального допуска, в блоке 5 - вел№ чины максимального допуска, в блоке 6 число деталей первого вида и в блоке 7 число деталей второго вида. Работа устройства обработки информации о комплектовании партии деталей по- ясняется фиг. 2. Каждая группа 1 деталей А имеет определенное количество де талей Oj , аналогично каждая группа j деталей В имеет определенное количеств деталей Ъ . Ограничения, накладьтаемые на комплектацию, представлены выделенными ступенчатыми линиями ч.а верхняя граница, п, - нижняя. В приведенном случае ограничения линейные, так как ,j -nf const, в общем случае . . Комплектация начинается с i 1, где ctj 10, которая может соединяться с деталями вида В по группам } 1 и j 2, в которых соответственно при и при Ь2 4 видно, что детали соберутся только при гДб будет остаток, который используется при комплектации деталей О1з 9. Таким образом, просматривается каждый столбец ct в пределах ограничений и В результате получаем оптимальную с точки зрения максимально возможного числа комплектов комплектовочную таблицу. На фиг. 2 это числа деталей, необходимых для комплектования в пересечении строк И столбцов. Устройство работает следующим образом. Сначала производится загрузка блоков памяти. Для этого переключатель 36 устанавливается в такое положение, кото рое приводит к блокировке элементов И И 24 - 26 и разрешает работу элемента И 31. Генератор 1 формирует три тактовые последовательности, которые сдви нуты на треть периода по отношешпо друг к другу, и одиночные импульсы. Последние используются при вводе ..

100111 «

формации в устройство. При его наличии регистр 16 устанавливается в положение А1, счетчик 17 - в такое, что на выходе дешифратора 18 будет выход В1,.а тактовые импульсы, пройдя через схемы 31, 32 и 23, поступают на входы записи блоков памяти, что приводит к записи информации, установленной на входах. Аналогично при повторном импульсе ТИ4 произойдет запись данных по регистрам А2, В2 и т.д. При переводе переключателя в другое положение устройство переходит в режим обработки информации. Блокируется элемент И 31, производится установка в исходное состояние рзегистрю 16 и счетчика 17 (установочные цепи не показаны). Тактовый импульс с элемента 24 производит считывание информации из регистров А1, В1 блоков 4 - 7. На сумматоре осуществляется вычитание и, если знак результата положителен, то сигнал знакового разряда блокирует элементы И 28 и 29 через элемент НЕ 32 и разрешает прохождение тактовых импульсов чер)ез элементы И 27 и ЗО. Тактовый импульс второй последовательности, пройдя через элементы И 30 и ИЛИ 23, разрешает прохождение данных через элемент И 13 на элемент ИЛИ 15 и на вход узла 34 управления цифропечатью. Зтот же галпульс пройдя чер)ез элемент 11 задер1жки, дает разрешение записи результата вычитания в регистр А1 блока 6. Тактовый импульс третьей последовательности, пройдя черюз элемент И 27, произведет обнуление регистра В1 блсиса 7 памяти и произведет добавление единицы в счетчик 17. Если знак суммы отрицательный, то блокируются элементы И 27 и 30 и разрешается прохождение импульсов чер)ез элементы И 28 и 29. Дальнейшая работа устройства аналогична вышеизложенной с той разницей, что обнуляется соответствующий регистр А, р езультат суммы переписывается в регистр блока 7 памяти. Синхронно с этим происходит -вывод на цифропечать 35. Увеличение счетчика 17 происходит до тех пор, пока содержимое счетчика не станет больше верхней границы допуска, что выявляет схема 19 сравнения и не дает сигнал на сдвиг регистра 16. Это приводит к анализу новой группы . Использование предлагаемого изобрюгения позволяет повьсить гтяцежность. сшюить объем незавершенного производства и усжорить процесс составления про граммы комплектования по сравнению с i известными устройствами в 3,5 5 раз. Формула изобретения Устройство для обработки информации о комплектовании партии деталей, содержащее счетчик, регистр, элемент И, ИЛИ блок вывода данных на печать, отличающееся тем, что, с целью повышения надежности и сокращения непроизводительных затрат времени, в нэго введены сумматор, четыре блока памяти, элементы задержки, переключатель, дешифратор, схема сравнения и генератор тактовых импульсов, первый выход которого соединен с первым входомПервого элемента И, второй выход подключен к первым входам второго и третьего элементов И, третий выход подключен к пер вому входу четвертого элемента И, четвертый выход генератора тактовых импульсов соединен с первыми входами первого и второго элементов ИЛИ и с вторым входом третьего элемента И, вход первого элемента НЕ и вторые входы первого, второго и четвертого элементов И через переключатель соединены с иоточником ПИ1ания, третий вход третьего элемента И соединен с выходом первого элемента НЕ, выход первого элемента И соединен с входами считывания с перво го по четвертый блоков памяти, группы информационных входов первого и второг блоков памяти являются соответственно первой и второй группами информационны входов устройства, выход второго элеме та И подключен к первым входам пятого и шестого элементов И и к управляющему входу блока вывода данных на печать выход третьего элемента И соединен с пернЕШи входами третьего и четвертого элементов ИЛИ и с входами записи первого и второго блоков памяти, выход четвертого элемента И соединен с первы ми входами седьмого и восьмого элемен И и с вто{я 1м входом второго элемента ИЛИ, выход которого подключен к счетному входу счетчика, выходы которо соединены с входами дешифратора и с первой группой входов схемы сравнения. выход которой соединен с вторым входом первого элемента ИЛИ, выход которого подключен к тактовому входу регистра, вторые входы шестого и седьмого элеме тов И и вход второго элемента НЕ подключены к выходу знакового разряда сумматора, выход второго элемента НЕ подключен к вторым входам пятого и восьмого элементов И, выход пятого элемента И соединен с вторым входом третьего элемента ИЛИ, выход шестого элемента И соединен с вторым входом четвертого элемента ИЛИ, выход которого соединен с входом первого элемента задержки и с первыми входами элементов И первой группы, вторые входы которых соедине№1 соответственно с выходами четвер того блока памяти, выход третьего элемента- ИЛИ соединен с входом второго элемента задержки и с первыми входами элементов И второй грзтшы, вторые входы которых соединены соответственно с выходами третьего блока памяти, выход седьмого элемента И подключен к установочному входу четвертого блока памяти, выход восьмого элемента И соединен с установочным входом третьего блока памяти, вторая группа входов схемы сравнения соединена с выходами второго блока памяти, установочные входы счетчика соединены соответственно с выходами первого блока памяти, выходы регистра подключены соответственно к управляюшим входам первого, второго и третьего блоков памяти и к первой грутше входов блока вывода данных на печать, выходы дешифратора подключены соответственно к управляющим входам четвертого блока памяти и к второй группе входов блока вывода данных на печать, третья группа входов которого соединена с выходами элементов ИЛИ первой группы, входы которых соединены соответственно с выходами элементов И первой и второй групп, входы сумматора соединены соответстве но с выходами третьего и четвертого блоков памяти, информационные выходы сумматора соединены соответственно с первыми входами элементов ИЛИ второй группы ми входами элементов ИЛИ второй и треть ей групп, вторые входы элементов ИЛИ второй группы являются третьей группой информационных входов устройства, вторые входы элементов ИЛИ третьей грутьпы являются четвертой группой информационных входов устройства, информадиот ные входы третьего блока памяти соединены соответственно с выходами элементов ИЛИ второй группы, вход записи подключен к выходу первого элемента задержки, информационные входы четвертого паМяти соединены соответственно с выходами элементов ИЛИ третьей груть9i6oiii210

пы, вход записи подключен к выходу . Патент США № 346212,

рого элемента задержки.кл. G Об F 15/46, рпублнк. 1976.

Источтпси информапии,№ 648975, кл. Q Об F 7/ОО, 1977

принятые во внимание при, акспертизе S (прототип).

2« Авторское свидетельство СССР

Авторы

Даты

1983-02-28—Публикация

1981-09-28—Подача