(5) ЧАСТОТНО-ФАЗОВЫЙ ДИСКРИМИНАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 1991 |

|

RU2040852C1 |

| Частотно-фазовый дискриминатор | 1980 |

|

SU936376A1 |

| Устройство тактовой синхронизации | 1986 |

|

SU1411990A1 |

| Селектор пачки импульсов | 1979 |

|

SU813751A2 |

| АДАПТИВНЫЙ ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 2000 |

|

RU2166773C1 |

| Частотно-фазовый дискриминатор | 1984 |

|

SU1182625A1 |

| Импульсный частотно-фазовый детектор | 1987 |

|

SU1580524A1 |

| Устройство для синхронизации канала воспроизведения данных | 1989 |

|

SU1674245A1 |

| ДЕМОДУЛЯТОР СИГНАЛОВ С ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 1995 |

|

RU2076458C1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1992 |

|

RU2012014C1 |

1

Изобретение относится к радиотехнике и автоматике и может быть использовано в устройствах автоподстройки частоты и фазы.

Известны частотно-фазовие дискриминаторы, содержащие триггеры и логические схемы 1 и 2.

Однако уровень выходного сигнала этих дискриминаторов в случае малой частотной расстройки мал или качественные показатели фазового режима недостаточно высоки,

Наиболее близким к предлагаемому является частотно-фазовый дискриминатор, содержащий два основных и два вспомогательных триггеры, попарно соединенные тактовые входы которых являются входами дискриминатора, а прямые выходы триггеров - основными выходами дискриминатора, причем основные выходы основных триггеров соединены с информационными входами вспомогательных триггеров в каждой

паре и через элемент И-НЕ сR-входами основных триггеров ЗЗ

Однако известный диc фи 1инaтop обладает недостаточной точностью дискриминаций в случае малой частотной расстройки из-за чего снижается быстродействие устройств, использующих этот дискриминатор, и отсутствие входов управления работой дискриминатора ,

10

Цель изоб|эетения - повышение точности при одновременном расширении возможности управления работой устройства.

Поставленная цель достигается тем,

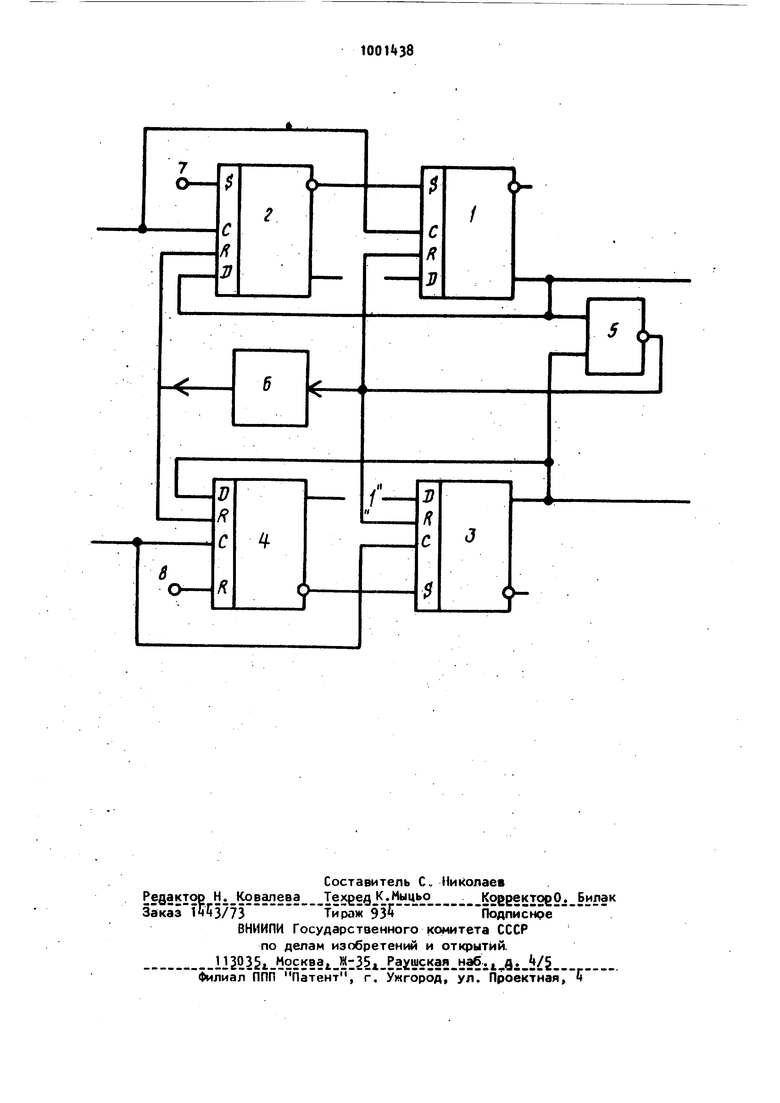

15 что в частотно-фазовый дискриминатор, содержащий четыре триггера, тактовые вхОды первого и второго из которых соединены с первой входной шиной, тактовые входы третьего и чет(зер-того 20с второй входной шиной, а прямые выходы первого и третьего триггеров соединены непосредственно с информационными входами СООТВСТС1 веинг) пторого и четвертого триггеров и через элемент И-НЕ с R-входами первого и третьего триггеров, введен элемент задержки, вход которого подключен к выходу элемента И-НЕ, а выход - к р.-входам второго и четвертого триггеров, инверсные выходы которых подключены соответственно к S-входам первого и третьего триггеров, аS-вх ды - к дополнительным управляющим ши На чертеже приведена структурная электрическая схема предлагаемого дискриминатора. Дискриминатор содержит триггеры I-, элемент И-НЕ 5, элемент 6 задержки, дополнительные управляющие шины 7 и 8„ Входные сигналы подаются на спаренные тактовые входы триггеров, выходные сигналы снимаются с прямых выходов триггеров 1 и 3 и (или прямых выходов триггеров 2 и k), На управляющие шины 7 и 8 пода ются сигналы управления работой диск риминатора „ Дискриминатор работает следующим образом с Дискриминатор имеет два режима работы: режим сравнения частот и режим сравнения фаз Переход от режима сравнения частот к режиму сравнения фаз происходит автоматически при сближении входных частот Первый входной сигнал подается на тактовые входы триггеров 1 и 2, второй на тактовые входы триггеров 3 и „ Фазовый режим имеет место тогда, когда на э-входах триггеров 1 и 3 действуют разрешающие уровни: .единицы записываются в триггеры строго попеременно (входные частоты должны быть равны}, причем триггеры сбрасываются элементом И-НЕ как только случается, что в обоих триггерах записаны единицы о В зависимости от зна ка разности фаз входных сигналов вырабатываются импульсы, ширина которых пропорциональна разности фаз, на выходах одного или другого три|- геров 1 и Зе Триггеры 2 и ( находятся в состоянии нулей, так как в момент действия тактовых импульсов содержание соответствующих триггеров 1 и 3 тоже нули., В случае повышения частоты первого входного сигнала, действующего на ТЧктовых входах триггеров 1 и 2, инверсный выход триггера 2 поддсрживает триггер 1 в состоянии единицы. Аналогично в случае повышения частоты сигнала, действующего на тактовых входах триггеров 3 и 4, триггер 3 поддерживается в состоянии единицы триггером l, Это режим сравнения частот. Например, в случае повышения частоты первого входного сигнала обязательно наступает состояние, при котором между двумя тактовыми импульсами второго входного сигнала присутствуют два тактовых импульса первого сигнала - первый импульс записывает единицу в триггер 1, второй переписывает ее в триггер 2, что в свою очередь фиксирует триггер 1 в состоянии единицы поЗ-вхрдуо После этого тактовый импульс второго сигнала записывает единицу в триггер Зо Однако этот триггер сразу сбрасывается, импульс сброса на выходе элемента И-НЕ заканчивается, а триггер 1 остается фиксированным в состоянии единицы Импульс сброса задерживается в элементе задержки на время действия сброса на триггеры 1 и 3 Импульс сброса с выхода элемента задержки действует на триггеры 2 и t и сбрасывает триггер 2 из состояния единицы в состояние нуля Однако состояние единицы в триггере 1 сохраняется благодаря наличию элемента задержки„ Это состояние сбрасывается только тогда, когда частота второго входного сигнала становится выше частоты первого входного сигнала При работе дискриминатора в системе автоподстройки частоты расстройка между входными частотами уменьшается под действием обратной связи После смены знака частотной расстройки, т.е., когда частота второго входного сигнала становится чуть выше частоты первого входного сигнала, между двумя тактовыми импульсами первого входного сигнала появляются два тактовых импульса второго входного сигналаi. Первый импульс записывает единицу в триггер 3 после чего триггеры 2 и 3 сбрасываются вышеописанным образом. Второй импульс повторно записывает единицу в триггер 3 после чего триггеры 1 и 3 сбрасываются, и дискриминатор оказывается переключенным для работы в фазовом режиме Сигналы на управляющие входы 7 и 8 подаются, например, с целью торможения работы дискриминатор; или фиксирования его состояния в одном из двух состояний частотного режима. При подаче на управляющую шину 7 уровня, переключающего триггер 2 в состояние единицы, триггер 1 тоже фиксируется в состоянии единицы по 5-входу. В случае использования упра ляющей шины 8 в состоянии единиц фиксируются триггеры и 3Введение дополнительных управляющих шин дискриминатора, подключенных к 9-входам триггеров 2 и , обеспечи вает возможность управления работой дискриминатора, обеспечивает дополнительные функциональные возмож ности при его использовании Введение элемента задер : ки, вход которого подключен к выходу элемента И-НЕ, а выход - кЯ-входам триггеров 2 и , инверсные выходы которых подключены соответственно к S-вх дам триггеров 1 и 3, обеспечивает в случае малой частотной расстройки выходной.,CVIгнал дискриминатора таког же уровня, как и в случае большой ра стройки, т.е. повышает точность частотной дискриминации. Благодаря этом повышается быстродейсГвие устройств, использующих частотно-фазовый дискри минатор. Формула изобретения Частотно-фазовый дискриминатор, содержащий четыре триггера, тактовые входы первого и второго из которых соединены с первой входной шиной, тактовые входы третьего и четвертого - с второй входной шиной, причем прямые выходы первого и третьего Уриггеров соединены непосредственно с информационными входами соответственно второго и четвертого триггеров,и через элемент И-НЕ с R-входами первого и третьего триггеров, отличающийся тем, что, с целью повышения точности при одновременном расширении возможности управления работой дискриминатора, введен элемент задержки, вход которого подключен к выходу элемента И-НЕ, а выход - кК -входам второго и четвертого триггеров, инверсные выходы которых подключены соответственно к 5 Входам первого и третьего триггеров, а 5-входы - к дополнительным управляющим шинам. Источники информации, принятые во внимание при экспертизе К Патент США № 3(3, кл, 307-232, 1973 2, Патент США № , кл, 331-1А, 1978„ 3, Electronic Design News, v, 21, №17, с„ 55-59.

в

«

f

О

Авторы

Даты

1983-02-28—Публикация

1981-07-20—Подача