(54) ЧАСТОТНО-ФАЗОВЫЙ ДИСКРИМИНАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Частотно-фазовый дискриминатор | 1981 |

|

SU1001438A1 |

| Фазовый дискриминатор | 1986 |

|

SU1334355A1 |

| ЧАСТОТНО-ФАЗОВЫЙ ДЕТЕКТОР | 2006 |

|

RU2300170C1 |

| Цифровой частотно-фазовый дискриминатор | 1983 |

|

SU1117824A1 |

| Синтезатор частот | 1985 |

|

SU1363457A1 |

| ЭЛЕКТРОПРИВОД | 2003 |

|

RU2260897C2 |

| Частотно-фазовый детектор | 2019 |

|

RU2721416C1 |

| ЭЛЕКТРОПРИВОД | 2005 |

|

RU2302073C1 |

| Многоканальное устройство для контроля параметров | 1987 |

|

SU1444714A1 |

| УСТРОЙСТВО ДЛЯ АВТОМАТИЧЕСКОЙ БАЛАНСИРОВКИ РЕЗОНАТОРА ТВЕРДОТЕЛЬНОГО ВОЛНОВОГО ГИРОСКОПА ЛУЧОМ ЛАЗЕРА | 1993 |

|

RU2079107C1 |

1

Изобретение относится к радиотехнике и автоматике и может быть использовано в устройствах автоподстройки частоты и Фазы.

Известен частотно-фазовый дискриминатор, содержащий логические схемы и триггеры l .,

Однако этот дискриминатор не обеспечивает достаточный уровень выходного сигнала в случае малой частотной расстройки.

Наиболее близким к данному изобретению по технической сущности является частотно-фазовый дискриминатор, содержащий пять схем И-НЕ, фазовый и jj два блокирующих триггера, в котором входы фазового триггера подключены к входам дискриминатора и к входам двух схем И-НЕ, к вторым входам кото рых подключены соответственно основ- 20 ной и инверсный выходы фазового триггера, а к выходам - входы установки нуля блокировочных триггеров и по одному входу третьей схемы И-НЕ. Инверсные выходы блокировочных триггеров соединены с их входами установки единицы через ту же схему И-НЕ, а основные выходы соответственно - с первыми входами четвертой и пятой схем И-НЕ, при этом второй вход пятой схемы И-НЕ соединен с выходом четвертой схемы И-НЕ, второй вход которой подключен к инверсному выходу фазового триггера 2.

Этот дискриминатор характеризуется недостаточной точностью, обусловленной влиянием длительности импульсов входных серий, а также отсутствием входов управления работой.

Цель изобретения - повышение точности дискриминатора и обеспечение возможности управления дискриминатором .

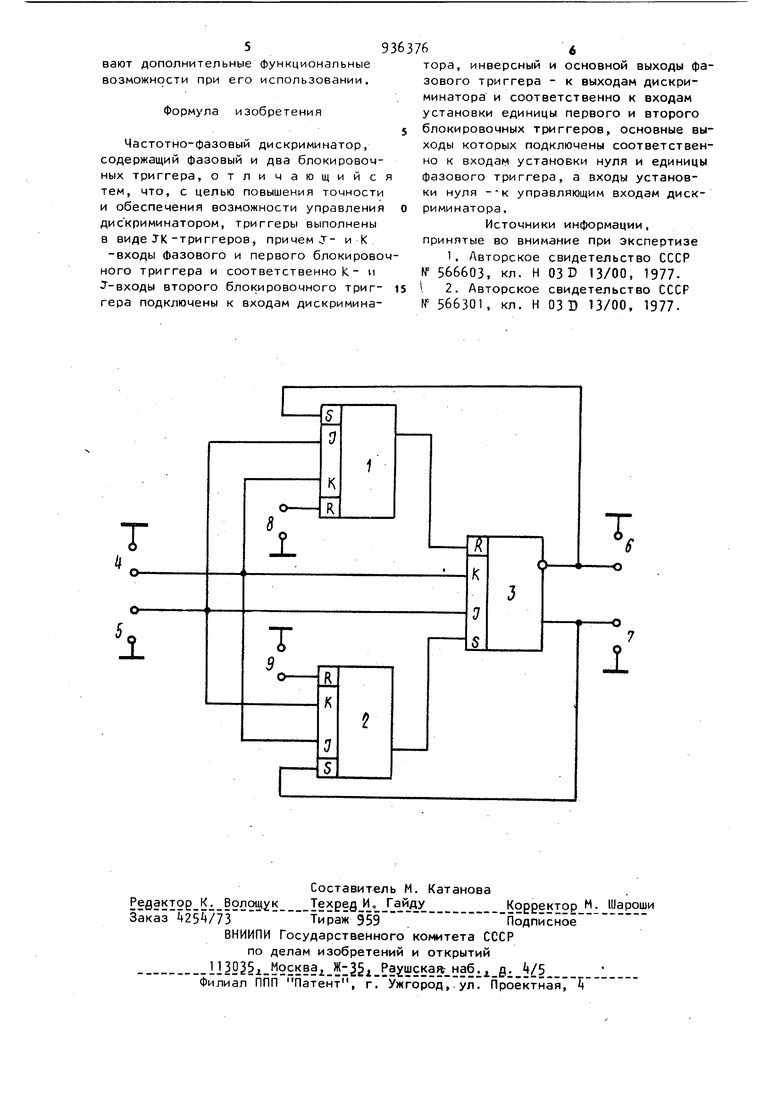

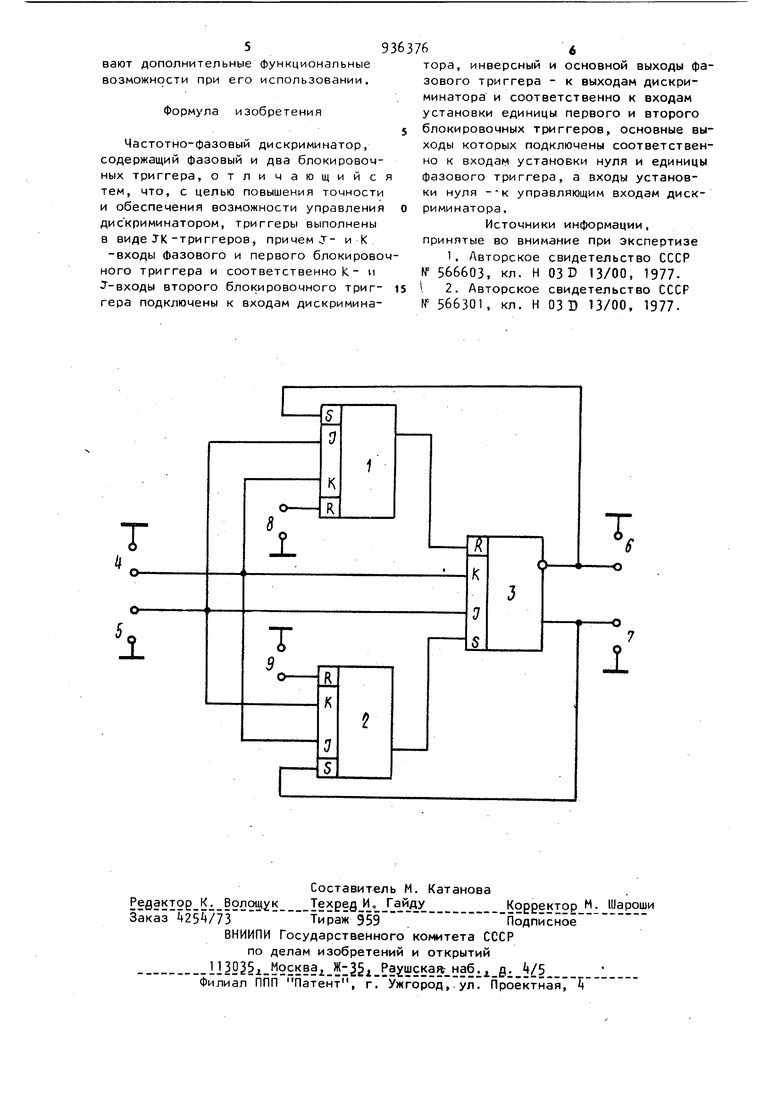

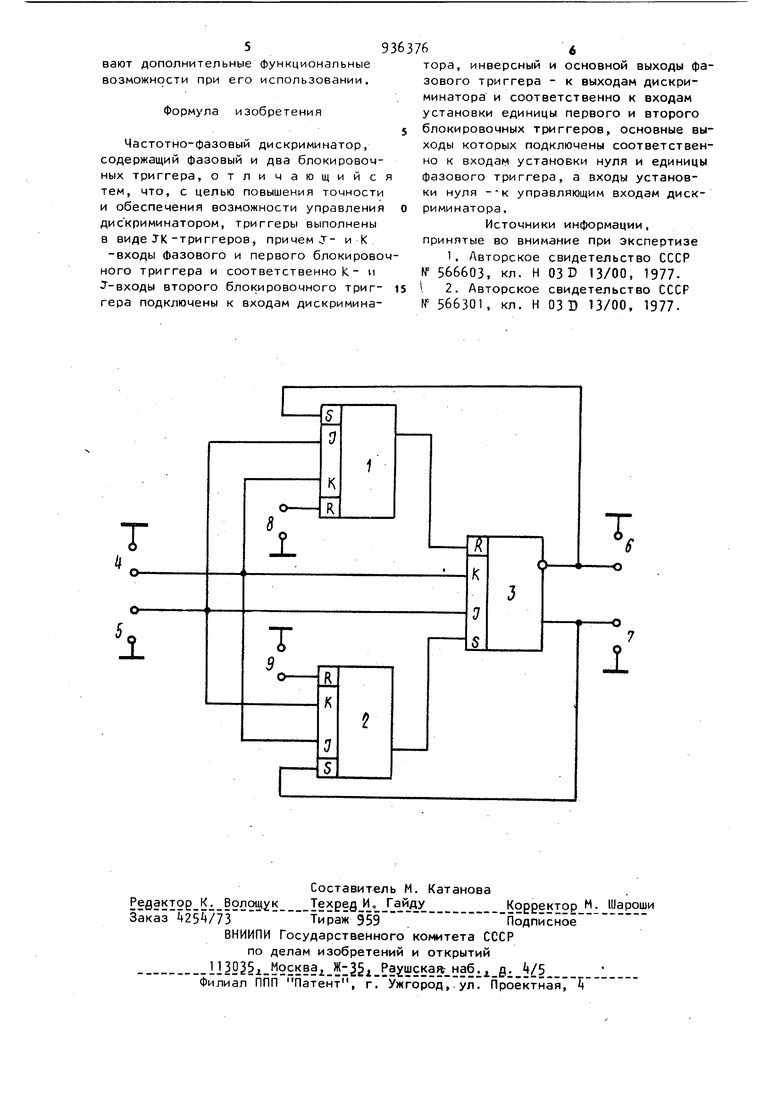

Поставленная цель достигается тем, что в 4acTofно-фазовом дискриминаторе, содержащем фазовый и два блокировочных триггера, триггеры выполнены ввиде Л К-триггеров, причем J и входы фазового и первого блокировочного триггера и соответственно К - и J - входы второго блокировочного триггера подключены к входам дискоиминатора, инверсный и основной выход фазового-триггера - к выходам дискри минатора и соответственно к входам установки единицы первого и второго блокировочных триггеров, основные вы ходы которых подключены соответствен но ко входам установки нуля и единицы фазового триггера, а входы установки нуля - к управляющим входам дискриминатора, Аа чертеже приведена принципиальнал электрическая схема дискриминатораДискриминатор содержит триггеры 1-3, первый и второй блокировочные и фазовый триггеры соответственно. Н входы и 5 подаются сравниваемые сигналы, выходные сигналы снимаются с выходов 6 и 7- На управляющие вхоДы о и 9 можно подать сигналы управления дискриминатором. Принцип работы дискриминатора заключается в следующем. Дискриминатор имеет два режима ра боты: режим сравнения частот и режим сравнения фаз. Переход от режима сравнения частот к режиму сравнения фаз происходит автоматически при сближении входных частот. Фазовый ре жим имеет место тогда, когда на входах установки единицы и нуля триггера 3 действуют разрешающие уровни дискриминатор работает как триггерный фазовый дискриминатор. В случае повышения частоты сигнала, действующего на входе 4, основной выход триг гера 1 поддерживает триггер 3 в состоянии нуля ( на основном выходе). Аналогично, в случае превышения частоты сигнала, действующего на входе Si. триггер 3 фиксируется в состоя нии единицы триггером 2. Это режим сравнения частот. Например, в случае превышения частоты сигнала входа k над частотой сигнала входа 5 обязательно возникает состояние, при котором между двумя активными фронтами импульсов входа 5 присутствуют два активные фронты импульсов входа . Первый фронт импульсов входа k записывает нуль в триггер 3. Единица с его инверсного выхода разрешает действоаать триггеру 1, и второй фронт импульсов.со входа k записывает нул в триггер 1, что переключает триггер 3 в состояние нуля, а это, в свою очередь, фиксирует триггер 2 в состоянии единицы. После этого к входным сигналам чувствителен только триггер 1, но изменение его состояния не влияет на состояние триггера 3, так как выходные сигналы триггера 1 только подтверждают состояние нуля триггера 3. Запаздывание сигналов в триггере 1 способствует принци пу работы дискриминатора. При работе дискриминатора в системе автоподстройки частоты расстройка между частотами сигналов входов k и 5 уменьшается под действием обратной связи. После смены знака частотной расстройки, т.е. когда частота сигнала входа 5 становится чуть выше частоты сигнала входа , между двумя активными фронтами сигнала входа 4 появляются два активные фронты си|- нала входа 5. Первый фронт записывает единицу в триггер 1, что разрешает действовать триггеру 3- Второй (фронт записывает единицу в триггер 3Далее активный фронт сигналов входа записывает в триггер 3 нуль.После этого активный фронт от входа 5 опять может записывать в триггер 3 единицу, и это уже функционирование дискриминатора в фазовом режиме. Как правило, JK .- триггеры имеют группы -Х и К. -входов и могут быть образованы группы входов дискриминатора для когерентных групп сравниваемых сигналов. Сигналы на управляющие входы 8 и 9 могут быть поданы, например, с целью торможения работы дискриминатора или фиксирования его состояния в одном из двух состояний режима частотного сравнивания. При подаче на управляющий вход 8 уровня, переключающего триггер 1 в состояние нуля, триггер 3 фиксируется в состоянии нуля триггером 1, а триггер 2 в состоянии единицы триггером 3- В случае использования управляющего входа Э соответствующие триггеры фиксируются в противоположных состояниях. выполнение триггеров дискриминатора в виде JK -триггеров, а также то, что входы (сигнальные, основные входы) дискриминатора подключены только к J- и К-входам триггеров, т.е. входам нечувствительным к длительности импульсов, делает его работу независимой от длительности импульсов, что повышает точность дискриминатора. Управляющие входы дискриминатора обеспечивают дополнительные функциональные возможности при его использовании.

Формула изобретения

Частотно-фазовый дискриминатор, содержащий фазовый и два блокировочных триггера, отличающийся тем, что, с целью повышения точности и обеспечения возможности управления дискриминатором, триггеры выполнены в виде JK-триггеров, причем J- и К

-входы фазового и первого блокировочного триггера и соответственной- и J -входы второго блокировочного триггера подключены к входам дискриминатора, инверсный и основной выходы фазового триггера - к выходам дискриминатора и соответственно к входам установки единицы первого и второго блокировочных триггеров, основные выходы которых подключены соответственно к входам установки нуля и единицы фазового триггера, а входы установки нуля -К управляющим входам дискриминатора.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1982-06-15—Публикация

1980-11-17—Подача