ел

00

о

СЛ

ю

45

Изобретение относится к радиотехнике и может быть использовано в импульсных и цифровых устройствах фазовой синхронизации, синтезаторах частоты, где требуется широкая полоса захвата при пропадании опорного сигнала.

Целью изобретения является сохранение установившегося режима работы при пропадании опорного сигнала.

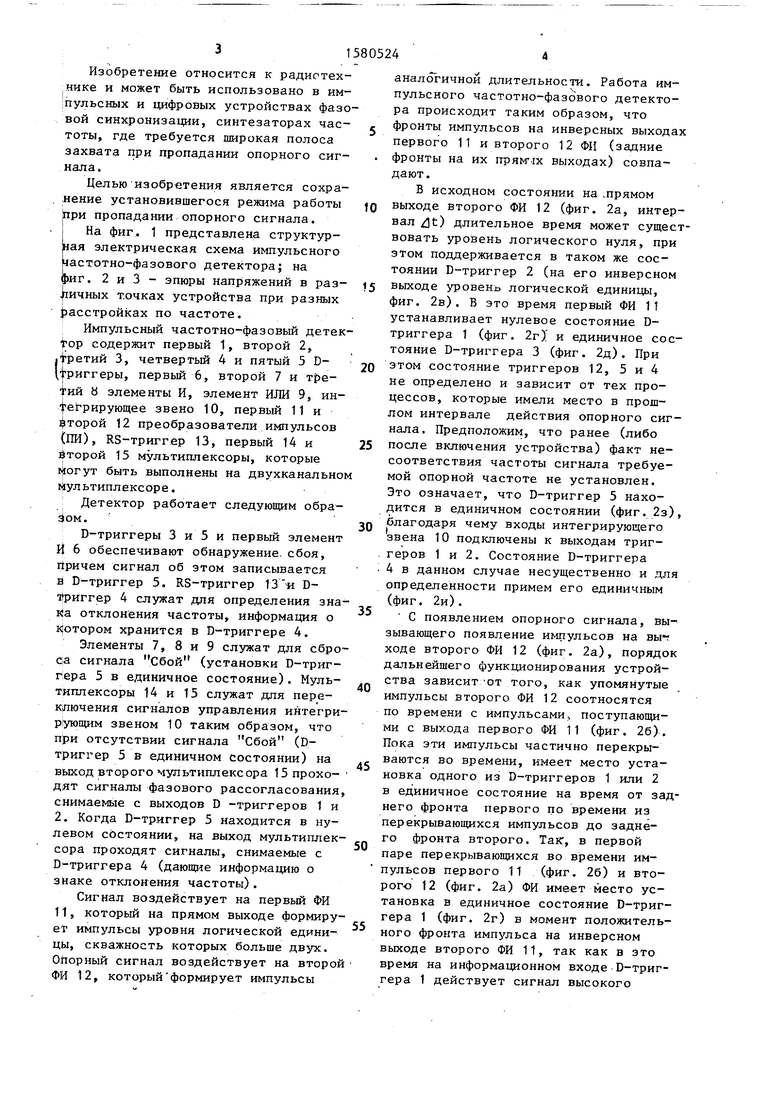

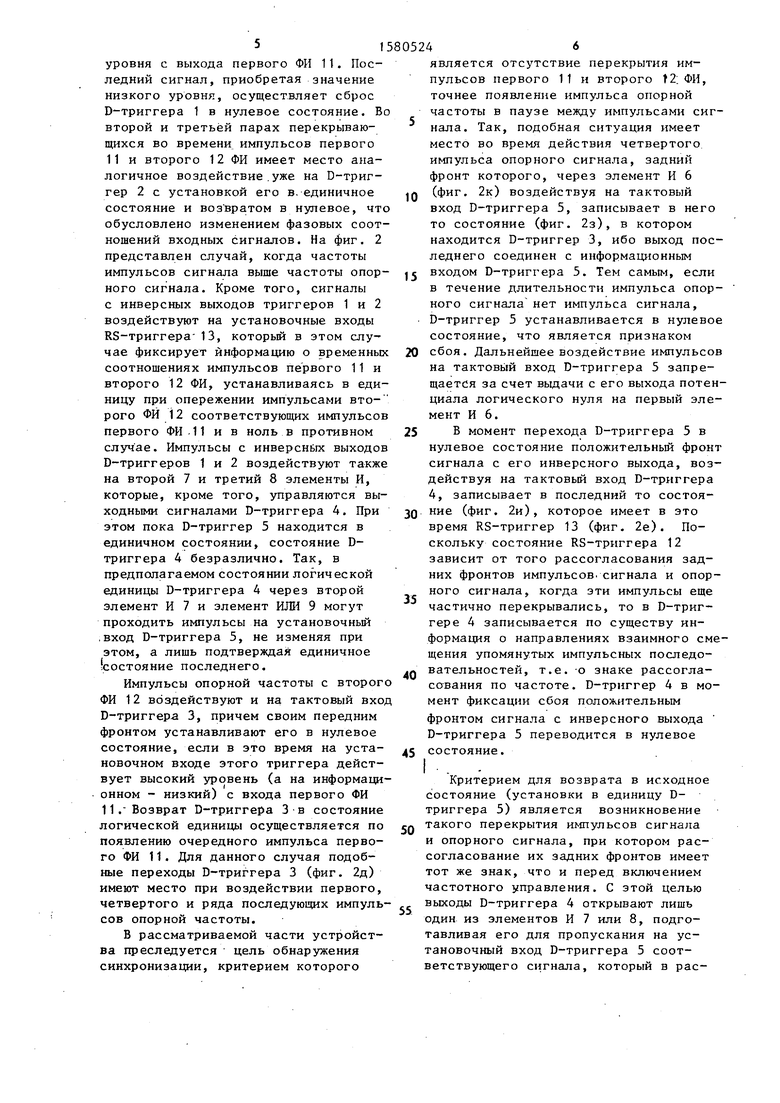

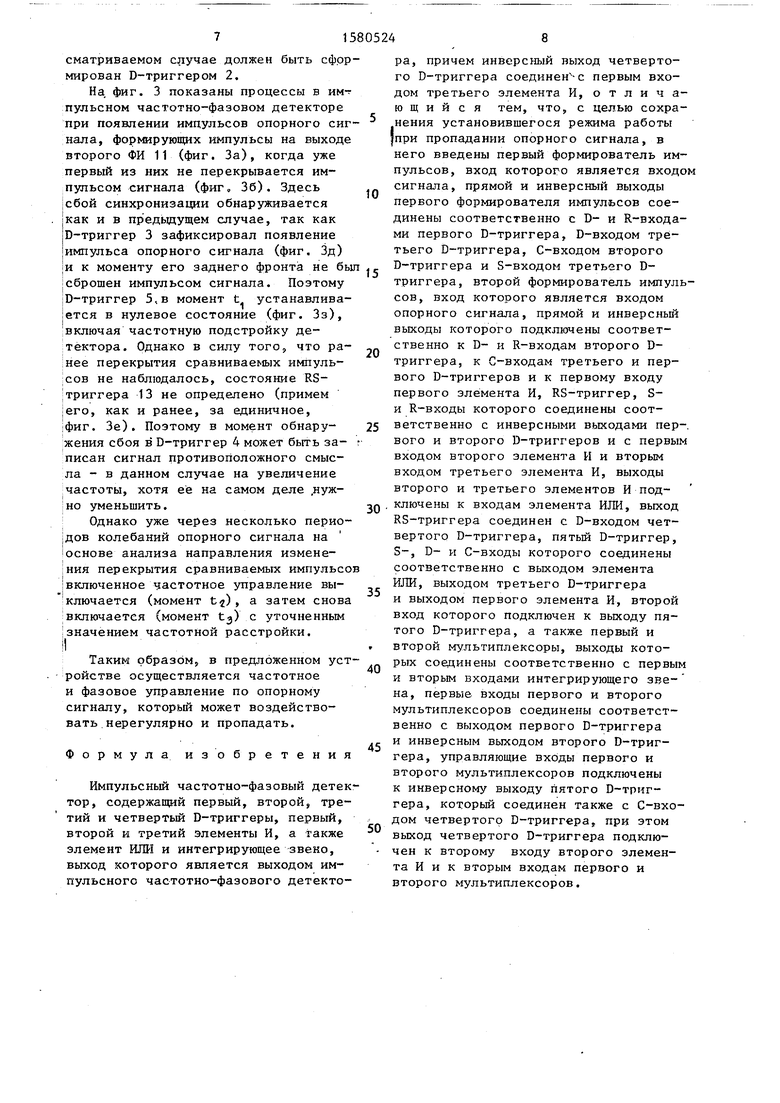

На фиг. 1 представлена структур- ая электрическая схема импульсного частотно-фазового детектора; на фиг. 2 и 3 - эпюры напряжений в раз- личных точках устройства при разных расстройках по частоте.

Импульсный частотно-фазовый детектор содержит первый 1, второй 2, .ретий 3, четвертый 4 и пятый 5 D- (риггеры, первый 6, второй 7 и третий Ь элементы И, элемент ИЛИ 9, интегрирующее звено 10, первый 11 и торой 12 преобразователи импульсов (ПИ), RS-триггер 13, первый 14 и второй 15 мультиплексоры, которые могут быть выполнены на двухканально мультиплексоре.

Детектор работает следующим обра- ёом.

D-триггеры З и 5 и первый элемент И 6 обеспечивают обнаружение сбоя, причем сигнал об этом записывается в D-триггер 5. RS-триггер D- триггер 4 служат для определения эна т/ta отклонения частоты, информация о котором хранится в D-триггере 4.

Элементы 7, 8 и 9 служат для сброса сигнала Сбой (установки D-триг- гера 5 в единичное состояние). Мультиплексоры 14 и 15 служат для переключения сигналов управления интегрирующим звеном 10 таким образом, что при отсутствии сигнала Сбой (D- триггер 5 в единичном состоянии) на выход второго мультиплексора 15 проходят сигналы фазового рассогласования снимаемые с выходов D -триггеров 1 и 2. Когда D-триггер 5 находится в нулевом состоянии, на выход мультиплексора проходят сигналы, снимаемые с D-триггера 4 (дающие информацию о знаке отклонения частоты).

Сигнал воздействует на первый ФИ 11, который на прямом выходе формирует импульсы уровня логической единицы, скважность которых больше двух. Опорный сигнал воздействует на второ ФИ 12, который формирует импульсы

o

0

5

5

0

5

0

5

0

5

аналогичной длительности. Работа импульсного частотно-фазового детектора происходит таким образом, что фронты импульсов на инверсных выходах первого 11 и второго 12 ФИ (задние фронты на их прям1 ix выходах) совпадают.

В исходном состоянии на .прямом выходе второго ФИ 12 (фиг. 2а, интервал /3t) длительное время может существовать уровень логического нуля, при этом поддерживается в таком же состоянии D-триггер 2 (на его инверсном выходе уровень логической единицы, фиг. 2в). В это время первый ФИ 11 устанавливает нулевое состояние D- триггера 1 (фиг. 2г) и единичное состояние D-триггера З (фиг. 2д). При этом состояние триггеров 12, 5 и 4 не определено и зависит от тех процессов, которые имели место в прошлом интервале действия опорного сигнала. Предположим, что ранее (либо после включения устройства) факт несоответствия частоты сигнала требуемой опорной частоте не установлен. Это означает, что D-триггер 5 находится в единичном состоянии (фиг. 2з), благодаря чему входы интегрирующего звена 10 подключены к выходам триггеров 1 и 2. Состояние D-триггера 4 в данном случае несущественно и для определенности примем его единичным (фиг. 2и).

С появлением опорного сигнала, вызывающего появление импульсов на выходе второго ФИ 12 (фиг. 2а), порядок дальнейшего функционирования устройства зависит от того, как упомянутые импульсы второго ФИ 12 соотносятся по времени с импульсами, поступающими с выхода первого ФИ 11 (фиг. 26). Пока эти импульсы частично перекрываются во времени, имеет место установка одного из D-триггеров 1 или 2 в единичное состояние на время от заднего фронта первого по времени из перекрывающихся импульсов до заднего фронта второго. Так1, в первой паре перекрывающихся во времени импульсов первого 11 (фиг. 2б) и второго 12 (фиг. 2а) ФИ имеет место установка в единичное состояние D-триггера 1 (фиг. 2г) в момент положительного фронта импульса на инверсном выходе второго ФИ 11, так как в это время на информационном входе D-триггера 1 действует сигнал высокого

уровня с выхода первого ФИ 11. Последний сигнал, приобретая значение низкого уровня, осуществляет сброс D-триггера 1 в нулевое состояние. Во второй и третьей парах перекрывающихся во времени импульсов первого 11 и второго 12 ФИ имеет место аналогичное воздействие уже на D-триг- гер 2 с установкой его в единичное состояние и возвратом в нулевое, что обусловлено изменением фазовых соотношений входных сигналов. На фиг. 2 представлен случай, когда частоты импульсов сигнала выше частоты опорного сигнала. Кроме того, сигналы с инверсных выходов триггеров 1 и 2 воздействуют на установочные входы RS-триггера 13, который в этом случае фиксирует информацию о временных соотношениях импульсов первого 11 и второго 12 ФИ, устанавливаясь в единицу при опережении импульсами второго ФИ 12 соответствующих импульсов первого ФИ 11 и в ноль в противном случае. Импульсы с инверсных выходов D-триггеров 1 и 2 воздействуют также на второй 7 и третий 8 элементы И, которые, кроме того, управляются выходными сигналами D-триггера 4. При этом пока D-триггер 5 находится в единичном состоянии, состояние D- триггера 4 безразлично. Так, в предполагаемом состоянии логической единицы D-триггера 4 через второй элемент И 7 и элемент ИЛИ 9 могут проходить импульсы на установочный вход D-триггера 5, не изменяя при этом, а лишь подтверждая единичное состояние последнего.

Импульсы опорной частоты с второго ФИ 12 воздействуют и на тактовый вход D-триггера З, причем своим передним фронтом устанавливают его в нулевое состояние, если в это время на установочном входе этого триггера действует высокий уровень (а на информационном - низкий) с входа первого ФИ 11. Возврат D-триггера З в состояние логической единицы осуществляется по появлению очередного импульса первого ФИ 11. Для данного случая подобные переходы D-триггера 3 (фиг. 2д) имеют место при воздействии первого, четвертого и ряда последующих импульсов опорной частоты.

В рассматриваемой части устройства преследуется цель обнаружения синхронизации, критерием которого

0

5

0

является отсутствие перекрытия импульсов первого 11 и второго t2 ФИ, точнее появление импульса опорной частоты в паузе между импульсами сигнала. Так, подобная ситуация имеет место во время действия четвертого импульса опорного сигнапа, задний фронт которого, через элемент И 6 (фиг. 2к) воздействуя на тактовый вход D-триггера 5, записывает в него то состояние (фиг. 2з), в котором находится D-триггер З, ибо выход последнего соединен с информационным входом D-триггера 5. Тем самым, если в течение длительности импульса опорного сигнала нет импульса сигнала, D-триггер 5 устанавливается в нулевое состояние, что является признаком сбоя. Дальнейшее воздействие импульсов на тактовый вход D-триггера 5 запрещается за счет выдачи с его выхода потенциала логического нуля на первый элемент И 6.

В момент перехода D-триггера 5 в нулевое состояние положительный фронт сигнала с его инверсного выхода, воздействуя на тактовый вход D-триггера 4, записывает в последний то состояние (фиг. 2и), которое имеет в это время RS-триггер 13 (фиг. 2е). Поскольку состояние RS-триггера 12 зависит от того рассогласования задних фронтов импульсов сигнала и опорного сигнала, когда эти импульсы еще частично перекрывались, то в D-триг- гере 4 записывается по существу информация о направлениях взаимного смещения упомянутых импульсных последо- Q вательностей, т.е. о знаке рассогласования по частоте. D-триггер 4 в момент фиксации сбоя положительным фронтом сигнала с инверсного выхода D-триггера 5 переводится в нулевое состояние.

5

0

5

5

0

5

Критерием для возврата в исходное состояние (установки в единицу D- триггера 5) является возникновение такого перекрытия импульсов сигнала и опорного сигнала, при котором рассогласование их задних фронтов имеет тот же знак, что и перед включением частотного управления. С этой целью выходы D-триггера 4 открывают лишь один из элементов И 7 или 8, подготавливая его для пропускания на установочный вход D-триггера 5 соответствующего сигнала, который в рас,

сматриваемом случае должен быть сформирован D-триггером 2.

На фиг. 3 показаны процессы в импульсном частотно-фазовом детекторе при появлении импульсов опорного сиг нала, формирующих импульсы на выходе второго ФИ 11 (фиг. За), когда уже первый из них не перекрывается импульсом сигнала (фиг, Зб). Здесь сбой синхронизации обнаруживается |как и в предыдущем случае, так как D-триггер З зафиксировал появление импульса опорного сигнала (фиг. Зд) и к моменту его заднего фронта не бы сброшен импульсом сигнала. Поэтому D-триггер 5,в момент t устанавливается в нулевое состояние (фиг. Зз), включая частотную подстройку детектора. Однако в силу того, что ранее перекрытия сравниваемых импульсов не наблюдалось, состояние RS- триггера 13 не определено (примем , его, как и ранее, за единичное, фиг. Зе). Поэтому в момент обнару- жения сбоя в D-триггер 4 может быть за- писан сигнал противоположного смысла - в данном случае на увеличение частоты, хотя ее на самом деле .нужно уменьшить.

Однако уже через несколько периодов колебаний опорного сигнала на основе анализа направления изменения перекрытия сравниваемых импульсо включенное частотное управление выключается (момент t) а затем снова включается (момент t3) с уточненным значением частотной расстройки.

Таким образом, в предложенном устройстве осуществляется частотное и фазовое управление по опорному сигналу, который может воздействовать нерегулярно и пропадать.

Формула изобретения

Импульсный частотно-фазовый детектор, содержащий первый, второй, третий и четвертый D-триггеры, первый, второй и третий элементы И, а также элемент ИЛИ и интегрирующее звено, выход которого является выходом импульсного частотно-фазового детекто5

.,,- 25 30

в

20

35

40

45

50

ра, причем инверсный выход четвертого D-триггера соединение первым входом третьего элемента И, отличающийся тем, что, с целью сохранения установившегося режима работы при пропадании опорного сигнала, в него введены первый формирователь импульсов, вход которого является входом сигнала, прямой и инверсный выходы первого формирователя импульсов соединены соответственно с D- и R-входа- ми первого D-триггера, D-входом третьего D-триггера, С-входом второго D-триггера и S-входом третьего D- триггера, второй формирователь импульсов, вход которого является входом опорного сигнала, прямой и инверсный выходы которого подключены соответственно к D- и R-входам второго D- триггера, к С-входам третьего и первого D-триггеров и к первому входу первого элемента И, RS-триггер, S- и R-входы которого соединены соответственно с инверсными выходами пер-, вого и второго D-триггеров и с первым входом второго элемента И и вторым входом третьего элемента И, выходы второго и третьего элементов И подключены к входам элемента ИЛИ, выход RS-триггера соединен с D-входом четвертого D-триггера, пятый D-триггер, S-, D- и С-входы которого соединены соответственно с выходом элемента ИЛИ, выходом третьего D-триггера и выходом первого элемента И, второй вход которого подключен к выходу пятого D-триггера, а также первый и второй мультиплексоры, выходы которых соединены соответственно с первым и вторым входами интегрирующего звена, первые входы первого и второго мультиплексоров соединены соответственно с выходом первого D-триггера и инверсным выходом второго D-триггера, управляющие входы первого и второго мультиплексоров подключены к инверсному выходу пятого D-триггера, который соединен также с С-входом четвертого D-триггера, при этом выход четвертого D-триггера подключен к второму входу второго элемента И и к вторым входам первого и второго мультиплексоров.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для передачи и приема сигналов начальной синхронизации | 1987 |

|

SU1543559A1 |

| Устройство для автоматического измерения параметров колебательных контуров | 1986 |

|

SU1406525A1 |

| СТАРТСТОПНАЯ СИСТЕМА СВЯЗИ | 2009 |

|

RU2396722C1 |

| ЧАСТОТНО-ФАЗОВОЕ РЕЛЕ | 2016 |

|

RU2641096C2 |

| УСТРОЙСТВО ПОИСКА И СОПРОВОЖДЕНИЯ СИГНАЛА СИНХРОНИЗАЦИИ В СПУТНИКОВЫХ СИСТЕМАХ СВЯЗИ ПО ПРИЕМУ | 1995 |

|

RU2093964C1 |

| Устройство для управления вентильным преобразователем | 1991 |

|

SU1774446A1 |

| Цифровой частотно-фазовый дискриминатор | 1986 |

|

SU1390774A2 |

| Частотно-фазовый дискриминатор | 1988 |

|

SU1589373A1 |

| Устройство тактовой синхронизации | 1989 |

|

SU1720162A1 |

| Круговой интерполятор | 1985 |

|

SU1359772A1 |

Изобретение относится к радиотехнике и и импульсной технике. Цель изобретения - сохранение установившегося режима работы при пропадании опорного сигнала. Импульсный частотно-фазовый детектор содержит первый, второй, третий, четвертый и пятый D-триггеры 1-5, первый, второй и третий элемент И 6-8,о элемент ИЛИ 9, интегрирующее звено 10, первый и второй формирователи импульсов 11 и 12, RS-триггер 13 и первый и второй мультиплексоры 14 и 15. Введенные третий, четвертый и пятый D-триггеры 3-5, RS-триггер 13, первый, второй и третий элементы И 6-8 и элемент ИЛИ 9 позволяют определить наличие частотной расстройки. Причем прямой выход четвертого D-триггера 4 определяется знак частотного рассогласования. Пятый D-триггер 5 в зависимости от величины расстройки определяет частотный или фазовый режим работы детектора. При этом в частотном режиме на входы интегрирующего звена 10 поступает сигнал с выхода четвертого D-триггера 4, а в фазовом режиме - сигналы с инверсных выходов первого и второго D-триггеров 1 и 2. При пропадании опорного сигнала на входе второго формирователя импульсов 12 пятый D-триггер 5 не изменяет своего состояния. 3 ил.

| Импульсный частотно-фазовый детектор | 1984 |

|

SU1221710A2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-07-23—Публикация

1987-06-02—Подача