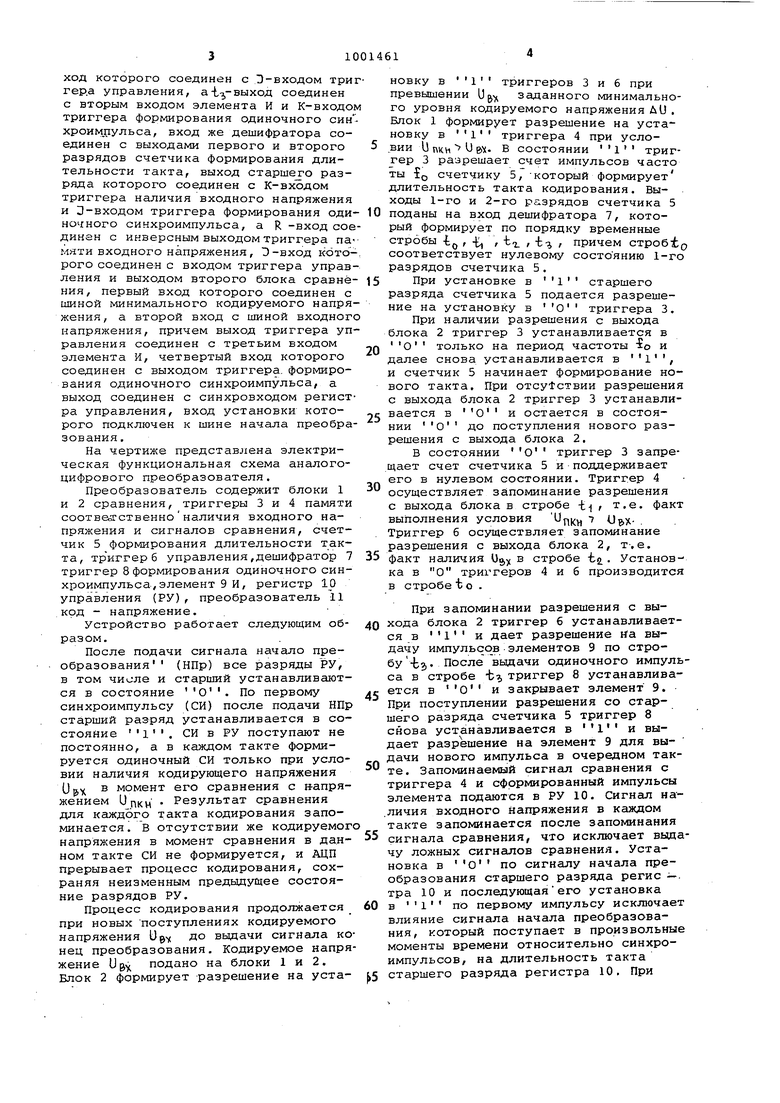

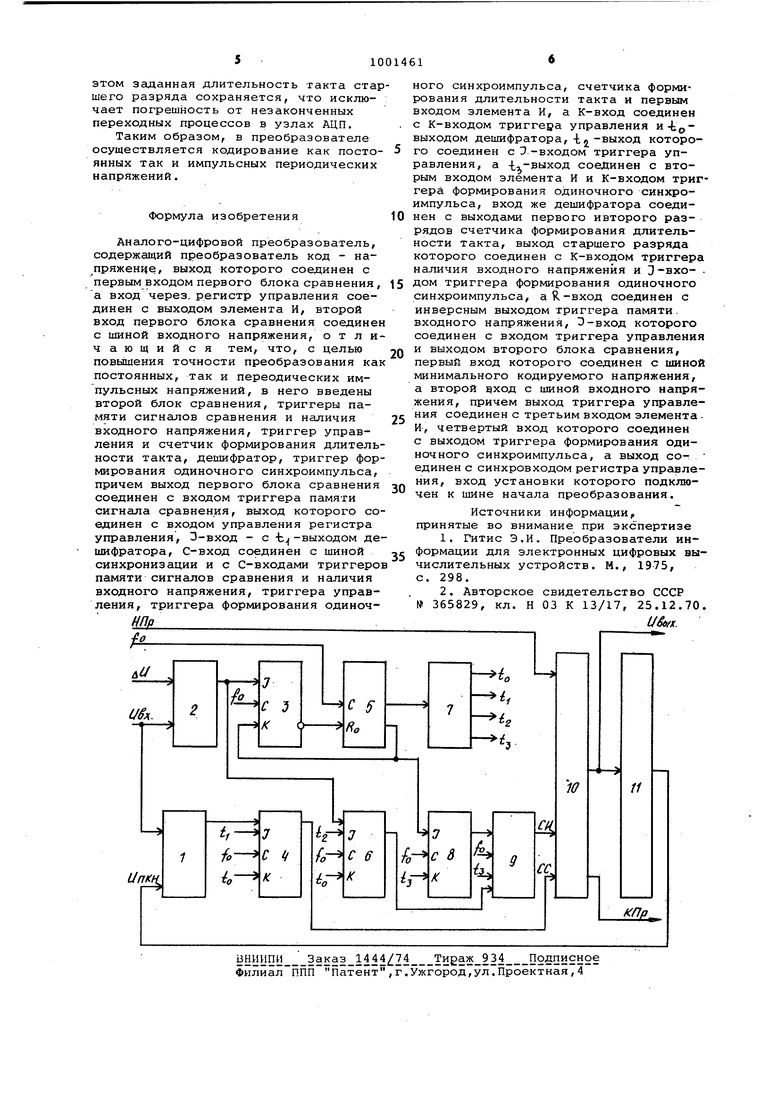

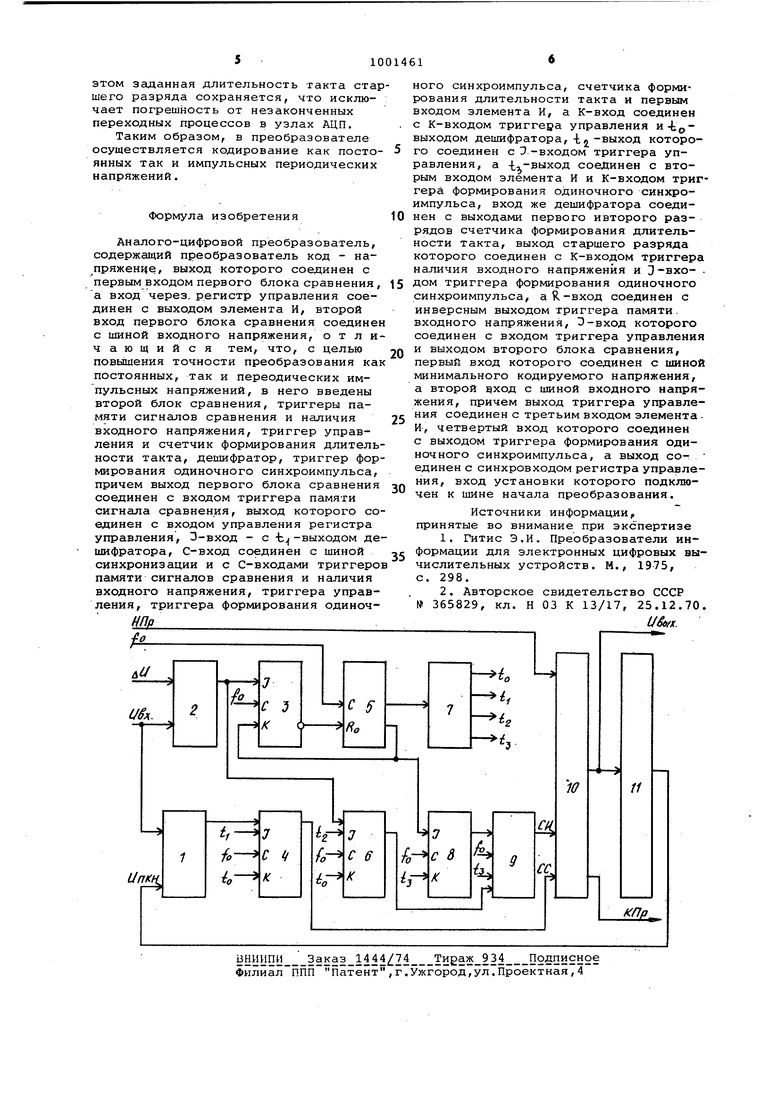

ход которого соединен с D-входом тр гера управления, а i -выход соединен с вторым входом элемента И и К-вход триггера формирования одиночного си хроим.цульса, вход же дешифратора со единен с выходами первого и второго разрядов счетчика формирования длительности такта, выход старшего разряда которого соединен с К-входом триггера наличия входного напряжения и 3-входом триггера формирования оди ночного синхроимпульса, а R -вход со динен с инверсным выходом триггера па мяти входного напряжения, Э-вход кото рого соединен с входом триггера управ ления и выходом второго блока сравнё НИН, первый вход которого соединен с шиной минимального кодируемого напря жения, а второй вход с шиной входног напряжения, причем выход триггера уп равления соединен с третьим входом элемента И, четвертый вход которого соединен с выходом триггера, формирования одиночного синхроимпульса, а выход соединен с синхровходом регист ра управления, вход установки которого подключен к шине начала преобра зования. На чертиже представлена электрическая функциональная схема аналогоцифрового преобразователя. Преобразователь содержит блоки 1 и 2 сравнения, триггеры 3 и 4 памяти соотвед ственно наличия входного напряжения и сигналов сравнения, счетчик 5 формирования длительности такта, триггерб управления,дешифратор 7 триггер 8 формирования одиночного синхроимпульса, элемент 9 И, регистр 10 управления (РУ), преобразователь 11 .код - напряжение. . Устройство работает следующим образом. После подачи сигнала начало преобразования (НПр) все разряды РУ, в том числе и старший устанавливаются в состояние О. По первому синхроимпульсу (СИ) после подачи НПр старший разряд устанавливается в состояние Ч. СИ в РУ поступают не постоянно, а в каждом такте формируется одиночный СИ только при условии наличия кодирующего напряжения (J в момент его сравнения с апряжением UnKM Результат сравнения для каждого такта кодирования запоминается. В отсутствии же кодируемог напряжения в момент сравнения в данном такте СИ не формируется, и АЦП прерывает процесс кодирования, сохраняя неизменным предыдущее состояние разрядов РУ. Процесс кодирования продолжается при новых поступлениях кодируемого напряжения Ug до выдачи сигнала ко нец преобразования. Кодируемое напря жение Ugy подано на блоки 1 и 2. Блок 2 формирует -разрешение на установку в 1 триггеров 3 и 6 при превышении U заданного минимального уровня кодируемого напряжения ДУ . Блок 1 формирует разрешение на установку в ч триггера 4 при условии и пки U е.. Б состоянии триггер 3 разрешает счет импульсов часто ты {Q счетчику 5, -который формирует длительность такта кодирования. Быходы 1-го и 2-го разрядов счетчика 5 поданы на вход дешифратора 7, который формирует по порядку временные стробы -tj, , -t, , t , -Ьт, , причем cTpoetp соответствует нулевому состоянию 1-го разрядов счетчика 5. При установке в Ч старшего разряда счетчика 5 подается разрешение на установку в О триггера 3. При наличии разрешения с выхода блока 2 триггер 3 устанавливается в I iQi I только на период частоты Ео и далее снова устанавливается в Ч, и счетчик 5 начинает формирование нового такта. При отсутствии разрешения с выхода блока 2 триггер 3 устанавливается в О и остается в состоянии о до поступления нового разрешения с выхода блока 2. В состоянии о триггер 3 запрещает счет счетчика 5 и поддерживает его в нулевом состоянии. Триггер 4 осуществляет запоминание разрешения с выхода блока в стробе -t , т.е. факт выполнения условия 7 U xТриггер 6 осуществляет запоминание разрешения с выхода блока 2, т-, е. факт наличия Оо, в стробе -t . Установ-ка в О триггеров 4 и б производится в стробе to . При запоминании разрешения с выхода блока 2 триггер 6 устанавливается в Ч и дает разрешение аа выдачу импульсовэлементов 9 по стробу -Ьз После выдачи одиночного импульса в стробе -Ьт, триггер 8 устанавливается в О и закрывает элемент 9. При поступлении разрешения со старшего разряда счетчика 5 триггер 8 снова устанавливается в Ч и выдает разрешение на элемент 9 для выдачи нового импульса в очередном такте. Запоминаемый сигнал сравнения с триггера 4 и сформированный импульсы элемента подаются в РУ 10. Сигнал наличия входного Напряжения в каждом такте запоминается после запоминания сигнала сравнения, что исключает вьщачу ложных сигналов сравнения. Установка в О по сигналу начала преобразования старшего разряда регис -. тра 10 и последующаяего установка в ч по первому импульсу исключает влияние сигнала начала преобразования, который поступает в произвольные моменты времени относительно синхроимпульсов, на длительность такта старшего разряда регистра 10, При этом заданная длительность такта ста шего разряда сохраняется, что исключает погрешность от незаконченных переходных процессов в узлах АЦП. Таким образом, в преобразователе осуществляется кодирование как посто янных так и импульсных периодических напряжений. Формула изобретения Аналого-цифровой преобразователь, содержащий преобразователь код - напряженче, выход которого соединен с первым входом первого блока сравнения а вход через, регистр управления соединен с выходом элемента И, второй вход первого блока сравнения соедине с шиной входного напряжения, отли чающийся тем, что, с целью повьпдения точности преобразования ка постоянных, так и переодических импульсных напряжений, в него введены второй блок сравнения, триггеры памяти сигналов сравнения и наличия входного напряжения, триггер управления и счетчик формирования длитель ности такта, дешифратор, триггер фор мирования одиночного синхроимпульса, причем выход первого блока сравнения соединен с входом триггера памяти сигнала сравнения, выход которого со единен с входом управления регистра управления, 3-вход - с -Ь -выходом де шифратора, С-вход соединен с шиной синхронизации и с С-входами триггеро памяти сигналов сравнения и наличия входного напряжения, триггера управ ления, триггера формирования одиночного синхроимпульса, счетчика формирования длительности такта и первым входом элемента И, а К-вход соединен с к-входом триггера управления и-Ьрвыходом дешифратора, -tj,-выход которого соединен с I) -входом триггера управления, а - -выход соединен с вторым входом элемента И и К-входом триггера формирования одиночного синхроимпульса, вход же дешифратора соединен с выходами первого ивторого разрядов счетчика формирования длительности такта, выход старшего разряда которого соединен с К-входом триггера наличия входного напряжения и . дом триггера формирования одиночного синхроимпульса, а R-вход соединен с инверсным выходом триггера памяти, входного напряжения, 3-вход которого соединен с входом триггера управления и выходом второго блока сравнения, первый вход которого соединен с шиной минимального кодируемого напряжения, а второй эход с шиной входного напряжения, причем выход триггера управления соединен с третьим входом элемента И, четвертый вход которого соединен с выходом триггера формирования одиночного синхроимпульса, а выход со- единен с синхровходом регистра управления, вход установки которого подключен к шине начала преобразования. Источники информации, принятые во внимание при экспертизе 1.Гитис Э.И. Преобразователи информации для электронных цифровых вычислительных устройств. М., 1975, с. 298. 2.Авторское свидетельство СССР № 365829, кл. Н 03 К 13/17, 25.12.70.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный аналого-цифровой преобразователь | 1980 |

|

SU930656A1 |

| СПОСОБ ТЕЛЕВИЗИОННОГО ВЕЩАНИЯ С ЗАЩИТОЙ ОТ НЕСАНКЦИОНИРОВАННОГО ПРИЕМА И СИСТЕМА ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2013024C1 |

| Аналого-цифровой преобразователь поразрядного кодирования | 1985 |

|

SU1325701A1 |

| Устройство для контроля аналоговых объектов | 1985 |

|

SU1288702A1 |

| Устройство для синхронизации распределенной вычислительной системы | 1988 |

|

SU1508201A1 |

| Устройство для ввода аналоговой информации | 1988 |

|

SU1501026A1 |

| Устройство для контроля знаний обучаемых | 1987 |

|

SU1524082A1 |

| Устройство для контроля цифровых узлов | 1982 |

|

SU1059576A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1988 |

|

SU1583967A1 |

| Устройство для отладки многопроцессорных систем | 1988 |

|

SU1644145A1 |

Авторы

Даты

1983-02-28—Публикация

1981-01-19—Подача