СП

ю

а

3150

счетчик 3, блок форьтроваиия приоритетного адреса 4, первый элемент ИЛИ 5, коммутатор 10, суммирующий усилитель 11, фильтр нижних частот 14, аналого-цифровой преобразователь 15, сумматор 16, блок памяти 9 и блок управления.. 1 3. Алгоритм преобразования данных по каждому из каналов состоит из двух последовательных этапов. На первом этапе осуществляется грубое преобразование методом разворачивания общей ступенчатой эталонной меры. На втором этапе методом считывания или последовательных приближений осуществляется точное преобразование от

дельно по каждому ия кан;шов. При этом точное преобразование выполняется последовательно для каналов с

близким значением аналогичных сигналов на входе, что позволяет исключить большие скачки напряжений на входе измерительного тракта точного преобразования и осуществить установку

фильтра НЧ без сколько-нибудь значительной потери быстродействия устройства. Наличие фильтра НЧ в точном измерительном тракте позволяет повысить помехозащищенность входов устройства

в высокочастотной части спектра аддитивных помех. 4 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для ввода аналоговых данных | 1988 |

|

SU1501025A1 |

| Устройство для считывания графической информации | 1986 |

|

SU1377882A1 |

| Устройство для контроля блоков оперативной памяти | 1986 |

|

SU1358003A1 |

| Устройство для контроля знаний обучаемых | 1983 |

|

SU1176362A1 |

| Программируемый аналого-цифровой преобразователь | 1987 |

|

SU1732469A1 |

| Адаптивный кодирующий преобразователь стационарных случайных процессов | 1980 |

|

SU960846A1 |

| Устройство для считывания информации | 1989 |

|

SU1693617A1 |

| Устройство для ввода информации | 1983 |

|

SU1145336A1 |

| СПОСОБ И УСТРОЙСТВО КОРРЕКЦИИ ПОГРЕШНОСТЕЙ АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ | 2007 |

|

RU2352060C1 |

| Устройство для воспроизведения псевдообъемного изображения | 1984 |

|

SU1233302A1 |

Изобретение относится к информационно-измерительной и вычислительной технике и может быть использовано в системах сбора и обработки аналоговых данных от объекта. Целью изобретения является повышение надежности устройства. Устройство содержит группу элементов сравнения 1, группу триггеров 6, группу элементов И 7, цифроаналоговый преобразователь 2, счетчик 3, блок формирования приоритетного адреса 4, первый элемент ИЛИ 5, коммутатор 10, суммирующий усилитель 11, фильтр нижних частот 14, аналого-цифровой преобразователь 15, сумматор 16, блок памяти 9 и блок управления 13. Алгоритм преобразования данных по каждому из каналов состоит из двух последовательных этапов. На первом этапе осуществляется грубое преобразование методом разворачивания общей ступенчатой эталонной меры. На втором этапе методом считывания или последовательных приближений осуществляется точное преобразование отдельно по каждому из каналов. При этом точное преобразование выполняется последовательно для каналов с близким значением аналогичных сигналов на входе, что позволяет исключить большие скачки напряжений на входе измерительного тракта точного преобразования и осуществить установку фильтра НЧ без сколько-нибудь значительной потери быстродействия устройства. Наличие фильтра НЧ в точном измерительном тракте позволяет повысить помехозащищенность входов устройства в высокочастотной части спектра аддитивных помех. 4 ил.

Изобретение относится к области информационно-измерительной и вычислительной техники и может быть использовано в системах сбора и обработки аналоговых данных от объекта.

Целью изобретения является повышение надежности устройства.

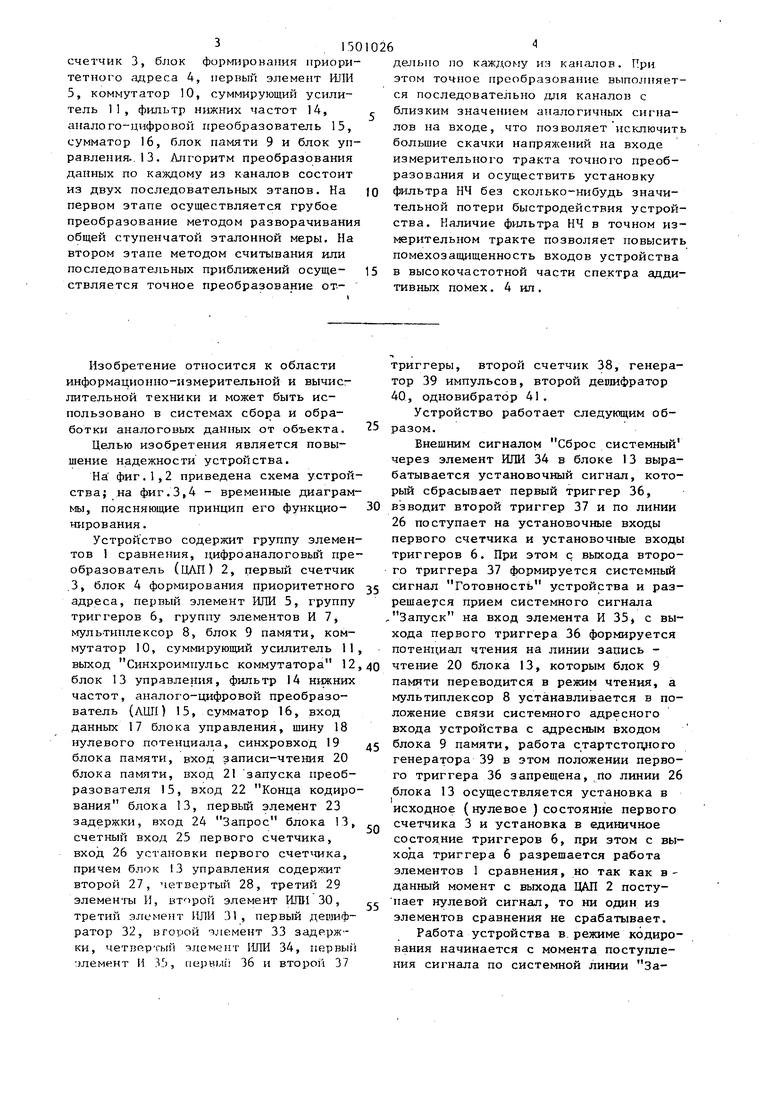

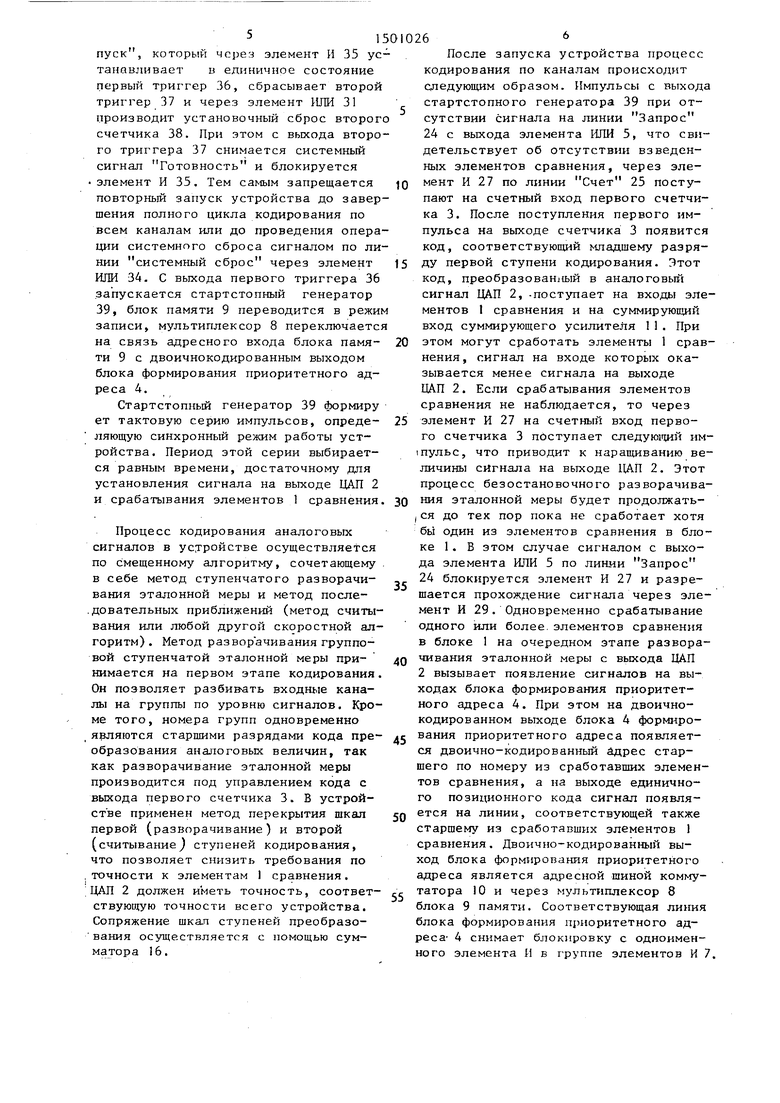

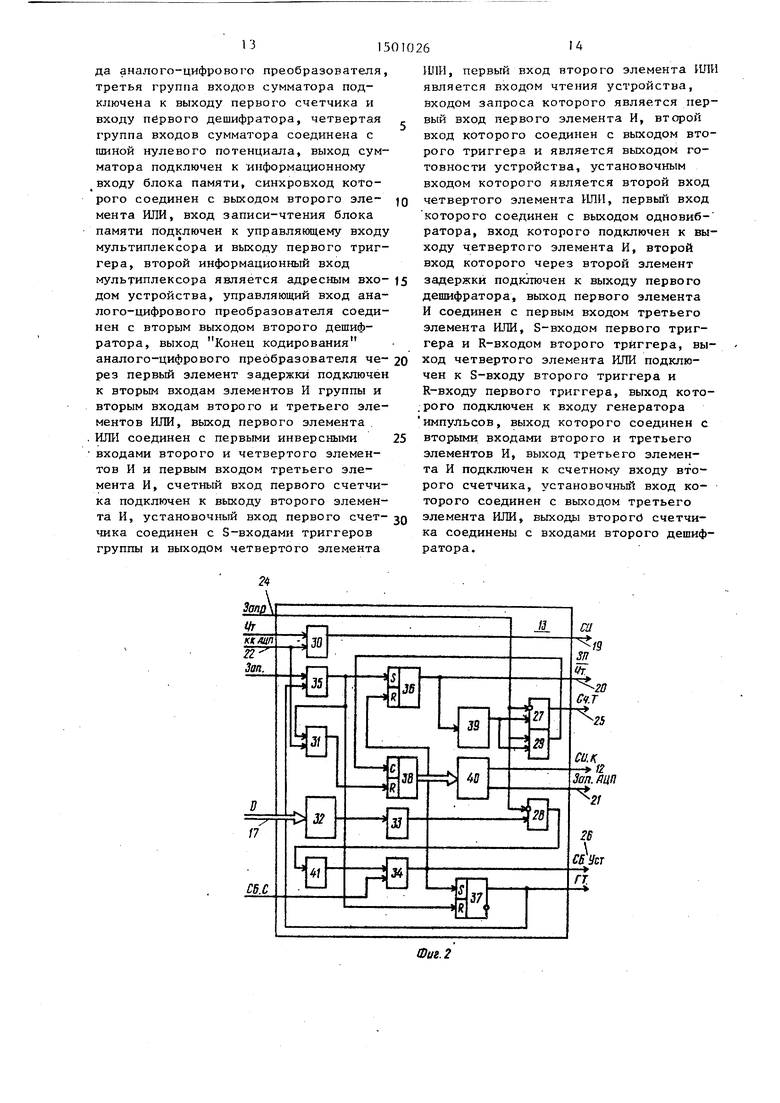

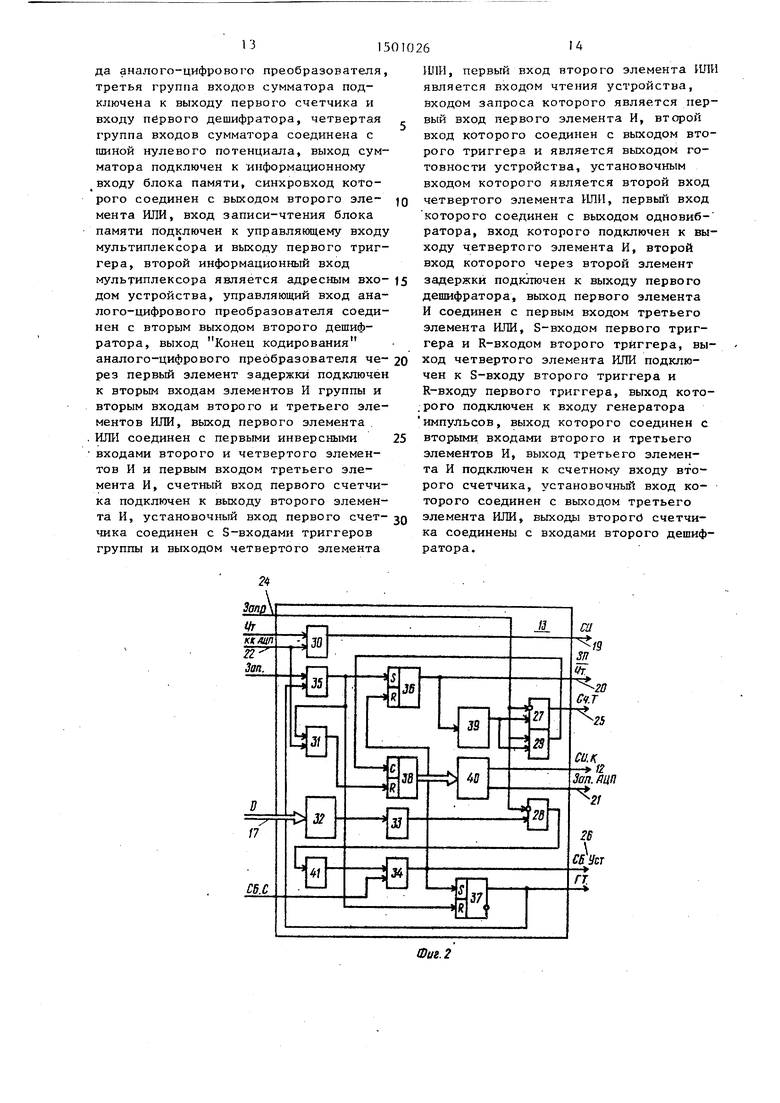

На фиг.1,2 приведена схема устройства; на фиг.3,4 - временные диаграммы, поясняющие принцип его функцио- нирования.

Устройство содержит группу элементов 1 сравнения, цифроаналоговьв преобразователь (ЦЛП) 2, первый счетчик .3, блок 4 формирования приоритетного адреса, первый элемент ИЛИ 5, группу триггеров 6, группу элементов И 7, мультиплексор 8, блок 9 памяти, коммутатор 10, суммирующий усилитель 11 выход Синхроимпульс коммутатора 12 блок 13 управления, фильтр 14 частот, аналого-цифровой преобразователь (ЛЦП) 15, сумматор 16, вход данных 17 блока управления, шину 18 нулевого потенциала, синхровход 19 блока памяти, вход записи-чтения 20 блока памяти, вход 21 запуска преобразователя 15, вход 22 Конца кодирования блока 13, первый элемент 23 задержки, вход 24 Запрос блока 13, счетный вход 25 первого счетчика, вход 26 установки первого , причем блок 13 управления содержит второй 27, четвертый 28, третий 29 элементы И, второй элемент ИЛИ 30, третий элемент ИЛИ 31, первый дешифратор 32, вгорой элемент 33 задерж- ки, четвертый элемент ИЛИ 34, первый элемент И 35, первый 36 и второй 37

триггеры, второй счетчик 38, генератор 39 импульсов, второй девшфратор 40, одновибратор 41.

Устройство работает следующим образом.

Внешним сигналом Сброс системный через элемент ИЛИ 34 в блоке 13 вырабатывается установочный сигнал, который сбрасывает первый триггер 36, взводит второй триггер 37 и по линии 26 поступает на установочные входы первого счетчика и установочные входы триггеров 6. При этом с выхода второго триггера 37 формируется системный сигнал Готовность устройства и раз- решаеуся прием системного сигнала ,Запуск на вход элемента И 35 с выхода первого триггера 36 формируется потенциал чтения на линии запись - чтение 20 блока 13, которым блок 9 памяти переводится в режим чтения, а мультиплексор 8 устанавливается в положение связи системного адресного входа устройства с адресным входом блока 9 памяти, работа стартстоцного генератора 39 в этом положении первого триггера 36 запрещена, ito линии 26 блока 13 осуществляется установка в исходное (нулевое ) состояние первого счетчика 3 и установка в единичное состояние триггеров 6, при этом с выхода триггера 6 разрешается работа элементов 1 сравнения, но так как в- данный момент с выхода ЦАП 2 поступает нулевой сигнал, то ни один из элементов сравнения не срабатывает.

Работа устройства в. режиме кодирования начинается с момента поступления сигнала по системной линии За51501026

который через элемент И 35 успуск

танавлнвает в единичное состояние первый триггер 36, сбрасывает второй триггер 37 и через элемент ИЛИ 31 производит установочный сброс второго счетчика 38. При этом с выхода второго триггера 37 снимается системный сигнал Готовность и блокируется элемент И 35. Тем самым запрещается повторный запуск устройства до завершения полного цикла кодирования по всем каналам или до проведения операции системного сброса сигналом по линии системный сброс через элемент ИЛИ 34. С выхода первого триггера 36 запускается стартстопный генератор 39, блок памяти 9 переводится в режим записи, мультиплексор 8 переключается на связь адресного входа блока памяти 9 с двоичнокодированным выходом блока формирования приоритетного адреса 4.

Стартстопный генератор 39 формиру ет тактовую серию импульсов, определяющую синхронный режим работы устройства. Период этой серии выбирается равным времени, достаточному для установления сигнала на выходе ЦАП 2 и срабатывания элементов 1 сравнения.

Процесс кодирования аналоговых сигналов в устройстве осуществляется по смещенному алгоритму, сочетающему . в себе метод ступенчатого разворачивания эталонной меры и метод последовательных приближений (метод считывания или любой другой скоростной алгоритм). Метод развор ачивания групповой ступенчатой эталонной меры принимается на первом этапе кодирования. Он позволяет разбив ать входные каналы на группы по уровню сигналов. Кроме того, номера групп одновременно

являются старшими разрядами кода преобразования аналоговых величин, так как разворачивание эталонной меры производится под управлением кода с выхода первого счетчика 3. В устройстве применен метод перекрытия шкал первой (разворачивание) и второй (считываниеJ ступеней кодирования, что позволяет снизить требования по

точности к элементам 1 сравнения.

ЦАП 2 должен иметь точность, соответствующую точности всего устройства. Сопряжение шкал ступеней преобразования осуществляется с помощью сумматора 16.

10

15

20

25

30

35

40

45

50

55

м п к к си м в э н зы ср эл го 1пу ли пр ни Iся бы ке да ша ме од в чи 2 хо но ко ва ся ше то го ет ст ср хо ад та бл бл ре но

0

5

0

5

0

5

0

5

0

5

После запуска устройства процесс кодирования по каналам происходит следующим образом. Импульсы с выхода стартстопного генератора 39 при отсутствии сигнала на линии Запрос 24 с выхода элемента ИЛИ 5, что свидетельствует об отсутствии взведенных элементов сравнения, через элемент И 27 по линии Счет 25 поступают на счетный вход первого счетчика 3. После поступления первого импульса на выходе счетчика 3 появится код, соответствующий младшему разряду первой ступени кодирования. Этот код, npeo6pa3OBaHj{bm в аналоговый сигнал ЦАП 2, -поступает на входы элементов 1 сравнения и на суммирующий вход суммирующего усилителя 11. При этом могут сработать элементы 1 сравнения, сигнал на входе которых оказывается менее сигнала на выходе ЦАП 2. Если срабатывания элементов сравнения не наблюдается, то через элемент И 27 на счетный вход первого счетчика 3 поступает следую1п;ий им- 1пульс, что приводит к наращиванию величины сигнала на выходе ЦАП 2. Этот процесс безостановочного разворачивания эталонной меры будет продолжать- Iся до тех пор пока не сработает хотя бы один из элементов сравнения в блоке 1 . В этом случае сигналом с выхода элемента ИЛИ 5 по линии Запрос 24 блокируется элемент И 27 и разрешается прохождение сигнала через элемент И 29. Одновременно срабатывание одного или более, элементов сравнения в блоке 1 на очередном этапе разворачивания эталонной меры с выхода ЦАП 2 вызывает появление сигналов на выходах блока формирования приоритетного адреса 4. При этом на двоично- кодированном выходе блока 4 формирования приоритетного адреса появляется двоично-кодированный адрес старшего по номеру из сработавших элементов сравнения, а на выходе единичного позиционного кода сигнал появляется на линии, соответствующей также старшему из сработавших элементов 1 сравнения. Двоично-кодированный выход блока формирования приоритетного адреса является адресной шиной коммутатора 10 и через мультиплексор 8 блока 9 памяти. Соответствующая линия блока формирования приоритетного адреса 4 снимает блокировку с одноименного элемента И в группе элементов И 7.

Далее схема устройства реализует алгоритм второй ступени кодирования по уже адресованному с выхода блока 4 каналу. Тактовые импульсы с выхода старстопного генератора 39 через элемент И 29 начинают поступать на счетный вход второго счетчика 38, По мере заполнения счетчика через второй дешифратор АО сначала вырабатывается управляющий импульс на линии Синхроимпульс коммутатора 12, по которому открывается адресованный канал аналогового коммутатора 10. Далее с выдержкой времени, необходимой для за- вершения переходных процессов на выходе НЧ-фильтра 14, вырабатывается сигнал на линии Запуск АЦП 21. АЦП 15 кодирует разност1а1Й сигнал между входным по адресованному каналу и эталонным с выхода ЦАП 2, Результат кодирования подается на младшие разряды первого входа сумматора 16. На старшие разряды этого же входа подается знаковый разряд выходного кода АЦЦ 15. С завершением процедуры кодирования АЦП 15 вырабатывается сигнал Конец кодирования, который через первый- элемент 23 задержки поступает на линию Конец кодирования АЦП 22 блока 13..Величина задержки определяется из времени распространения си1 - нала через сумматор 16. В блоке 13 сигналом по линии Конец кодирования АЦП 22 через элемент ИЛИ 30 формируется сигнал на линии Синхроимпульс 19, которым данные с выхода сумматора 16 заносятся в блок 9 памяти. Кроме того, сигнал Конец кодирования с выхода первого элемента 2 задержки поступа ет на объединенные вторые входы элементов И группы элементов И 7, где он, проходя через разблокированный с выхода блока формирования приоритетного адреса 4 эле мент И, поступает на установочный вход одноименного (одномерного ) три гера группы триггеров 6 и сбрасывает его. Сброс триггера в группе триггеров 6 вызывает запрет работы соответствующего элемента 1 сравнения. Таким образом, завершение кодирования на второй ступени преобразования по каналу, выставившему запрос работы второй ступени через элемент ИЛИ 5, приво,од1т к сбросу соответствуюше-- I o элемента 1 сраннения, который пер) сможет (:р;аботать только h сл.е- ДУЮ1ЦСМ цик1и; работы ус:.тройства, i.i .

д 5 0 5 Q п д

5

50

55

только после новой установки соответствующего триггера в группе 6.

Если на данной ступени разворачивания эталонной меры с выхода ЦАП сработало несколько элементов сравнения в группе 1, что является типовым случаем, то снятие сигнала с выхода элемента сравнения с обработанного канала приводит к формированию на выходе блока 5 формирования приоритетного адреса нового адреса, который соответствует номеру старшего из оставшихся сработавших элементов сравнения на данной ступени разворачивания эталона.

Следует отметить, что сигналом по линии Конец кодирования АЦП 22 в блоке 13 через элемент ИЛИ 31 осу- тДествляется сброс счетчика 38, через которьй реализуется программа работы второй ступени преобразования. Следовательно, по сигналу Конец кодирования с выхода АЦП 15 осуществляется запись полученных данных в блок 9 памяти, формирование адреса следующего канала, выставившего запрос на обслуживание второй ступенью преобразова- НИН на данном шаге разворачивания эталонной меры первой ступени разования и новый запуск программатора работы второй ступени, если с выхода элемента ИЛИ 5 еще имеется запрос, т.е. если еще есть каналы, выставившие запрос на работу второй ступен и на данном такте разворачивания эталона с выхода ЦАП 2.

Если же на выходе элемента ИЛИ 5 сигнала нет, то по линии Запрос 24 в блоке 13 блокируется элемент И 29 и разблокируется элемент И 27. Вновь следующий тактовьй импульс поступает на счетный вход счетчика 3, что приведет к наращиванию на одну ступень эталона первой ступени преобразования. Вновь срабатывает какая-то группа элементов сравнения в rpytine I и т.д. Далее устройство работает аналогично .

Следует отметить, что первая ступень преобразования на каждом шаге выделяет группу каналов, входные сигналы которых отличны друг от друга не более, чем на величину кванта разворачивания эталонного сигнала первой ступени. Следовательно, в процессе/ обработки этих каналов второй ступенью преобразования, которая работа ет через аналоговый коммутатор 10.

величина скачков напряжения на входе ПЧ-фипьтра 14 не будет превьшать величины кванта разворачивания эталона первой ступени. Величина кванта эталона первой ступени должна превьшать амплитуду помех по входу, так как в устройстве помехозащитой обладает только вторая ступень преобразования Если принять, например, число разрядов (двоичных ) первой ступени равными пяти, т.е. получить 31 ступень разворачивания эталона первой ступени, то при 20-вольтовом диапазоне |уровень помех не должен превьшать 0,65 В, что вполне реально. Кроме того, в процессе работы второй, по- мехозащищенной, ступени преобразования максимальные скачки напряжения в процессе переключения аналогового коммутатора 10 не превысят 0,65 В, что сохранит линейный режим работы цепочки 7 суммирующий усилитель 11, фильтр НЧ 14, АЦП 15. Линейный режим работы аналоговой измерительной, цепи и малые по амплитуде перепады напряжения позволяют существенно изучить динамику цепи, чем сохраняется возможность установки группового фильтра НЧ при удовлетворительном быстродействии устройства.

Механизм сравнения шкал первой и второй ступеней преобразования устройства реализуется сумматором 16. На второй вход этого сумматора, на старшие разряды, подается код с выхода первого счетчика 3. На остальные (младшие) разряды этого входа сумматора 16 подаются нули (эти разряды заземлены). С помощью АЦП 15 ко дЬруются младшие разряды. Однако вследствие допустимости использования в блоке 1 быстродействующих, но низкоточных элементов сравнения возможно , что в число обрабатываемых на данном этапе разворачивания эталона первой ступс1115 -каналов попадут сигналы превышающие по величине один квант эталона первой ступени. Поэтому АЦП 15 должен иметь шкалу, превышающую величину одного кванта с выхода АЦП 2. В этом случае сумматор 16 должен работать как на сложение, так и на вычитание. Поскольку код с выхода счетчика 3 всегда положительный .то код с выхода АЦП 15 формируется дополнительный, но, так как он подается на младшие разряды первого вхо-

0

5

0

5

0

5

0

5

0

5

да сумматора, то для сохранения правила сложения необходимо значение знакового разряда распространять на все старшие разряды. Следует отметить, что поскольку схема построена так, что эталон первой ступени кодирования всегда опережает по величине входные сигналы обрабатываемых второй ступенью каналов, то обычно за исключением редких случаев код на выходе АЦП 15 должен быть отрицательным и на старшие разряды первого входа сумматора распространяется единица.

Процесс кодирования устройства завершается с момента заполнения первого счетчика 3, выход которого по шине данных 17 поступает на вход дешифратора 32 в блоке 13. СигНсШ с выхода дешифратора 32 поступает через элемент 33 задержки на второй вход элемента И 28. Величина задержки вырабатывается из условия достаточности для срабатывания элементов сравнения в группе 1 на последней ступени разворачивания эталонной меры первой ступени преобразования. По завершении обработки последнего канала последней ступени развора чивания эталонной меры снимается сигнал Запрос 24 и с выхода элемент И 28 запустится одновибратор 41, с вьгхода которого уже независимо от состояния входа сформируется сигнал сброса, который через элемент НШ 34 действует аналогично сигналу системного сброса. Происходит установка устройства в исходное состояние.

Чтение данных из блока 9 памяти осуш;ествляется после анализа системной шины Готовность. Чтение можно осуществлять при наличии сигнала Готовность, так как в этом случае блок 9 памяти находится в режиме чтения, а его адресный вход через мультиплексор 8 подключен к адресному входу устройства. Синхронизация процедуры чтения осуществляется по системному синхровходу Чтение, сигнал с которого через элемент 1ШИ 30 поступает на выход Синхроимпульс 19 блока 13 и далее на синхровход блока 9 памяти.

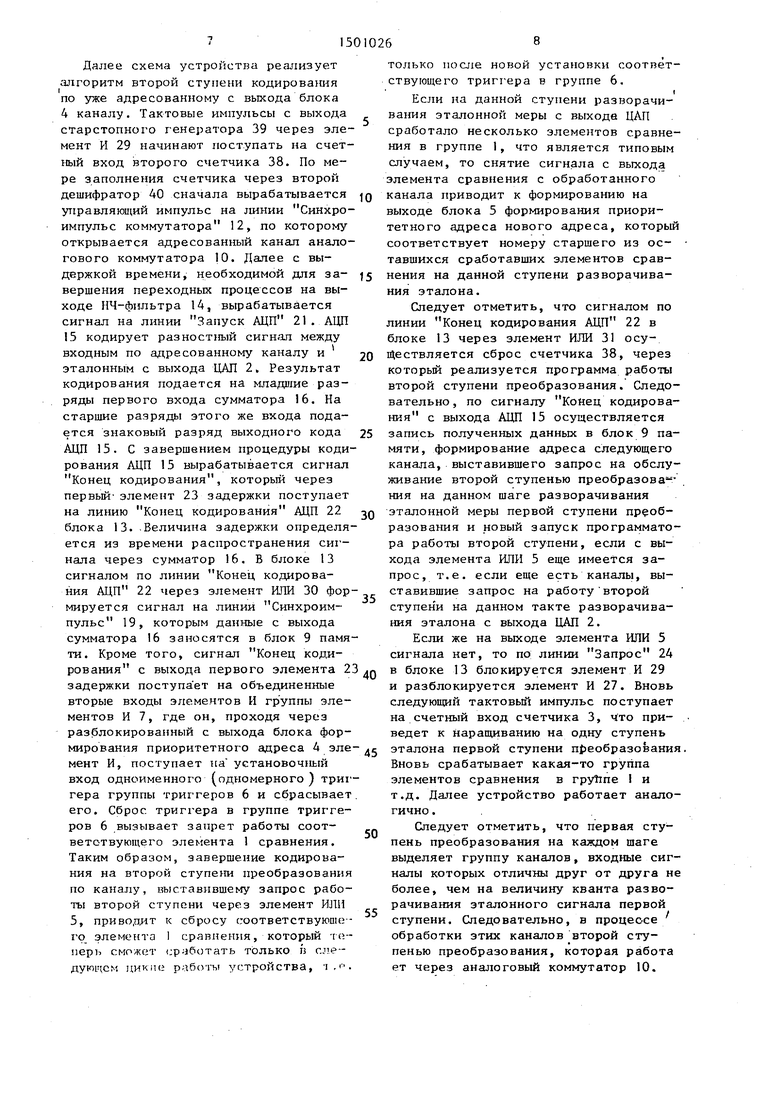

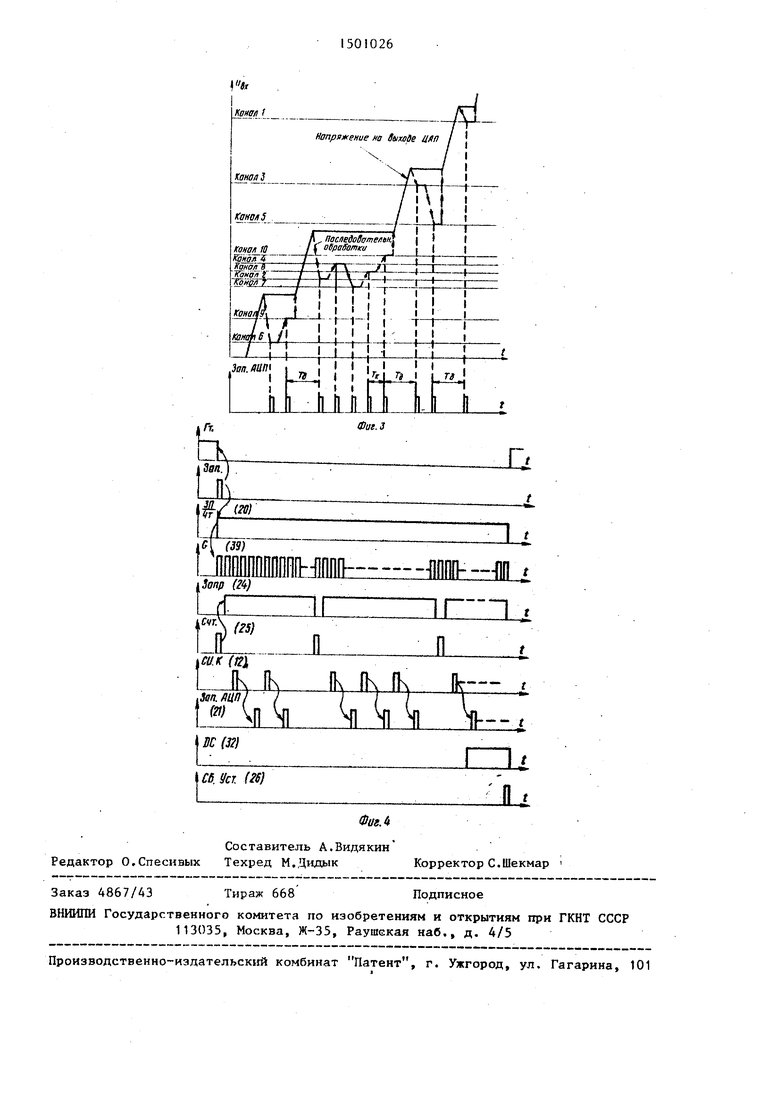

На фиг.З приведена временная диаграмма процедуры кодирования по каналам. .Стрелками показана последова- тельтюсть обработки кина.пя второй ступенью преобразования. Индексами

Т и Т обозначены соответственно время смены диапазона при переходе от одной степени разворачивания эталонной меры к другой и время кодирования по каналу второй ступенью преобразования .

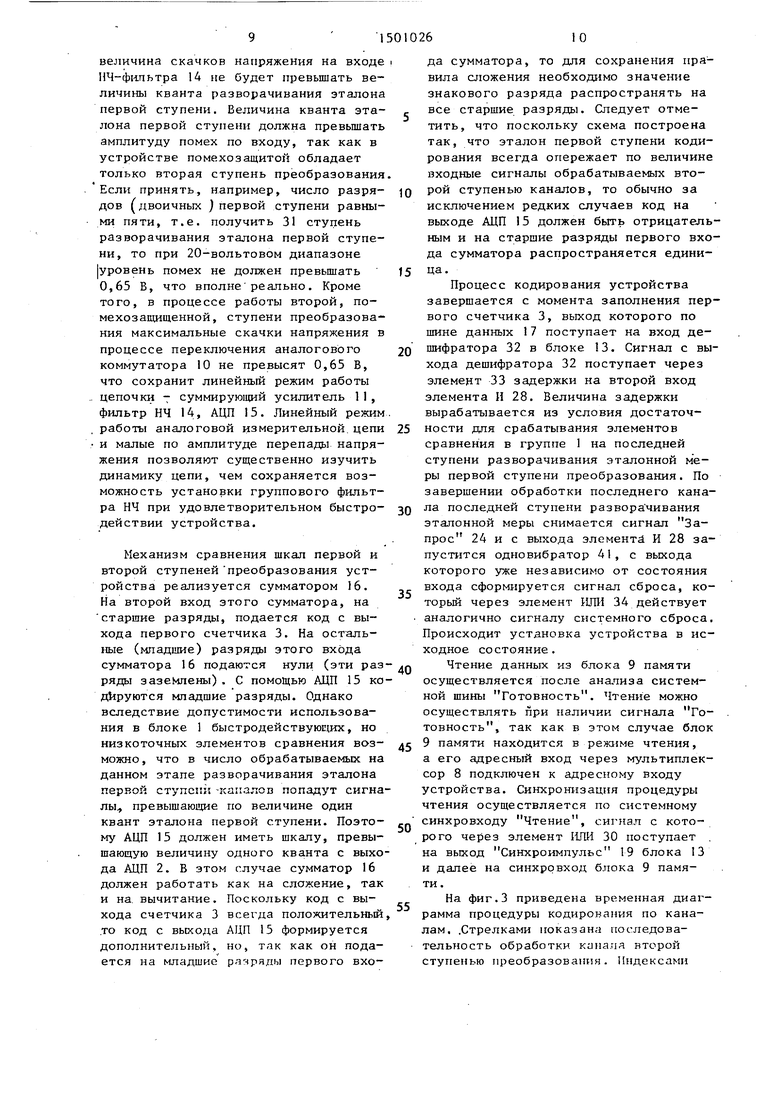

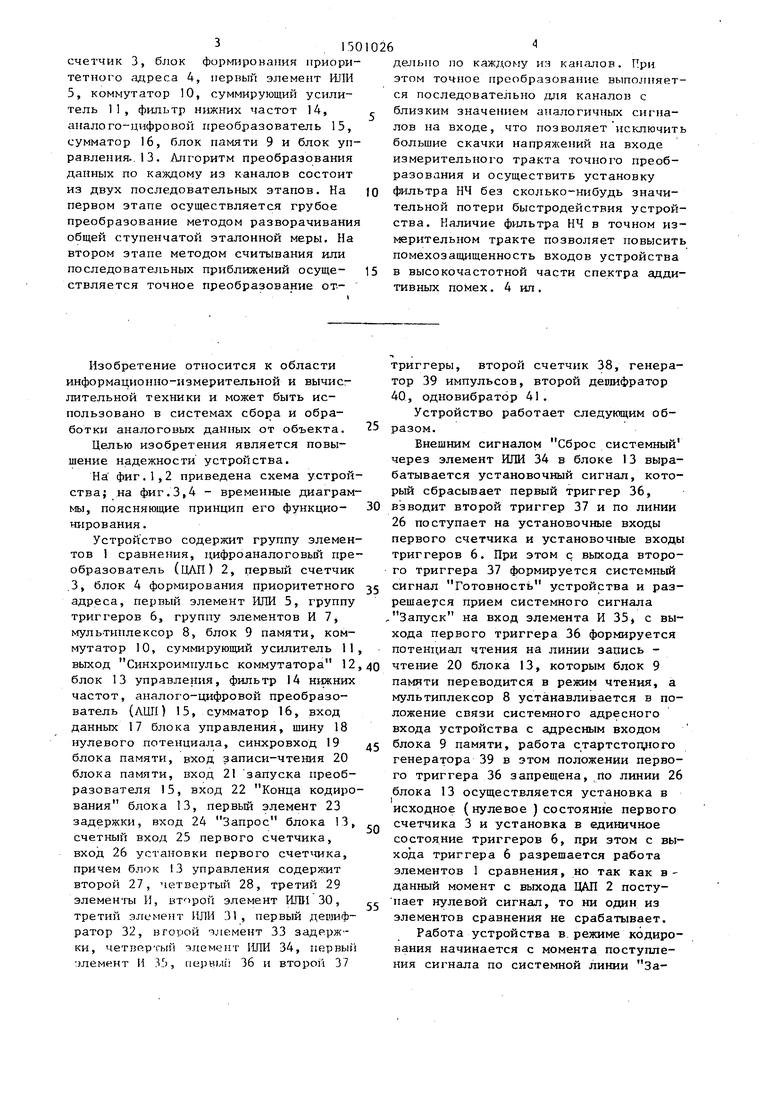

На фиг.4 приведена временная диаграмма работы блока 13. В скобках (цифрами) обозначены номера линий и блоков в соответствии с обозначениями на фиг.I и 2.

Дпя выявления преимуществ данного устройства по сравнению с прототипом сравним их по уровню помехозащищен- ности на высоких частотах. Устройство-прототип не защищено от помех во всем диапазоне частот, вплоть до частоты fр, крторая ДПЯ сравнения элементной базы достигает значения (5...20) МГц. Дпя предпоженного устройства при числе каналов N 512 и средней точности (п 12), выбирая частоту полюса фильтра из компромиссных требований к быстродействию и защищенности равной fо 1000 f , получаем fp Ю Гц, а(, кГц. Следовательно в диапазоне от 100 кГц до 10 КГц (т.е. две декады ) уровень подавления помех по входу будет не хуже 20 дБ. В диапазоне 10-100 кГц уровень подавления помех будет возрастать от 3 до 20 дБ. В то же время при указанных условиях время установления сигнала на выходе группового фильтра не превысит 10 мк Ске. Такое время может быть вполне компенсировано использованием быстродействующего АЦП (например, АЦП считывания ). Следовательно, устройство при равном быстродействии на половине частотного диапазона, воспринимаемого устройством, аддитивных помех имеет уровень защищенности по входу на 20 дБ более, чём устройство-про- тотип. Устройство может быть реализовано на микросхемах серий 594, 521, 574, 544, I 108, ИЗО, I 133.

Формула изобретения

Устройство для ввода аналоговой информации, содержащее группу элементов сравнения, группу триггеров-, группу элементов И, дифро аналог о вьпЧ преобразователь, первый счетчик, блок формирования приоритетного адреса, первый элемент ИЛИ, мультиплексор, блок памяти, блок управления, причем

д

5

0

0

5

первые информационные входы элементов сравнения являются информационными входами устройства, вторые информационные входы элементов ср авнения подключены к выходу цифроаналогового преобразователя, входы которого соединены с выходами первого счетчика, / выходы элементов сравнения подключены к входам блока формирования приоритетного адреса и входам первого элемента ИЛИ, стробирукяцие входы элементов сравнения соединены с выхода- ми соответствующих триггеров группы, выходы элементов И группы соединены с R-входами соответствующих триггеров группы, первые входы элементов И группы соединены с соответствующими выходами единичного позиционного кода блока формирования приоритетного адреса, двоично-кодированный выход которого подключен к первому информационному входу мультиплексора, выход которого соединен с адресным входом блока памяти, выход которого является информационным выходом устройства, отличающееся тем, что, с целью повышения надежности устройства, в него введены аналоговый коммутатор, суммирующий усилитель, аналого-цифровой преобразователь, сумматор, первый элемент задержки, фильтр нижних частот, а блок управления содержит первый и второй триггеры, второй элемент задержки, второй, третий и четвертый элементы ИЛИ, первый и второй дешифраторы, одновибратор, с первого по четвертый элементы И, второй счетчик, генератор импульсов, причем информационные входы коммутатора соединены с информационными входами устройства, выход коммутатора соединен с вычитающим . входом суммирующего усилителя, суммирующий вход которого подключен к выходу цифроаналогового преобразователя, адресный вход коммутатора соединен с двоично-кодированным выходом блока формирования приоритетного адреса, синхронизирующий вход коммутатора подключен к первому выходу второго дешифратора, выход суммирующего усилителя через фильтр нижних частот подключен к информационному входу аналого-цифрового преобразователя, информационные выходы которого соединены с первой группой входов сумматора, вторая группа входов которого подключена к выходу знакового разряда аналого-цифрового преобразователя, третья группа входов сумматора подключена к выходу первого счетчика и входу пбрвого дешифратора, четвертая группа входов сумматора соединена с пшной нулевого потенциала, выход сумматора подключен к информационному входу блока памяти, синхровход которого соединен с выходом второго элемента ИЛИ, вход записи-чтения блока памяти подключен к управляющему входу мультиплексора и выходу первого триггера, второй информационный вход мультиплексора является адресным вхо- 15 дом устройства, управляющий вход аналого-цифрового преобразователя соединен с вторым выходом второго дешифратора, выход Конец кодирования

lUlH, первый вход второго элемента Ш1 является входом чтения устройства, входом запроса которого является пер вый вход первого элемента И, второй вход которого соединен с вькодом вто рого триггера и является выходом готовности устройства, установочным входом которого является второй вход четвертого элемента ИЛИ, первьш вход которого соединен с выходом одновибратора, вход которого подключен к вы ходу четвертого элемента И, второй вход которого через второй элемент задержки подключен к выходу первого дешифратора, выход первого элемента И соединен с первым входом третьего элемента ИЛИ, S-входом первого триггера и R-входом второго триггера, вы

10

аналого-цифрового преобразователя че- 20 х°Д четвертого элемента ИЛИ подклюрез первый элемент задержки подключен к вторым входам элементов И группы и вторым входам второго и третьего элементов ИЛИ, выход первого элемента . РШИ соединен с первыми инверсными 25 входами второго и четвертого элементов И и первым входом третьего элемента И, счетный вход первого счетчика подключен к выходу второго элеменчен к S-входу второго триггера и R-входу первого триггера, выход кото рого подключен к входу генератора импульсов, выход которого соединен с вторыми входами второго и третьего элементов И, выход третьего элемента И подключен к счетному входу второго счетчика, установочный вход которого соединен с выходом третьего

та И, установочный вход первого счет- JQ элемента ИЛИ, выходы второго счетчичика соединен с S-входами триггеров группы и выходом четвертого элемента

ка соединены с входами второго дешиф ратора.

151026

lUlH, первый вход второго элемента Ш1И является входом чтения устройства, входом запроса которого является первый вход первого элемента И, второй вход которого соединен с вькодом второго триггера и является выходом готовности устройства, установочным входом которого является второй вход четвертого элемента ИЛИ, первьш вход которого соединен с выходом одновиб ратора, вход которого подключен к выходу четвертого элемента И, второй вход которого через второй элемент задержки подключен к выходу первого дешифратора, выход первого элемента И соединен с первым входом третьего элемента ИЛИ, S-входом первого триггера и R-входом второго триггера, вы10

х°Д четвертого элемента ИЛИ подключен к S-входу второго триггера и R-входу первого триггера, выход которого подключен к входу генератора импульсов, выход которого соединен с вторыми входами второго и третьего элементов И, выход третьего элемента И подключен к счетному входу второго счетчика, установочный вход которого соединен с выходом третьего

элемента ИЛИ, выходы второго счетчика соединены с входами второго дешифратора.

Коми f

Ийпрягквиие на выходе U/lf

МНОЙ 3

kSanp (г)

1Г-I

| Устройство для ввода аналоговой информации | 1985 |

|

SU1260966A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для ввода информации | 1983 |

|

SU1151946A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Многоканальная система ввода аналоговой информации | 1984 |

|

SU1247857A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-08-15—Публикация

1988-03-15—Подача