чем синхр.овход блока соединен с пер--вым входом первого элемент сложения по модулю два, второй вход которого соединен с выходом первого ключа, шиной электропитания блока, выходом второго ключа и первьом входом второго элемента сложения по модулю два, второй вход которого соединен с информационным входом блока, выход которого соединен с выходом первого элемента НЕ, вход первого ключа соединен с входом второго ключа, входом третьего ключа, информационным входом второго триггера и шиной нулевого потенциала блока, выход третьего ключа соединен с шиной электропитания блока и единичным входом .первого триггера, синхровход которого соединен с выходом первого элемента И-НЁ, первый вход которого соединен с выходом первого

триггера и вх9дом первого элемента НЕ, второй вход первого элемента И-Н соединен с выходом элемента И, первы вход которого соединен с выходом второго элемента НЕ, вход которого соединен с выходом второго элемента сложения rto модулю два и синхровходом второго триггера, нулевой вход которого соединен с шиной электропитания, блока и нулевым входом первого триггера, информационный вход которого соединен с выходом первого элемента сложения по модулю два и первым входом второго элемента И-НЕ, выход которого соединен с единичным входом второго триггера, инверсный выход которого соединен с вторым входом элемента И и с вторым входом второго элемента И-НЕ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых объектов | 1986 |

|

SU1319037A2 |

| Устройство для контроля аналоговых объектов | 1986 |

|

SU1397941A1 |

| Цифровой адаптивный линейный интерполятор | 1982 |

|

SU1095189A1 |

| СИСТЕМА ПЕРЕДАЧИ ИНФОРМАЦИИ | 1991 |

|

RU2043659C1 |

| Устройство для локализации неисправностей | 1980 |

|

SU903888A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1104590A1 |

| Устройство для ввода информации | 1982 |

|

SU1080132A1 |

| Устройство для сопряжения вычислительной машины с аппаратурой передачи данных | 1989 |

|

SU1679492A1 |

| Устройство для контроля цифровых объектов | 1981 |

|

SU1005064A1 |

| УСТРОЙСТВО АДАПТИВНОГО КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ | 2000 |

|

RU2169431C1 |

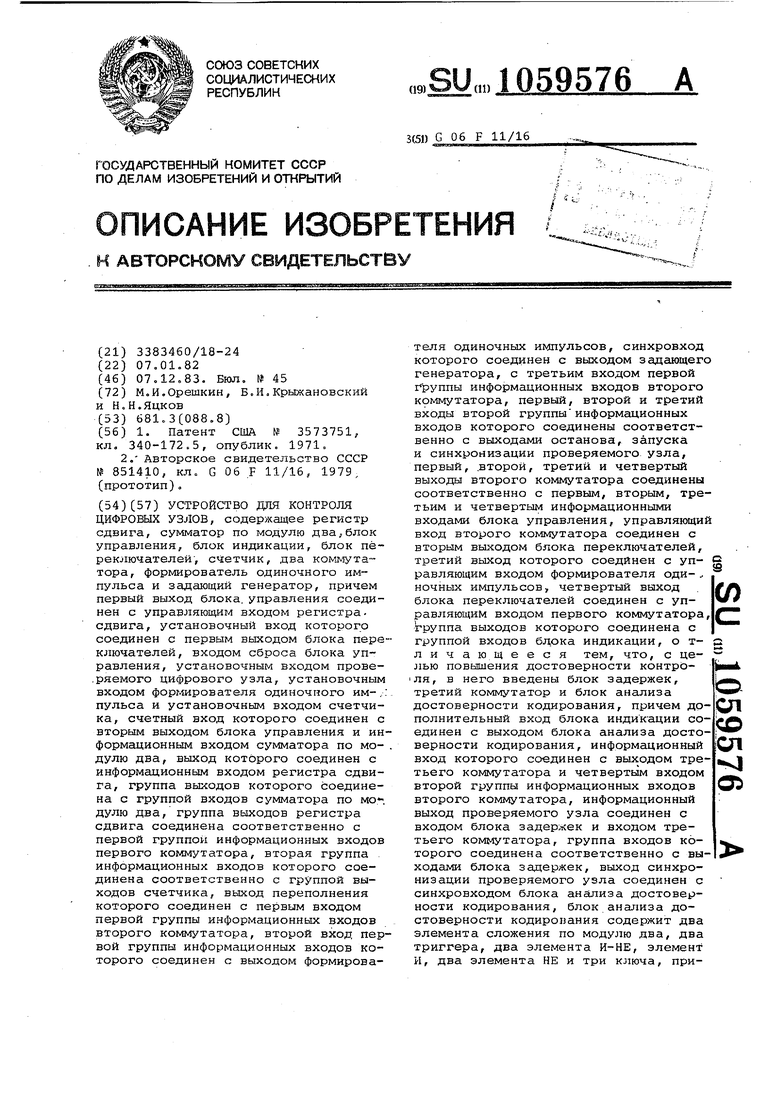

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЦИФРОВЫХ УЗЛОВ, содержащее регистр сдвига, сумматор по модулю два,блок управления, блок индикации, блок переключателей, счетчик, два коммутатора, формирователь одиночного импульса и задающий генератор, причем первый выход блока, управления соединен с управляющим входом регистра. сдвига, установочный вход которого соединен с первым выходом блока переключателей, входом сброса блока управления, установочным входом прове.ряемого цифрового узла, установочным входом формирователя одиночного им-,: пульса и установочным входом счетчика, счетный вход которого соединен с вторым выходом блока управления и информационным входом сумматора по мо-. дулю два, выход которого соединен с информационным входом регистра сдвига, группа выходов которого соединена с группой входов сумматора по . дулю два, группа выходов регистра сдвига соединена соответственно с первой группой информационных входов первого коммутатора, вторая группа информационных входов которого соединена соответственно с группой выходов счетчика, выход переполнения которого соединен с первым входом первой группы информационных входов второго коммутатора, второй вход первой группы информационных входов которого соединен с выходом формирователя одиночных импульсов, синхровход которого соединен с выходом задающего генератора, с третьим входом первой Группы информационных входов второго коммутатора, первьлй, второй и третий входы второй группы информационных входов которого соединены соответственно с выходами останова, запуска и синхронизации проверяемого узла, первый, .второй, третий и четвертый выходы второго коммутатора соединены соответственно с первым, вторым, третьим и четвертым информационными входами блока управления, управлякяций вход второго коммутатора соединен с вторым выходом блока переключателей, третий выход которого соединен с уп- О $5 равляющим входом формирователя оди(Л ночных импульсов, четвертый выход блока переключателей соединен с управляющим входом первого коммутатора, группа выходов которого соединена с группой входов бдока индикации, о т- ff личающееся тем, что, с це- лью повышения достоверности контро1ЛЯ, в него введены блок задержек, третий коммутатор и блок анализа ел достоверности кодирования, причем дополнительный вход блока индикации единен с выходом блока анализа досто01 верности кодирования, информационный вход которого соединен с выходом тре тьего коммутатора и четвертым входом 05 второй группы информационных входов второго коммутатора, информационный выход проверяемого узла соединен с входом блока задержек и входом третьего коммутатора, группа входов которого соединена соответственно с выходами блока задержек, выход синхронизации проверяемого узла соединен с синхровходом блока анализа достоверности кодирования, блок анализа достоверности кодирования содержит два элемента сложения по модулю два, два триггера, два элемента И-НЕ, элемент И, два элемента НЕ и три ключа, при

Изобретение относится к вычислительной технике и может быть использовано для кодирования логического, состояния цифровых систем, их контроля и поиска в них неисправных компонентов (соединительных элементов, микросхем, типовых элементов замены и модулей, -устройств и подсистем и т.д. ).

Известно устройство, предназначенное для обнаружения неисправных модулей в цифровых системах, содержащее общий с цифровым объектом генератор тактовой частоты и анализирующее ограниченное раз и навсегда выбранное число контрольных точек цифрового объекта (выбранные точки жестко связаны с входом устройства ) 1 J.

Недостатками данного устройства являются невозможность использования его в наиболее широко распространенных асинхронных системах, а также невозможность осуществлять диагностику с точностью до типового элемента замены в сложных цифровых объектах, диагностика которых требует анализа относительно большого и не всегда предсказуемого числа контрольных точек.

Наиболее близким к предлагаемому является устройство для контроля «цифровых объектов,, содержащее регистр сдвига, сумматор, блок управления, блок индикации, пульт управления, первый коммутатор, счетчик, формирователь одиночного импульса, задающий генератор и второй коммутатор, причем первый и второй входы счетчика соединены соответственно с первым выходом

2

блока управления, первый выход счетчика соединен .с первым входом перво го коммутатора, первый выход блоКа управления соединен с первыми входами счетчика и сумматора, выход которого соединен с первым входом регистра сдвига, второй выход блокауправ-. ления соединен с вторым входом регис.тра сдвига, первый выход которого

0 соединен с вторым входом сумматора,, первый выход пульта управления соединен с третьим входом регистра сдвига и пятым входом блока управления, второй и третий входы первого комму5 татора соединены соответственно с

вторым выходом регистра сдвига и вторым выходом пульта управления, а выход - с входом блока индикации, второй выход счетчика соединен с первым входом второго коммутатора, второй вход которого соединен с третьим выходом пульта управления, первый выход которого соединен с входом цифрового объекта, третий, четвертый, пятый и шестой входы второго коммутатора соединены с группой выходов цифрового объекта, а первый, второй, третий и четвертый выходы второго коммутатора соединены соответственно с первым, вторым, третьим и четвертым входами блока управления, выход задающего генератора соединен с седьмьам и восьмым входами второго коммутатора и первым входом формирователя одиночного импульсс, второй и третий входы

5 которого соединены соответственно с первым и четвертым выходами пульта управления, а выход - с девятым входом второго коммутатора. Известное устройство позволяет снимать двоичный сигнал с любого ко такта, цифрового объекта, построенно го на элементной базе с любой степе нью интеграции, и осуществлять диаг 41остику как синхронных, так и асинхронных цифровых объектов с любой степенью диагностического разрешени Оно наделено средствами эффективного самоконтроля СзJ. Однако известное устройство не исключает влияния на результат преобразования случайных сбоев, помех и переходных процессов. Следует отметить , что только один ошибочный результат преобразования, например, при поиске неисправного компонента может привести к его неверному определению. Для того, чтобы избежать влияния случайных сбоев и помех,приходится осуществлять в каждой контрольной точке объекта повторное коди рование ( преобразование ) двоичного сигнала, что приводит к удвоенным потерям времени. Однако и повторное кодирование не позволяет избежать недостоверного результата в случаях устойчивого совпадения фронта импуль са синхронизации и фронта импульса кодируемого сигнала. Цель изобретения - повышение достоверности контроля. Поставленная цель достигается тем, что в устройство для контроля цифровых узлов, содержащее регистр сдвига сумматор по модулю два,блок управления, блок индикации, блок переключателей, счетчик, два коммутатора, формирователь одиночного .импульса и задающий генератор, причем первый выход блока управления соединей с управляющим входом регистра сдвига, установочный вход которого соединен с первым выходом блока переключателей, .входом сброса блока уп равления, установочным входом проверлемого цифрового узла, установочным входом формирователя одиночного импульса и установочным входом счетчика, счетный вход которого соединен с вторым выходом блока управления и информационным входом сумматора по модулю два, выход которого соединен с информационньдм входом регистра сдвига, группа выходов которого соединена с группой входов сумматора по модулю два, группа выходов регистра сдвига соединена соответственно с первой группой информационных входов первого коммутатора, вторая группа информационных входов которого соеди нена соответственно с группой выходо счетчика, выхода переполнения которо го соединен с первым входом первой группы информационных входов второго коммутатора, второй вход первой груп пы информационных входов которого оединен с выходом формирователя одиочных импульсов, синхровход которого соединен с выходом задаквдего генеатора, с третьим входом первой группы информационных входов второго комутатора, первый, второй и третий входы второй группы информационных входов которого соединены соответственно с выходами останова, запуска и синхронизации проверяемого узла, первый, второй, третий и четвертый выходы второго коммутатора соединены соответственно с первым, вторым,треЬгьим и четвертым информационными входами блока управления, управлякядий вход второго коммутатора соединен с вторым выходом блока переключателей, третий выход которого соединен с управляющим входом формирователя одиночных импульсов, четвертый выход блока переключателей соединен с управляющим входом первого коммутатора, группа выходов которого соединена с группой входов блока индикации, введены блок задержек, третий коммутатор и. блок анализа достоверности кодирования, причем дополнительный вход блока индикации соединен с выходом блока анализа достоверности кодирования, информационный вход которого соединен с выходом третьего коммутатора и четверты1у1 входом второй группы информационных входов второго коммутатора, информационнЕлй выход проверяемого узла соединен с входом блока задержек и входом третьего коммутатора, группа входов которого соединена соответственно с выходами блока задержек, выход синхронизации проверяемого узла соединен с синхровходом блока анализа достоверности кодирования, блок анализа достоверности кодирования содержит два элемента сложения по модулю два, два триггера, два элемента И-НЕ, элемент И, два элемента НЕ и три ключа, причем синхровход блока соединен с первым входом первого элемента сложения по модулю два, второй вход которого соединен с выходом первого ключа, шиной электропитания блока, выходом второго ключа и первым входом второго элемента сложения п© модулю два, второй вход которого соединен с информационным входом блока, выход которого соединен с выходом первого элемента НЕ, вход первого ключа соединен с входом второго ключа, входом третьего ключа, информационным входомвторого триггера и шиной нулевого потенциала блока, выход третьего ключа соединен с шиной электропитания блока и единичным входом первого триггера, синхровход которого соединен с выходом первого элемента И-НЕ, первый вход которого соединен с выходом первого триггера и входом пер-

вого элемента НЕ, второй вход первого элемента И-НЕ соединен cf выходом элемента И, первый вход которого соединен с выходом- второго элемента НЕ, вход которого соединен с выхо.дом второго элемента.сложения по мО дулю два и синхровходом второго триггера, нулевой вход которого соединен с шиной электропитания блока и нулевым входом первого триггера, информационный вход которого соединен с выходом первого элемента сложения по модулю два и первым входом второго элемента И-НЕ, выход которого соединен с единичным входом второго триггера, инверсный выход которого соединен с вторым входом элемента И и вторым входом второго элемента И-НЕ

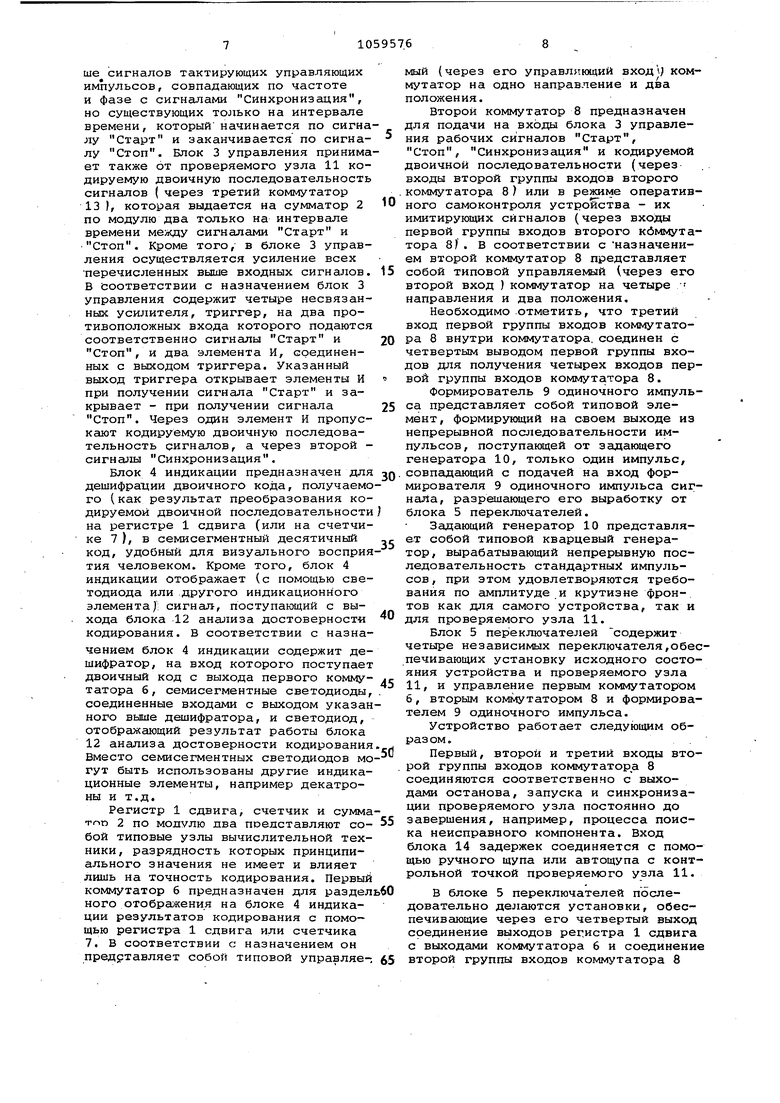

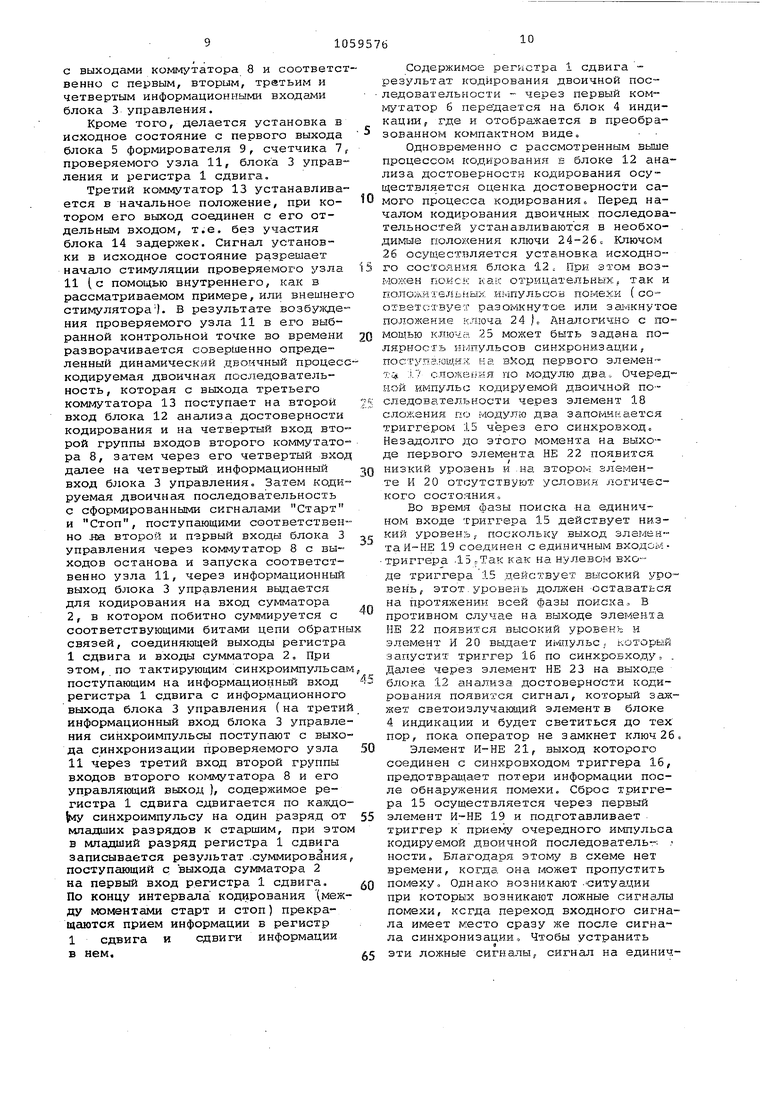

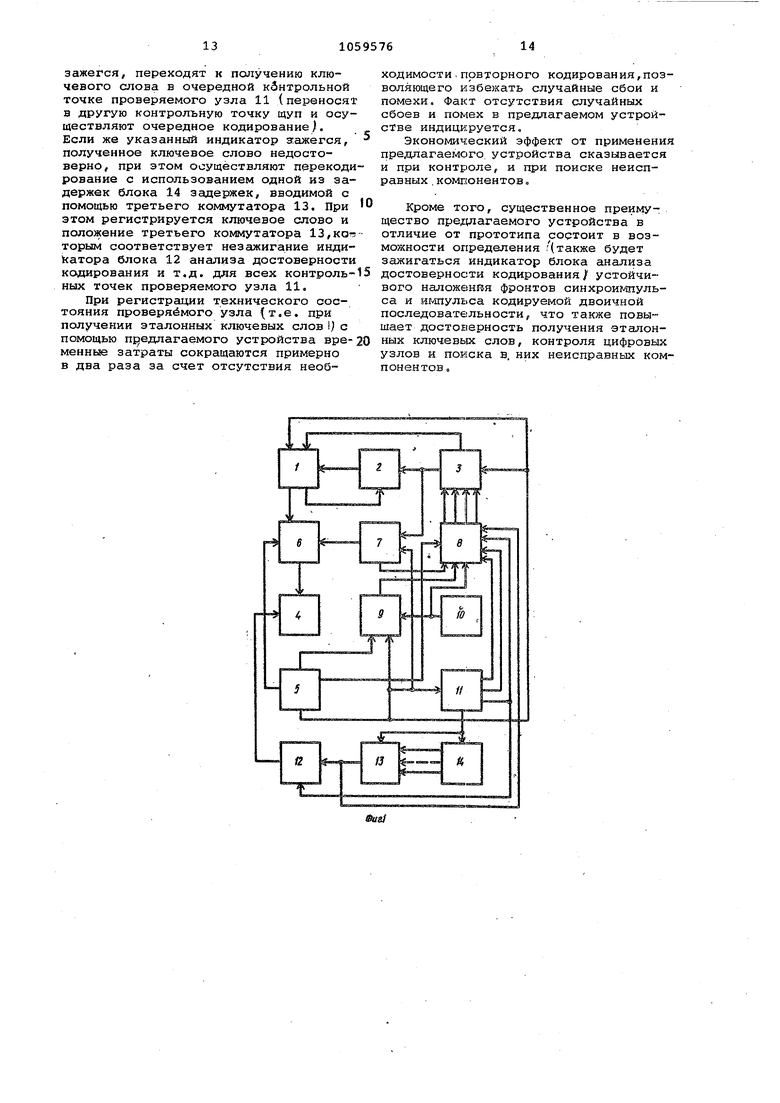

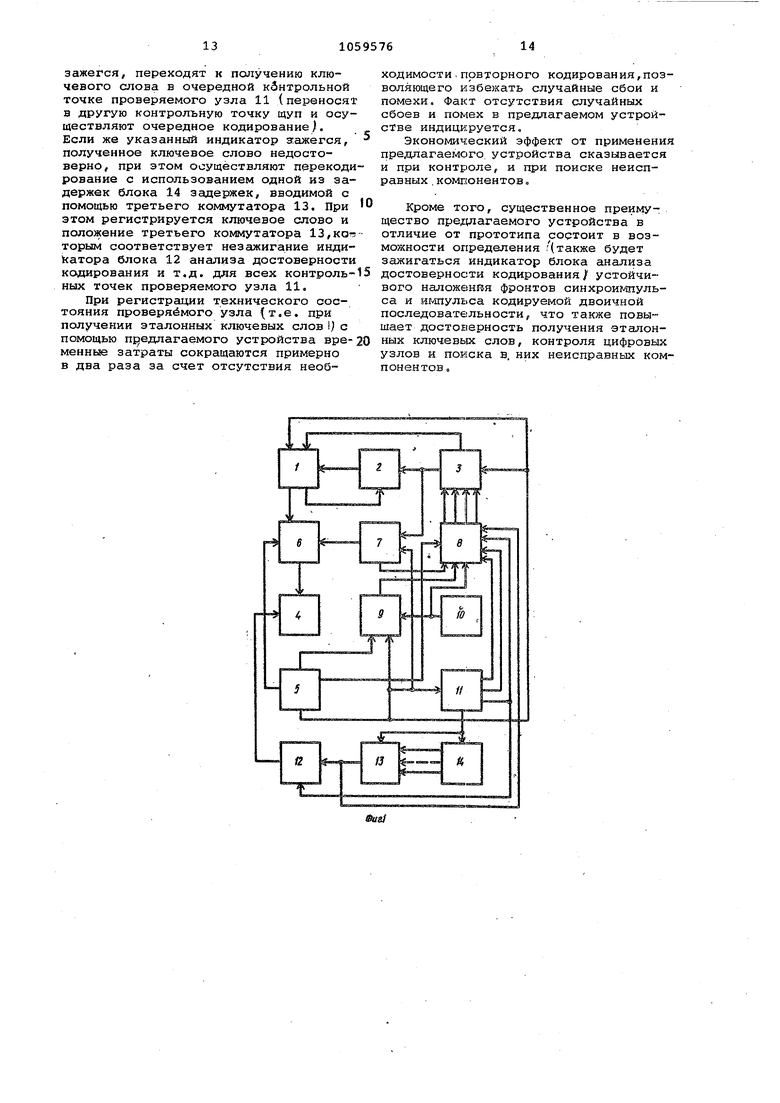

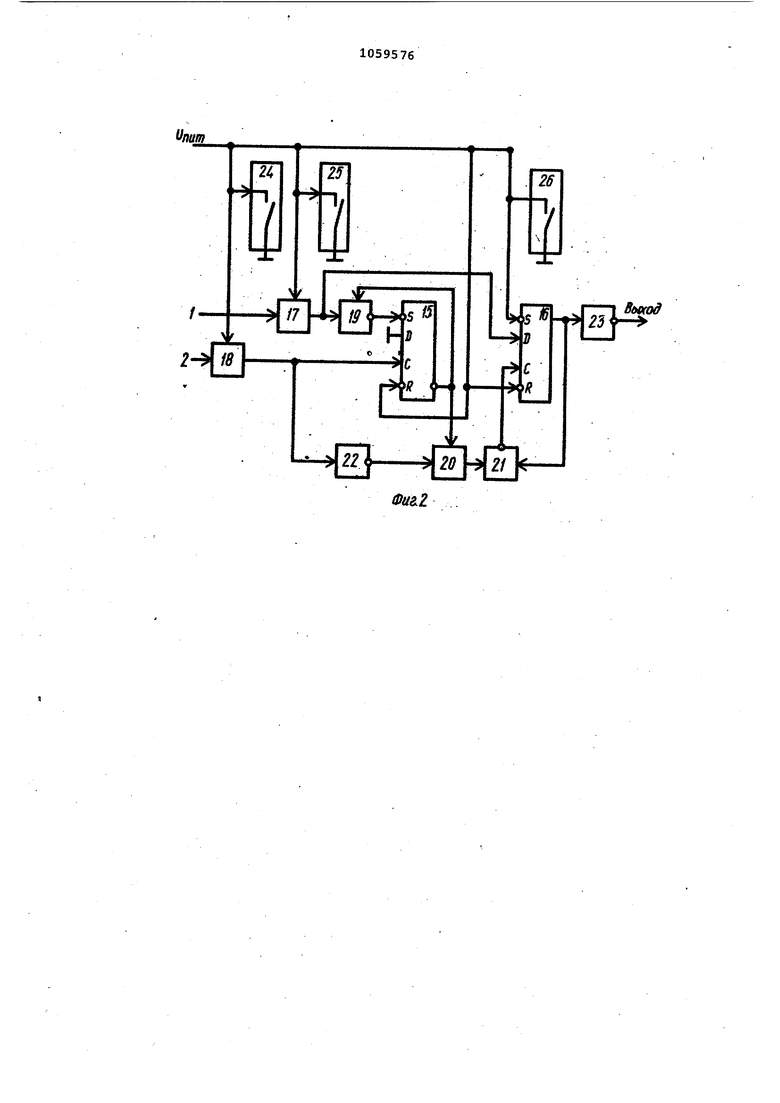

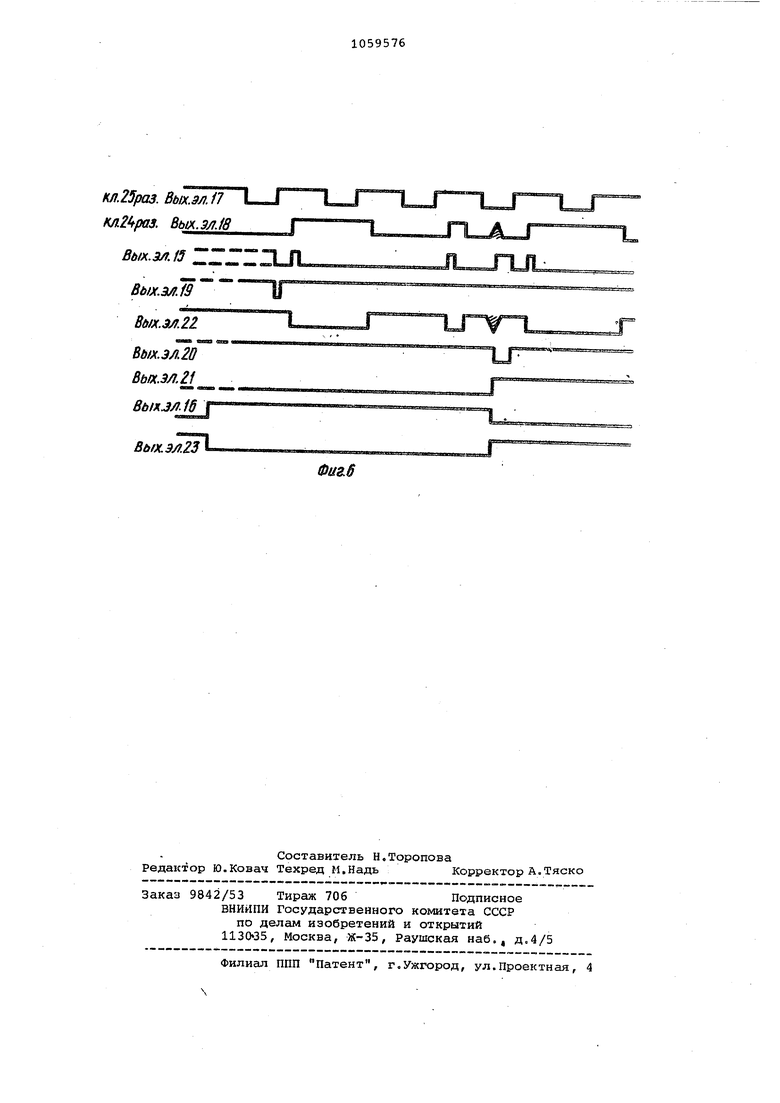

На фиг.1 представлена блок-схема устройства для контроля цифровых узлов j на .2 - пример реализации рлока анализа достоверности кодирования; на фиг.З - временная диаграмма работы блока анализа достоверности ,кодирования при наличии случайной положительной помехи, совпадающей с уровнем логической единицы сигнала синхронизации; на фиг,4-6 -. временная диаграмма работы блока анализа достоверности кодирования при наличии случайной положительной помехи, совпадающей с уровнем логического нуля сигнала синхронизации, при наличии случайной отрицательной помехи, совпадгиощей с уровнем логического нуля сигнала синхронизации, и при наличии случайной отрицательной помехи, совпс1дающей с уровнем логической единицы сигнала синхронизации соответственно.

Устройство содержит регистр 1 сдв га, сумматор 2 по модулю два, блок 3 управления, блок 4 индикации, блок 5 переключателей, первый коммутатор 6, счетчик 7, второй коммутатор 8, формирователь 9 одиночного импульса, задающий генератор 10, проверяегЛлй узел 11, который не входит в состав устройства и приводится лишь для пояснения работы устройства, блок 12 анализа достоверности кодирования, третий коммутатор 13 и блок 14 задер жек.

Блок 12 анализа достоверности кодирования содержит триггеры 15 и 16, элементы 17 и 18 сложения по модулю два, элемент И-НЕ 19, элемент И 20, элемент И-НЕ 21, элементы НЕ 22 и 23.и ключи 24-26,

Сущность предлагаемого технического решения состоит в оперативном об.наружении влияния на результат кодирования случайных сбоев, помех или совпадений фронтов импульсов синхрониэ ции с импульсами кодируемсэй двоичной последовательности, С этой целью на синхровхрд и информационный

входы блока анализа достоверности кодирования подают последовательность синхроимпульсов и кодируемую двоичную последовательность, где осуществляется с высокой точностью анализ фронтов указанных сигналов (обнаруживается помеха длительностью несколько наносекунд ). При обнаружении помехи полученный результат код: ирования не использу ется (осуществляется перекодирование), если же перекодирование устойчивО приводит к обнаружению ошибки, то это значит, что ошибка является следствием не случайных помех, сбоя, а устойчивого совпадения фронтов синхроимпульсов и кодируемой двоичной последовательности. В этом случае оператор через третий коммутатор вводит задержку и добивается устранения нежелательного совпадения. В дальнейшем используется результат кодирования, полученный с использованием определенной задержки.

Блок 12 анализа достоверности кодирования предназначен для выявления критических ситуаций, при которых, например, фронтсинхроимпульса (на синхровходе блока 12 ) совпадает с фронтом импульса кодируемой двоичной последовательности (на информационном Ьходе блока 12/, при этомна выходе блока 12 анализа достоверности коди рования формируется сигнал, который зажигает индикационный элемент на блоке 4 индикации.

Третий коммутатор 13 предназначен для возможности подачи кодируе-гмой двоичной последовательности на вход второго коммутатора 8 и информационный вход блока 12 анализа достоверности кодирования с любого из выходов блока 14 задержек. Для этого в качестве.третьего коммутатора

13может быть использован любой типовой комм5 -татор на одно направление и на несколько положений по числу выходов блока 14 задержек. Переключение коммутатором 13 осуществляется вручную.

Блок 14 задержек предназначен для искусственного сдвига во времени кодируемой двоичной последовательности, поступающей на вход блока 14 задержек, относительно последовательности .синхроимпульсов. В общем случае.блок.

14задержек содержит h типовых двухполюсных элементов задержек с различным временем задержки, входы которых соединены между собой и представляют собой вход блока 14 задержек, а выходы образуют п выходов блока 14 задержек.

Блок 3 управления предназначен дЛя приема от проверяемого узла 11 Счерез второй коммутатор 8 ) управляющих сигналов Старт, Стоп и Синхронизация и формирования из указанных выше сигналов тактирующих управляющих импульсов, совпадающих по частоте и фазе с сигналами Синхронизация, но существующих только на интервале времени, который начинается по сигна лу Старт и заканчивается по сигна лу Стоп. Блок 3 управления принима ет также от проверяемого узла 11 кодируемую двоичную последовательность сигналов ( через третий коммутатор 13 I, которая выдается на сумматор 2 по модулю два только на интервале времени между сигналами Старт и . Кроме того, в блоке 3 управления осуществляется усиление всех перечисленных выше входных сигналов. В Соответствии с назначением блок 3 управления содержит четыре несвязанных усилителя, триггер, на два противоположных входа которого подаются соответственно сигналы Старт и Стоп, и два элемента И, соединенных с выходом триггера. Указанный выход триггера открывает элементы И при получении сигнала Старт и закрывает - при получении сигнала Стоп. Через один элемент И пропускают кодируемую двоичную последовательность сигналов, а через второй сигналы Синхронизация. Блок 4 индикации предназначен для дешифрации двоичного кода, получаемо го (как результат преобразования кодируемой двоичной последовательности на регистре 1 сдвига (или на счетчике 7 ), в семисегментный десятичный код, удобный для визуального восприя тия человеком. Кроме того, блок 4 индикации отображает (с помощью светодиода или другого индикационного элемента): сигнал, поступающий с выхода блока 12 анализа достоверности кодирования. В соответствии с назначением блок 4 индикации содержит дешифратор, на вход которого поступает двоичный код с выхода первого коммутатора б, семисегментные светодиоды, соединенные входами с выходом указан ного выше дешифратора, и светодиод, отображающий результат работы блока 12 анализа достоверности кодирования Вместо семисегментных светодиодов мо гут быть использованы другие индикационные элементы, например декатроны и т.д. Регистр 1 сдвига, счетчик и сумма Ti-ir) 2 по МОДУЛЮ два поедставляют собой типовые узлы вычислительной техники, разрядность которых принципиального значения не имеет и влияет лишь на точность кодирования. Первый коммутатор 6 предназначен для раздел ного отображения на блоке 4 индикации результатов кодирования с помощью регистра 1 сдвига или счетчика 7. В соответствии с назначением он представляет собой типовой управляе-, мый {через его управляющий коммутатор на одно направление и два положения. Второй коммутатор 8 предназначен для подачи на входы блока 3 управления рабочих сигналов Старт, Стоп, Синхронизация и кодируемой двоичной последовательности (через входы второй группы входов второго коммутатора 8) или в режиме оперативного самоконтроля устройства - их имитирующих сигналов (через входы первой группы входов второго кйммутатора 8). В соответствии с назначением второй коммутатор 8 представляет собой типовой управляемый (через его второй вход ) коммутатор на четыре направления и два положения. Необходимо отметить, что третий вход первой группы входов коммутатора 8 внутри коммутатора, соединен с четвертым выводом первой группы входов для получения четырех входов первой группы входов коммутатора 8. Формирователь 9 одиночного импульса представляет собой типовой элемент , формирующий на своем выходе из непрерывной последовательности импульсов, поступающей от задающего генератора 10, только один импульс, совпадающий с подачей на вход формирователя 9 одиночного импульса сигнала, разрешающего его выработку от блока 5 переключателей. Задающий генератор 10 представляет собой типовой кварцевый генератор, вырабатывающий непрерывную последовательность стандартных импульсов, при этом удовлетворяются требования по амплитуде и крутизне фронтов как для самого устройства, так и для проверяемого узла 11. Блок 5 переключателей содержит четыре независимых переключателя,обеспечивающих установку исходного состояния устройства и проверяемого узла 11, и управление первым коммутатором б, вторым коммутатором 8 и формирователем 9 одиночного импульса. Устройство работает следующим образом.. Первый, второй и третий входы второй группы входов коммутатора 8 соединяются соответственно с выходами останова, запуска и синхронизации проверяемого узла постоянно до завершения, например, процесса поиска неисправного компонента. Вход блока 14 задержек соединяется с помощью pytiHoro щупа или автощупа с контрольной точкой проверяемого узла 11. В блоке 5 переключателей последовательно делаются установки, обеспечивающие через его четвертый выход соединение выходов регистра 1 сдвига с выходами коммутатора 6 и соединение второй группы входов коммутатора 8 с выходами коммутатора 8 и соответст венно с первым, вторим, третьим и четвертым информационными входами блока 3 управления. Кроме того, делается установка в исходное состояние с первого выхода блока 5 формирователя 9, счетчика 1 проверяемого узла 11, блока 3 управления и регистра 1 сдвига. Третий коммутатор 13 устанавливается в начальное положение, при котором его выход соединен с его отдельным входом, т.е. без участия блока 14 задержек. Сигнал установки в исходное состояние разрешает начало стимуляции проверяемого узла 11 (с помощью внутреннего, как в рассматриваемом примере, или внешнег стимулятора). В результате возбуждения проверяемого узла 11 в его выбранной контрольной точке во времени разворачивается совершенно определенный динамический двоичный процесс кодируемая двоичная последовательность, которая с выхода третьего комглутатора 13 поступает на второй вход блока 12 анализа достоверности кодирования и на четвертый вход второй группы входов второго ко1 мутатора 8, затем через его четвертый вход далее на четвертый информационный вход блока 3 управления о Затем кодируемая двоичная последовательность с сформированными сигналами Старт и Стоп, поступающими соответственно ла второй и первый входы блока 3 управления через коммутатор 8 с выходов останова и запуска соответственно узла 11, через информационный выход блока 3 управления выдается для кодирования на вход сумматора 2, в котором побитно суммируется с соответствующими битами цепи обратны связей, соединяющей выходы регистра Iсдвига и входы сумматора 2, При этом, по тактирующим синхроимпульсам поступающим на информационный вход регистра 1 сдвига с информационного выхода блока 3 управления (на третий информационный вход блока 3 управления синхроимпульсы поступают с выхода синхронизации проверяемого узла IIчерез третий вход второй группы входов второго коммутатора 8 и его управляющий выход ), содержимое регистра 1 сдвига сдвигается по каждоtviy синхроимпульсу на один разряд от лотадших разрядов к старшим, при этом в младший разряд регистра 1 сдвига записывается результат .суммирования поступающий с выхода сумматора 2 на первый вход регистра 1 сдвига, По концу интервала кодирования (между моментами старт и стоп) прекращаются прием информации в регистр 1 сдвига и сдвиги информации в нем. Содержимое регистра 1 сдвига результат кодирования двоичной последовательрюсти - через первый комм татор 6 передается на блок 4 индикащш, где и отображается в преобразованном компактном виде. Одновременно с рассмотренным выше процессом кодирования Е блоке 12 анализа достоверности кодирования осуществляется оценка достоверности самого процесса кодирования. Перед началом кодирования двоичных последовательностей устанавливаются в необходимые положения ключи 24-2б« Ключом 26 осуществляется установка исходного состояния блока 12, При зтом возможен noHcjc Kaic отрицательных, так и положительных и.шульсов помехи ( соотЕетствуег разомкнутое или затолкнутое положение ключа 24 Jo Аналогично с помощью ключе: 25 может быть задана полярность импульсов синхронизации, поступа.ющкх к а вКод первого элементу сложения по модулю два. Очередной импульс кодируемой двоичной последовательности через элемент 18 сложения ПС модулю два запогдинается триггером 15 через его синхровход Незадолго до этого момента на выходе первого элемента НЕ 22 появится низкий уровень и .на втором элементе И 20 отсутствуют условия логического состояния о Во время фазы поиска на единичном входе триггера 15 действует низкий уровень, поскольку выход элемента 19 соединен с единичным входомтриггера .15 ,Так как на нулевом вхо-де триггера 15 действует ВРЛСОКИЙ уровень, этот, уровень должен (оставаться на протяжении всей фазы поиска, В противном случае на выходе элемента НБ 22 появится высокий уровень и элемент И 20 выдает импульс который запустит триггер 16 по синхровходу . Далее через элемент НЕ 23 на выходе блока 12 анализа достоверности кодирования появится сигнал, который зажжет светоизлучаклдий элемент в блоке 4 индикации и будет светиться до тех пор, пока оператор не замкнет ключ 26 Элемент И-НЕ 21, выход которого соединен с синхровходом триггера 16, предотврав.1ает потери информации после обнаружения помехи. Сброс триггера 15 осуществляется через первый элемент И-НЕ 19 и подготавливает триггер к приему очередного импульса кодируемой двоичной последователь-. .ности Благодаря этому в схеме нет времени, когда, она может пропустить помеху. Однако возникают .ситуации при которых возникают ложные сигнэ.лы помехи, когда переход входного сигнала имеет место сразу же после сигнала синхронизации. Чтобы устранить эти ложные сигналы, сигнал на единичный вход триггера 16 подается через первый элемент 17 сложения по модулю два, который выполняет роль буфер ного каскада. Более подробно рассмотрим работу блока 12 с помощью временных диаграм фиг.3-6 . В верхней части фиг.З (верхние двенадцать сигналов ) представлена временная диаграмма работы блока 12 при отсутствии помехи, а в ее нижней части (нижние девять сигналов - при наличии случайной положительной поме хи (заштрихованный импульсj, совпада ющей с уровнем логической единицы сигнала синхронизации. Для всех рассматриваемыхчна фиг.4 случаев в качестве входных сигналов блока 12 выбраны одни и те же сигналы. Для упрощения временных диаграмм эти сигналы на фиг.4-6 не повторяются, а возникающая в цепи данных поме ха показана непосредственно наложенной на сигнал на выходе элемента 18 заиштрихованный импульс на фиг. 3-6 . Как следует из представленных времен ных диаграмм, любая опасная по ампли туде помеха обнаруживается блоком 12, если на выходе элемента 18 она представлена как положительный импульс, наложенный на уровень логического нуля данных и совпадающий с уровнем логического нуля синхроимпульса на выходе элемента 17. Именно с этой целью ключи 25 к 24 должны быть соответственно для случая, пред ставленного в нижней части фиг.З, разомкнут и замкнут, для случая, представленного на фиг.4, замкнут и замкнут, для случая, представленного на фиг.5, замкнут и разомкнут, и для случая, представленного на фиг.6, i .; разомкнут и разомкнут. После установки ключей 25 и 24 в положения, определяемые характером действующей в объекте помехи, путем кратковременного замыкания ключа 26 блок 12 устанавливается в исходное положение. При этом по перепаду сигнала от 1 к О (сигнал кл.26 на фиг.З) триггер 16 устанавливается в единицу, а на .выходе элемента НЕ 23 (на выходе блока 12) формируется сиг нал с уровнем логического нуля (вых.эл.1б и 23 на фиг.з. Этому неизменному состоянию соответствует отсутствие помехи в процес се контроля объекта (верхние двенадцать сигналов на фиг.З ). Общей логикой работы блока 12 также является то, что по каждому перепаду от О к 1 на синхровходе триггера 15 (вых.эл.18 /указанный триггер уста навливается в нулевое состояние, а через обратную связь, соединяющую вьоход триггера Ij через элемент И-НЕ 19 с его вторым входом, указанный триггер через короткое время (соизмеримое с временем срабатывания триггера } вновь устанавливается в единичное сортояние (вых.эл.15 и 19 на фиг. 3 ). В отсутствий .помехи на выходе элег мента И 20 сохраняется неизменным уровень логической единицы, так как входные сигналы указанного элемента (вых.эл.) 15 и 22 в верхней чаСти (фиг.З) находятся всегда в противофазеТ При этом на выходе элемента 21 сохраняется уровень логического нуля, так как на его входах остаются неизменными уровни логической единицы (вых.эл.16 и 20 -в верхней части фиг.З/. Триггер 16 сохраняет свое исходное состояние (вых.эл.16). При наличии помехи (нижняя часть фиг.З) в момент формирования ее переднего фронта (по пеоепаду от О к 1) через синхровход триггер 15 установится в нулевое состояние, а в единичное состояние установится через его единичный вход (через цепь .. . обратной связи )только в момент перепада от О Ч очередного синхроимпульса. В результате Этого на выходе элемента 20.вырабатывается отрицательный импульс,сформированный на интервале совпадения единичных уровней его входных сигналов (нижняя часть фиг.З, вых.эл.15, 22 и 20 ). Как следствие, на выходе элемента 21 сформируется уровень логической единицы, передний фронт которого переключит триггер 16 из единичного состояния в нулевое, в результате чего на выходе блока 12 сформируется уровень единичного состояния, сигнализирующий о наличии помехи (вых.эл. 16 и 23). Аналогичным образом блок 12 работает при действии помех другого характера (фиг.4-6 ). Использование предлагаемого устройства в режиме счета перепадов, а также в режиме оперативного самоконтроля полностью рассмотрены в. прототипе и здесь не имеют принципиального значения. Контроль проверяемого узла 11, а также поиск неисправного компонента в нем осуществляется с помощью предлагаемого устройства путем описанного выше процесса кодирования динамики работы проверяемого узла 11 в его характерных контрольных точках и сравнения получаемых реальных ключевых слов с соответствующими эталонными. С помощью предлагаемого устройства также получают этгшонные ключевые слова. При этом, получив очередное ключевое слово, проверяют не зажжется ли индикатор блока анализа достоверности кодирования. Если он не

зажегся, переходят к получению ключевого слова в очередной кбнтрольной точке проверяемого узла 11 (переносят в другую контрольную точку щуп и осуществляют очередное кодирование}. Бели же указанный индикатор згажегся, полученное ключевое слово недостоверно, при этом осуществляют перекодирование с использованием одной из задержек блока 14 задержек, вводимой с помощью третьего коммутатора 13, При этом регистрируется ключевое слово и положение третьего коммутатора 13,ког торым соответствует незажигание индикатора блока 12 анализа достоверности кодирования и т.д. для всех контроль-15 ных точек проверяемого узла 11.

При регистрации технического состояния проверяемого узла (т.е. при получении эталонных ключевых слов I) с помощью П : едлагаемого устройства вре- 20 менные затраты сокращаются примерно в два раза за счет отсутствия необходимости ,повторного кодирования,позволяющего избежать случайные сбои и помехи. Факт отсутствия случайных сбоев и помех в предлагаемом устройстве индицируется.

Экономический эффект от применени предлагаемого устройства сказывается и при контроле, и при поиске неисправных .компонентов

Кроме того, существенное преимущество npejtnaraeMoro устройства в отличие от прототипа состоит в возможности определения ,( также будет зажигаться индикатор блока анализа достоверности кодирования J устойчивого наложешвя фронтов синхроимпульса и иг-шулв.са кодируемой двоичной последовательности, что также повышает достоверность получения эталонных ключевых слов, контроля цифровых узлов и поиска в. них неисправных компонентов.

Bxodi BxodZ

к л. 26

кл.25раз Вшзл17

КД.. Вш.эл 1в Вых. ,111

Вд1Х.ЗЛ19 Вых. эл22

Вых, эл20 Вш.злЦ

B.mJ6 Вых.эл23

КА25разВш.эл17

м. изамк. Вь/х.эл 18

Вых.злШ Вых.эл.22

ВЫХ.ЭЛ.2& Вых.зл2

Вь1хзл16

Выхм23.

кл.25раз. Вых.эл. П м.. Вы.зл1в

ВЫК.Ж15 ШГГТДЛ

Вых.зл. F -у-

Вш.зл22

Вд1Х.эл20 Вьк-ЭЛ.Ц

BbtXjAfS

ВЫХ.ЭЛ23

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США № 3573751, кл, 340-172.5, опублик | |||

| Устройство станционной централизации и блокировочной сигнализации | 1915 |

|

SU1971A1 |

| Устройство для контроля цифровыхОб'ЕКТОВ | 1979 |

|

SU851410A1 |

Авторы

Даты

1983-12-07—Публикация

1982-01-07—Подача