(5) МАЖОРИТАРНО-РЕЗЕРВИРОВАННОЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Мажоритарно-резервированное устройство | 1984 |

|

SU1182696A1 |

| Многоканальное резервированное счетное устройство | 1983 |

|

SU1099389A1 |

| Резервированный счетчик импульсов | 1986 |

|

SU1370778A1 |

| Резервированное счетное устройство | 1986 |

|

SU1350830A1 |

| Устройство для коррекции ошибок внешней памяти | 1989 |

|

SU1662011A1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ИСПРАВЛЕНИЯ ОШИБОК ДЛЯ МАГНИТНЫХ НАКОПИТЕЛЕЙ | 1992 |

|

RU2037890C1 |

| Аналого-цифровой преобразователь | 1988 |

|

SU1571761A1 |

| Резервированное запоминающее устройство | 1983 |

|

SU1164789A1 |

| Трехканальная мажоритарно-резервированная система | 1981 |

|

SU1104696A1 |

| Резервированный делитель частоты | 1990 |

|

SU1780187A1 |

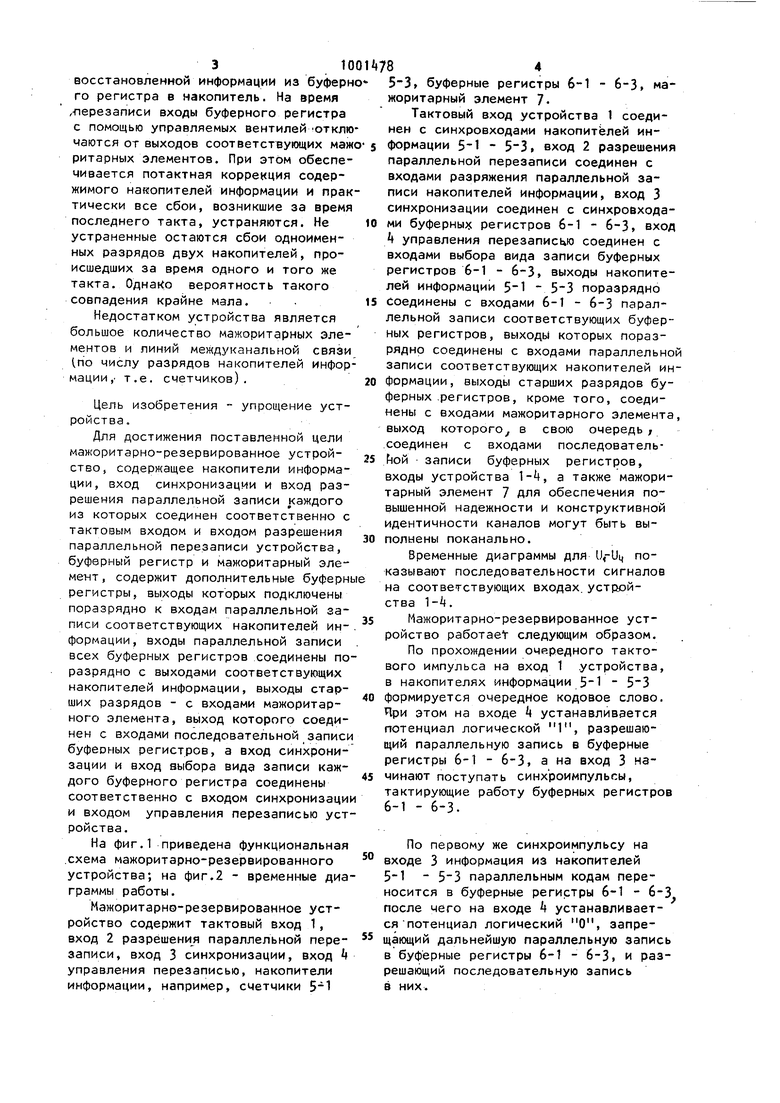

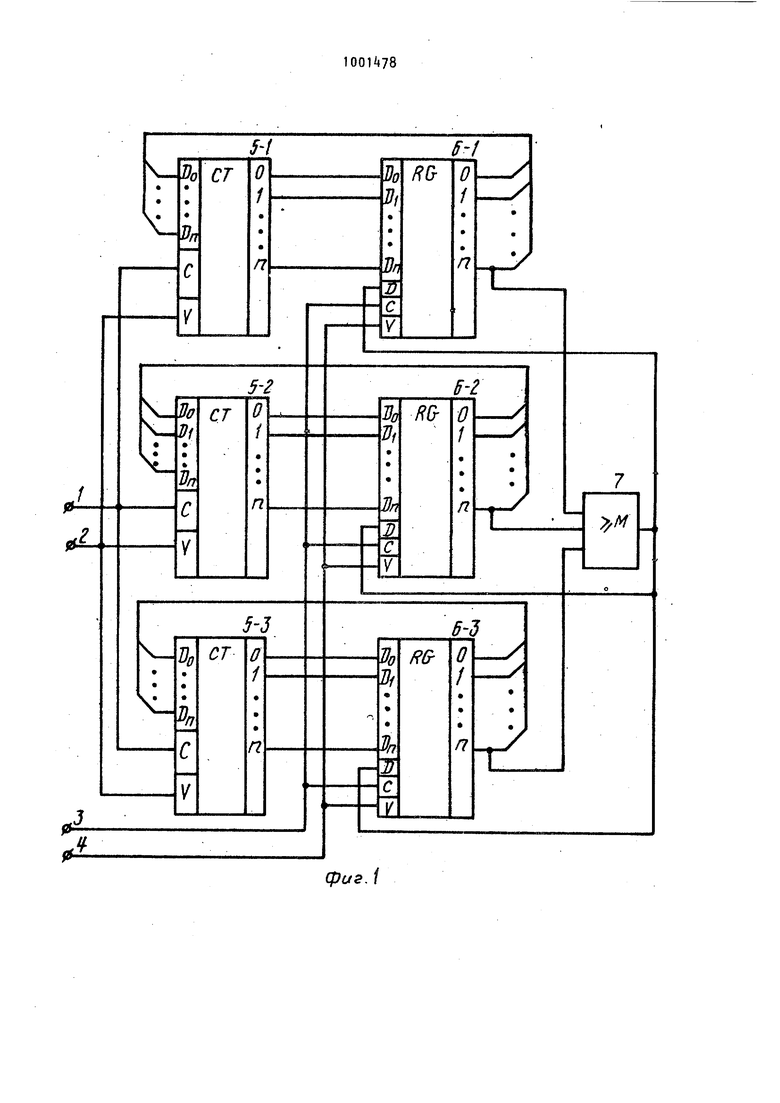

Изобретение относится к цифровой технике и может быть использовано в устройствах дискретной автоматики и вычислительной технике повышенной надежности, например в пересчетных устройствах с коррекцией результатов счета. Известно мажоритарно-резервированное устройство, содержащее резервированные логические блоки для обработки цифровой информации и соединенные с ними мажоритарные элементы для вогстй новления достоверной информации 1 3 Однако устройство обладает, вопервых, недостаточной надежностью, посколь су для искажения выходной информации достаточно сбоя одноименных разрядов двух каналов, возникших в любое время в течение цикла работы устройства даже в различных тактах и, во-вторых, большим числом мажоритарных элементов (по числу двоичных разрядов в слове выходной информации) И, соответственно, большим числом мажоритарны.х связей на входах мажоритарных элементов. Известно мажоритарно-резервированное устройство, содержащее канальные накопители выходной информации (например счетчики), мажоритарные элементы поразрядного голосования, подключенные к соответствующим их выходам, и буферный регистр, входы параллельной записи которого через управляемые вентили соединены с выходами соответствующих мажоритарных элементов, выходы регистра поразрядно соединены с входами параллельной записи (предуста новки) накопителей информации . . В устройстве в буферном регистре (в течение почти всего цикла работы устройства) хранится достоверная информация, восстановленная поразрядно мажоритарными элементами- Каждый такт ( перед поступлением очередного синхроимпульса происходит перезапись восстановленной информации из буферн го регистра в накопитель. На время ,лерезаписи входы буферного регистра с помощью управляемых вентилей-отклю чаются от выходов соответствующих маж ритарных элементов. При этом обеспечивается потактная коррекция содержимого накопителей информации и прак тически все сбои, возникшие за время последнего такта, устраняются. Не устраненные остаются сбои одноименных разрядов двух накопителей, происшедших за время одного и того же такта. Однако вероятность такого совпадения крайне мала. Недостатком устройства является большое количество мажоритарных элементов и линий междуканальной связи (rio числу разрядов накопителей инфор мации, т.е. счетчиков). Цель изобретения - упрощение устройства. Для достижения поставленной цели мажоритарно-резервированное устройство, содержащее накопители информации, вход синхронизации и вход разрешения параллельной записи каждого из которых соединен соответственно с тактовым входом и входом разрешения параллельной перезаписи устройства, буферный регистр и мажоритарный элемент, содержит дополнительные буферн регистры, выходы которых подключены поразрядно к входам параллельной записи соответствующих накопителей информации, входы параллельной записи всех буферных регистров соединены по разрядно с выходами соответствующих накопителей информации, выходы старших разрядов - с входами мажоритарного элемента, выход которого соединен с входами последовательной записи буферных регистров, а вход синхронизации и вход выбора вида записи каждого буферного регистра соединены соответственно с входом синхронизаци и входом управления перезаписью уст ройства. На фиг.1 приведена функциональная .схема мажоритарно-резервированного устройства; на фиг.2 - временные диа граммы работы. Мажоритарно-резервированное устройство содержит тактовый вход 1, вход 2 разрешения параллельной перезаписи, вход 3 синхронизации, вход управления перезаписью, накопители информации, например, счетчики 5-1 5-3, буферные регистры 6-1 - 6-3, мажоритарный элемент 7Тактовый вход устройства 1 соединен с синхровходами накопителей информации 5-1 - 53, вход 2 разрешения параллельной перезаписи соединен с входами разряжения параллельной записи накопителей информации, вход 3 синхронизации соединен с синхровходами буферные ; регистров 6-1 - 6-3, вход управления перезаписью соединен с входами выбора вида записи буферных регистров 6-1 - 6-3, выходы накопителей информации 5-1 - 5-3 поразрядно Соединены с входами 6-1 - 6-3 параллельной записи соответствующих буферных регистров, выходы которых поразрядно соединены с входами параллельной записи соответствующих накопителей информации, выходы старших разрядов буферных .регистров, кроме того, соединены с входами мажоритарного элемента, выход кoтopoгo в свою очередь/ .соединен с входами последователь й записи буферных регистров, входы устройства 1-, а также мажоритарный элемент 7 для обеспечения повышенной надежности и конструктивной идентичности каналов могут быть выполнены поканально. Временные диаграммы для Uf-Ui показывают последовательности сигналов на соответствующих входах, устройства 1-4. Мажоритарно-резервированное устройство pa6oTaet следующим образом. По прохождении очередного тактового импульса на вход 1 .устройства, в накопителях информации 5-1 - 5-3 формируется очередное кодовое слово. Яри этом на входе устанавливается потенциал логической 1, разрешающий параллельную запись в буферные регистры 6-1 - 6-3, а на вход 3 начинают поступать синхроимпульсы, тактирующие работу буферных регистров 6-1 - 6-3. По первому же синхроимпульсу на входе 3 информация из накопителей 5-1 - параллельным кодам переносится в буферные регистры 6-1 - 6-3 после чего на входе k устанавливается потенциал логический О, запрещающий дальнейшую параллельную запись в буферные регистры 6-1 - 6-3, и разрешающий последовательную запись 8 них. 51 Последующие синхроимпульсы с входа 3 устройства, число которых должно быть равно числу разрядов накопителей 5-1-5 3 информации, обеспечивают сдвиг информации по кольцу, вкл чающемуВ себя буферные регистры 6-1 - 6-3 и мажоритарный элемент 7После прохождения последнего синхроимпульса с входа 3 на регистры 6-1 6-3, в них оказывается перезаписанной информацияJ извлеченная из накопителей 5-1 -5-3 и восстановленная по большинству в мажоритарном элементе 7. Цикл восстановления информации завершает импульс, поступающий на вход 2 устройства, и обеспечивающий перезапись восстановленной информации,из буферных регистров 6-1 - 6-3 в накопители 5-1 5-3 информации. Считывание выходной информации с устройства может выполняться . с накопителей 5-1 - или с буферных регистров 6-1 - 6-3. В последнем случае считывание должно быть запрещено на время цикла перезаписи инфор мации, в регистрах, т.е. от второго до последнего импульса на входе 3 устройства. Применение предлагаемого мажоритарно-резервир1,ванного устройства обеспечивает при надежности не хуже, чем у прототипа, уменьшение как аппа ратурного состава числа корпусов микросхем), так и числа связей между каналами устройства.. Увеличение аппаратурного состава устройства на 2 регистра (для развитых серий ИМс, например, кор пуса на разряд) окупается устранением п-1 (п - число разрядов) мажоритарных элементов (1/3 корпуса на раз ряд для случая узлового резервирования) . Выигрыш получается еще более lQ6 существенным в случае сетевого резервирования с трехканальными мажоритарными элементами (корпус на разряд), а также при использовании для обеспечения контролепригодности устройства управляемых мажоритарных элементов (до 2 корпусов на разряд). Формула изобретения Мажоритарно-резервированное устройство, содержащее накопители информации, вход синхронизации и вход разрешения параллельной записи каждого из которых соединен соответственно с тактовым входом и входом разрешения параллельной перезаписи устройства, буферный регистр и мажоритарный элемент, отличающееся тем, что, с целью упрощения устройства, оно содержит дополнительные буферные регистры, выходы которых подключены поразрядно к входам параллельной записи соответствующих накопителей информации, входы параллельной записи всех буферных регистров соединены поразрядно с выходами соответствующих накопителей информации, выходы старших разрядов - с входами мажоритарного элемента выход которого соединен с входами последовательной записи буферных регистров, а вход синхронизации и вход выбора вида записи каждого буфера ного регистра соединены соответственно с входом синхронизации и входом управления перезаписью устройства. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № , кл. G 06 F 11/00, 1975. 2.Авторское свидетельство СССР № 508937, кл. Н 03 К 21-30, 1975 (прототип).

Cpus. 1

срие.2

Авторы

Даты

1983-02-28—Публикация

1981-09-25—Подача