Изобретение относится к вычислительной технике и может быть использовано в устройствах регистрации цифровой информации на магнитном подвижном носителе.

Известно устройство для исправления ошибок при параллельном считывании двоичной информации [1] которое содержит блок воспроизведения, схему свертки по модулю два по строке, схему свертки по модулю два по диагонали, сумматоры, буферные регистры сдвига, логические элементы И, НЕ и ячейки памяти. Данное устройство позволяет исправлять одиночные ошибки информации.

В случае наличия ошибок в двух и более разрядах информации возможно появление одновременно двух искажений в векторах наклонной или вертикальной четности.

В этом случае при сравнении соответствующих сигналов четности (сформированного и считанного) сигнал несоответствия не формируется, так как четное число информации в строке не меняет ее сигнал четности и, следовательно, при сравнении четности (сформированной и считанной) не будет сформирован сигнал несоответствия, что приведет к неверному нахождению искаженных позиций в разрядах информации.

Наиболее близким к заявляемому является многоканальное устройство исправления ошибок для магнитных накопителей [2] содержащее блок регистров сдвига, блоки свертки по модулю два вертикальной и наклонной четности, регистр сдвига, группу триггеров, первую и вторую группы элементов И, группу элементов НЕ, два элемента неравномерности, триггер, третью и четвертую группы элементов И, блок обнаружения многократной ошибки и элемент НЕ. Данное устройство позволяет исправлять ошибки, возникающие в результате искажения или выпадения одного разряда параллельной информации, и запрещает дополнительное искажение выходной информации в случае выпадений или искажений двойной и большей кратности разрядов информаций.

Однако данное устройство имеет большое защитное пространство, которое характеризует зону нечувствительности устройства к ошибкам информации. Это означает, что часть ошибок, которые попали в зону нечувствительности, не исправляется, поэтому чем больше защитное пространство, тем ниже достоверность.

Цель изобретения повышение достоверности считываемой информации путем уменьшения защитного пространства кода.

Для достижения цели многоканальное устройство исправления ошибок для магнитных накопителей содержит блок регистров сдвига, блок свертки по модулю два наклонной четности, блок свертки по модулю два вертикальной четности, регистр сдвига, группу триггеров, первую, вторую, третью и четвертую группы элементов И, группу элементов НЕ, первый и второй элементы "Неравнозначность", элемент НЕ, блок обнаружения многократной ошибки, выполненный на второй группе триггеров и мажоритарном элементе, при этом информационные входы блока регистров сдвига и входы блока свертки по модулю два наклонной четности поразрядно соединены и являются информационными входами устройства, выходы блока регистров сдвига подключены к входам блока свертки по модулю два вертикальной четности и к первым входам сумматоров по модулю два, вторые входы которых соединены с выходами соответствующих элементов И четвертой группы, а выходы сумматоров являются выходами устройства, тактовые входы регистров сдвига и входы синхронизации триггеров группы объединены и соединены с входом синхронизации устройства, информационный вход регистра сдвига является входом вертикальной четности устройства, а выход подключен к первому входу первого элемента "Неравнозначность", второй вход которого соединен с выходом блока свертки по модулю два вертикальной четности, а ее выход соединен с вторым входом каждого элемента И первой группы, первый вход каждого элемента подключен к прямому выходу одноименного триггера группы и второму входу элемента И второй группы, выход каждого элемента И первой группы через соответствующий элемент НЕ группы подключен к первым входам одноименных элементов И второй и третьей групп, выход каждого элемента И второй группы подключен к информационному входу последующего триггера первой группы, а выход каждого элемента И третьей группы соединен с первым входом предыдущего элемента И этой же группы и третьим входом предыдущего элемента И первой группы, вход наклонной четности устройства соединен с первым входом первого блока "Неравнозначность", второй вход которого соединен с выходом блока свертки по модулю два наклонной четности, а выход подключен к информационному входу первого триггера, первый вход каждого триггера второй группы соединен с первым входом соответствующего элемента И четвертой группы и подключен к выходу соответствующего элемента И первой группы, выходы триггеров второй группы через мажоритарный элемент подключены к выходу устройства многократной ошибки и к входу элемента НЕ, выход которого соединен с вторыми входами элементов И четвертой группы, блок обнаружения ошибок содержит пятую группу из N/2 элементов И, а N триггеров второй группы блока соединены в N/2 пар, причем вход обнуления первого триггера соединен с входом обнуления N-го триггера и образуют вход обнуления N/2 пары, вход обнуления второго триггера соединен с инверсным входом обнуления (N-1)-го триггера и образуют вход обнуления (N-1) пары, инверсный вход N/2 триггера соединен с инверсным входом (N/2+1)-го триггера и образуют вход обнуления первой пары, первый вход каждого элемента И пятой группы, кроме первого, соединен с выходом предыдущего элемента И этой же группы, второй вход каждого элемента И пятой группы, начиная с первого и до N/2-го, соединен в обратной последовательности с инверсным выходом соответствующего триггера первой группы, начиная с N/2 до первого триггера, а третьи входы этих элементов И соединены с инверсными выходами соответствующих триггеров первой группы, начиная с (N/2+1)-го до N-го.

Выход каждого элемента И пятой группы, начиная с первого, соединен с входом обнуления соответствующей пары триггеров, начиная с 1-й пары до N/2 пары.

Введение пятой группы элементов И в блок обнаружения ошибок и объединение N триггеров второй группы в N/2 пар, а также подключение этих элементов И позволяет дифференциально подавать сигнал разрешения для исправления на каждую пару из двух каналов, что изменяет защитное пространство с постоянного N2 для всех разрядов информации на переменное в зависимости от позиционного расположения разрядов информации, которое определяется как i.N, где i 2,4,6, N. Кратность двум определяется объединением триггеров второй группы из блока обнаружения многократной ошибки в пары.

Так как защитное пространство характеризует зону нечувствительности устройства к ошибкам информации, т.е. часть ошибок, которые попали в зону нечувствительности, не исправляется, то уменьшение защитного пространства повышает эффективность работы устройства, а в конечном итоге повышает достоверность считываемой информации.

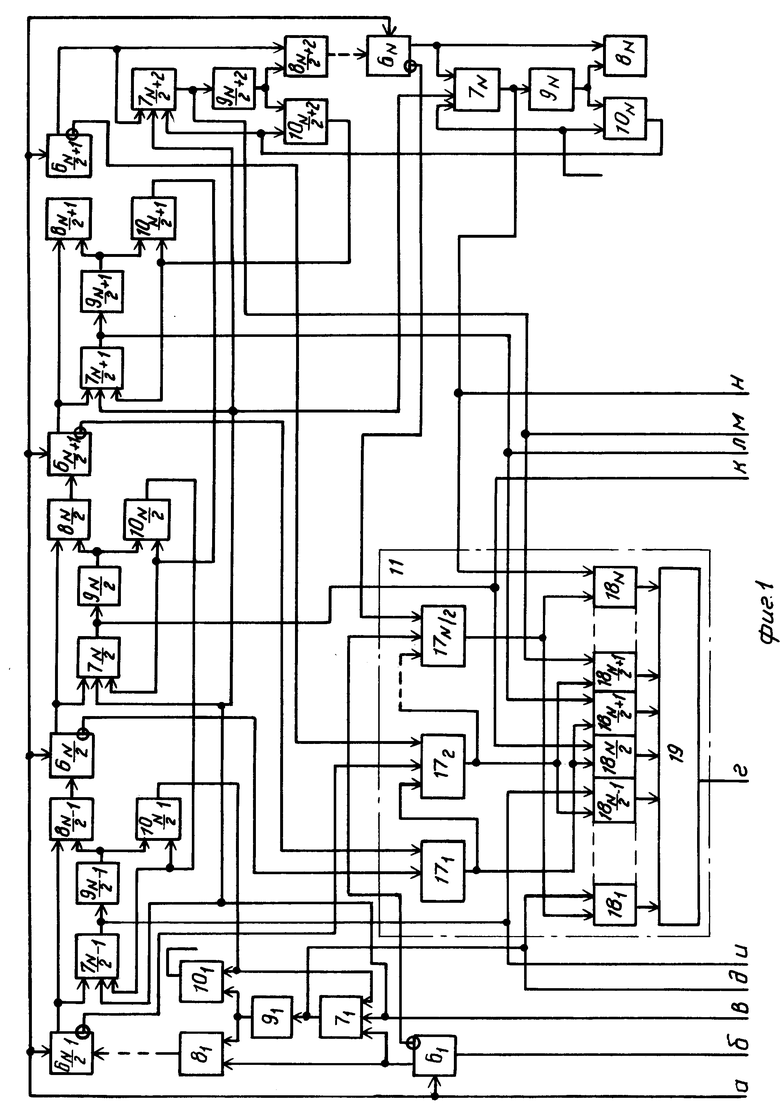

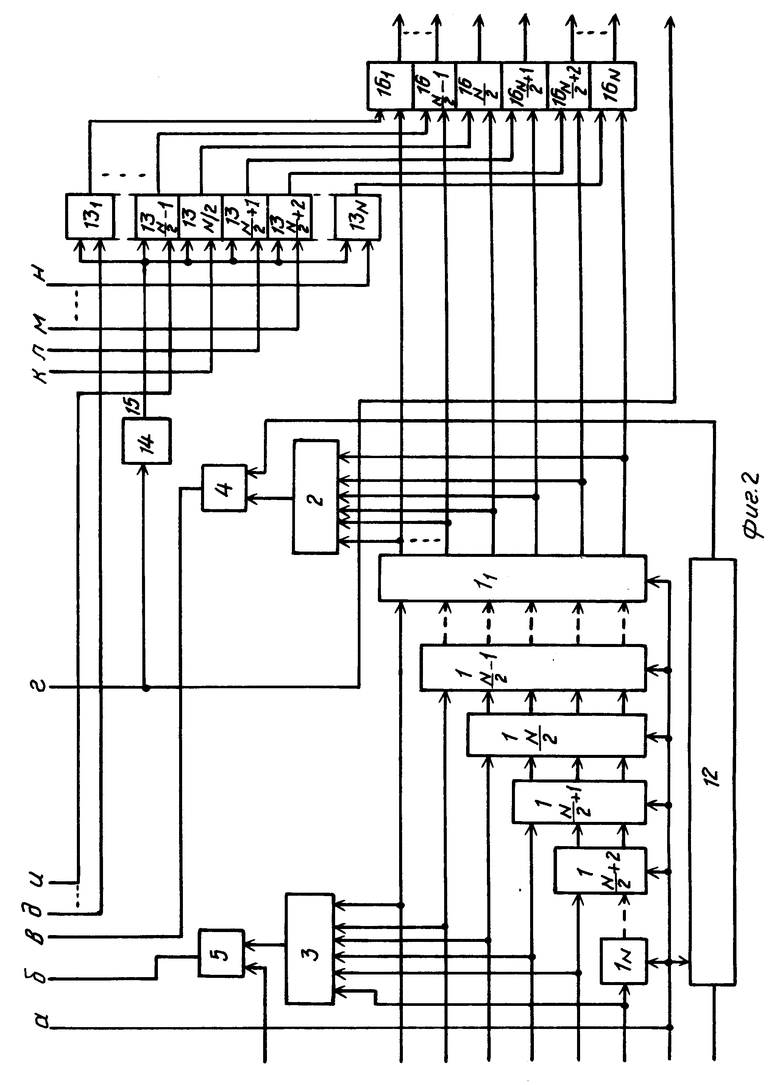

На фиг. 1, 2 представлена структурная схема многоканального устройства исправления ошибок для магнитного накопителя.

Устройство содержит блок 1 регистров 11-1N сдвига (где N число каналов или разрядов входной информации), блок 2 свертки по модулю два вертикальной четности, блок 3 свертки по модулю два наклонной четности, первый 4 и второй 5 элементы "Неравнозначность", группу триггеров 61,6N, первую группу элементов И 71.7N, вторую группу элементов И 81.8N, группу элементов НЕ 91.9N, третью группу элементов И 101.10N, блок 11 обнаружения многократной ошибки, регистр 12 сдвига, четвертую группу элементов И 131.13N, элемент НЕ 14, имеющий выход 15 и блоки 161.16N сумматоров по модулю два.

Блок 11 обнаружения многократной ошибки содержит пятую гpуппу трех входовых элементов И 171.17N/2, вторую группу триггеров 181.18N и мажоритарный элемент 19. Триггеры 181.18N соединены в N/2 пар в следующем порядке. Входы обнуления триггеров 181 и 18N соединены и образуют N/2 пару, триггеры 182 и 18N-1 соединены и образуют (N/2-1)-ю пару, аналогично соединены остальные триггеры и первую пару образуют соединения триггеров 18 N/2 и 18 N/2+1.

Информация поразрядно поступает на входы блока регистров 1 сдвига и входы блока 3 свертки по модулю два наклонной четности, выходы блока 1 регистров подключены к первым входам блока 16 сумматоров и входам блока 2 свертки по модулю два вертикальной четности, выход которого соединен с первым входом первого элемента "Неравнозначность", второй вход которого соединен с выходом регистра 12 сдвига, вход которого является входом вертикальной четности устройства. Выход элемента 4 соединен с вторыми входами элементов И 71.7N первой группы, первый вход каждого из этих элементов соединен с первым входом элементов И81.8N и подключен к прямому выходу триггера 61.6N, выходы элементов И 71.7N через элементы НЕ 91.9N подключены к вторым входам элементов И 81. 8N и 101.10N. Выходы элементов 81.8N соединены с информационным входом последующего триггера 62.6N, а выход каждого элемента И третьей группы 101. 10N подключен к первому входу предыдущего элемента этой же группы 101.10N-1 и третьему входу элементов И 71.7N.

Вход наклонной четности устройства соединен с первым входом второго элемента "Неравнозначность" 5, второй вход которого соединен с выходом блока 3, а выход подключен к информационному входу триггера 61, инверсные выходы триггеров 61. 6N/2 соединены в обратной последовательности с вторыми входами элементов И 17N/2 17N/2+1, а инверсные выходы триггеров 6(N/2+1).6N соединены с третьими входами элементов И 171.17N/2.

Первые входы элементов 171.17N/2 соединены с выходами предыдущих элементов этой же группы, а выходы элементов 171.17N/2 соединены с входами обнуления соответствующей пары триггеров 18, установочные входы триггеров 181.18N соединены с выходами элементов И71.7N и первыми входами элементов 131.13N. Выходы триггеров 181.18N соединены с входами мажоритарного элемента 19, выход которого соединен с выходом устройства "Ошибка 2", и через элемент НЕ 14- с вторыми входами элементов И 131.13N, выходы которых подключены к вторым входам сумматоров 161.16N, выходы которых являются информационными выходами устройства. Тактовые входы регистров 11.1N и 12 и входы синхронизации триггеров 61.6N объединены и подключены к входу синхронизации устройства.

Устройство работает следующим образом. Информация, считанная с магнитного носителя (не показан), поступает на блок 3 свертки по модулю два, на выходе которого формируется сигнал наклонной четности, и одновременно через блок 1 регистров, обеспечивающих ступенчатый сдвиг, поступает на блок 2 свертки по модулю два, на выходе которого фоpмируется сигнал вертикальной четности.

Сформированный сигнал наклонной четности с блока 3 и сигнал наклонной четности, считанной с магнитного носителя, поступают на элемент "Неравнозначность" 5, на выходе которого вырабатывается сигнал несоответствия наклонных четностей. Сформированный сигнал вертикальной четности с блока 2 подается на один из входов элемента "Неравнозначность" 4, на другой вход которого подается сигнал считанной вертикальной четности через регистр 12. На выходе элемента "Неравнозначность" 4 вырабатывается сигнал несоответствия вертикальных четностей. Сигнал несоответствия наклонных четностей в случае отсутствия сигнала несоответствия вертикальных четностей переписывается с одного триггера 6 в следующий через элемент И8 синхронно с передачей информации в регистры 1 и 12.

В случае появления сигнала несоответствия вертикальных четностей, наличия сигнала несоответствия наклонных четностей, записанного в триггеры 6, и отсутствия сигналов запрета с последующих элементов И 10 на выходе элемента И17 вырабатывается сигнал коррекции. Он подается на один из входов соответствующего элемента И13 и на вход установки в "1" соответствующего триггера 18. Сигнал коррекции с элемента И8 через элемент НЕ9 запрещает прохождение сигнала несоответствия наклонных четностей через элемент И8 на последующий триггер 6 и через элемент И10 запрещает выделение сигнала коррекции на предыдущем элементе И7.

При искажении считанной информации, например в i-м разряде, сигналы несоответствия вертикальной и наклонной четностей совпадают на входах i-го элемента И7, на выходе которого выделяется сигнал коррекции информации. Сигнал коррекции информации через элемент НЕ9 запрещает прохождение сигнала несоответствия наклонных четностей на вход (i+1)-го триггера 6 и через элементы НЕ9 и И10 запрещает выделение сигнала коррекции (i-1)-м элементом И7. Сигнал коррекции информации с выхода i-го элемента И7 подается на i-й элемент И13 и на вход установки в "1" i-го триггера 18, устанавливая его в единичное состояние. Сигнал с выхода i-го триггера 18 поступает на мажоритарный элемент 19, который формирует единичный сигнал при наличии двух или более единиц на его входах, поэтому при искажении информации только в i-м разряде с выхода мажоритарного элемента 19 снимается нулевой потенциал.

При установке в единичное состояние триггеров 18, количество которых совпадает с функцией мажоритарного элемента 19, т.е. больше или равно двум, вырабатывается сигнал "Многократная ошибка", который подается на выходную шину и через элемент НЕ 14 на один из входов элементов И 13 и запрещает прохождение сигналов коррекции информации на выходы сумматоров 16 по модулю два. Информация, поступающая на другие входы сумматоров 16 с буферных регистров 1, без изменения передается на выход. Сигнал с выхода мажоритарного элемента 19 несет сообщение о наличии во входной информации двойной или большей кратности ошибки.

Конец запрета на коррекцию информации определяется обнулением триггеров 181.18N, которое осуществляется дифференциально для каждой пары разрядов информации в зависимости от его позиции. Объединение разрядов в пары аналогично объединению триггеров 18. Обнуление каждой пары триггеров 18 осуществляется следующим образом.

Конец запрета на коррекцию первой пары разрядов N/2 (N/2+1) информации определяется обнулением первой пары триггеров 18N/2-18N/2+1, которое происходит через элемент И 171 при наличии единиц, на инверсных выходах триггеров 6N/2 и 6N/2+1. В такое состояние они устанавливаются при отсутствии искажений в N/2 и N/2+1 разрядах входной информации (первая пара).

Конец запрета на коррекцию второй пары (N/2-1) N/2+2) разрядов информации определяется обнулением триггеров второй пары 18(N/2-1) 18(N/2+2), которое происходит через элемент И172 при наличии единиц на инверсных выходах триггеров 6N/2-1, 6N/2, 6N/2+1, 6N/2+2. В такое состояние они устанавливаются при отсутствии искажений в N/2-1,N/2, N/2+1, N/2+2 разрядах входной информации и т.д.

Конец запрета на коррекцию N/2-й пары первого и N-го разрядов информации определяется обнулением триггеров N/2-й первой пары 181 и 18N, которое происходит через элемент И17 N/2 при наличии единиц на инверсных выходах триггеров 61.6N.

В такое состояние они устанавливаются при отсутствии искажений во всех N разрядах входной информации. Таким образом дифференциальное обнуление триггеров позволило сократить защитное пространство, т.е. зону нечувствительности, в среднем на 40%

Защитное пространство известного устройства постоянно для всех разрядов определяется как N2, т.е. в течение N тактов синхроимпульсов обнуляются N триггеров при отсутствии искажений во всех разрядах информации (N.N N2).

В предлагаемом устройстве защитное пространство переменное, зависит от позиционного расположения разрядов информации и определяется как i . N, где i 2,4,6.N кратность двум, определяется объединением триггеров 18 в пары.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДВУХУРОВНЕВОЕ УСТРОЙСТВО ИСПРАВЛЕНИЯ ОШИБОК | 1992 |

|

RU2037891C1 |

| Многоканальное устройство исправления ошибок для магнитных накопителей | 1986 |

|

SU1383440A1 |

| Многоканальное резервированное устройство | 1981 |

|

SU991628A1 |

| Многоканальное резервированное устройство | 1984 |

|

SU1164712A1 |

| Запоминающее устройство с коррекцией групповых ошибок | 1987 |

|

SU1481863A1 |

| Многоканальное резервированное устройство | 1982 |

|

SU1034209A1 |

| Многоуровневое устройство исправления ошибок для магнитных носителей | 1988 |

|

SU1580440A1 |

| Многоканальное резервированное устройство | 1983 |

|

SU1111263A1 |

| Устройство для задержки цифровой информации с самоконтролем | 1986 |

|

SU1429174A1 |

| Запоминающее устройство с коррекцией групповых ошибок | 1983 |

|

SU1141453A1 |

Использование: изобретение относится к вычислительной технике и может использоваться в устройствах регистрации цифровой информации на подвижных магнитных носителях при высокоплотной записи. Сущность изобретения: с целью повышения достоверности считанной информации за счет уменьшения зоны нечувствительности устройства устройство содержит регистры сдвига, блоки свертки по модулю два вертикальной и наклонной четности, первый и второй элементы "Неравнозначность", триггеры, группы элементов И, элементы НЕ, блок обнаружения многократной ошибки, выполненный на группе элементов И, триггерах и мажоритарном элементе, сумматор. Устройство позволяет дифференциально подавать сигнал разрешения для исправления ошибок информации на каждую пару из двух разрядов и сокращает зону нечувствительности устройства к ошибкам информации (защитное пространство). 2 ил.

МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ИСПРАВЛЕНИЯ ОШИБОК ДЛЯ МАГНИТНЫХ НАКОПИТЕЛЕЙ, содержащее блок регистров сдвига, блок свертки по модулю два наклонной четности, блок свертки по модулю два вертикальной четности, регистр сдвига, группу триггеров, первую, вторую, третью и четвертую группы элементов И, группу элементов НЕ, первый и второй элементы НЕРАВНОЗНАЧНОСТЬ, элемент НЕ, блок обнаружения ошибок, состоящий из второй группы триггеров и мажоритарного элемента, при этом информационные входы блока регистров сдвига и входы блока свертки по модулю два наклонной четности поразрядно соединены и являются информационными входами устройства, выходы блока регистров сдвига подключены к входам блока свертки по модулю два вертикальной четности и к первым входам сумматоров по модулю два, вторые входы которых соединены с выходами соответствующих элементов И четвертой группы, а выходы сумматоров являются выходами устройства, тактовые входы регистров сдвига и входы синхронизации триггеров группы объединены и соединены с входом синхронизации устройства, информационный вход регистра сдвига является входом вертикальной четности устройства, а выход подключен к первому входу первого элемента НЕРАВНОЗНАЧНОСТЬ, второй вход которого соединен с выходом блока свертки по модулю два вертикальной четности, а выход соединен с вторым входом каждого элемента И первой группы, первый вход каждого элемента соединен с вторым входом одноименного элемента И второй группы и подключен к прямому выходу одноименного триггера первой группы, а выход каждого элемента И первой группы через соответствующий элемент НЕ группы подключен к первым входам одноименных элементов И второй и третьей групп, выход каждого элемента И второй группы подключен к информационному входу последующего триггера первой группы, а выход каждого элемента И третьей группы соединен с первым входом предыдущего элемента И этой же группы и третьим входом предыдущего элемента И первой группы, вход наклонной четности устройства соединен с первым входом первого блока НЕРАВНОЗНАЧНОСТЬ, второй вход которого соединен с выходом блока свертки по модулю два наклонной четности, а выход подключен к информационному входу первого триггера, установочный вход каждого триггера второй группы соединен с первым входом соответствующего элемента И четвертой группы и подключен к выходу соответствующего элемента И первой группы, выходы триггеров второй группы через мажоритарный элемент подключены к выходу блока ошибок и входу элемента НЕ, выход которого соединен с вторыми входами элементов И четвертой группы, отличающееся тем, что блок обнаружения ошибок содержит пятую группу из N/2 элементов И, где N число каналов или разрядов информации, а N триггеров второй группы блока соединены в N/2 пар, причем входы обнуления первого и N-го триггеров соединены и образуют вход N/2 пары, входы обнуления второго и (N - 1)-го триггеров соединены и образуют вход обнуления  пары, входы обнуления средних триггеров с

пары, входы обнуления средних триггеров с  и (N/2 + 1)-го триггеров объединены и образуют вход обнуления первой пары, первый вход каждого элемента И пятой группы, кроме первого, соединен с выходом предыдущего элемента И этой же группы, второй вход каждого элемента И пятой группы, начиная с первого и до N/2-го, соединен в обратной последовательности с инверсным выходом соответствующего триггера первой группы, начиная с N/2-го до первого триггера, а третьи входы этих же элементов И соединены с инверсными выходами соответствующих триггеров первой группы, начиная с

и (N/2 + 1)-го триггеров объединены и образуют вход обнуления первой пары, первый вход каждого элемента И пятой группы, кроме первого, соединен с выходом предыдущего элемента И этой же группы, второй вход каждого элемента И пятой группы, начиная с первого и до N/2-го, соединен в обратной последовательности с инверсным выходом соответствующего триггера первой группы, начиная с N/2-го до первого триггера, а третьи входы этих же элементов И соединены с инверсными выходами соответствующих триггеров первой группы, начиная с  до N-го выход каждого элемента И пятой группы соединен с входом обнуления одноименной пары триггеров.

до N-го выход каждого элемента И пятой группы соединен с входом обнуления одноименной пары триггеров.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Многоканальное устройство исправления ошибок для магнитных накопителей | 1986 |

|

SU1383440A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1995-06-19—Публикация

1992-02-17—Подача