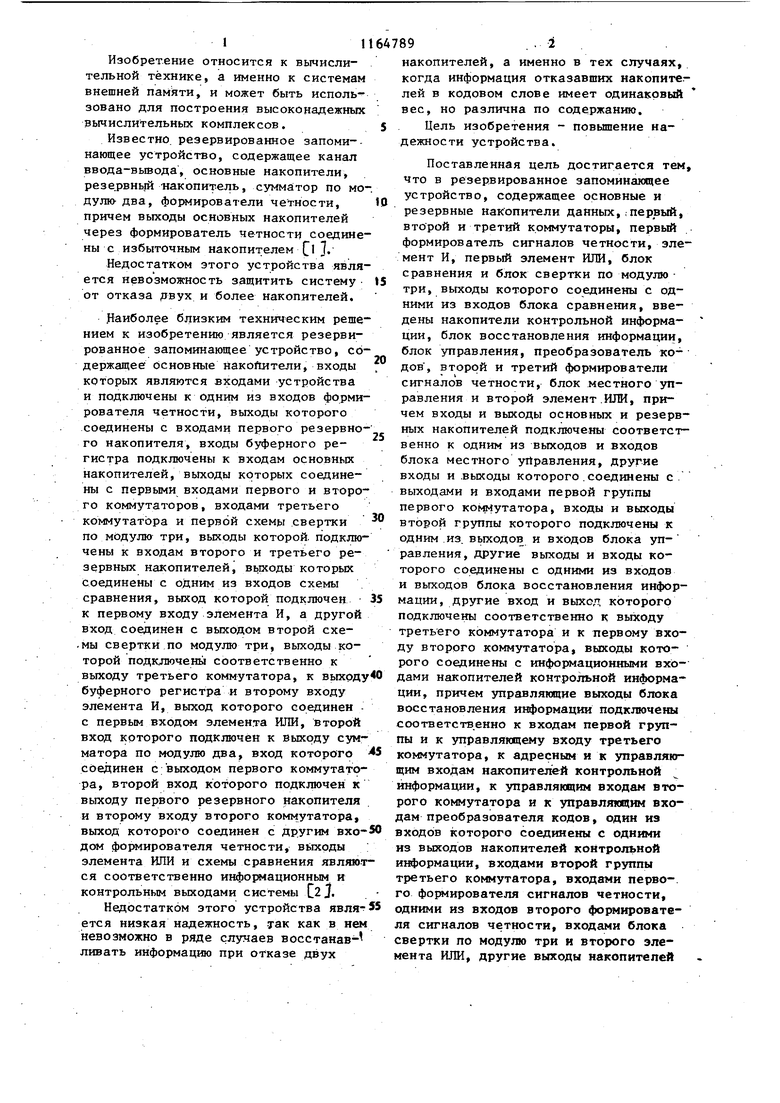

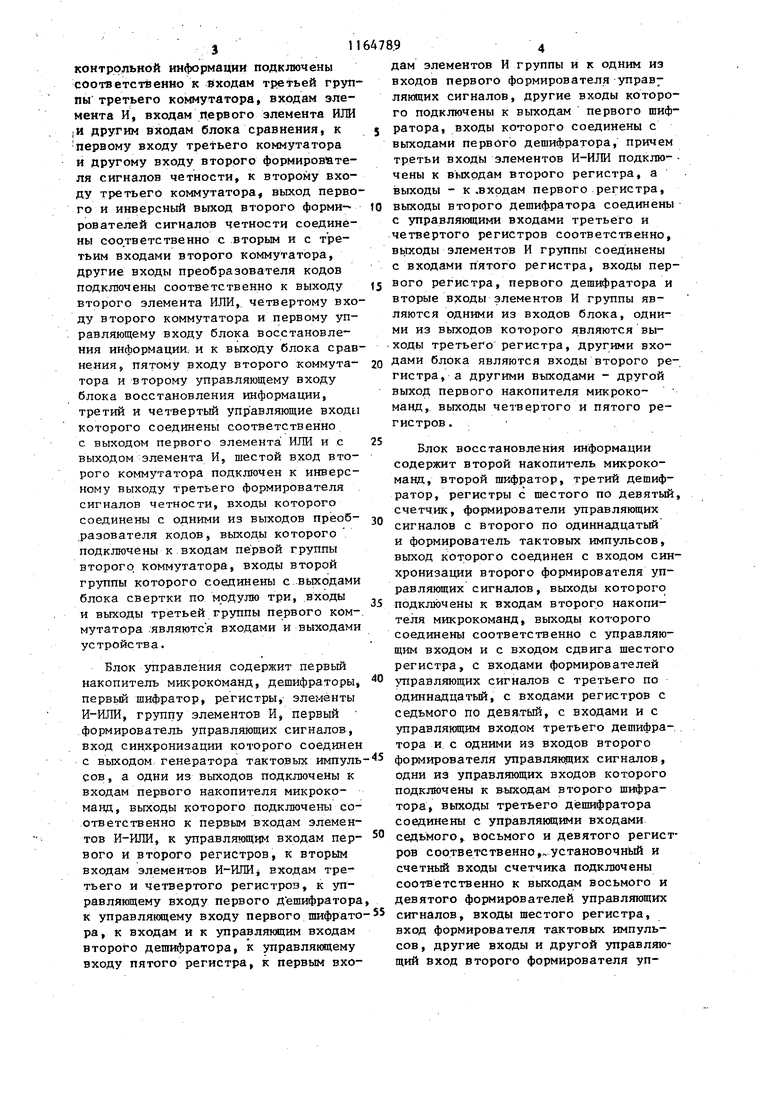

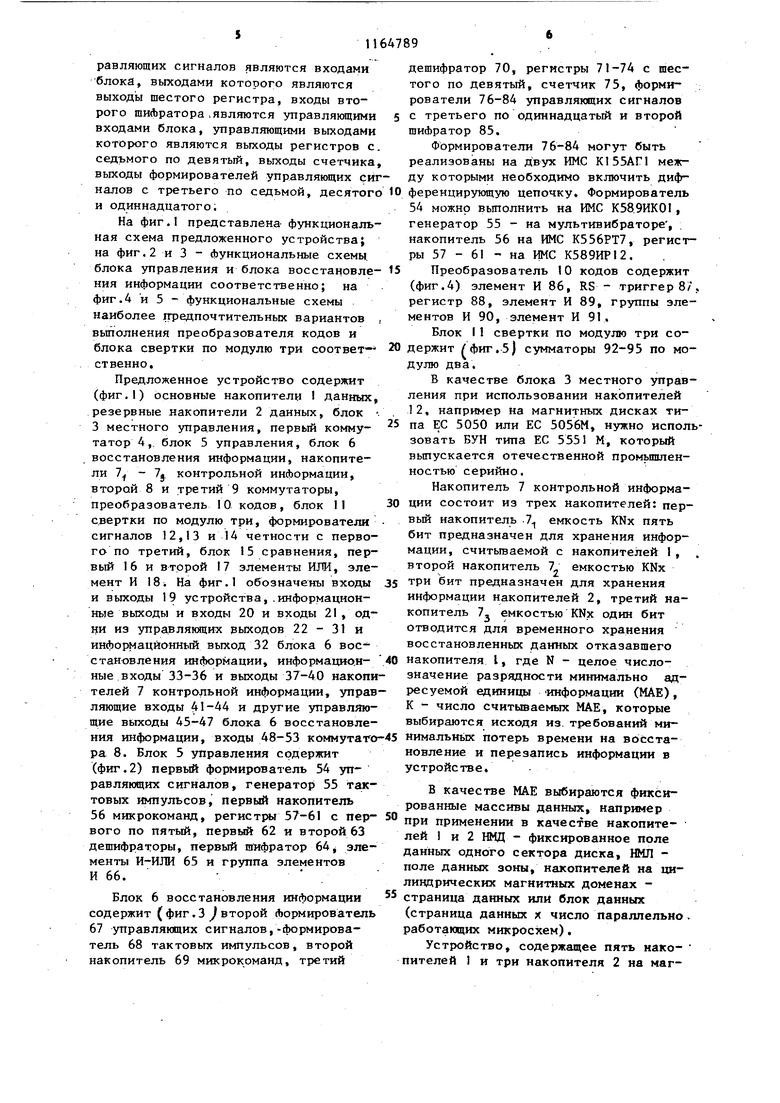

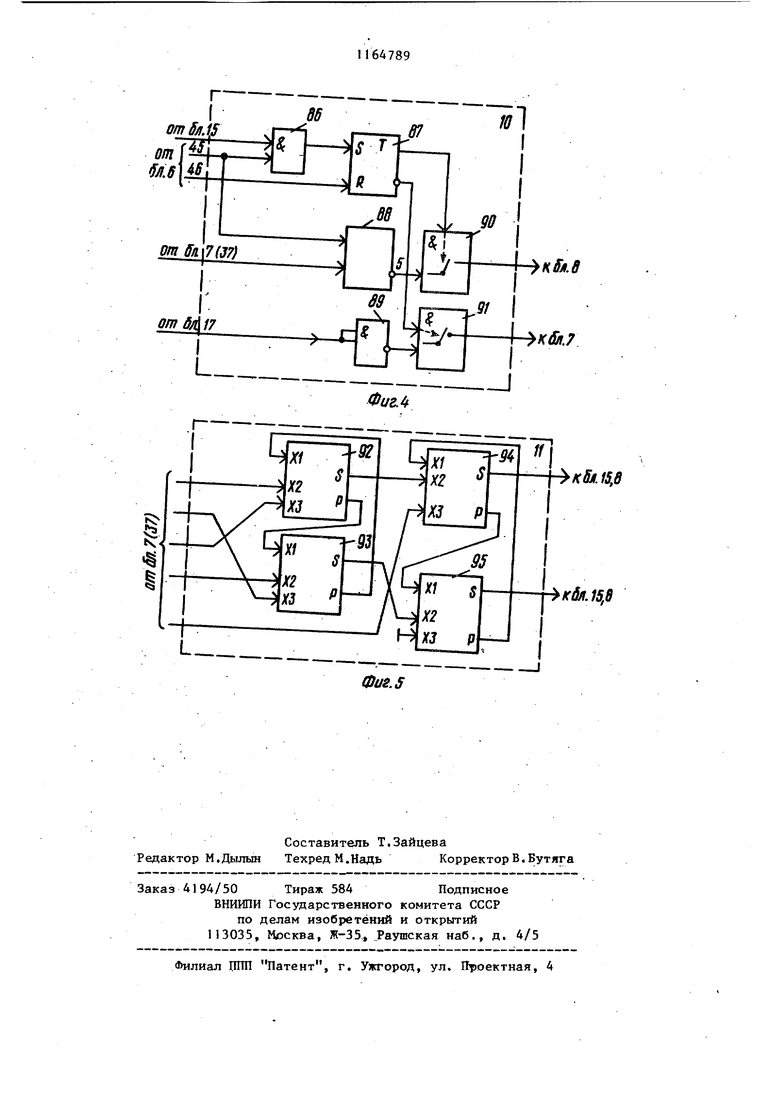

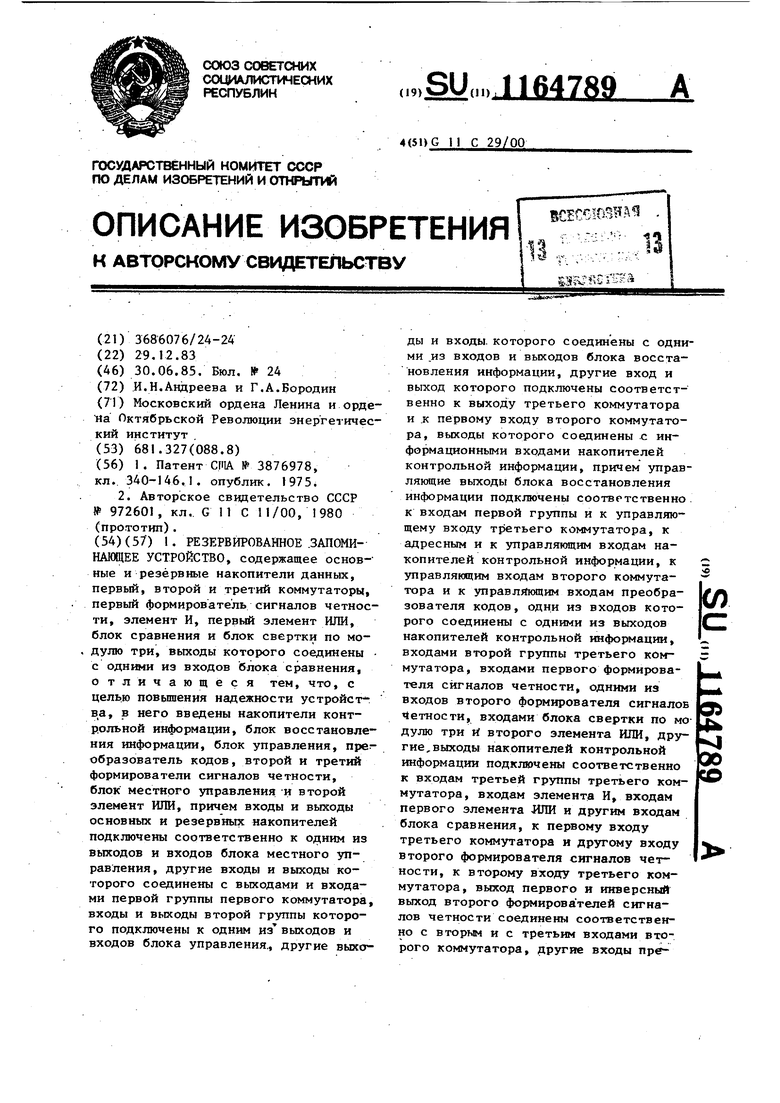

образователя кодов подключены соответственно к выходу второго элемента ИЛИ, четвертому входу второго коммутатора и первому управляющему входу блока восстановления инфop faции и к выходу блока сравнения, пятому входу второго коммутатора и второму управляющему входу блока восстановления информации, третий и четвертый управ ляющие входы которого соединены соответственно с выходом первого элеманта ИЛИ и с-выходом элемента И, шестой вход второго коммутатора подключён к инверсному выходу третьего формирователя сигналов четности, входы которого соединены с одними из выходов преобразователя кодов, выходы которого подключены ко входам пер вой группы второго коммутатора, входы второй группы которого соединены с выходами блока свертки до модулю три, входы и выходы третьей группы первого коммутатора являются входами и выходами устройства. 2, Устройство по П.1, о т л и -, чающееся тем, что блок управ ления содержит первый накопитель микрокоманд, дешифраторы, первый шифратор, регистры, элементы И-ИЛИ, группу элементов И,.первый формирователь управляющих сигналов, вход синхронизации которого соединен с выходом генератора тактовых импульсов , а одни из выходов подключены к входам первого накопителя микроко-манд, выходы которого подключены соответственно к первым входам, элементов И-ИЛИ, к управляющим входам первого и второго регистров, к вторым входам элементов И-РШИ, входам третьего и четвертого регистров, к управляющему в;соду первого дешифратора, к управляющему входу первого шифратора, к входам и к управляющим входам второго дешифратора, к управляющему входу пятого регистра, к первым входам элементов И группы и к одним из входов первого формирователя управляющих сигналов, другие входы которого подключены к выходам первого щифратора, вХоды которого соединены с выходами первого дещифратора, причем третьи входы элементов И-ИЛИ подключены к.выходам второго регистра, а выходы - к входам первого регистра, выходы второго дешифратора соединены с.-управляющими входами третьего и чет вертого; регистров соответственно, выходы эле ментов И группы соединены с входами пятого регистра, входы первого регистра, первого дешифратора и вторые входы элементов И группы являются одними из входов блока, одними из выходов которого являются выходы третьего регистра, другими входами блока являются входы второго регистра, а другими выходами - другой выход первого накопителя микрокоманд, выходы четвертого и пятого регистров. 3. Устройство по пп.1 и 2, о т л и.ч а ю щ е ее я тем, что блок восстановления информации содержит второй накопитель микрокоманд, второй шифратор, третий дешифратор, регистры с шестого по девятый, счетчик., формирователи упра вляющих сигналов с второго по одиннадцатый и формирователь тактовых импульсов, выход которого соединен с входом синхронизации второго формирователя управляющих сигналов, выходы которого подключены к входам второго накопителя микрокоманд, выходы которого соединены соответственно с управляющим входом и с входом сдвига шестого регистра, с входами формирователей управляющих сигналов с третьего по одиннадцатый, с. входами регистров с седьмого по девятый, с входами и с управляющим входом третьего дешифратора и с одними из входов второго формирователя управляющих сигналов, одни, из управляющих входов которого .подключены к вы;ходам второго шифратора, выходы третьего дешифратора соединены с управляющими входами седьмого, восьмого и девятого регистров соответственно, установочный и счетный входы счетчика подключены соответственно к выходам восьмого и девятого формирователей управлякмцих сигналов, входы шестого регистра, вход формирователя тактовых импульсов, другие входы и другой управляющий, вход второго формирователя. . управляющих сигналов являются входами блока, выходами которого являются выходы шестого.регистра, входы второго шифратора являются управлякяцими входами блока, управляющими выходами icOTOporo являются выходы регистров с седьмого по девятый, выходы счетчика, выходы формирователей управляющих сигналов с третьего по седьмой, десятого и одиннадцатого. Изобретение относится к вычислительной технике, а именно к системам внешней памяти, и может быть использовано для построения высоконадежных вычислительных комплексов, Известно, резервированное запоми-нающее устройство, содержащее канал ввода-вьшода, основные накопители, резервный -накопитель, сумматор по модулю-два, формирователи четности, причем выходы основных накопителей через формирователь четности соединены с избыточным накопителем С 1Недостатком этого устройства является невозможность защитить систему от отказа двух и более накопителей. Наиболее близким техническим решением к изобретению является резервированное запоминающее устройство, содержащее основные накоЛители, входы которых являются входами устройства и подключены к одним из входов формирователя четности, выходы которого соединены с входами первого резервного накопителя, входы буферного регистра подключены к входам основных накопителей, выходы которых соединены с первыми входами первого и второго коммутаторов, входами третьего коммутатора и первой схемы .свертки по модулю три, выходы которой, подключены к входам второго и третьего резервных накопителейj вьпсоды которых соединены с одним из входов схемы сравнения, выход которой подключен к первому входу элемента И, а другой вход соединен с выходом второй схемы свертки по модулю три, выходы которой подключены соответственно к выходу третьего коммутатора, к выхрду буферного регистра и второму входу элемента И, выход которого соединен с первым входе элемента ИЛИ, второй вход которого подключён к ВЫХОДУ сумматора по модулю два, вход которого соединен с выходом первого коммутатора, второй вход которого подключен к выходу первого резервного накопителя и второму входу второго коммутатора, выход которого соединен с другим входом формирователя четности, вьгхрды элемента ИЛИ и схемы сравнения являют ся соответственно информационным и контрольным выходами системы L2 J. Недостатком этого устройства является низкая надежность, так как в нем невозможно в ряде случаев восстававливать информацию при отказе двух накопителей, а именно в тех случаях, когда информация отказавших накопителей в кодовом слове имеет одинаковый вес, но различна по содержанию. Цель изобретения - повышение надежности устройства. Поставленная цель достигается тем. Что в резервированное запоминающее устройство, содержащее основные и резервные накопители данных,г первый, второй и третий коммутаторы, первый формирователь сигналов четности, элемент И, первый элемент ИЛИ, блок сравнения и блок свертки по модулю три, выходы которого соединены с одними из входов блока сравнения, введены накопители контрольной информации, блок восстановления информации, блок 5Т1равления, преобразователь кодов, второй и третий формирователи сигналов четности, блок местного управления и второй элемент.ИЛИ, причем входы и выходы основных и резервных накопителей подключены соответственно к одним из выходов и входов блока местного уйравления, другие входы и .выходы которого .соединены с . выходами и входами первой первого коммутатора, входы и выходы второй группы которого подключены к одним .из. вьгходов и входов блока уп- равнения, другие вьпсоды и входы которого соединены с одними из входов и выходов блока восстановления информации, другие вход и выход которого подключены соответственно к выходу третьего коммутатора и к первому входу второго коммутатора, выходы которого соединены с информационными входами накопителей контрольной информации, причем управляющие выходы блока восстановления информации подключены соответственно к входам первой группы и к управляющему входу третьего коммутатора, к адресным и к управляющим входам накопителей контрольной информации, к управляющим входам второго коммутатора и к управляпщим входам преобразователя кодов, один из входов которого соединены с одними из выходов накопителей контрольной информации, входами второй группы третьего коммутатора, входами перво-. го формирователя сигналов четности, одними из входов второго формирователя сигналов четности, входами блока свертки по модулю три и второго элемента ИЛИ, другие выходы накопителей контрольной информации подключены соответственно к входам третьей груп пы третьего коммутатора, входам элемента И, входам первого элемента ИЛИ |И другим входам блока сравнения, к первому входу третьего коммутатора и другому входу второго формирователя сигналов четности, к второму входу третьего коммутатора, выход перв.о го и инверсный выход второго формирователей сигналов четности соединены соо.тветственно с .вторым и с третьим входами второго коммутатора, другие входы преобразователя кодов подключены соответственно к выходу второго элемента ИЛИ,, четвертому вхо ду второго коммутатора и первому управляющему входу блока восстановления информации, и к выходу блока срав нения, пятому входу второго коммутатора и второму управляющему входу блока восстановления информации, третий и четвертый управляющие входы которого соединены соответственно с выходом первого элемента ИЛИ и с выходом элемента И, шестой вход второго коммутатора подключен к инверсному выходу третьего формирователя сигналов четности, входы которого соединены с одними из выходов преоб.раэователя кодов, выходы которого подключены к входам первой группы второго, коммутатора, входы второй группы которого соединены с выходами блока свертки по модулю три, входы и выходы третьей группы первого коммутатора .являются входами и выходами устройства. Блок з равления содержит первый накопитель микрокоманд, дешифраторы, первьй шифратор, регистры, элементы И-ИЛИ, группу элементов И, первый формирователь управляющих сигналов, вход синхронизации которого соединен с выходом генератора тактовьпс импуль сов, а одни из выходов подключены к входам первого накопителя микрокоманд, выходы которого подключены соответственно к первым входам элементов И-ИЛИ, к управляющим входам первого и второго регистров, к вторым входам элементов И- fflИj входам третьего и Четвертого регистров, к управляющему входу первого Дешифратора К управляющему входу первого шифрато ра, к входам и к управляющим входам второго дешифратора, к управляющему входу пятого регистра, к первым входам элементов И группы и к одним из входов первого формирователя управу ляющих сигналов, другие входы которого подключены к выходам первого шифратора, входы которого соединены с выходами первого дешифратора, причем третьи входы элементов И-ИЖ подклю- чены к выходам второго регистра, а выходы - к .входам первого регистра, выходы второго дешифратора соединены с управляющими входами третьего и четвертого регистров соответственно, вьтходы элементов И группы соединены с входами пятого регистра, входы первого регистра, первого дешифратора и вторые врсоды элементов И группы являются одними из входов блока, одними из выходов которого являются выходы третьего регистра, другими входами блока являются входы второго регистра, а другими выходами - другой выход первого накопителя микрокоманд, выходы четвертого и пятого регистров. Блок восстановления информации содержит второй накопитель микрокоманд, второй шифратор, третий дешифратор, регистры с шестого по девятый, счетчик, формирователи управляющих сигналов с второго по одиннадцатый и формирователь тактовых импульсов, выход которого соединен с входом синхронизации второго формирователя управляющих сигналов, выходы которого подключены к входам второго накопителя микрокоманд, выходы которого соединены соответственно с управляющим входом и с входом сдвига шестого регистра, с входами формирователей управляющих сигналов с третьего по одиннадцатьй, с входами регистров с седьмого по , с входами и с управляющим входом третьего дешифратора и. с одними из входов второго формирователя управлякяцих сигналов, одни из управляющих входов которого подключены к выходам второго шифратора, выходы третьего дешифратора соединены с управлякнцими входами седьмого , восьмого и девятого регистров соответственно,установочнЬй и счетный входы счетчика подключены соответственно к выходам восьмого и девятого формирователей управляющих сигналов, входы шестого регистра, вход формирователя тактовых импульсов , другие входы и другой управляющий вход второго формирователя управляющих сигналов являются входами блока, выходами которого являются выходы шестого регистра, входы второго шиАратора .являются управлякяцими входами блока, управляющими выходами которюго являются выходы регистров с седьмого по девятый, выходы счетчика выходы формирователей управляющих си налов с третьего по седьмой, десятог и одиннадцатого. На фиг.1 представлена функциональ ная схема предложенного устройства; на фиг. 2 и 3 - функциональные схемы, блока управления и блока восстановле- ния информации соответственно; на фиг,4 и 5 - функциональные схемы наиболее предпочтительных вариантов выполнения преобразователя кодов и блока свертки по модулю три соответ- ственио. Предложенное устройство содержит (фиг.1) основные накопители I данных резервные накопители 2 данных, блок 3 местного управления, первый коммутатор 4 ,. блок 5 управления, блок 6 восстановления информации, накопители 7 - 7j. контрольной ииформации, второй 8 и третий 9 коммутаторы, преобразователь 10 кодов, блок 11 свертки по модулю три, формирователи сигналов 12,13 и 14 четности с первого по третий, блок 15 сравнения, первый 16 и второй 17 элементы ИЛИ, элемент И 18. На фиг.1 обозначены входы и выходы 19 устройства,.информационные выходы и входы 20 и входы 21, одни из управляющих выходов 22-31 и информационный выход 32 блока 6 восстановления информации, информационные входы 33-36 и выходы 37-40 накопи телей 7 контрольной ииформации, управ ляющие входы 41-44 и другие управляющие выходы 45-47 блока 6 восстановления ииформации, входы 48-53 коммутаго ра 8. Блок 5 управления содержит (фиг.2) первый формирователь 54 управляющих сигналов, генератор 55 тактовых импульсов, первый накопитель 56 микрокоманд, регистры 57-61 с первого по пятый, первый 62 и второй 63 дешифраторы, первый шифратор 64 элементы И-ИЛИ 65 и группа элементов И 66.- . Блок 6 восстановления информации содержит ( фиг.3 Jвторой Аормирователь 67 управляющих сигналов,-формирователь 68 тактовых импульсов, второй накопитель 69 микрокомаид, третий дешифратор 70, регистры 71-74 с шестого по девятый, счетчик 75, форми- ; рователи 76-84 управляющих сигналов с третьего по одиннадцатый и второй шифратор 85. Формирователи 76-84 могут быть реализованы на двух ИМС К155АГ1 между которыми необходимо включить диф ференцирующую цепочку. Формирователь 54 можно выполнить на ИМС К58.9ИК01 , генератор 55 - на мультивибраторе , накопитель 56 на ИМС К556РТ7, регистры 57 - 61 - на ИМС К589Ш12. Преобразователь 10 кодов содержит (фиг.4) элемент И 86, RS - триггер 8/, регистр 88, элемент И 89, группы элементов И 90, элемент И 91. Блок I1 свертки по модулю три содержит /фиг.5) сумматоры 92-95 по модулю два. В качестве блока 3 местного управления при использовании накопителей 12, например на магнитных дисках типа ЕС 5050 или ЕС 5056М, нужно использовать БУН типа ЕС 5551 М, который вьшускается отечественной промьшшенностью серийно. Накопитель 7 контрольной информации состоит из трех накопителей: первьш накопитель 7 емкость KNx пять бит предиазначен для хранеиия информации, считьшаемой с накопителей 1, второй накопитель 7 емкостью KNx три бит предназначен для хранения информации иакопителей 2, третий накопитель 7 емкостью KNx один бит отводится для временного хранения восстановленных данных отказавшего накопителя I, где N - целое числозначение разрядности минимально адресуемой единицы Информации (МАЕ), К - число считываемых МАЕ, которые выбираются исходя из требований минимальиьк потерь времени на восстановление и перезапись информации в устройстве. В качестве МАЕ выбираются фиксированные массивы данных, например при применении в качестве иакопителей 1 и 2 НМД - фиксированное поле даиных одного сектора диска, НМЛ поле данных зоны, накопителей на цилиндрических магнитных домеиах страница данных или блок данных (страница данных х число параллельно. работающих микросхем). Устройство, содержащее пять накопителей 1 и три накопителя 2 иа магнитных дисках, работает следующим обраэом.

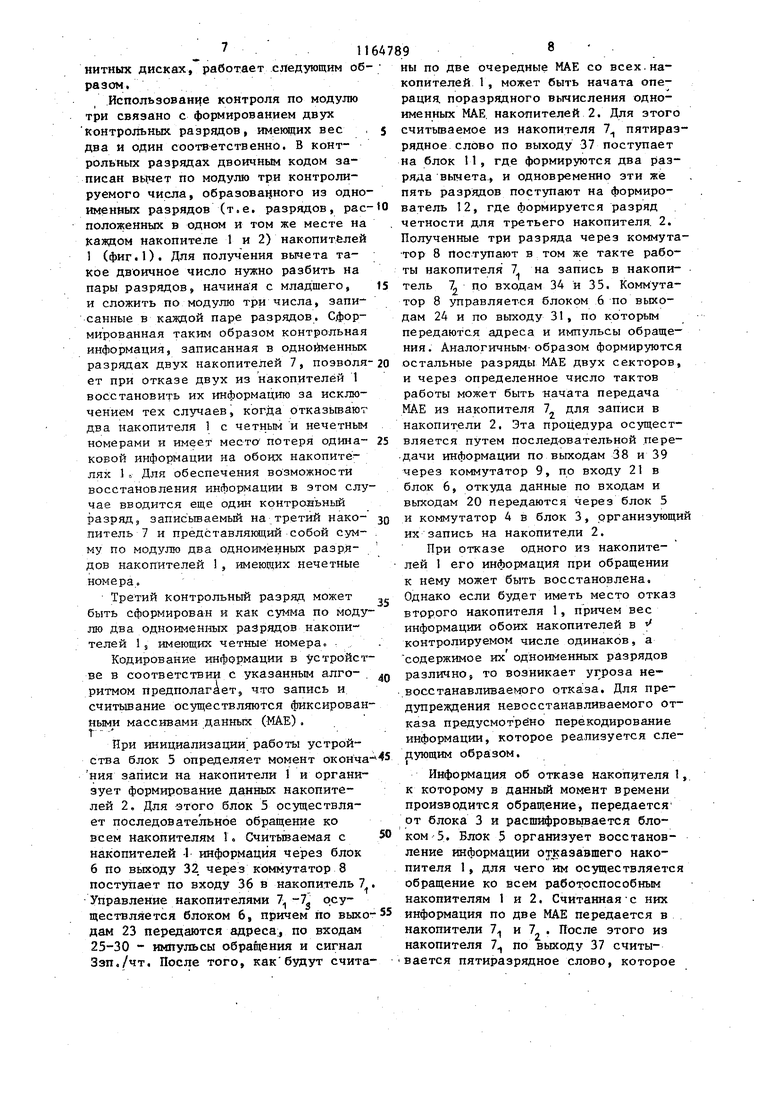

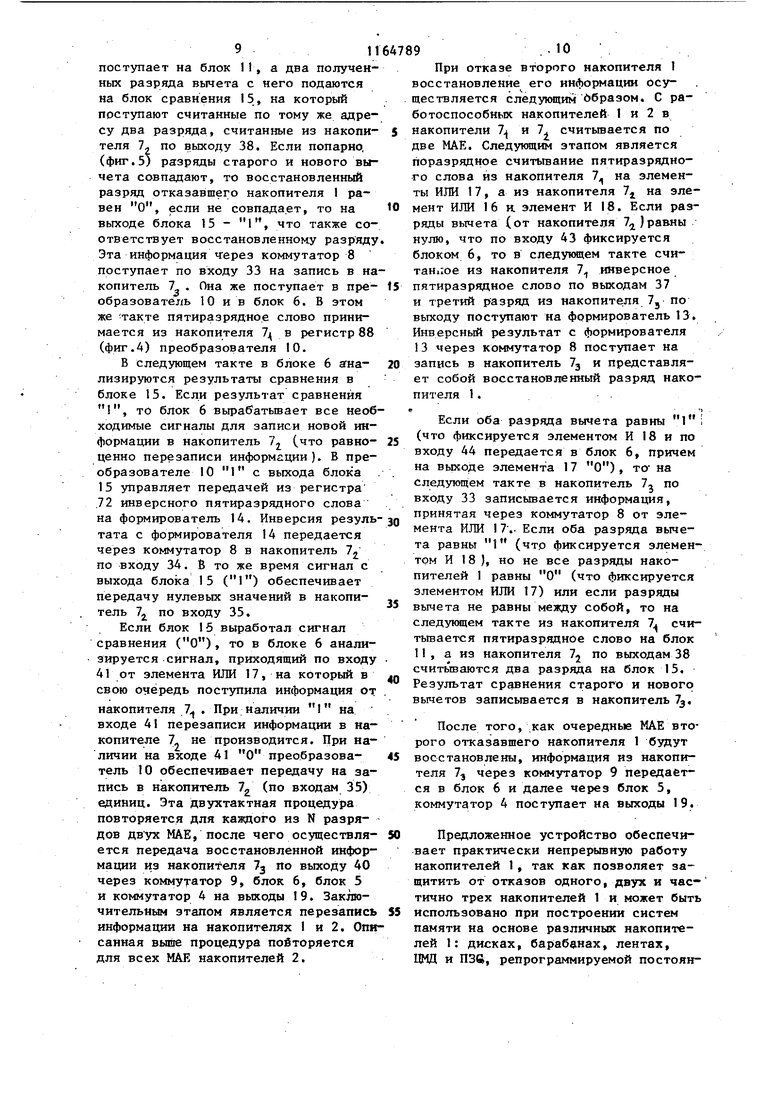

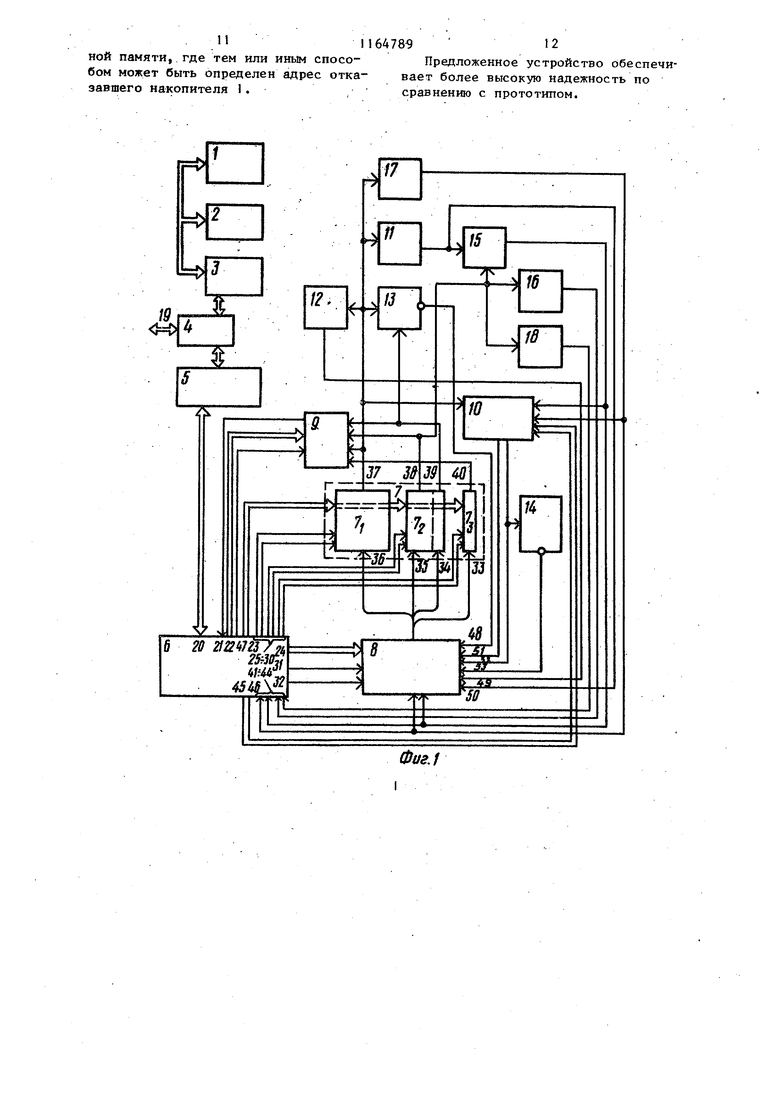

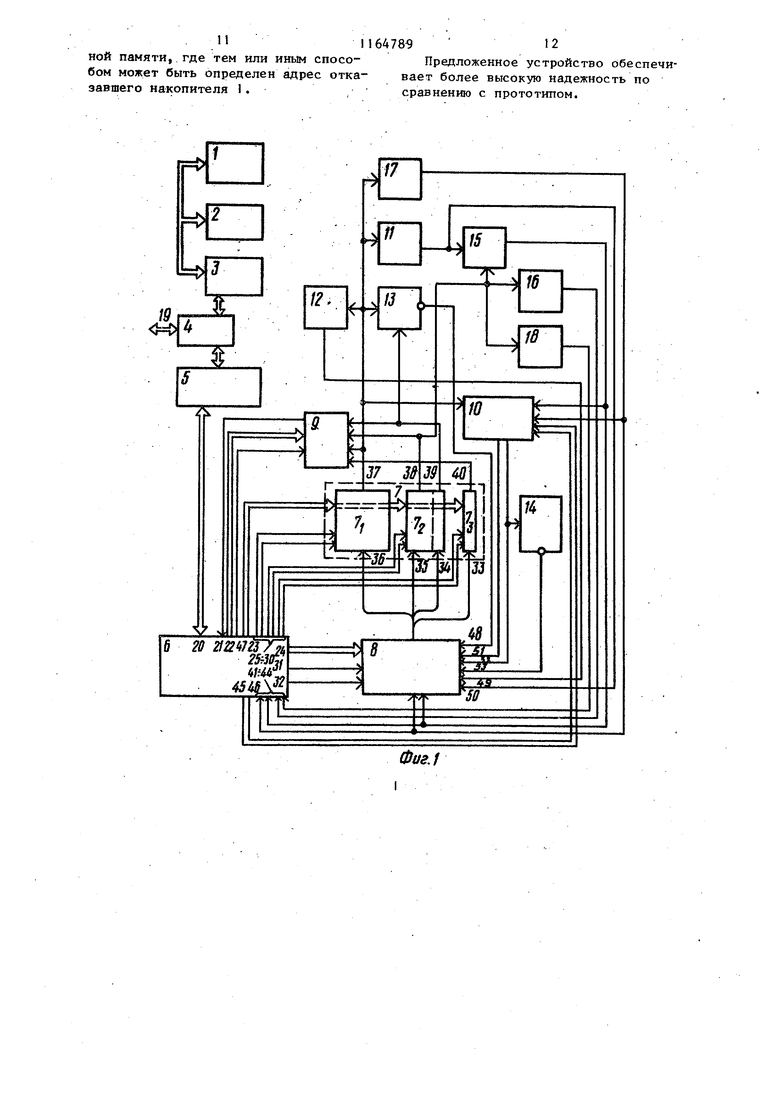

Использование контроля по модулю три связано с формированием двух контрольных разрядов, имекмдих вес , два и один соответственно. В контрольных разрядах двоичным кодом записан вьгчет по модулю три контролируемого числа, образованного из одноименных разрядов (т.е. разрядов, рас-О положенных в одном и том же месте на каждом накопителе 1 и 2) накопителей 1 (фиг.1). Для получения вычета такое двоичное число нужно разбить на пары разрядов, начиная с младшего, и сложить по модулю три числа, запи санные в каждой паре разрядов. Сформированная таким образом контрольная информация, записанная в одноименных разрядах двух накопителей 7, поэволя ет при отказе двух из накопителей 1 восстановить их информацию за исклочением тех случаев, когда отказывают два накопителя 1 с четным и нечетным номерами и имеет место потеря одинаКОБОЙ информации на обоих накопителях 1 о Для обеспечения возможности восстановления информации в этом слу чае вводится еще один контрольный разряд, записьшаемый на третий накопитель 7 и представлякяций собой сумму по модулю два одноимённых разрл дов накопителей 1, имеющих нечетные номера. Третий контрольньй разряд может быть сформирован и как сумма по моду лю два одноименных разрядов накопителей 1S имеющих четные номера. : Кодирование информации в устройст ве в соответствии с указанным алго- . ритмом предполагает, что запись и считывание осуществляются фиксирован ными массивами данных (МАЕ). Г-- , , При инициализации работы устройства блок 5 определяет момент оконча ния записи на накопители 1 и организует формирование данных накопителей 2. Для этого блок 5 осуществляет последовательное обращение ко всем накопителям 1. Считьгоаемая с накопителей -1 информация через блок 6 по выходу 32, через коммутатор 8 поступает по входу 36 в накопитель 7 Управление накопителями 1 -7 о.существляется блоком 6, причем по выхо дам 23 передаются адреса,, по входам 25-30 - импульсы обращения и сигнал Ззп./чт. После того, какбудут счита

ны по две очередные МАЕ со всех.накопителей 1, может быть начата операция поразрядного вычисления одноименных МАЕ. накопителей 2. Для этого считьшаемое из накопителя 7 пятиразрядное слово по выходу 37 поступает на блок 11, где формируются два разряда вычета,, и одновременно эти же пять разрядов поступают на формирователь 12, где формируется разряд четности для третьего накопителя. 2. Полученные три разряда через коммутатор В поступают в том же такте работы накопителя 7 на запись в накопитель по входам 34 и 35. Коммутатор 8 управляется блоком 6 по выходам 24 и по выходу 31, по которым передаются адреса и импульсы обращения. Аналогичным-образом формируются остальные разряды МАЕ двух секторов, и через определенное число тактов работы может быть начата передача МАЕ из накопителя 7 для записи в Накопители 2. Эта процедура осуществляется путем последовательной .передачи информации по выходам 38 и 39 через коммутатор 9, по входу 21 в блок 6, откуда данные по входам и выходам 20 передаются через блок 5 и коммутатор 4 в блок 3, организующий их запись на накопители 2. При отказе одного из накопителей 1 его информация при обращении к нему может быть восстановлена. Однако если будет иметь место отказ второго накопителя 1, причем вес информации обоих накопителей в контролируемом числе одинаков, а содержимое их одноименных разрядов различно, то возникает угроза невосстанавливаемого . Для предупреждения невосстанавливаемого отказа предусмотрено перекодирование информации, которое реализуется следующим образом. Информация об отказе накопителя 1,. к которому в данный момент времени производится обращение, передается от блока 3 и расшифровывается блоком 5. Блок 5 организует восстановление информации от саэавшего накопителя 1, для чего им осуществляется обращение ко всем работоспособным накопителям 1 и 2. Считанная-с них информация по две МАЕ передается в накопители 7 и 7 . После этого из накопителя 7 по выходу 37 считывается пятиразрядное слово, которое 911 поступает на блок 11, а два полученных разряда вычета с него подаются на блок сравнения 15, на который поступают считанные по тому же адресу два разряда, считанные из накопителя 7, по выходу 38. Если попарно, (фиг.5) разряды старого и нового вычета совпадают, то восстановленный разряд отказавшего накопителя 1 равен О, если не совпадает, то на выходе блока 15 - 1, что также соответствует восстановленному разряду Эта информация через коммутатор 8 поступает по входу 33 на запись в на копитель 7-. Она же поступает в преобразоватёль 10 и в блок 6. В этом же такте пятиразрядное слово принимается из накопителя 7. в регистр 88 (фиг.4) преобразователя 10. В следующем такте в блоке 6 агнализируются результаты сравнения в блоке 15. Если результат сравнения 1, то блок 6 вырабатьшает все необ ходимые сигналы для записи иовой информации в накопитель 7 (что равноценно перезаписи информации). В преобразователе 10 1 с выхода блока 15 управляет передачей из регистра .72 инверсного пятиразрядного слова на формирователь 14. Инверсия резуль тата с формирователя 14 передается через коммутатор 8 в накопитель 7 по входу 34. 6 то же время сигнал с выхода блока I5 (1) обеспечивает передачу нулевых значений в накопитель 7 по входу 35. Если блок 15 выработал сигнал сравнения (О), то в блоке 6 анализируется сигнал, приходящий по входу 41 от элемента ИЛИ 17, на который в свою очередь поступила информация от накопителя 7 . При наличии 1 на входе 41 перезаписи информации в накопителе 7« не производится. При наличии на входе 41 О преобразователь 10 o6ecne4HBvaeT передачу на запись в накопитель 7 (по входам 35) единиц. Эта двухтактная процедура повторяется для каждого из N разрядов двух МАЕ, после чего осуществляется передача восстановленной информации из накопителя 7 по выходу 40 через коммутатор 9, блок 6, блок 5 и коммутатор 4 на выходы 19. Заключительным этапом является перезапись информации на накопителях 1 и 2. Опи санная выше процедура повторяется для всех МАЕ накопителей 2. 9 При отказе второго накопителя 1 восстановление его информации осуществляется следующим Образом. С работоспособных накопителей 1 и 2 в накопители 7 и 7 считьшается по две МАЕ. Следующим этапом является поразрядное считывание пятиразрядного слова из накопителя 7 на элементы ИЛИ 17, а из накопителя 7 на элемент ИЛИ 16 и. элемент И 18. Если разряды вычета (от накопителя 7,)равны нулю, что по входу 43 фиксируется блоком 6, то в следующем такте счиTaHiioe из накопителя 7 инверсное пятиразрядное слово по выходам 37 и третий разряд из накопителя 7, по выходу поступают на формирователь 13. Инверсный результат с формирователя 13 через коммутатор 8 поступает на запись в накопитель 7 и представляет собой восстановленный разряд накопителя 1. Если оба разряда вычета равны 1 (что фиксируется элементом И 18 и по входу 44 передается в блок 6, причем на вькоде элемента 17 О) , то на следующем такте в накопитель 7 по входу 33 записывается информация. коммутатор 8 от элемента ИЛИ 17.. Если оба разряда вычета равны 1 (что фиксируется злементрм И 18 ), но не все разряды накопителей 1 равны О (что фиксируется элементом ИЛИ 17) или если разряды вычета не равны между собой, то на следующем такте из накопителя 7 считьгаается пятиразрядное слово на блок 11, а из накопителя 7 по выходам 38 считываются два разряда на блок 15. Результат сравнения старого и нового вычетов записывается в накопитель 7j. После того, как очередные МАЕ второго отказавшего накопителя 1 будут восстановлены, информация из накопителя 7э через коммутатор 9 передается в блок 6 и далее через блок 5, коммутатор 4 поступает на выходы 19. Предложенное устройство обеспечивает практически непрерывную работу накопителей 1, так как позволяет защитить от отказов одного, двух и частично трех накопителей 1 и может быть использовано при построении систем памяти на основе различных накопителей 1: дисках, барабанах, лентах, ЦМД и ПЗв, репрограммируемой постоян1 1164789 12

ной памяти,.где тем или иным спосо- Предложенное устройство Обеспечибом может быть определен адрес отка- вает более высокую надежность по завшего накопителя 1.сравнению с прототипом.

| название | год | авторы | номер документа |

|---|---|---|---|

| Резервированное запоминающее устройство | 1983 |

|

SU1149317A1 |

| Резервированное запоминающее устройство | 1983 |

|

SU1149319A1 |

| Запоминающее устройство с самоконтролем (его варианты) | 1982 |

|

SU1117714A1 |

| Резервированное запоминающее устройство | 1981 |

|

SU972601A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1164706A1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| Микропрограммный процессор | 1981 |

|

SU980095A1 |

| Микропрограммный процессор | 1982 |

|

SU1062712A1 |

| Перестраиваемый микропрограммный процессор | 1981 |

|

SU983713A1 |

| Запоминающее устройство с самоконтролем | 1982 |

|

SU1091228A1 |

1. РЕЗЕРВИРОВАННОЕ .ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО, содержащее основные и резервные накопители данных, первый, второй и третий коммутаторы, первый формирователь сигналов четности, элемент И, первый элемент ИЛИ, блок сравнения и блок свертки по модулю три, выходы которого соединены с ОДН1Ф1И из входов блока сравнения, отличающеся тем, что, с целью повьппения надежности устройст , в него введены накопители контрольной информации, блок восстановления информации, блок управлеиия, пре образователь кодов, второй и третий формирователи сигналов четности, блок местного управления и второй элемент ИЛИ, причем входы и выходы основных и резервных накопителей подключены соответственно к из выходов и входов блока местного управления, другие входы и выходы которого соединены с выходами и входами первой группы первого коммутатора, входы и выходы второй группы которого подключены к одним из выходов и входов блока управления., другие выходы и входы, которого соединены с одними ,из входов и выходов блока восстановления информации, другие вход и выход которого подключены соответственно к выходу третьего коммутатора и .к первому входу второго коммутатора, выходы которого соединены с информационными входами накопителей контрольной информации, причем управляющие выходы блока восстановления информации подключены соответственно к входам первой группы и к управляющему входу третьего коммутатора, к адресным и к управляющим входам накопителей контрольной информации, к управляющим входам второго коммутатора и к управл}Пощим входам преобра(Л зователя кодов, одни из входов которого соединены с одними из выходов накопителей контрольной инфор 4ации, входами второй грзшпы третьего коммутатора, входами первого формирювателя сигналов четности, одними из входов второго формирователя сигналов О) 4 Четности, входами блока свертки по модулю три и второго элемента ИЛИ, другие, выходы накопителей контрольной эо со информации подключены соответственно к входам третьей группы третьего коммутатора, входам элемента И, входам первого элемента ЯЛИ и другим входам блока сравнения, к первому входу третьего коммутатора и другому входу второго формирователя сигналов четности, к второму входу третьего коммутатора, выход первого и инверсный выход второго формирователей сигналов четности соединены соответственно с вторым и с третьим входами второго коммутатора, другие входы пре

Jl

ш

W

SI

57ti

56

62 f

64 «

63

20

14

f

55

3ff

Ж

§ I

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент CMIA № 3876978, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| опублик | |||

| Сплав для отливки колец для сальниковых набивок | 1922 |

|

SU1975A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Резервированное запоминающее устройство | 1981 |

|

SU972601A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1985-06-30—Публикация

1983-12-29—Подача