(З) РЕВЕРСИВНЫЙ СЧЕТЧИК ИМПУЛЬСОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Реверсивное счетное устройство | 1983 |

|

SU1112570A1 |

| СПОСОБ ИЗМЕРЕНИЯ СКОРОСТИ ВРАЩЕНИЯ ВАЛА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2017156C1 |

| Функциональный аналого-цифровой преобразователь | 1985 |

|

SU1260979A1 |

| Цифровой фазометр | 1989 |

|

SU1711090A1 |

| Устройство для сортировки информации | 1986 |

|

SU1365075A1 |

| Цифровой фазометр | 1987 |

|

SU1499264A1 |

| ЛИНЕЙНО-КРУГОВОЙ ИНТЕРПОЛЯТОР | 1991 |

|

RU2010293C1 |

| Устройство поэлементной синхронизации | 1987 |

|

SU1517142A1 |

| Устройство для программного счета изделий | 1983 |

|

SU1113824A1 |

| Устройство для автоматического переключения однофазных нагрузок в низковольтных распределительных сетях | 1981 |

|

SU1026234A1 |

Изобретение относится к импульсной технике и может быть использовано в вычислительных и измерительных устройствах. Известен реверсивный счетчик импульсов, содержащий реверсивные сче ные разряды, устройство индикации, триггер знака и схему выделения нулевого состояния 1. Однако это устройство обладает .недостаточной надежностью. Известен также реверсивный счетчик импульсов, содержащий последовательно, соединенные счетные разряды, выходы которых соединены с соответствующими входами устройства индикации и схемы выделения нулевого состояния всех разрядов, триггер зн ка, управляющий вход которого соединен с выходом устройства выделения нулевого состояния всех разрядов, а выходы подключены к управляю |и(им входам коммутатора входов Г2. Недостатком известного устройст ва также является невысокая надежность. Цель изобретения - повышение надежности счетчика импульсов. Поставленная цель достигается тем что в реверсивном счетчике импульсов, содержащем последовательно соединенные счетные разряды, выходы которых соединены с соответствующими входами устройства индикации и схемы выделения нулевого состояния всех разрядов, триггер знака, управляющий вход которого соединен с выходом устройства выделения нулевого состояния всех разрядов, а выходы подключены к управляющим входам коммутатора входов,информационные входы триггера знака подключены к прямым выходам формирователей сигналов, входы которых являются входами устройства, а инверсные выходы соединены с соответствующими информационными входами

310

коммутатора входов и входами элемента задержки, выход которого подключен к первому входу триггера разрешения счета, второй вход которого соединен с инверсным выходом схемы выделения нулевого состояния всех разрядов, а выход - с управляющими входами ключей, выходы которых подключены соответственно к входам сложения и вычитания первого разряда счетчика, а информационные входы соединены с выходами коммутатора входов, причем вход обнуления триггера разрешения счета и счетных разрядов соединены между собой и подключены к третьему входу устройства.

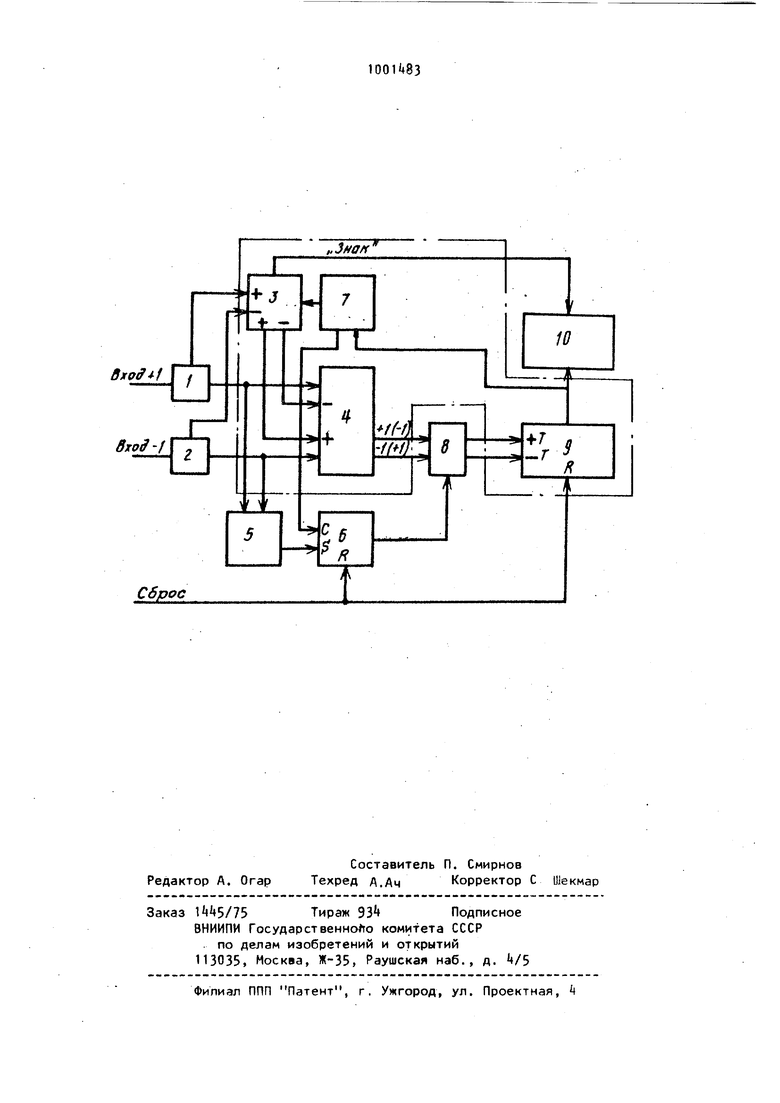

На чертеже представлена блок-схема реверсивного счетчика.

Реверсивный счетчик импульсов содержит формирователи 1 и 2 импульсов, прямые выходы которых подключены к информационным входам триггера 3 знака, а инверсные выходы - к соответствующим информационным входам коммутатора 4 и входам элемента 5 задержки, выходом подключенного к первому входу триггера 6 разрешения сче та.Входы триггера 3 знака соединены с управляющими входами коммутатора i. Второй вход триггера 6 разрешения счета соединен с инверсным выходом схемы 7 выделения нулевого состояния всех разрядов, прямой выkoд которой соединен с управляющим входом триггера 3 знака. Выходы коммутатора соединены с соответствующими входами ключей 8, управляющие входы которых подключены к выходу триггера 6 разрешения. Выходы ключей 8 соединены с соответствующими входами .первого разряда счетчика 9. Все разряды счетчика 9 соединены с входами схемы 7 выделения нулевого состояния и с устройством 10 индикации.

Устройство работает следующим образом.

Изменение состояния триггера 3 знака возможно при одновременном появлении высоких потенциалов на входе управления и на одном из информационных входов.

Величина задержки импульса в элементе 5 задержки должна превышать время переходных процессов в триггере знака и коммутаторе входов, но не должна превышать минимального времени между двумя соседними входными

пульсами, поступающими по обоим входам. В начальный момент после включения реверсивный счетчик импульсов может иметь произвольные состояния.

5 Предположим, что счетчик имеет состояния, показанные на чертеже.

Выход + триггера 3 знака равен

логическому О, выход

логической 1. Выход элемента 5 задержки установки триггера разрешения 6 в единичное состояние равен логической 1, сигнал Разрешение с выхода триггера б также равен логической 1. Выход схемы 7 выделения нулевого состояния счетчика равен логическому О соответственно, инверсный выход схемы 7 (С- вход триггера 6 разрешения)равен логической 1.

В начале работы передним фронтом сигнала Сброс происходит установка триггера 6 разрешения в нулевое состяние и сброс в О всех разрядов счетчика 9. Состояние триггера 3 знака при этом не меняется, так как он

реагирует только на входные сигналы.

Реверсивный счетчик работает от инверсных входных импульсов. Первый входной импульс, поступивший, например, по входу +1 отрицательным перепадом, т.е. передним фронтом импульса, запускает формирователь 1, который калибрует длительность выходного импульса, не зависящую отчдлительности входного. Импульс с прямого

выхода формирователя 1 поступает на вход + триггера 3 знака и передним фронтом устанавливает его в соответствующее состояние,, при котором на выходе + триггера появляется

логическая 1, а на выходе - логический О. Импульс с инверсного выхода поступает одновременно на коммутатор k и элемент 5 задержки. При этом на выходе коммутатора появляется ложный импульс, длительность которого равна времени переключения триггера знака и коммутатора. Но так как сигнал Разрешение, задержанный элементом 5 задержки, равен еще О, то ни на входе +Т, ни входе -Т счетчика импульс не появляется.

Входной импульс на входе счетчика появляется после срабатывания триггера 6 по сигналу с выхода элемента 5 задержки. При этом на выходе триггера 6 разрешения появляется логическая 1 и ключи 8 открываются. 5 пропуская импульс (и все последующие) с выхода +1 коммутатора k. Положительный перепад, т.е. задний фронт импульса по входу +Т, записыв ет в счетчик 9 единицу. При последующем подсчете импульсов по входу +1 состояния триггера 3 знака и три гера 6 разрешения не меняются. Текущее состояние счетчика определяет ся разностью числа импульсов, посту пающих на вход +Т и вход -Т. Если число импульсов, поступающих на вход -Т, оказывается равным числу импульсов, поступающих на вхо +Т, то задним фронтом импульса по входу -Т счетчик 9 устанавливается в нуль. Отрицательный перепад импул са со схемы 7 выделения нулевого состояния счетчика по С-входу триггера 6 разрешения устанавливает последний в состояние логического О, закрывая ключи 8. Следующий им пульс, поступающий по входу -1 устанавливает триггер 3 знака в соответствующее состояние, при котором на выходе + появляется логический О, .а на выходе - -логическая 1 Коммутатор k также принимает соответствующее состояние, и согласно описанному вышг, на его выходе появ ляется ложный импульс, который, однако, на выход ключей не проходит, так как сигнал Разрешение еще равен О, Через время задержки эле мента 5 ключи 8 открываются и импульс появляется на входе +Т счетчи ка, но знак при этом будет минус. Аналогично происходит подсчет импульсов в любую сторону от нулево го состояния сметчика 9Таким образом, повышение надежности pa6otbi реверсивного счетчика достигается исключением ложных импульсов, появляющихся вследствие переходных процессов при переключении режимов работы устройства. 83 Формула изобретения Реверсивный счетчик импульсов, содержащий последовательно соединен- , ные счетные разряды, выходы которых соединены с соответствующими входами устройства индикации и схемы выделения нулевого состояния всех разрядов, триггер знака, управляю- щий вход которого соединен с выходом устройства выделения нулевого состояния всех разрядов, а выходы подключены к управляющим входам коммутатора входов, отличающийся тем, что, с целью повышения надежности, информационные входы триггера знака подключены к прямым выходам формирователей сигналов, входы которых являются входами устройства, а инверсные выходы соединены с соответствующими информационными входами коммутатора входов, и входгми элемента задержки, выход которого подключен к первому входу триггера разрешения счета, второй вход которого соединен с инверсным выходом схемы выделения нулевого состояния всех разрядов, а выход - с управляющими входами ключей; выходы которых подключены соответственно к входам сложения и вычитания первого разряда счетчика, а информационные входы соединены с выходами коммутатора входов, причем вход обнуления триггера разрешения счета и счетных разрядов соединены между собой и подключены к третьему входу устройства. Источники информации, принятые во внимание при экспертизе 1.Авторскоесвидетельство СССР № , кл. Н03 К 23/00, 1970. 2.Авторскоесвидетельство СССР N- , кл. Н03 К 23/00, 1975 (прсттотип) .

Авторы

Даты

1983-02-28—Публикация

1981-05-18—Подача