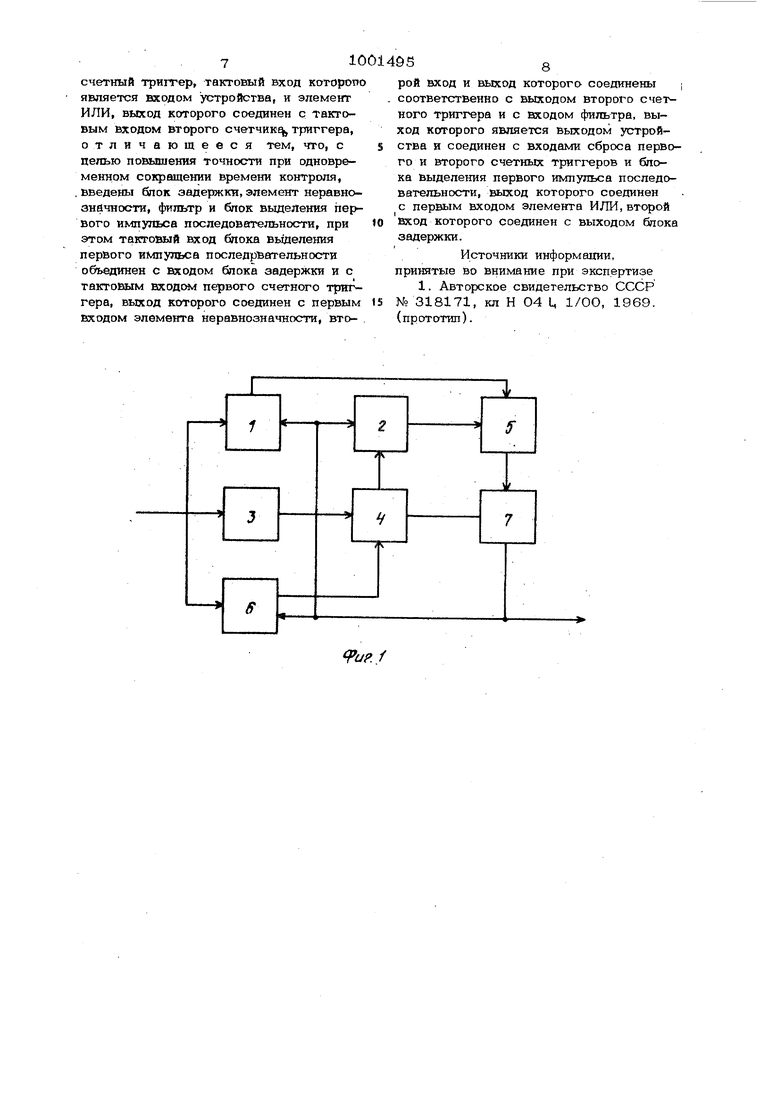

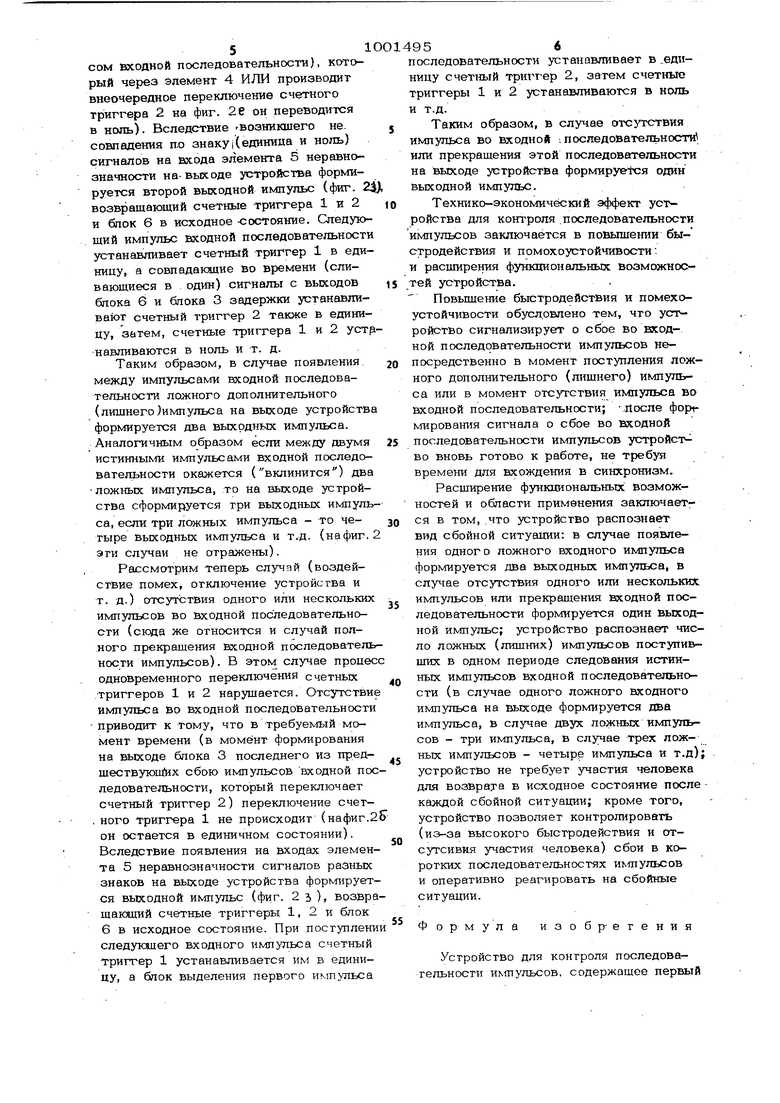

(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПОСЛЕДОВАТЕЛЬНОСТИ ИМПУЛЬСОВ Устройство относится к электросвязи и может бытъ использовано для анализа сбоев последовательности импульсов. Известно устройство для контроля последовательности импульсов, содержащее первый счетный триггер, тактовый вх которого является, входом устройства, и элемент ИЛИ, выход которого соединен с тактовым входом второго счетного триггера t1 3 Однако известное устройство требует большого времени и не обеспечивает высокой точности контроля. Цель изобретения - повышение точности при одновременном сокращении времени контроля. Для достижения указанной цели в ус ройство для контроля последовагельност импульсов, содержащее первый счетный триггер, тактовый вход которого являет ся входом устройства, и элемент ИЛИ, выход которого соединен с тактовым входом второго счетного триггера, вг5едены блок задержки, элемент неравнозначности, фильтр и блок выделения первого импульса последовательности, при этом тактовый вход блока выделения первого импульса последовательности объединен с входом блока задержки и с тактовым входом первого счетного триггера, выход которого соединен с первым Екодом элемента неравнозначности, второй вход и выход которого соединены соответственно с выходом второго счетного триггера, с входом фильтра, выход которого является выходом устройства и соединен с входами сброса первого и второго счетных триггеров и блока выделения первого импульса последовательности, выход которого соединен с -первым входом элемента ИЛИ, второй вход которого соединен с выходом блока задержки. На фиг. 1 приведена структурная электрическая схема устройства; но фиг. 2 - В1 емениая диаграмма его работы. Устройство содержит первый и второй счетные триггеры 1 и 2 блок 3 зедержки, элемент ИЛИ 4, элемеш- 5 неравнозначности, блок 6 вьщеления первого импульса последоват« ЯЬности и фильтр 7. На фиг. 2 введены следующие обозначения: с( - последовательность вход ных импульсов, б - имтгутгьсы на выходе первого счетного; триггера, & - импульсы на выходе блока выделения первого импульса из последовательности, -V - импуттьсы на выходе блока задержки, Э - импульсы на выходе элемента ИЛИ, е - импульсы на выходе второго счетного триггера, Ж - импульсы ни выходе элемента неравнозначности, Ь импульсы на выходе устройства. Счетные триггеры 1 и 2 имеют поте т1альные выходы разрядов. Блок 3 осуществляет задержку входных импульсов на время Т, принятое равным периоду следования входных импульсов. Фильтр 7 предназначен для управления случайных помех (всплесков единим ного уровня) на выходе элемента 5 нер нпзначности, которые возникают нестабильности переходных процессов в случае низкого быстродействия приме ненных логических элементов и нестабильности времени задержки блока 3. В качестве фильтра.7 используется интегрируклцая RCuenb. Устройство работает следуклцим образом. При включении питания счетные триг геры 1 и 2 и блок 6 переводятся в нулевое (сброшенное состояние). При поступлении на вход устройства последовательности .импульсов (фиг. 2с) первый же импульс устанавливает счетный триггер 1 в единичное состояние (фиг. 25) и вьщеляется блоком 6 выделения первого импульса (фиг. 2в). Выделенный блоком 6 импульс проходит через элемент 4 ИЛИ (фиг. 2 Э) и уст навливает счетный триггер 2 также в единичное состояние (фиг. 2 ie ), всле/iст ие чего на выходе элемента 5 нерав нозначности сигнал не формируется (фиг. 2 ). Второй из импульсов входно последовательности устанавливает счет ный триггер 1 в нулевое состояние. Однако в это время (т.е. спустя время Т, где Т- период следования входных импутпьсов) на выходе блока 3 задержки (фиг. 2t,) формируется импульс, которы является первым задержанным импульсом из входной последовательности импульсов (его формирование совпадает во времени с поступлением на вход устройства второго импульса). Импульс с выхода блока 3 задержки проходит через элемент 4 ИЛИ и устанавливает счетный триггер 2 также в ноль. Вследствие этого импульс на выходе элемента 5 неравнозначности не формируется. Третий Входной импульс устанавливает счетный триггер 1 в единицу, одновременно с этим второй задержанный импульс устанавливает счетный триггер 2 в единицу, затем счетные триггеры 1 и 2 устанавливаются в ноль и т. д. Пусть (например, из-за воздействия помех) Во входной последовательности оказьгоается ложный (лишний) импульс (фиг. 2d). В этом случае процесс одновременного переключения счетных триггеров 1 и 2 нарушается. Поступление дополнительного импульса приводит к неочередному переключению счетного триггера 1 (фиг. 25), он переводится В единичное состояние). Вследствие этого -на входах элемента неравнозначности формируются сигналыразных логических уровней: ноль и единица. Поэтому на выходе элемента 5 формируется импуттьс (фиг. 2 ж), который через фильтр 7 проходит на выход устройства (фиг. 2 ъ), одновременно с этим возвращая счетные триггера 1 и 2 и блок 6 в исход- , ное состояние. Вслед за этим на вход устройства поступает очередной импульс входной последовательности, устанавливающий счетный триггер 1 в единицу. При этом на выходе блока 3 задержки формируется импульс (этот импульс является задержанным последним из предшествующих сбою импульсов входной последовательности), совпадающий во времени с импульсом на выходе блока 6 выделения первого импульса последовательности (он формируется по той причине, что блок 6 возвращен в исходное состояние выходным импульсом устройства) . Вследствие совпадения во времени этих импульсов на выходе элемента 4 ИЛИ формируется только один (соответствующий им импульс (фиг. 2д), уста.навливающий счетный триггер 2 также в единицу. Вследствие того, что сигналы на входах элемента 5 неравнозначности совпадают по знаку (две логические единицы) импульс на выходе устройства не формируется. В следующем промежутке времени на выходе блока 3 формируется импульс (этот импульс является задержанным (ложным) импульсом Екодной последовательности), который через элемент 4 ИЛИ производит внеочередное переключение счетного триггера 2 на фиг. 26 он переводится в ноль). Вследствие -возникшего не. совпадения по знаку(единица и ноль) сигналов на входа элемента 5 неравнозначности на-выходе ycrpolfcTBa формируется второй выходной импульс (фиг. 2 возвращающий счетные триггера 1 и 2 и блок 6 в исходное -состояние. Следующий импульс входной последовательности устанавливает счетный триггер 1 в единицу, а совпадающие во времени (сливающиеся в один) сигналы с выходов блока 6 и блока 3 задержки устанавливают счетный триггер 2 также в единицу, затем, счетные триггера 1 и 2 устр навливаются в ноль и т. д. Таким образом, в случае появления между импульсами входной последовательности ложного дополнительного (лишнего) и МП улье а на выходе устройств формируется два выходных импульса. Аналогичным образом если межру двумя истинныкт и myльcaми входной последовательности окажется (вклинится) два ложных импульса, то на выходе устройства сформируется три выходных импуль са, если три ложных импульса - то четыре выходных импульса и т.д. (нафиг. эти случаи не отресжены). Рассмотрим теперь случай (воздействие помех, отключение устройства и т. д.) отсутствия одного или нескольких импульсов во входной последовательности (сюда же относится и случай полного прекращения входной последователь ности импульсов). В этом случае процес одновременного переключения счетных триггеров 1 и 2 нарушается. Отсутстви импульса во входной последовательности приводит к тому, что в требуемый момент времени (в момент формирования на выходе блока 3 последнего из предществуюлййх сбою импульсов входной пос ледовательности, который переключает счетный триггер 2) переключение счет. ного триггера 1 не происходит (нафиг.2 он остается в единичном состоянии). Вследствие появления на входах элемента 5 неравнозначности сигналов разных знаков на выходе устройства формируется выходной импульс (фиг. 2 i ), возвра щающий счетные триггеры 1, 2 и блок 6 в исходное состоя1ше. При поступлени следутащего входного импульса счетный триггер 1 устанавливается им в единицу, а блок выделения первого импульса последовательности устанавливает в ..единицу счетный 2, затем счетные триггеры 1 и 2 устанавливаются в ноль и т.д. Таким образом, в случае отсутствия импульса во входной .последовательности или прекращения этой последовательности на выходе устройства формируе1ч;я один выходной импульс. Технико-экономический эффект устройства для контроля.последовательности импульсов заключается в повышении быстродействия и помохоустойчивости: и расширения функциональных возможностей устройства. Повьпиение быстродействия и помехоустойчивости обусловлено тем, что устройство сигнализирует о сбое во входной последовательности импульсов непосредственно в момент поступления ложного дополнительного (лишнего) импульса или в момент отсутствия импульса во входной последовательности; Яосле форг мирования сигнала о сбое во входной последовательности импульсов устройство вновь готово к работе, не требуя времени для вхождения в синхронизм. Расширение функциональных возможностей и области применения заключается в том, .что устройство распознает вид сбойной ситуации: в случае появления одного ложного входного импульса формируется два выходных импульса, в случае отсутствия одного или нескольких импульсов или прекращения входной последовательности формируется один выходной импульс; устройство распознает число ложных (лишних) импульсов поступивших в одном периоде следования истинных импульсов входной последовательности (в случае одного ложного входного импульса на выходе формируется два импульса, в случае двух ложных импульсов - три импульса, в случае трех ложных импульсов - четыре импульса и т.д); устройство не требует участия человека для возврата в исходное состояние после каждой сбойной ситуации; кроме того, устройство позволяет контролировать (из-за высокого быстродействия и отсутсивия участия человека) сбои в коротких последовательностях иьшульсов и оперативно реагировать на сбойные ситуации. Формула изобр-етения Устройство для контроля последовательности икшульсов, содержащее первый 710 счетный триггер, тактовый вход которопо является входом устройства, и элемент ИЛИ, выход которого соединен с тактовым входом второго счетчик% триггера, отлич ающееся тем, что, с целью повышения точности при одновременном сокращении времени контроля, введены блок задержки, элемент неравнозначности, фильтр и блок вьщеления первого импульса последовательности, при этом тактовый вход блока вьщеления первого импульса последрвательности объединен с входом блока задержки и с тактовым входом первого счетного триггера, выход которого соединен с первым входом элемента неравнозначности, вто9Sрой вход и выход которого соединены | соответственно с выходом второго счет ного триггера и с входом фильтра, выход которого является выходом устройства и соединен с входами сброса первого и второго счетных триггеров и блока выделения первого импульса последовательности, выход которого соединен с первым входом элемента ИЛИ, второй вход которого соединен с выходом блока задержки. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР №318171, кл Н 04 Ц 1/ОО, 1969. (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство тактовой синхронизации | 1982 |

|

SU1104674A1 |

| Устройство для цикловой синхронизации | 1981 |

|

SU1107317A1 |

| Устройство синхронизации | 1983 |

|

SU1095435A1 |

| @ -Разрядный счетчик в коде Грея | 1982 |

|

SU1070695A1 |

| Устройство цикловой синхронизации | 1981 |

|

SU987836A1 |

| Устройство для контроля импульсов синхронизации | 1982 |

|

SU1068943A2 |

| Счетный элемент с контролем | 1983 |

|

SU1129740A1 |

| Устройство для контроля серий импульсов | 1989 |

|

SU1676076A1 |

| Формирователь импульсов,сдвинутых во времени | 1978 |

|

SU781801A1 |

| Счетный элемент с контролем | 1986 |

|

SU1345340A1 |

HJ-M 4) Jfi4J4J

- I -

Cs Ча 4i C« « i

ni

Авторы

Даты

1983-02-28—Публикация

1981-12-29—Подача