объединен с выходом блока регенерации и с входом формирователя переднего фронта импульсов, выход которого подключен к соответствующему вход интегратора, а выход третьего элемента И подключен к сигнальному входу фазового дискриьшнатора, причем выходы управляемого делителя частоты и блока регенерации являются выходами устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство тактовой синхронизации | 1981 |

|

SU978378A1 |

| Устройство тактовой синхронизации | 1980 |

|

SU906016A1 |

| Устройство поэлементного фазирования | 1980 |

|

SU928665A1 |

| Устройство тактовой синхронизации | 1980 |

|

SU938419A1 |

| Устройство тактовой синхронизации | 1989 |

|

SU1720162A1 |

| Устройство тактовой синхронизации | 1981 |

|

SU970717A1 |

| Устройство для приема сигналов с относительной фазовой модуляцией | 1982 |

|

SU1083401A1 |

| Устройство синхронизации равнодоступной многоадресной системы радиосвязи | 1987 |

|

SU1478363A1 |

| Устройство для приема сигналов с относительной фазовой модуляцией | 1986 |

|

SU1356253A1 |

| Усредняющее устройство с блокировкой | 1981 |

|

SU978380A1 |

УСТРОЙСТВО ТАКТОВОЙ СИНХРОНИЗАЦИИ, содержащее последовательно сое;;иненные первый реверсивный счетчик, первый триггер, первый элемент И, блок, управления, управляемый делитель частоты, делитель частоты, первый элемент задержки, интегратор и первый дешифратор, выходы которого через управляемьй делитель частоты подключены к второму входу блока управления, последовательно соединенные второй реверсивный счетчик, второй дешифратор, коммутатор, к другимвходам которого подключенывыходы соответствующих разрядов первого реверсивного счетчика, второй триггер и второй элемент И, выход которого подключен к третьему входу блока управления, задающий генератор, выход которого подключен к тактовому входу управляемого делителя частоты, первьй выход которого подключен к тактовому входу фазового дискриминатора, второй выход - к первому входу третьего триггера, к второму входу которого подключены выходы первого и второго элементов И через элемент ИЛИ, а выход третьего триггера подключен к управляющим входам первого и второго элементов И, управлякмций выход интегратора подключен к входу сброса второго дешифратора и через второй элемент задержки - к входу сброса второго реверсивного счетчика, при этом первьй выход фазового дискриминаторе, подключен к объединенным первым входам первого и второго реверсивных счетчиков и к второму входу первого элемента И, а второй выход - к объединенным BTopuiM входам первого и второго реверсивных счетчиков и второго элемента И, другой выход коммутатора подключен к соответствующему входу первого триггера, а другой выхоп первого реверсивного счетчика § подключен к соответствующему входу второго триггера, выход делителя час(Л тоты подключен к входу сброса первого Дешифратора, а также третий элемент И и формирователь переднего фронта импульсов, отличаю.щ е е с я тем, что, с целью повышения точности синхронизации путем снижения влияния ложных корректирукадих импульсов, введены элемент неравнозначности, блок регенерации и дополнительные первый и второй элементы задержки, при этом к тактовому и стро35 .-бирующему входам блока регенерации подключены соответственно второй вы4 ход управляемого делителя частоты и выход задающего генератора, а сигнальный вход блока регенерации через первьй дополнительньй элемент задержки соединен с первым входом блока третьего элемента И, к второму входу которого подключен выход блока регенерации через элемент неравнозначности, к другому входу которого подключен выход второго дополнительного элемента задержки, вход которого

Изобретение относится к передаче дискретных сообщений и может быть использовано для обеспечения тактовой синхронизации приемной части ап паратуры. Известна устройство тактовой синхронизации, содержащее последователь но соединенные блок управления, первьй управлягмый делитель частоты и фазовый дискриминатор, выходы которого подключены к суммирующему и вычитающему входам первого реверсивного счетчика, а также згадающий генератор, интегратор и последовательно соединенные первый триггер и первый элемент И, при этом выход задающего генератора подключен к второму входу лервого управляемого делителя частоты, последовательно соединенные второй управляемый делитель частоты, первый элемент задержки, второй реверсивный счетчик, первый дешифратор и коммутатор, а также формирователь переднего фронта импульса, делитель частоты, второй элемент задержки, второй и третий дешифраторы и послед вательно соединенные второй триггер и второй элемент И, к второму входу которого, а также второму входу первого элемента И, вычитающему и рующеМу входам второго реверсивного счетчика подключены соответствующие выходы фазового дискриминатора, а выходы первого и второго элементов И подключены соответственно к суммирую щему и вычитающему входам блока упра ления, к тактовому входу которого подключен второй выход первого управ ляемого делителя частоты, к управляющим входам которого подключены выходы второго дешифратора, к входам которого и входам третьего дешифрато ра подключены выходы интегратора, к входу которого подключен выход формирователя переднего фронта импульса вход которого объединен с информационным входом фазового дискриминатора, а к сбросовому входу интегратора через второй элемент задержки и к управляющим входам второго и третьего дешифраторов непосредственно подключен выход делителя частоты, к счетному входу которого и счетному входу второго управляемого делителя частоты подключен первый выход первого управляемого делителя частоты, при этом выходы третьего дещифратора подключены к входам .установки начальных состояний второго управляемого делителя частоты, выход которого подключен к управляющему входу первого дешифратора, а выходы первого реверсивного счетчика подключены к установочным входам первого и второго триггеров, к сбросовым входам которых подключены выходы коммутатора, к вторым входам которого подключены вторые вькоды первого рев ерсивного счетчика Л . Недостатками устройства являются низкие помехоустойчивость и точность фазирования, а также сложная реализация . Наиболее близким техническим решением к предлагаемому является устройство тактовой синхронизации, содержащее последовательно соединенные первый реверсивный счетчик, первый триггер, первый элемент И, блок управления, управляемый делитель частоты, делитель частоты, первый элемент задержки, интегратор и первый дешифратор, выходы которого через управляемьй делитель частоты подключены к второму входу блока управления, последовательно соединенные второй реверсивньй счетчик, второй дешифратор, коммутатор, к другим входам которого подключены выходы соответствующих разрядов первого реверсивного счетчика, второй триггер и второй элемент И, выход которого подклю«ч к Г))(.;11. входу Олока ynpaijjieНИЧ, -ЛЛ.ЧК ГСНераТсчр, ОЫХ(Ч1, (зго 11одк:тк)чен к тактовому входу упрамляемогч делителя частоты, первьп вход KOTopoio подключен к тактовому входу фазового дискриминатора,второй выход - к первому входу третьего триггера, к второму входу которого подключены выходы первого и второго элементов И черезэлемент НЛП, а выход третьего триггера подключен к управляющим входам первого и второго элементов И, управляющий выход интегратора подключен к входу сброса второго дешифратора и через второй элемент задержки - к входу.сброса второго реверсивного счетчика, при этом первый выход фазового диcкpи oiнaтopa подключен к объединенным первым

входам первого и второго реверсивных счетчиков и к второму входу перзого элемента И, а второй выход - к объединенным вторым входам первого и .второго реверсивных счетчиков и второго элемента И, другой выход коммутатора подключен к соответствующему входу первого триггера, а другой выход первого реверсивного счетчика подключен к соответствующему входу второго три гера, выход делителя частоты подключен к входу сброса первого дешифратора, а также третий элемент И и формирователь переднего фронта импульсов, выход которого через третий элемент И подключен к объединенным входам интегратора и четвертого триггера, к другому входу которого подключен выход делителя частоты, а выход четвертого триггера подключен к другому входу третьего элемента И, а вход формирователя переднего фронта импульсов объединен с соответствующи входом фазового дискриминатора 21.

Недостатком известного устройства тактовой синхронизации яапяется низкая точность синхронизации из-за али НИН ложных корректирующих импульсов.

Цель изобретения - повышение точности cинxpo rизaции путем снижения влияния ложных корректирующихимпульсов.

Для достижения поставленной цели в устройство тактовой синхронизации, содержащее последовательно соединенные первый реверсивный счетчик, первый триггер, первый элемент И, блок управления, управляемый делитель частоты, делитель частоты, первьп элемент задержки, интегратор и первый

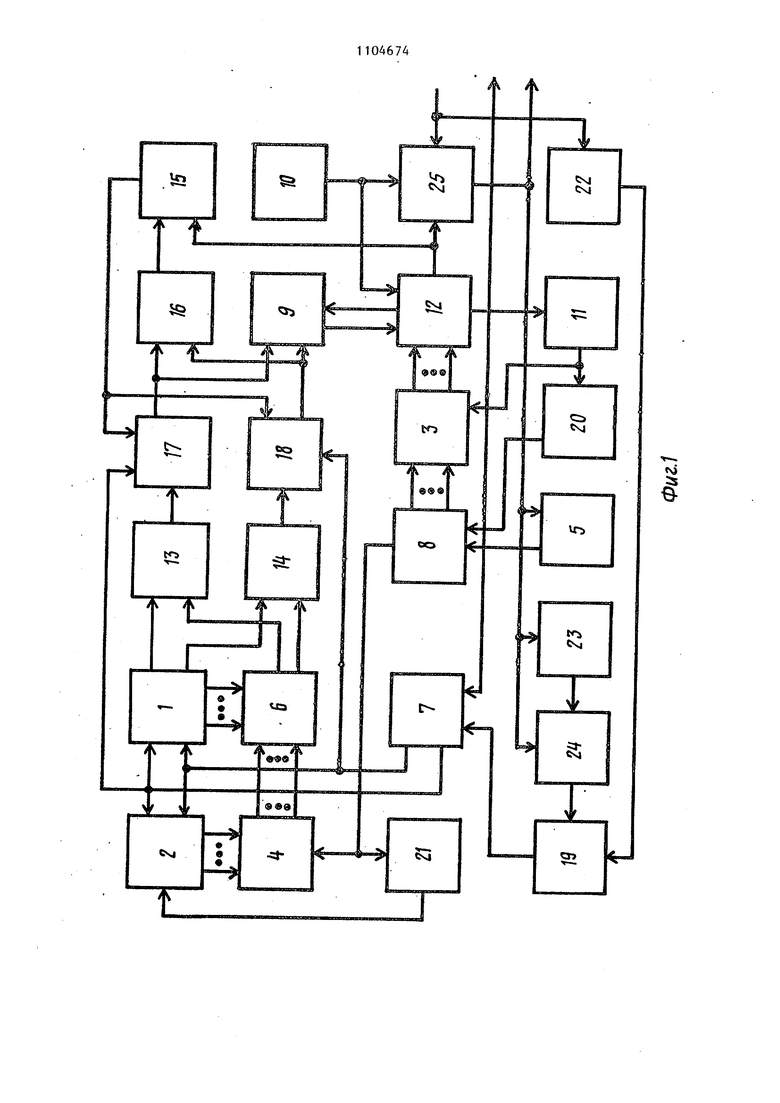

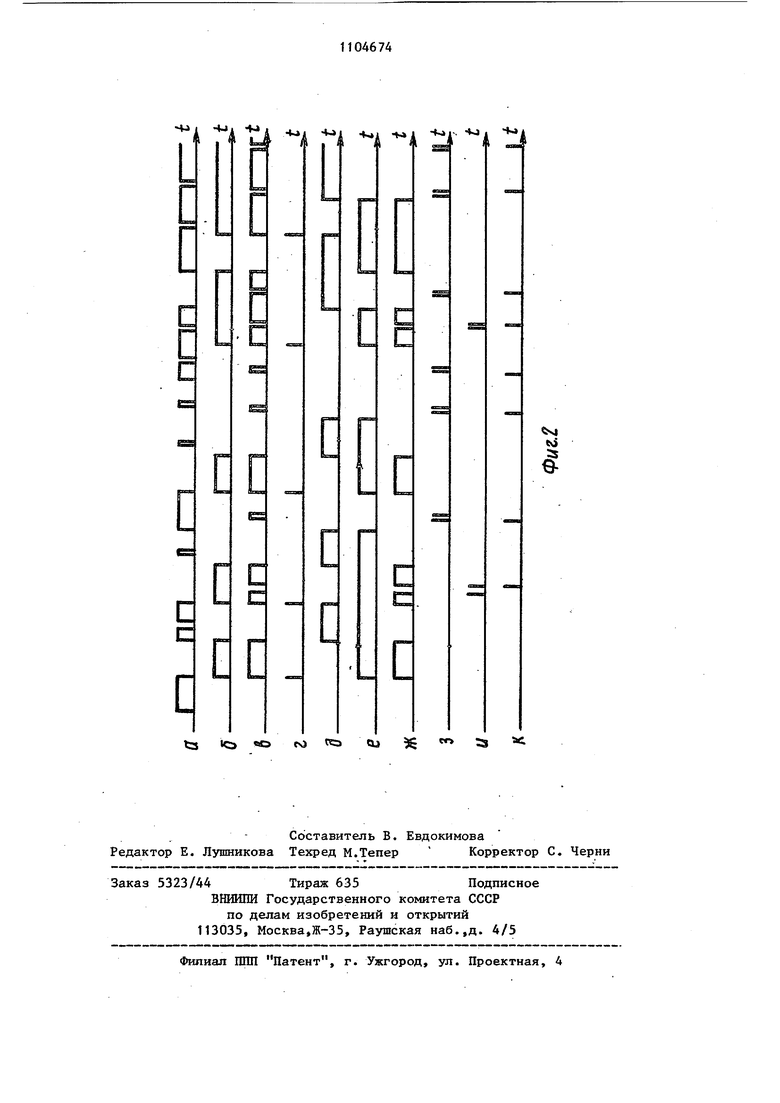

дешифратор, выходы которого через управляемый делите чь частоты подключе)1ы к второму входу блока управления, последовательно соединенные второй реверсивный счетчик, второй дешифратор, коммутатор, к другим входам которого подключены выходы соответствующих разрядов первого реверсивного счетч 1ка, второй триггер и второй элемент И, выход которого подключен к третьему входу блока управления, задающий генератор, выход которого подключен к тактовому входу управляемого делителя частоты первый выход которого подключе к тактовому входу фазового дискриминатора, второй выход - к первому входу третьего триггера, к второму вход которого подключены выходы первого и второго элементов И через элемент ИЛИ, а выход третьего триггера подключен к управляющим входам первого и второго элементов И, управляющий выход интегратора подключен к входу сброса второго дещифратора и через второй э.пемент задержки - к входу сброса второго реверсивного счетчика при этом nepBbtfi выход фазового дис криминатора подключен к объединенным первым входам первого и второго реверсивных счетчиков и к второму входу первого элемента Н, а второй выход - к объединеннымвторым входам первого и второго реверсивных счетчиков и второго элемента И, другой выход коммутатора подключен к соответствующему входу первого триггера, а другой выход первого реверсивного счетчика подключен к соответствующему входу второго триггера, выход делителя частоты подключен к входу сброса пер.вого дешифратора, а также третий элемент И и формирователь переднего фронта импульсов, введены элемент неравнозначности, бЛок регенерации и дополнительные первый и второй элементы задержки, при этом к тактовому и стробирующему входам блока регенерации подключены соответственно второй выход управляемого делителя частоты и выход задающего генератора, а сигнальный вход блока регенерации через первьй дополнительньгй элемент задержки соединен с первым входом блока третьего элемента И к второму входу которого подключен выход блока регенерации через элемен неравнозначности, к другому входу которого подключен выход второго дополнительного элемента задержки, вхо которого объединен с выходом блока регенерации и с входом формирователя переднего фронта импульсов, выход которого подключен к соответствующему входу интгератора, а выход третье го элемента И подключен к сигнальном входу фазорого дискриминатора, приче выходы управляемого делителя частоты и блока регенерации являются выходами устройства. На фиг. 1 представлена структурна электрическая схема устройства тактовой синхронизации; .на фиг. 2 временные диаграммы, поясняющие его работу. Устройство тактовой синхронизации содержит первый и второй реверсивные счетчик. 1 и 2, первый и второй дешифраторы 3 и 4, формирователь 5 переднего фронта импульсов, коммутатор 6, фазовый дискриминатор 7, интегратор 8, блок 9 управления, задаю щий генератор 10, делитель 11 частоты, управляемый делитель 12 частоты, первый, второй и третий триггеры ISIS, элемент ИЛИ 16, первый, второй и третий элементы И 17-29, первый и второй элементы 20 и 21 задержки, первый и второй дополнительные элементы 22 и 23 задержки, элемент 24 н равнозначности и блок 25 регенерации Устройство тактовой синхронизации работает следующим образом. Последовательность импульсов высокой частоты с выхода задающего генератора 10 поступает на тактовый вход управляемого делителя 12, вслед ствие чего на его первом и втором выходах формируются тактовые импульсы (на первом выходе - тактовый миандр, на втором - узкие импульсы), следующие -с частотой, близкой к скорости дискретной модуляции (скорости телеграфирования) принимаемых элементов сообщения, (фиг. 2а), поступающих на сигнальньй вход блока 25 регенерации и вход первого дополнительного элемента 22 задержки. Блок 25 регене рации осуществляет интеграцию принимаемых элементов сообщения, вследствие чего на его выходе формируется регенерированная (т.е. восстановленная, или другими словами, очищенная от помех) последовательность входных импульсов (фиг. 26), отстоящая во времени от поступающих из канала связи элементов сообщения на длительность одного элемента сообщения. На выходе первого дополнительного элемента 22 задержки (фиг. 2в) с задержкой во времени, равной длительности одного элемента сообщения, формируются принимаемые (не восстановленные от помех) из канала связи элементы сообщения . Регенерированная последовательность входных импульсов с выхода блока 25 регенерации поступает на вход формирователя 5 переднего фронта импульса, на второй вход элемента 24 .неравнозначности и на вход второго дополнительного элемента 23 задержки. С выхода второго дополнительного элемента 23 задержки регенерированная последовательность входных импульсов (фиг. 2д), задержанная на время, равное длительности одного элемента сообщения, поступает на первый вход элемента 24 неравнозначности. Так как единичный уровень напряжения на выходе элемента 24 неравнозначности может быть сформирован только в случае поступления на его входы разных логических сигналов (ноль и единица или единица и ноль), а второй дополнительный элемент 23 задержки осуществляет задержку регенерированной входной последовательности на длительность одного элемента сообщения, то на вы-ходе элемента 24 неравнозначности (фиг. 2е) единичные сигналы формируются только в случае смены логического уровня (ноль и единица) регенерированной последовательности входных импульсов. Другими словами, нулевой уровень напряжения на выходе элемента 24 неравнозначности формируется и только в случае появления во входной последовательности двойных,тройных и т.д.. посылок одного знака (неодиночных нулевых или единичных элементов сообщения), причем нулевой уровень напряжения соответствует во времени определенной части группы регенерированных посьшок одного знака (второй половине для двойной посьшки, второй и третьей частям для тройной посьшки и т.д.). Уровни напряжения с выхода элемента 24 неравнозначности (фиг.2е) поступают на второй вход третьего элемента И 19, на первьй вход которого поступает задержанная на длительность одного элемента сообщения входная (т.е. не восстановленная от помех) последовательность принимаемых элементов сообщения (фиг. 2в).Вследствие этого на второй вход фазового дискриминатора 7 поступают только элементарные посыпки сообщения и пер вые части двойных, тройных и т.д. по сыпок (фиг. 2ж). По этой причине искажение помехами в канале связи остальных частей (кроме первых) двойных, тройных и т.д. посылок не влияе на работу фазового дискриминатора 7. Фазовый дискриминатор 7 осуществляет сравнение фазы прошедших через трети элемент И 19 принимаемых элементов сообщения (по существу их фронтов) с фазой выходных тактовых импульсов устройства и при их несовпадении (отс тавание или опережение) на одном из его выходов формируется соответствую щий корректирующий импульс добавлени или вычитания (по одному корректирующему импульсу на каждьй из фронтов входного сигнала-), поступающий на соответствующие входы (первые или вторые), или другими словами, суммирующие или вычитающие первого и второго реверсивных счетчиков 1 и 2. Первый реверсивный счетчик 1, осу ществляя частичную защиту от ложной подстройки частоты при случайных искажениях принимаемых элементов сообщения (одиночных посыпок или первых частей неоднократно повторяющихся посыпок одного знака), производит усреднение входных величин. Если число импульсов, поступающих на один из входов (например, первый, т.е. суммирующий) первого реверсивного счетчика 1, превысит число импульсов поступивших на его другой вход (второй, т.е. вычитающий), на величину, равную коэффициенту пересчета первого реверсивного счетчика 1 , на одном из выходов его последних разрядов (в данном случае на первом выходе, т.е. на выходе последнего разряда добавления) формируется импульс, устанавливающий соответствующий первый триггер 13 в единичное состояние, подготавливающий к работе первый элемент И (в данном случае первый элемент И 17) по второму входу.Сброс первого триггера 13 в нулевое состояние для защиты от случайных искажеНИИ, принимаемых элементов сообщения производится через коммутатор 6 сиг.налом с выхода промежуточного разряд вычитания первого реверсивного счетчика 1, т.е. частично усредненным сигналом. Аналогичным образом, установка в единичное состояние второго триггера производится максимально усредненным сигналом с второго выхода (выхода последнего разряда вычитания) первого реверсивного счетчика 1, а его сброс в нулевое состояние частично усредненным сигналом с второго выхода коммутатора 6 (т.е. сигналом с выхода промежуточного разряда добавления первого реверсивного счетчика 1). Для обеспечения быстродействия и точности фазирования в ycлoви x сильных помех коэффициент частичного усреднения сбросовых сигналов является переменным, т.е. коммутатор 6 осуществляет коммутацию сбросных входов первого и второго триггеров 13 и 14 с выходами определенных разрядов вычитания и добавления первого реверсивного счетчика 1 в зависимости от того, на каком из вторых, входов коммутатора 6 сформирован уровень напряжения логической единицы (т.е. в зависимости от кода числа на выходах второго дешифратора 4). Сигнал на определенном выходе второго дешифратора 4 формируется в зависимости от кода числа, записанного во второй реверсивньй счетчик 2, т.е. в зависимости от соотношения числа импульсов добавления и вычитания (другими словами от режима работы устройства: устойчивая синхронизация, режим вхождения в синхронизм, устойчивое Рассогласование частот задающих генерато.ров приемной и передающей частей системы передачи и т.д.), поступивших с выходов фазового дискриминатора 7 за промежуток времени между двумя импульсами на первом выходе (выходе промежуточного разряда) интегратора 8, что позволяет учесть структуру принимаемых сообщений и обеспечить высокую точность и быстродействие устройства. Следует заметить, что интегратор 8 (по второму входу) заряжается (фиг. 2г) передними фронтами (с выхода формирователя 5 переднего фронта импульса) регенерированной последовательности принимаемых элементов сообщения (фиг42б) т.е. дробления принимаемых элементов сообщения (фиг. 2а) не оказывают влияния на работу интегратора 8. Ввод информации в второй дешифратор 4 производится сигналом с первого выхода интегратора 8. Этот же сигнал, задержанный во втором элементе 21 задержки (на время, достаточное для 91 ввода информации в второй дешифратор 4), осуществляет сброс второго ревер сивного счетчика 2 (по третьему входу) в нулевое состояние. Емкость второго реверсивного счетчика 2 выбирается достаточной для того, что бы за время между двумя сбросовыми импульсами не произошло его переполнение. Импульсы, следующие с частотой телеграфирования с второго выхода управляемого делителя 12 частоты, периодически устанавливают третий триггер 15 в единичное состояние, единичный уровень напряжения с выход которого подготавливает к работе по третьим входам первого и второго элементов И 17 и 18. Как следует из приведенного выше процесса управления первого и второго триггерами 13 и 14, они могут одновременно находиться в состоянии логического нуля, в единичном же состоянии может находиться только один из этих триггеров (первый триггер 13 или второй триггер 14). В случае, если первый 13 и третий триг геры 15 оба находятся в единичном состоянии, то первый же корректирующий импульс добавления (сформированный на первом выходе фазового дискри минатора 7) без усреднения проходит через первый элемент И 17 на первый (т.е. суммирующий) вход блока 9 упра ления. Одновременно с этим импульс с выхода первого элемента И 17 через элемент ИЛИ 16 поступает на сбросовый вход третьего триггера 15, переводя его в нулевое состояние и запрещая (по третьему входу) прохождение импульсов через первый элемент И. Вследствие того, что утановка в единичное состояние третьего триггера 1 5 производится с частотой телеграфирования, за время, равное длительности одного элемента сообщения на вход блока 9 управления не может пройти более одного корректирующего импульса (истинного, обусловленного фронтом принимаемого сообщения, или ложного, обусловленного, например, дробления), что повышает помехоустойчивость устройства и точность фазирования (так как истинные коррек тирующие импульсы формируются только по фронтам принимаемого элемента ссо щения). Аналогичным образом третий триггер 15, управляя вторым элементом И 18, уменьшает число ложных кор ректирующих импульсов вычитания,проходящих на второй, (т.е. исключакмпий) вход блока 9 управления.. Таким образом, сигналы с выходов первого и второго элементоа И 17 и 18 поступают на суммирующий и исключаюпщй входы блока 9 управления. Вследствие этого изменяется количество импульсов высокой частоты (поступающих с выхода задающего генератора 10), подвергаемых делению в управляемом делителе 12 частоты,т .е.. осуществляется подстройка частоты и фазы следования тактовых импульсов на выходе устройства (первом выходе управляемого делителя 12 частоты). Шаг подстройки (т.е. дискретизация подстройки) частоты и фазы выходных тактовых импульсов, т.е. величина смещения тактового импульса на выходе устройства от его основного положения, приходящаяся на один добавленный или исключающий импульс, подвергаемый делению в управляемом делителе 12 частоты, устанавливается в зависимости от того, на каком из выходов первого дешифратора 3 имеется уровень напряжения логической единицы. Уровень напряжения логической . единиць на определенном выходе первого дешифратора 3 устанавливается в зависимости от показаний интегратора 8. Ввод показаний интегратора 8 в первый дешифратор 3 производится через промежуток времени, равный периоду следования импульсов на выходе делителя 11 и определяющий число элементов принимаемого сообщения, анализ .которого характеризует среднюю частоту чередования единичных и нулевых посылок и их групп в принимаемом сообщении, т.е. их статистическую характеристику (структуру принимаемых сообЕмкость интегратора 8 выбирается достаточной для того, чтобы за время между дв5Т сбросовыми импульсами, поступающими с выхода делителя 11 частоты через второй дополнительный элемент 21 задержки не произошло его переполнение.Заряд интегратора 8 осуществляется передними фронтами (фиг. 2г) принимаемых jneMeHTOB сообщения, которые з реляст ормирователь 5 переднего фронта импульса из регенерированной блоком 25 регенерации (фиг. 2б) последовательность входньгх импульсов устройства (фиг. 2а), что обеспечивает высокую остоверность выделенных фронтов. Чем чаще чередуются единичные и нулевые элементы или их группы в составе принимаемых сообщений (т.е. чем чаще фазовый дискриминатор осуществляет сравнение фазы входных и тактовых импульсов и формирует соответствующие знаку рассогласования корректирующие импульсы), тем вьше показания интегратора 8 и тем меньще шаг подстройки частоты управляемого делителя 12 частоты, устанавливаемый первым дешифратором 3 (путем включения блока 9 управления между соответствующими разрядами управляемого делителя 12 частоты). Аналогичным образом, чем чаще чередуются единичные и нулевые элементы сообщения на входе устройства тем меньше период следования сигналов на первом выходе интегратора 8, т.е. тем меньше промежуток времени, в течение которого реверсивным счетчиком 2 определяется соотношение числа импульсов добавления и вьмитания, формируемых фазовым дискриминатором 7 (т.е. тем меньше время анализа режима работы предлагаемого устройства). Осуществление заряда интегратора 8 импульсами, формируемыми из фронтов регенерирования (очищенных от помех) блоком 25 регенерации элементов принимаемых сообщений, позволяет полностью исключить его заряд ложным импульсами, обусловленными дробления ми элементов сообщения (сравнение фиг. 2г и фиг. 2л). Вследствие этого уровень помех в канале связи не оказывает влияния на точность установления шага дискретизации подстройки частоты, а также на точность установ ления промежутков времени анализа ре жима работы устройства (так как сред няя частота чередования нулевых и 1 412 единичных элементов сообщения и их групп определяется верно),что недостижимо в известном устройстве. Осуществление запрета прохождения на вход фазового дискриминатора 7 последующих (кроме первой) частей (элементов) двойных, тройных и т.д. посылок позволяет исключить формирование на выходах фазового дискриминатора основной части ложных корректирующих импульсов (сравнение фиг.2к и фиг. 2и), следствием чего является повьппение точности синхронизации (элемент ИЛИ и третий триггер ограничивают как в известном устройстве число ложных импульсов, прошедших на выход фазового дискриминатора 7, из-за поражения помехами одиночных элементов сообщения и первых элементов двойных, тройных и т.д. посылок). Так как вероятность появления двойных, тройных и т.п. посылок в сообщении приблизительно равна 0,5, то только данный фактор обеспечивает повышение точности синхро 1изации в условиях помех в сравнении с известным почти в два раза. С учетом же имеющейся защиты интегратора от воздействия помех достигаемый выигрыш точности синхронизации в условиях помех в сравнении с известным будет значительно вьше. Кроме того, осуществление защиты от помех интегратора приводит к умень шению емкости интегратора и реверсивных счетчиков, а значит и к упрощению дешифраторов -Кроме того, уменьшение их емкости, а значит и инерционности, позволяет более оперативно реагировать на изменение фазы входных импульсов и режима работы устройства, т.е. повысить быстродействие синхронизации, а значит, и точность синхронизации.

«

44

-ц

II

а

с

с

t3 (О юРсэйл « i

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство тактовой синхронизации | 1980 |

|

SU906016A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство тактовой синхронизации | 1981 |

|

SU978378A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1984-07-23—Публикация

1982-02-16—Подача