Изобретение относится к вычислительной технике и предназначено для использования в быстродействуюйдах специализированных ЦВМ для вычисления функций синуса и косинуса.

Известно устройство для вычисления функций вида содержащее регистр аргумента,- блок модификации аргумента, два сумматора, ключ, два блока памяти, мультиплексор, блок умножителей, два регистра, доинфратсф нуля и блок управления. Для получения одного результата в данном устройстве необходимо выполнить три времяемких операции умножения и три операции сложения ij.

Недостатком этого устройства является низкое быстродействие.

Наиболееблизким по технической сущности к изобретению является тригонометрический вычислитель, содержащий три сумматора, два блока сдвига, четыре регистра, блок постоянной памяти для хранения коэффициентов, блок управлении. На вычисление тригонометрической функции в данном устройстве от п-разрядного аргумента требуется затратить п тактов, причем в каждом такте необходимо выполнить операцию выборки константы из блока ,

постоянной памяти, операцию сдвига промежуточного результата в блоке сдвига, операцию суммирования, нет:-. сколько операций записи в регистры, операцию анализа знаков промежуточных результатов.

Быстродействие данного устройства;;

10

Т. «2,5 nt (см) ,

где t -- время суммирования двух чисел на сумматоре Г21. ; Недостатками известного устройст15ва являются низкое быстродействие и большие объемы дорогостоягдах ПЗУ для хранения констант и микропрограмм блока микропрогратимного управления.

20

Целью изобретения является повышение быстродействия устройства.

Поставленная цель достигается тем, что в конвейерное устройстве для вычисления функций синуса и ко25синуса, содержащее входной регистр, два промежуточных регистра, входной сумматор, два выходных сумматора и блок управления, причем прявюй выход входного регистра соединен с

30 1 первым входом входного руммато а.

прямые выходы первого и второго промежуточных регистров соединены с первыми входами соответствующих выходных суммато ров, дополнительно введены два входных коммутатора, два выходных коммутатора, два выходных регистра, триггер и (п-2) блоков .вычисления итерации {где п - разрядность аргумента), причем первый и второй входы блока управления являются входом задания размерности маесива и входом пуска соответственно, выход блока управления соединен с синхровходами входного регистра, промежуточных регистров, триггера, выходных регистров и блоков вычисления итерации, выход старшего разряда входного регистра соединен с управляющими входами первого и второго входных коммутаторов, выходы которых соединены соответственно с первым информационным входом блока вычиления итерации и вторым входом входного сумматора,первый и второй информационные входы первого входного коммутатора соединены с входами соответст-венно прямого и обратного кодов на чальных условий вычисления косинуса устройства, первый и второйинформационные входы второго входного коммутатора соединены, с входами соответственно qpHMoro иобратного кодов константы 0,25 устройства, вхо прямого кода начальных условий вычисления косинуса которого соединен со вторым информационным входом бло- ка вычисления итерации, третий информационный вход которого соединен с выходом входного сумматора, выходы с первого по третий -го блока вычисления итерации (,2,...,n-3) соединены соответственно с первого по третий информационными входами (i+1)-ro блока вычисления итерации, выходы с первого по третий (п-2)-го блока вычисления итераций соединены с информационными входами соответственно первого и второго промежуточных регистров и триггера, выход которого соединен с управляющими входами выходных коммутаторов, первые и вторые информационные входы которых соединены с прямыми и инверсными выходами соответствующих промежуточных регистров, выходы первого и второго выходных.коммутаторов соединены со вторыми входами .соответ ственно второго и первого выходных сумматоров, выходы которых соединены с информационными входами соответст-v вующих выходньгх регистров, при этом блок вычисления итерации (1«1,2,... п-2) содержит три регистра, три «ом мутатора и три сумматора, причем синхровход блока соединен с синхровходами первого, второго и третьего ре гистров информационнее входы которых соединены с соответствующими информационными входами блока, выход старшего разряда третьего регистра соединен с управляющими входами первого, второго и третьего коммутаторов, прямые выходы первого и второго регистров соединены с первыми информационными входами соответствующих коммутаторов и первыми. входами соответствующих сумматоров, инверсные выходы первого и второго регистров соединены со вторыми информационными входами соответствующих коммутаторов, выходы перврго и второго коммутаторов соединены со вторыми входами соответственно второго и первого сумматоров, первый и второй информационные входы третьего коммутатора соединены с входами соответственно прямого, и обратного кода константы arctg2 % выход третьего коммутатора и прямой выход третьего регистра соединены соответственно с первым и вторым входами третьего сумматора, выходы первого, второго и третьего сумматоров соединены с соответствуквдими выходами блока, причем блок управления содержит генератор импульсов, триггер, элемент И, элемент ИЛИ-НЕ и счетчик установочный вход которого соединен ,с первым входом блока, второй вход которого соединен с первым входом триггера, второй вход которого через элемент ИЛИ-НЕ соединен с выходом счетчика, счетный вход которого соединен с выходом элемента И и выходом блока управления, выходы триггера и генератора импульсов соединены со входами элемента И,

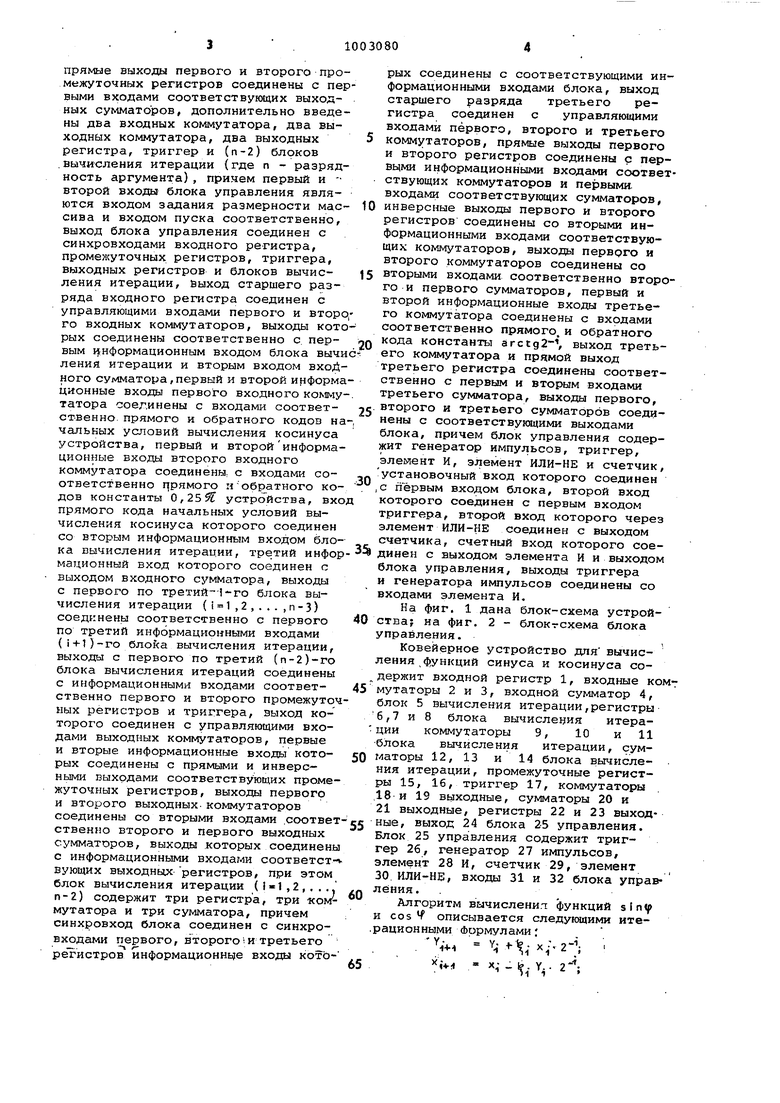

На фиг. 1 дана блок-схема устройства; на фиг. 2 - блоктсхема блока управления.

Ковейерное устройство для вычисления функций синуса и косинуса со,держит входной регистр 1, входные комутаторы 2 и 3, входной сумматор 4, блок 5 вычисления итерации,регистры 6,7 и 8 блока вычисления итера:ции коммутаторы 9, 10 и 11 блока вычисления итерации, сумматоры 12, 13 и 14 блока вычисления итерации, промежуточные регистры 15, 16, триггер 17, коммутаторы ,18 и 19 выходные, сумматоры 20 и 21 выходные, регистры 22 и 23 выходные, выход 24 блока 25 управления. Блок 25 управления содержит триггер 26, генератор 27 импульсов, элемент 28 И, счетчик 29, элемент 30. ИЛИ-НЕ, входы 31 и 32 блока управления.

Алгоритм вычисления функций и cos Ч описывается следующими ите.рационными Формулами Y:

Х,ч-. .Y.. г-

, х,Ч1 arctg2-; t ; которые при начальных значениях .. e 1/-i oTTTrUfo f дают после n итераций Xj, и с точностью , I Устройство работает следующим образом. По входу 31 в счетчик 29 блока 25 управления загружается число, равное -длине обр: батываемого массива. По сигналу Пуск,поступающему по ВХОДУ 32, триггер 26 устанавливается в состояние 1 и сигнал с его выхода пропускает на выход элемента И 28 импульсы, вырабатываемые генератором 27 импульсов, которые по выходу 24 поступают на регистры устройства. Регистры устройства построены на D-триггерах, поэтому запись инфо мации в регистры производится по переднему фронту импульса записи. По первому импульсу во входной регистр 1 записывается значение операнда if , представленное в обрат ном коде в форме с фиксированной за пятой . .Сигнал с выхода старшего разряда регистра 1, определяющий знак управляет прохождением информации через коммутаторы 2 и 3. Бели знак V положительный, то через коммутатор 2 пропускается значение х, сфо мированное на входе монтажным способом, а через коммутатор 3 значени ПХ4, представленное в обратном коде и также сформированное монтажным способом. Если знак V отрицательный то черюз коммутаторы 2, 3 проходят xj, и Л:/4, сформированное на их входах монтажным способом. На сумматоре 4 формируется значение V С приходом из блока управления второго импульса в регистр 6 первог блока 5 вычисления итерации записывается значение с выхода коммутатор 2, в регистр 7-значение х, а в регистр 8 - значение с выхода суммато ра 4. Одновременно в регистр 1 пост пает следующий операнд массива. Над вторым операндом производятс операции, аналогичные выполняемым в первом такте над первым операндом, т.е. над вторым операндом выполняет ся первая итерация. Над первым операндом в первом блоке 5 вычисления итерации выполняется вторая итераци В зависимости от знака V, , записанного в регистре 8, через коммутато|ры 9, 10 и 11 проходят соответствую щие прямые или обратные значения ре гистров 6 и 7г а также значения arct 2 в прямом или обратном коде. На сумматора 12 формируется зна чение Y, на сумматоре 13 - Xj, на сумматоре 14 Сдвиг значений х и Y,, на один разряд вправо, т.е. их умножение на 2 , осуществляется путем соединения выходов регистров 6 и 7 с соответствующими входами коммутаторов 9 и 10 со сдвигомна радряд вправо, т.е. k-й разряд регистра соединяется с (К+1)-м разрядом комму татора. С приходом третьего импульса ре-зультаты вычислений, полученные в .первом блоке 5 вычисления итерации, записываются в регистры второго вычислительного блока 5, вычисления итерации, а в первый бло.; 5 записываются результаты из первой ступени конвейера. Во входной регистр 1 поступает значение третьего операнда обрабатываемого массива. В первой ступени выполняется первая итерация над третьим операндом, во второй вторая итерация над вторым операндом, в третьей - третья итерация над первым операндом. В дальнейшем, с приходом каждого импульса, результаты предыдущих блоков 5 вычисления итерации поступают в последующие блоки, а во входной регистр поступает новый операнд и т.д., причем в К1ЖДОМ следующем блоке значения из регистров б и 7 пос .тупают на коммутаторы 9 и 10 со (СДВИГОМ на один разряд вправо большим, чем в предыдущем блоке, а в выражениях арктангенсов, которые формируются монтажным способом на входах коммутаторов 11, степень двойки возрастает на единицу. С приходом п-го импульса в регистры 15 и 16 записываются значения из сумматоров 12 и 13 (п+2)-го блока, а в триггер 17 поступает значение знакового разряда сумматора 14. По сигналам с выходов этого триггера из регистров 15 и 16 через коммутаторы 18 и 19 на сумматоры 20 и 21 поступают значения и Хц / сдвинутые на (п-1)-разрядов вправо. На сумматооах 20 и 21 формируются первые результаты Yy, и х, которые по приходу (п+1)-го импульса записываются в выходные регистры ; 22, 23 и из них поступают на выход устройства. В дальнейшем, с приходом каждого нового импульса,.на выходе появляется новый результат. Вместе с поступлением на регистры стройства тактовые импульсы из элемента И 28 поступают на счетчик 29, и с поступлением каждого импульса из содержимого счетчика вычитается единица. Как только содержимое счетчика станет равным нулю, что указывает на окончание обработки всего массива чисел, элементсэм ИЛИ-НЕ 30 вырабатывается сигнал, который поступает. на триггер 26 исбрасывает его в О Сигнал с выхода этого триггера зап.рещает прохождение тактовых иг/шуль/ сов УЗ генератора 27 через элемент И 28. на ре1:истры устройства и работа прекращается. Предлагаемое устройство работает по конвейерному принципу, поэтому в каждом такте в него можно вводить новый операнд, а на выходе получать новый результат вычисления. При обработке массивов чисел быстродействие устройства определяется дпитель ностью такта обработки данных которое равно задержке в одной ступени конвейера устройства и определяется выражением v.- ч/о t - время суммирования на сум маторе; t. - задержка информации комму татором. Видно, что по быстродействию пре лагаемое устройство значительнЬ пре восходит известное. В предлагаемом устройстве при обработке массивов чисел быстродействие повышено в { .s2,5 п раз См KW Кроме того, в предлагаемом устройстве нет необходимости хранить в ПЗУ константы, количество которых равно 2п, поскольку они подаются монтажным способом, а также не нужно ПЗУ для хранения микропрограгФ сложного блока микропрограммного управления, так как управление устройством осуществляется от простого яблока управления. «формула изобретения 1. Конвейерное устройствр для вычисления функций синуса и косинуса, содержащее входнойрегистр, два про межуточных регистра, входной сумматор, два выходных сумматора и блок управления, прг1чем прямой выход входного регистра соединен с первым .входом входного сумматора, прямые выходы первого и второго .пpoмeжy гoч ных регистров, соединены с первыми входами соответствующих выходных сумматоров, о т лги чающееся тем, что, с целью повышения быстродействия устройства при вычислении функций для массива чисел, в него введены два входных коммутатора, два выходных коммутатора, два выход ных регистра,: триггер И (п-2) блоков вычисления итерации (где п - разряд ность аргумента), причем первый и второй входы блока управления являются аходом задания размерности мас сива и. входо пуска соответственно, выход блока управления соединен с ;синхровходами входного регистра. промежуточных регистров, триггера, выходных регистров и блоков вычисле ния итерации, выход старшего разряда входного регистра соединен с уп-: равляющими входами и второго входных коммутаторов, выходы ко|Торых соединены соответственно .с ;первым информационным входом блока вычисления итерации и вторым входом входного сумматора, первый и второй информационные входы первого входного коммутатора соединены с .входами соответственно прямого и обратного кодов начальных условий вычислений косинуса у.стройства, первый и второй информационные входы второго входного коммутатора соединены с входами соответственно прямого и обратного кодов константы 0,25У2Г устройства, вход прямого кода начальных условий вычисления косинуса которого соединен с вторым информационным входом блока вычисления итерации, третий информационный вход которого соединен с выходом входного сумматора, выходы с первого по третий i го блока вычисления итерации (i 1 , 2,. ..., п-3) соединены соответственно с первого по третий информационными входами {И-1)-го блока вычисления итерации, выходы с первого по треТий (п-2)-го блока вычисления итераций соединены с информационными входами соответственно первого и второго промежуточных регистров и триггера, выход которого соединен с управляющими входами выходных коммутаторов, первые и вторые информационные входы которых соединены с прямыми и инверсными выходами соответствующих промежуточных регистров выходы первого и второго выходных коммутаторов соединены с вторыми входами .соответственно второго и первого выходных сумматоров, выходы которых соединены с информационными входами соответствующих выходных регистров. 2. Устройство поп.1,-отлич ающе е:ся тем, что -й блок вычисления итерации (1 1, 2, .. . п-2) содержит три регистра, три коммутатора и три сумматора, причем синхровход блока соединен с синхровходами первого, второго и третьего регистров, информационные входы которых соединены с соответствующими информационными входами блока, выход старшего разряда третьего регистра соединен с управляющими входами первого, второго и третьего коммутаторов, прямые выходы первого и второго регистров соединены с первыми информационньями входами соответст.вующих коммутаторов и первыми входами соответствующих суммаjropoB, инверсные выходы первого и

второго регистров соединены с вторы,ми информационными входами соответствующих коммутаторов, выходал первого и второго коммутаторов соединены с вторыми входами соответственно вто- рого и первого сумматоров, первый и второй информационные входы третьего коммутатора соединены с ьходами соответственно прямого, и обратного кода константы arctg2 , выход третьего коммутатора и.прямой выход третьего регистра соединены соответственно с первым и вторым входами третьего сумматора, выходы первого, второго и третьего сумматоров соединены с соответствующими выходами блока.

3. Устройство по п.1,отличаю щееся тем, что блок управления содержит генератор импульсов,

WJf

триггер, элемент И, элемент ИЛИ-НЁ и счетчик, установочный вход которого соединен с первым входом блока, втсРрой вход которого соединен с первым входом триггера, второй вход которого через элемент ИЛИ-НЕ соединен с выходом счетчика, счетный вход которого соединен с выходом элемента И и выходом блока управления, выходы триггера и генератора импульсов соединены с входами элемента И.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 760111, кл. G 06 F 15/31, 1978.

2.Оранский А..М, Аппаратные методы в цифровой вычислительной технике. Минск, BIV, 1977, с. 132,

рис. 5.20 Опрототип ).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для реализации быстрого преобразования Фурье | 1984 |

|

SU1233166A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1983 |

|

SU1115060A1 |

| Конвейерное устройство для вычисления функции Y=е @ | 1981 |

|

SU962927A1 |

| Многоканальное устройство для быстрого преобразования Фурье с конвейерной обработкой операндов | 1984 |

|

SU1211752A1 |

| Конвейерное устройство для вычисления функции @ = @ | 1981 |

|

SU964635A1 |

| Устройство для реализации двухмерного быстрого преобразования Фурье | 1982 |

|

SU1164730A1 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU1130861A1 |

| Конвейерное устройство для вычисления логарифмической и экспоненциальной функций | 1982 |

|

SU1027722A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ БЫСТРЫХ ГЕОМЕТРИЧЕСКИХ ПРЕОБРАЗОВАНИЙ | 1991 |

|

RU2020557C1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

Авторы

Даты

1983-03-07—Публикация

1981-10-09—Подача