элемента ИСКЛЮЧАННЦЕЕ ИЛИ блока анализа состояния соединен с одним из разрядов информационного выхода регистра кода операции блока управления , первый вход элемента И-НЕ блока управления соединен с инверсным выхцдом триггера блока управления, а выход э.лемента И-НЕ блока управления подключен к управляющим входам первого, второго и третьего регистров, отличающееся тем, что, с целью повышения быстродействия вычисления, сумматоры вьтолне- ,ны в избыточной знакоразрядной системе счисления, в блок анализа состояния введены узел приоритета и шифратор, вькоды третьего и четвертого сдвигателей соединены с вторыми информационными входами соответственно первого и второго сумматоров, выходы которых соединены с информационными входами соответственно четвертого и третьего сдвигателей, управляющие входы которых подключены к адресной шине устройства, выходы первого и второго регистров подключены к первым информационньм входам соответственно четвертого и пятого сум30361

маторов, вторые информационные входы которых соединены с выходами соответственно второго и первого сдвигателей, в блоке анализа состояния выход коммутатора соединен с входом узла приоритета, информационный выход которого подключен к входу шифратора, выход которого соединен с информационным входом узла буферной памяти, второй выход которого подключен квторому адресному входу одноразрядного узла памяти, управляющий выход узла приоритета блока анализа состо- яния подключен к информационному входу триггера блока анализа состояния, синхровход которого соединен с тактовым входом одноразрядного узла памя ти блока анализа состояния, а выход соединен с информационном входом триггера блока управления и вторым входом элемента И-НЕ блока управления, второй вход элемента ИСКПЮЧАЩЕЕ ИЛИ блока анализа состояния соединен с адресной шиной устройства, дополнительный выход регистра кода операции блока управления подключен к стробирующему входу блока памя ти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления элементарных функций | 1980 |

|

SU1103225A1 |

| Устройство для вычисления функции | 1984 |

|

SU1180884A1 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU1035604A1 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU940155A1 |

| Мультипроцессорная система | 1983 |

|

SU1156088A1 |

| Универсальный цифровой преобразователь координат | 1980 |

|

SU924701A1 |

| Микропрограммный процессор | 1985 |

|

SU1275457A1 |

| Параллельный процессор | 1985 |

|

SU1315989A1 |

| Центральный процессор | 1991 |

|

SU1804645A3 |

| Система коммутации | 1986 |

|

SU1354200A1 |

УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ЭЛЕМЕНТАРНЫХ ФУНКЦИЙ, содержащее три регистра, четыре сдвигателя, пять сумматоров, блок памяти, блок управления и блок анализа состояния, причем первые информационные входы регистров соединены с информационной шиной устройства, выходы первого, второго и третьего сумматоров . соединены с соответствующими выходами устройства и с вторыми информационными входами соответствующих регистров, выходы первого, второго и третьего регистров соединены соответственно с информационными входами первого и второго сдвигателей и первым информационным входом третьего сумматора, первые информационные входы первого и второго сумматоров соединены с выходами четвертого и пятого сумматоров соответственно, второй информационный вход третьего сумматора подключен к выходу блока памяти, причем блок управления содержит генератор импульсов, регистр кода операции, триггер и элемент И-НЕ, блок анализа состояния r.v.,.....V |f| . i f содержит одноразрядный узел памяти, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, коммутатор узел буферной памяти, триггер, при этом шина кода операции устройства соединена с информационным входом регистра кода операции блока управления, вход запуска устройства соединен с управляющим -входом регистра кода операции блока управления, установочным входом триггера блока управления и входом запуска ганератЬра импульсов блока управления, выход генератора импульсов блока управления соединен -с синхровходами первбго, второго и третьего регистров, г триггера блока управления и триггере блока анализа состояния, информационный выход регистра кода операции блока управления соединен с первым адресным входом одноразрядного узла с .памяти блока анализа состояния и Зправляющим входом коммутатора блока анализа состояния, информационные входы которого соединены с вы&9 ходами первого, второго и третьего сумматоров, выход одноразрядного эо узла памяти блока анализа состояния Э) соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ блока анализа состояния, выходы одноразрядного узла памяти и элемента ИСКЛЮЧАЮЩЕЕ ИЛИ блока анализа состояния подключены к управляющим входам первого, второго, третьего, четвертого и пятого сумматоров, первьй выход узла буферной памяти блока анализа состояния соединен с адресной шиной устройства, которая подключена к управляющим входам первого и второго сдвигателей и блока памяти, второй вход

i Изобретение относится к вьиислительной технике и может быть ирпользовано в цифровых моделирующих,.управляющих и вычислительных системах как общего, так и специального назначения. ,.

Известно устройство для вычисления элементарных функций, состоящее из трех регистров, четырех блоков сдвига, блока памяти, семи сумматоров, четырех переключателей и блока управления, выполненного в виде собственно блока управления и блока анализа состояния, причем коррекция деформации решения осуществляется путем вычисления на дополнительных сумматорах соответствующих поправок 13.

Однако устройство имеет ограниченное быстрЬдействие, узкие функциог нальные возможности и область при:менения за счет ограничения диапазона изменения аргумента и невозможности непрерывного генерирования функций, в том числе с управляемым шагом.

Недостатки вызваны зависимостью коэффициента деформации решения от набора итераций, в результате чего . этот набо15 задается фиксированным, поэтому вариации его, в зависимости от аргумента или режима функционирования, недопустимы.

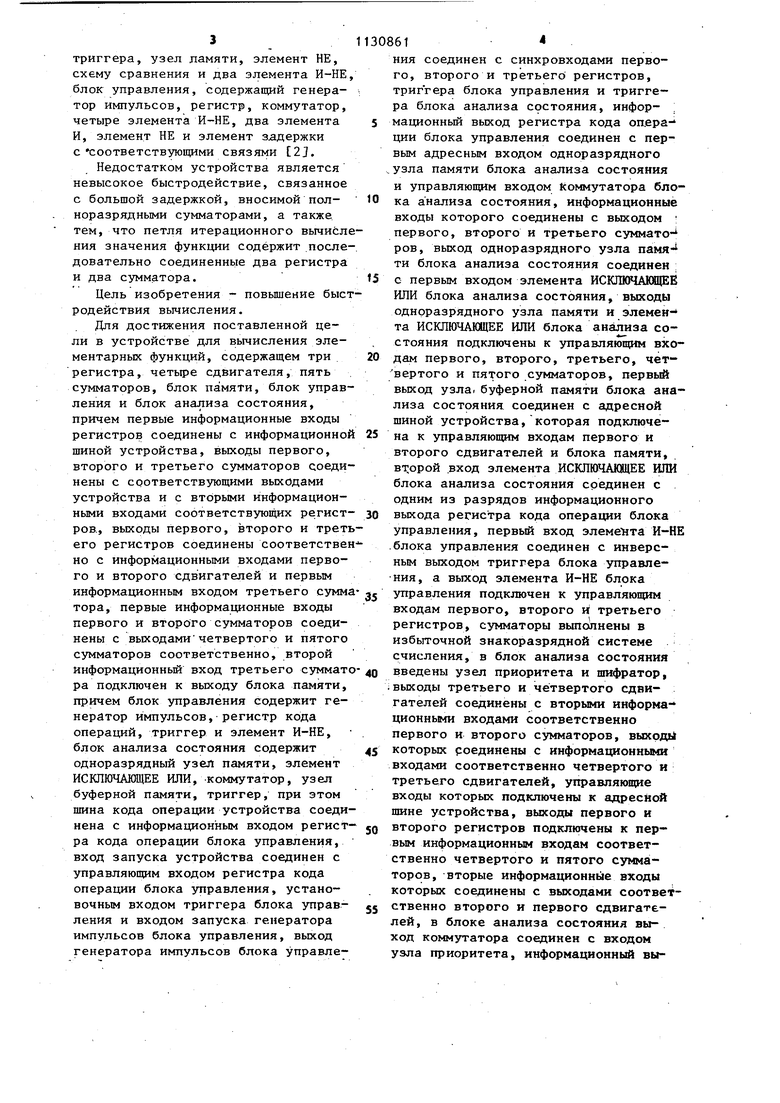

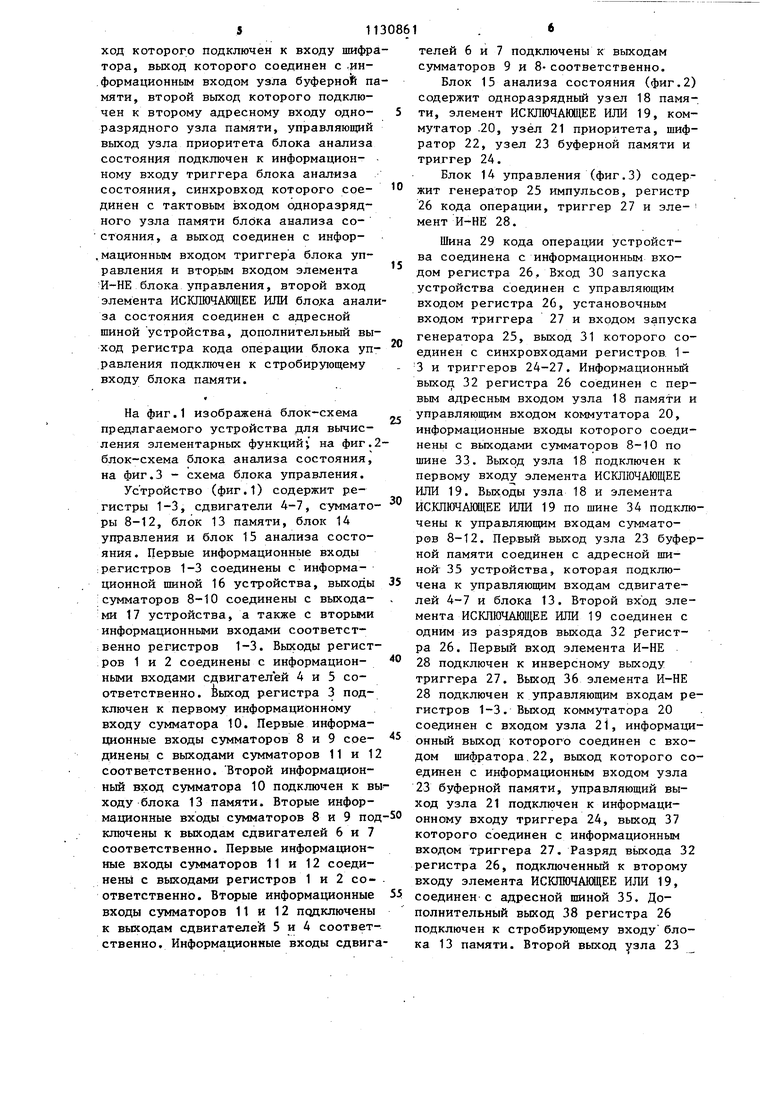

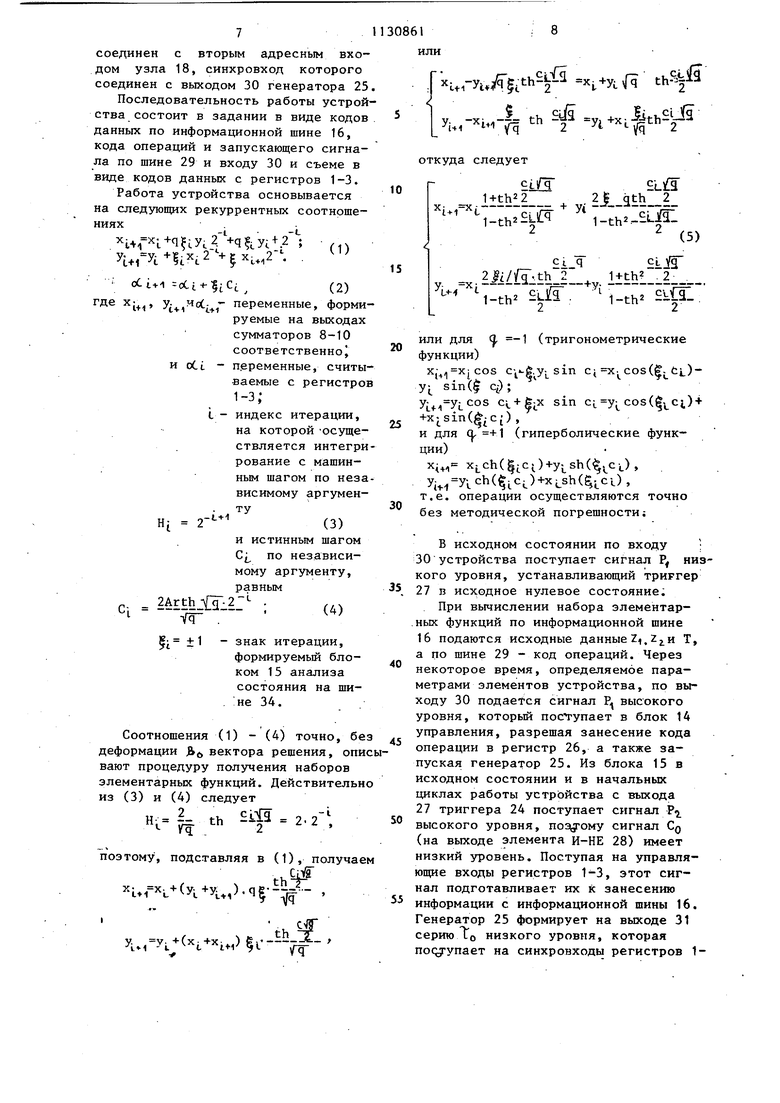

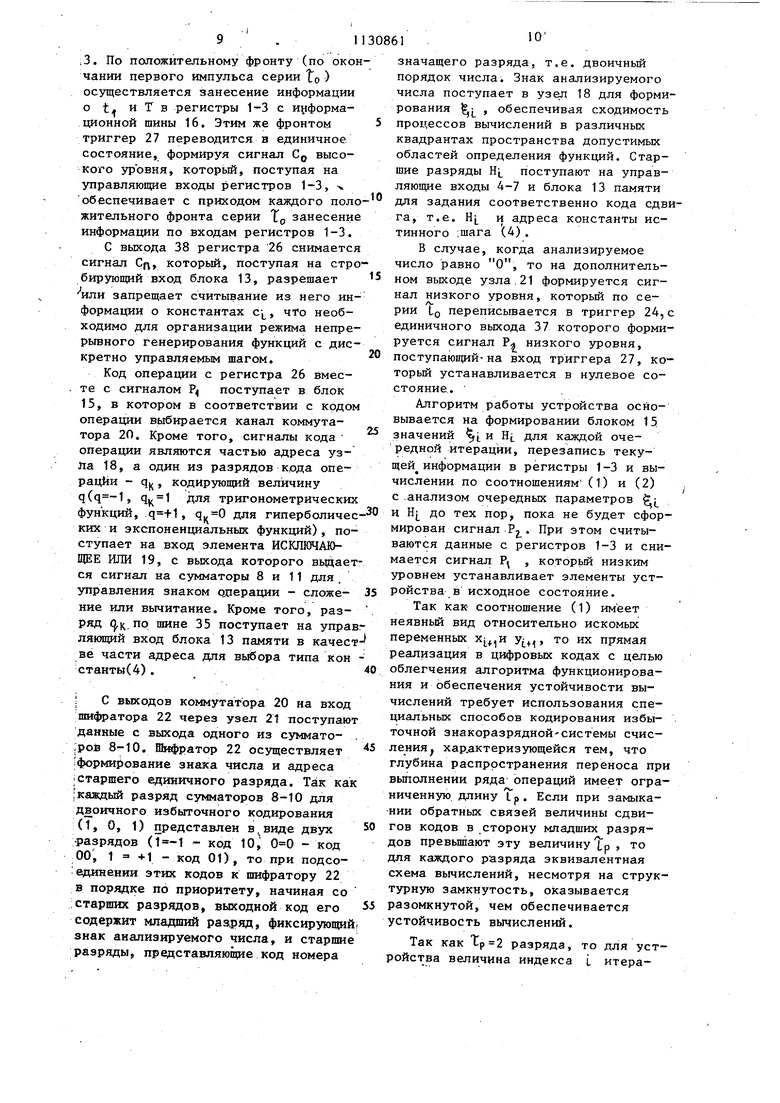

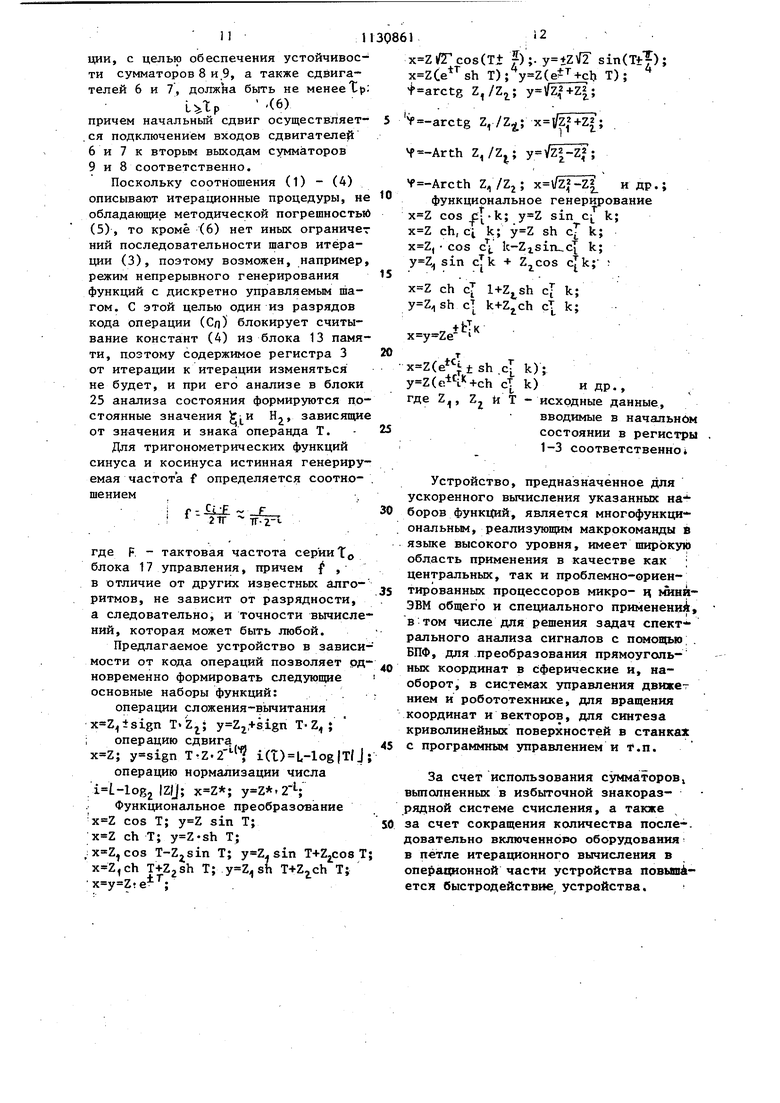

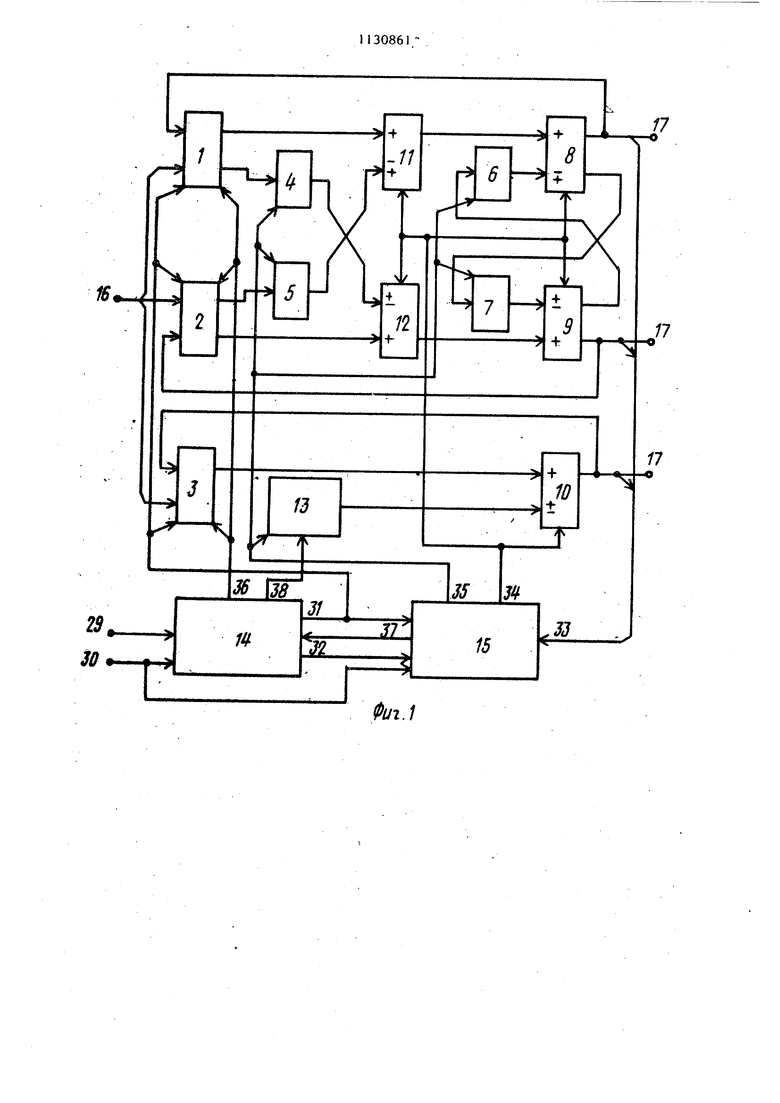

Наиболее близким к изобретению является устройство для вычисления элементарных функций, содержащее пять регистров, два сдвигателя, пять сумматоров, два переключателя, два блока памяти, два счетчика и регистр кода операций, блок анализа з1нака, содержащий регистр, одноразрядный узел памяти и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, блок нормализации, содержащий коммутатор, счетчик, четыр 3 триггера, узел памяти, элемент НЕ, схему сравнения и два элемента И-НЕ блок управления, содержащий генератор импульсов, регистр, коммутатор, четыре элемента И-НЕ, два элемента И, элемент НЕ и элемент задержки ссоответствующими связями 12. Недостатком устройства является невысокое быстродействие, связанное с большой задержкой, вносимой полноразрядными сумматорами, а также тем, что петля итерационного вычисл ния значения функции содержит после довательно соединенные два регистра и два сумматора. Цель изобретения - повышение быс родействия вычисления. Для достижения поставленной цели в устройстве для вычисления элементарных функций, содержащем три регистра, четыре сдвигателя, пять сумматоров, блок памяти, блок управ ления и блок анализа состояния, причем первые информационные входы регистров соединены с информационно шиной устройства, выходы первого, второго и третьего сумматоров соеди нены с соответствующими выходами устройства и с вторыми информационными входами соответствующих регист ров., выходы первого, второго и трет его регистров соединены соответстве но с информационными входами первого и второго сдвигателей и первым информационным входом третьего сумм тора, первые информационные входы первого и второго сумматоров соединены с выходамичетвертого и пятого сумматоров соответственно, второй Информационный вход третьего суммат ра подключен к выходу блока памяти причем блок управления содержит генератор импульсов, регистр кода операций, триггер и элемент И-НЕ, блок анализа состояния содержит одноразрядный узел памяти, элемент ИСКПЮЧАЩЕЕ ИЛИ, -коммутатор, узел буферной памяти, триггер, при этом шина кода операции устройства соеди нена с информационным входом регист ра кода операции блока управления, вход запуска устройства соединен с управляющим входом регистра кода операции блока управления, установочным входом триггера блока управления и входом запуска генератора импульсов блока управления, выход генератора импульсов блока управле61ния соединен с синхровходами первого, второго и третьего регистров, триггера блока управления и триггера блока анализа состояния, инфор- ; мационный выход регистра кода опера- ции блока управления соединен с первым адресным входом одноразрядного узла памяти блока анализа состояния и управляющим входом Коммутатора блока анализа состояния, информационные входы которого соединены с выходом ; первого, второго и третьего сумматоров, выход одноразрядного узла памяти блока анализа состояния соединен с первым входом элемента ИСКЛЮЧАКНЦЕВ ИЛИ блока анализа состояния, выходы одноразрядного узла памяти и элемен- та ИСКЛЮЧАЮЩЕЕ ИЛИ блока анализа состояния подключены к управляющим входам первого, второго, третьего, четвертого и пятого сумматоров, первый выход узла, буферной памяти блока анализа состряния соединен с адресной шиной устройства, которая подключена к управляющим входам первого и второго сдвигателей и блока памяти, вт.орой .вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ блока анализа состояния соединен с одним из разрядов информационного выхода регистра кода операции блока управления, первый вход элемента И-НЕ блока управления соединен с инверсным выходом триггера блока управления, а выход элемента И-НЕ блока управления подключен к управляющим входам первого, второго и третьего регистров, сумматоры выполнены в избыточной знакоразрядной системе счисления, в блок анализа состояния введены узел приоритета и шифратор, выходы третьего и четвертого сдвигателей соединены с вторыми информа- ционньми входами соответственно первого и второго сумматоров, выхрд которых роединены с информационными входами соответственно четвертого и третьего сдвигателей, утфавляющие входы которых подключены к адресной шине устройства, выходы первого и второго регистров подключены к первым информационным входам соответственно четвертого и пятого сумматоров, вторые информационные входы которых соединены с выходами соответственно второго и первого сдвигателей, в блоке анализа состояния выход коммутатора соединен с входом узла приоритета, информационный вы511ход которого подключен к входу шифра тора, выход которого соединен с .ин.формационным входом узла буферной па мяти, второй выход которого подключен к второму адресному входу одноразрядного узла памяти, управляющий выход узла приоритета блока анализа состояния подключен к информационному входу триггера блока анализа состояния, синхровход которого соединен с тактовым входом одноразрядного узла памяти блока анализа состояния, а выход соединен с инфор.мадконным входом триггера блока управления и вторым входом элемента И-НЕ блока управления, второй вход элемента ИСКЛЮЧАЩЕЕ ИЛИ блока анали за состояния соединен с адресной шиной устройства, дополнительный выход регистра кода операции блока управления подключен к стробирующему входу блока памяти. На фиг.1 изображена блок-схема предлагаемого устройства для вычисления элементарных функций; на фиг. блок-схема блока анализа состояния, на фиг.З - схема блока управления. Устройство (фиг.1) содержит регистры 1-3, сдвигатели 4-7, сумматоры 8-12, блок 13 памяти, блок 14 управления и блок 15 анализа состояния . Первые информационные входы :регистров 1-3 соединены с информационной шиной 16 устройства, выходы :сумматоров 8-10 соединены с выходами 17 устройства, а также с вторьми информационными входами соответст,венно регистров 1-3. Выходы регист ров 1 и 2 соединены с информационными входами сдвигателей 4 и 5 соответственно. Выход регистра 3 подключен к первому информационному входу сумматора 10. Первые информационные входы сумматоров 8 и 9 соединены с выходами сумматоров 11 и 1 соответственно. Второй информационный вход сумматора 10 подключен к в ходу блока 13 памяти. Вторые информационные входы сумматоров 8 и 9 под ключены к выходам сдвигателей 6 и 7 соответственно. Первые информационные входы сумматоров 11 и 12 соединены с выходами регистров 1 и 2 соответственно. Вторые информационные входы сумматоров 11 и 12 подключены к выходам сдвигателей 5 и 4 соответственно. Информационные входы сдвиг 1 - телей 6 и 7 подключены к выходам сумматоров 9 и 8- соответственно. Блок 15 анализа состояния (фиг.2) содержит одноразрядный узел 18 памяти, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 19, коммутатор .20, узел 21 приоритета, шифратор 22, узел 23 буферной памяти и триггер 24. Блок 14 управления (фиг.З) содержит генератор 25 импульсов, регистр 26 кода операции, триггер 27 и элемент И-НЕ 28. Шина 29 кода операции устройства соединена с информационным входом регистра 26, Вход 30 запуска устройства соединен с управляющим входом регистра 26, установочным входом триггера 27 и входом запуска генератора 25, выход 31 которого соединен с синхровходами регистров. 13 и триггеров 24-27. Информационньй выхо;:; 32 регистра 26 соединен с первым адресным входом узла 18 памяти и управляющим входом коммутатора 20, информационные входы которого соединены с выходами сумматоров 8-10 по шине 33. Выход узла 18 подключен к первому входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 19. Выходы узла 18 и элемента ИСКЛЮЧАЩЕЕ ИЛИ 19 по шине 34 подключены к управляющим входам сумматоров 8-12. Первый выход узла 23 буферной памяти соединен с адресной шиной 35 устройства, которая подключена к управляющим входам сдвигателей 4-7 и блока 13. Второй вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 19 соединен с одним из разрядов выхода 32 регистра 26. Первый вход элемента И-НЕ 28 подключен к инверсному выходу триггера 27. Выход 36 элемента И-НЕ 28 подключен к управляющим входам регистров 1-3. Выход коммутатора 20 соединен с входом узла 21, информадионный выход которого соединен с входом шифратора,22, выход которого соединен с информационным входом узла 23 буферной памяти, управляющий выход узла 21 подключен к информационному входу триггера 24, выход 37 которого соединен с информационным входом триггера 27. Разряд вьгхода 32 регистра 26, подключенный к второму входу элемента ИСКЛЮЧАЩЕЕ ИЛИ 19, соединен с адресной шиной 35. Дополнительный выход 38 регистра 26 подключен к стробирующему входу блока 13 памяти. Второй выход узла 23 соединен с вторым адресным вхо дом узла 18, синхроБХод которого соединен с выходом 30 генератора 25 Последовательность работы устрой ства состоит в задании в виде кодов данных по информационной шине 16, кода операций и запускающего сигнала по шине 29 и входу 30 и съеме в виде кодов данных с регистров 1-3. Работа устройства основывается на следующих рекуррентных соотношениях 14Г 1+П 1УсД+Ч 1У1+2-; . у. у. +Е х- 2 + С Х- I Ul 5j.L 1 t+i oCi+1 oCif-:§iCi. У,иоС.- переменные, форми руемые на выходах сумматоров 8-10 соответственно и oCi. - переменные, считы ваемые с регистро I - индекс итерации, на которой Осуществляется интегри рование с машинным шагом по неза висимому аргументуи истинным шагом С по независимому аргументу, равным г- - 2Arth -{J-2 YT . ±1 - знак итерации, формируемый блоком 15 анализа состояния на шине 34. Соотношения (1) - (4) точно, бе деформации Jb, вектора решения, опи вают процедуру получения наборов элементарных функций. Действительн из (3) и (4) следует H. 2 сс 2-2 .4 Yq:2 поэтому, подставляя в (1), получае th4 (yi4.,(..i |i---7f1 или uгУt./Г5,,.я th 1 „ ,,. l th v, 2 У1 lyq 2 Vq откуда следует ctfq , y. 2J.ath 2 1+th22 .Lir i . , 2|i//J. l±thi 2, SL. ЬЙ: или для ( -1 (тригонометрические функции) x- xjcos .sin .cos()yj sin($ Cj); YLti yLCos 4 + |i.x sin (,)-«+xj sin(C) , и для c +1 (гиперболические функции) ()(.С1.), ..е. операции осуществляются точно без методической погрешности; В исходном состоянии по входу ; 30 устройства поступает сигнал Р низкого уровня, устанавливающий триггер 27 п исходное нулевое состояние; При вычислении набора элементарных функций по информационной шине 16 подаются исходные данные Z,. Т, а по шине 29 - код операций. Через некоторое время, определяемое параметрами элементов устройства, по выходу 30 подается сигнал Рд высокого уровня, который пос тупает в блок 14 управления, разрешая занесение кода операции в регистр 26, а также запуская генератор 25. Из блока 15 в исходном состоянии и в начальных циклах работы устройства с выхода 27 триггера 24 поступает сигнал Р высокого уровня, сигнал CQ (на выходе элемента и-НЕ 28) имеет низкий уровень. Поступая на управляющие входы регистров 1-3, этот сигнал подготавливает их к занесению информации с информационной шины 16. Генератор 25 формирует на выходе 31 серию TO низкого уровня, которая noqjynaeT на синхровходы регистров 1,3. По положительному фронту (по окон чании первого импульса серии to) осуществляется занесение информации о t, и Т в регистры 1-3 с ирформационной шины 16. Этим же фронтом триггер 27 переводится в единичное состояние, формируя сигнал С высокого уровня, который, поступая на управляющие входы регистров 1-3, обеспечивает с приходом каждого поло жительного фронта серии TO занесение информации по входам регистров 1-3. С выхода 38 регистра 26 снимается сигнал Cfj, который, поступая на стро бирующий вход блока 13, разрешает или запрещает считывание из него информации о константах с-, что необходимо для организации режима непрерывного генерирования функций с дискретно управляемым шагом. Код операции с регистра 26 вместе с сигналом Р поступает в блок 15, в котором в соответствии с кодом операции выбирается канал коммутатора 20. Кроме того, сигналы кода операции являются частью адреса узла 18, а один из разрядов кода операции - q|, кодирующий величину q(, для тригонометрических функций, ., для гиперболичес ких и экспоненциальных функций), поступает на вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 19, с выхода которого вьдает ся сигнал на сумматоры 8 и 11 для. управления знаком операции - сложение или вычитание. Кроме того, разряд 9К Р шине 35 поступает на упра ляющий вход блока 13 памяти в качес ее части адреса для вьЙора типа кон станты(4). С выходов коммутатора 20 на вход шифратора 22 через узел 21 поступаю данные с выхода одного из суммато,ров 8-10. НЬфратор 22 осуществляет |форю1 ование знака числа и адреса ;старшего единичного разряда. Так ка каладый разряд сумматоров 8-10 для двоичного избыточного кодирования (1, О, 1) представлен двух :-разрядов ( - код 10, - код 00, 1 +1 - код 01), то при подсоединении этих кодов к шифратору 22 в порядке по приоритету, начиная со :старших разрядов, выходной код его содержит младший раяряд, фиксирующий знак анализируемого числа, и старшие разряды, представляющие код номера значащего разряда т.е. двоичный порядок числа. Знак анализируемого числа поступает в узел 18 для формирования , обеспечивая сходимость процессов вычислений в различных квадрантах пространства допустимых областей определения функций. Старшие разряды HL поступают на управляющие входы 4-7 и блока 13 памяти для задания соответственно кода сдвига, т.е. Н и адреса константы истинного .шага (4). В случае, когда анализируемое число равно О, то на дополнительном выходе узла.21 формируется сигнал низкого уровня, который по серии to переписьтается в триггер 24,с единичного выхода 37 которого формируется сигнал Рл низкого уровня, поступающий-на вход триггера 27, ко торый устанавливается в нулевое состояние. Алгоритм работы устройства основывается на формировании блоком 15 значений i и Н для каждой очередной итерации, перезапись текущей информации в регистры 1-3 и вычислении по соотношениям (1) и (2) . с .анализом очередных параметров И Hj до тех пор пока не будет сформирован сигнал Р2. При зтом считываются данные с регистров 1-3 и снимается сигнал Р , которьм низким уровнем устанавливает элементы устройства в исходное состояние. Так как- соотношение (1) имеет неявный вид относительно искомых переменных ,и у, то их прямая реализация в цифровых кодах с целью облегчения алгоритма функционирования и обеспечения устойчивости вычислений требует использования специальных способов кодирования избыточной знакоразряднойсистемы счисления хардктеризующейся тем, что глубина распространения переноса при вьшолнении ряда операций имеет ограниченную длину Lp. Если при замыкании обратных связей величины сдвигов кодов в сторону младших разрядов превышают эту величину tp , то для каждого разряда эквивалентная схема вычислений, несмотря на структурную замкнутость, оказывается разомкнутой, чем обеспечивается устойчивость вычислений. Так как разряда, то для устройства величина индекса L итераn1ции, с целью обеспечения устойчивости сумматоров 8 и.9, а также сдвигателей 6 и 7, должна быть не менее Тр Utp (6) причем начальный сдвиг осуществляет.ся подключением входов сдвигателей 6 и 7 к вторым выходам сумматоров 9 и 8 соответственно. Поскольку соотношения (1) - (4) описывают итерационные процедуры, н обладающие методической погрешность (5), то кроме (6) нет иных ограниче НИИ последовательности шагов итерации (3), поэтому возможен, например режим непрерывного генерирования функций с дискретно управляемым шагом. С этой целью один из разрядов кода операции (Сп) блокирует считывание констант (4) из блока 13 памя ти, поэтому содержимое регистра 3 от итерации к итерации изменяться не будет, и при его анализе в блоки 25 анализа состояния формируются по стоянные значения ХцИ 2, зависящи от значения и знака операнда Т. Для тригонометрических функций синуса и косинуса истинная генериру емая частота f определяется соотношениемi fra: : 2ТГ тГрт. где F - тактовая частота серии То блока 17 управления, причем , в отличие от других известных алгоритмов, не зависит от разрядности, а следовательно, и точности вычисле ний, которая может быть любой. Предлагаемое устройство в завися мости от кода операции позволяет рд новременно формировать следуюп1ие основные наборы функций: операции сложения-вьмитания x Z isign T. ,+sign Т-Z ; ; операцию сдвига T-Z.2-Y i(t) L-log|Tl J операцию нормализации числа i L-log2 IZIJ; .2-V .| Функциональное преобразование cos T; sin T; ch T; T; T; . sin T ,ch T; ,sh T; 1 x Zlfrcos(T± |);. y 4ZV2 sin(Tt|); Т); ( Т); t arctg Z,/Z,; y fzf+z|; V -arctg Z, x |/Z2+Z2; f -Arth Z, y Vz|-Zf; 4 -Arcth ,; x /Z2-z и др.; функциональное генерирование cos sin Cj k; ch,ci k; sh c k; , cos c k-Zisiruc{ k; sin cTk + ; ch c7 cT cT cT k; i-tTK ( sh .c k); ( cT k) и др.. где Z, Z. и Т - исходные данные, вводимые в начальном состоянии в регистры 1-3 соответственно Устройство, предназначенное для ускоренного вычисления указанных наборов функций, является многофункциональным, реализующим макрокоманды в язьже высокого уровня, имеет широкую область применения в качестве как ; центральных, так и проблемно-ориентированных процессоров микро- ц етниЭВМ общего и специального применений, в том числе для решения задач спект-рального анализа сигналов с помов(ью БПФ, для преобразования прямоуголь„ „ координат в сферические и. наоборот, в системах управления движет нием и робототехнике, для вращения координат и векторов, для синтеза криволинейных поверхностей в станках с программным управлением и т.п. За счет использования сумматоровj вьшопненных в избыточной знакоразрядной системе счисления, а также за счет сокращения количества после-, доватепьно включенноро оборудования в петле итерационного вычисления в операционной части устройства повыш ется быстродействие устройства.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для вычисления тригонометрических функций | 1974 |

|

SU519717A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU1035604A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-12-23—Публикация

1980-06-26—Подача