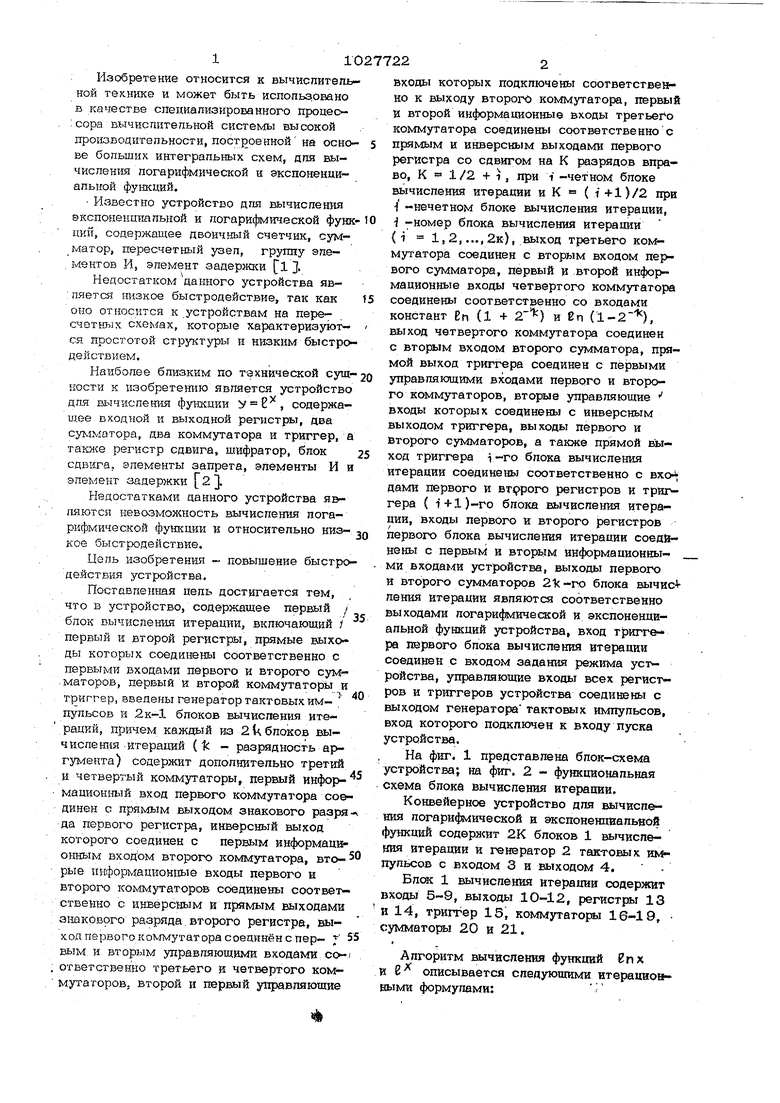

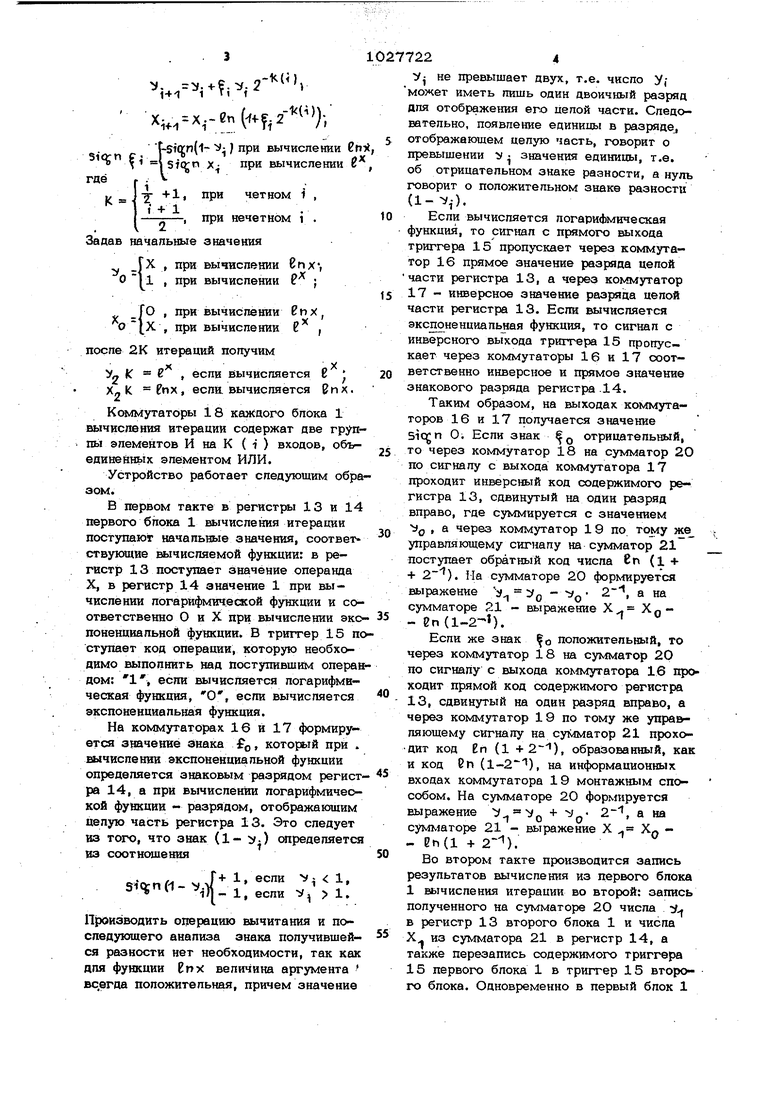

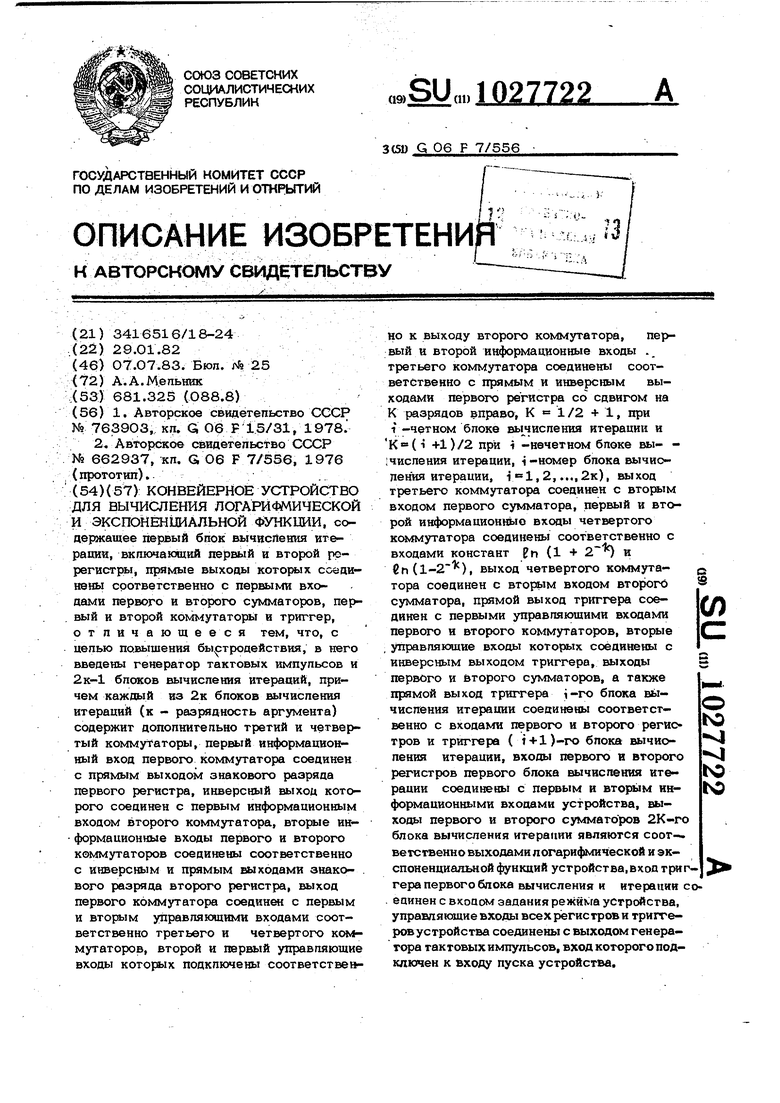

110 Изобретение относится к вычиспитепьной тегснике и может быть использовано в качестве специализированного процес icopa вычиспитепьной системы высокой лроизводигепьности, построенной на основе бопьшик интегральных схем, дпя вычиспешет аогарифмичеасой и экспоненииапьной функций. Известно устройство дгш вычисления экспоненциальной и погарифмической функ 1ШЙ, содержащее двоичный счетчик, сумматор, пересчетный узел, группу элементов И, элемент задержзш 1 J Недостатком данного устройства яв- : пяется низкое быстродействие, так как оно относнтся к .устройствам на пересчетш х схемах, которые характеризуются простотой структуры и низким быстродействием. Наиболее близким по технической сущности к изобретению является устройство для вы ч йс пения У 2. , содержащее входной и выходной регистры, два сумматора, два коммутатора и триггер, а такисе регистр сдвига, ЕШфратор, блок сдвига, элементы запрета, элементы И и элемент задержки 2. Недостатками данного устройства я&ляются невозможность вычисления погарифмической функции и относительно низкое быстродействие. Цепь изобретения - повышение быстро действия устройства. ПoQтaвлeн шя цепь достигается тем, что в устройство, содержащее первый / блок вычисдекия итерации, включающий У первый и второй регистры, прямые выходы которых соединены соответственно с первыми входами первого и второго сум-маторов, первый и второй коммутаторы и триггер, введены генератор тактовых импульсов и 2к-1 блоков вычиспения итераций, причем каждый из 2 U блоков вычисления итераций (k - разрядность apvгумента) содержит допопнктепьно третий и четвер7-ый коммутаторы, первый инфо1 мацион Л1 й вход первого коммутатора сое динен с прямым выходом знакового разря да первого регистра, инверсный выход которого соединен с первым информационным входЬм второго коммутатора, вторые информациоН11ые входы первого и второго коммутаторов соединены соответственно с инверсным и прямым выходами знаковрго разряда второго регистра, выход первого кокгмутатора соединён с пер- вым и вторым управляющими входами coответственно третьего и четвертого коммутаторов, второй и гюрвый ухфавпяющие 22 ВХОДЫ которых подключены соответстве но к выходу второго коммутатора, первый И второй информационные входы третьего коммутатора соединены соответственно с прямым и инверсным выходами первого регистра со сдвигом на К разрядов вправо, К 1 /2 4- 1 , при 1 -четном блоке вь1числения итерации и К ( i +1)/2 при -нечетном блоке вычисления итерации, i -номер блока вычисления итерации {i 1,2,..., 2к), выход третьего коммутатора соединен с вторым входом первого сумматора, первый и второй информационные входы четвертого коммутатора соединены соответственно со входами констант Еп (1 + 2) и бп (1-2), выход четвертого коммутатора соединен с вторым входом второго сумматора, прямой выход триггера соединен с первыми управляющими входами первого и второго коммутаторов, вторые управляющие входы которых соединены с инверсным выходом триггера, выходы первого и второго cjTMMaTOpoB, а также прямой выход триггера i-го блока вычисления итерации соединены соответственно с вхо дами первого и второго регистров и триггера { 1+1)-го блока вычисления итерация, входы первого и второго регистров первого блока вычисления итерации соединены с первым и вторьш информационны- . ми входами устройства, выходы первого н второго сумматоров блока вычис г ления итерации являются соответственно выходами логарифмической и экспоненциальной функций устройства, вход триггера первого блока вычисления итерации соединен с входом задания режима устройства, управляющие входы всех регистров и триггеров устройства соединены с выходом генератора тактовых импульсов, вход которого подключен к входу пуска устройства. На фиг. 1 представпена блок-схема устройства; на фиг. 2 - функциональная схема блока вычисления итерации. Конвейерное устройство для вычисления логарифмической и экспоненциальной функций содержит 2К блоков 1 вычисления итерации и генератор 2 тактовых импульсов с входом 3 и выходом 4. Блок 1 вычисления итерации содержит входы 5-9, выходы 10-12, регистры 13 и 14, триггер 15, коммутаторы 16-19, сумматоры 20 и 21. Алгоритм иычиспения функций 2пх v. К описывается следующими итерацио йыми формулами: ,-К(0. H.-i-fi f x,,-x.-en.f, t-Siffn(l- i;) при Бычиспении m SiOn f I T) 1rtX 1 tg(vn X- при вычислении к pflfi . . V -я- +1, при четном i , 1 + 1 ---, при нечетном i Задав начальные значения ГХ , при вычиспении бпх, -Р о . при вычислении при вычиспении 8 п X , к -РolX , при вычиспении В , после 2К итераций получим ,х если вычисгшется 6 J Рпх, еспа вычисляется В п х. Коммутаторы 18 каждого блока 1 вычисления итерации содержат две груп пь1 элементов И на К ( i ) входов, объединейньгх элементом ИЛИ. Устройство работает следующим обра зом. В первом такте в регистры 13 и 14 первого блока 1 вычисления итерации поступают начальные значения, соответствующие вычисляемой функции: в регистр 13 поступает значение операнда X, в регистр 14 значение 1 при вычислении логарифмической функции и соответственно О и X при вычислении экс поненциапьной функции. В триггер 15 п ступает код операции, которую необходимо выполнить над поступившим опера дом: , если вычисляется логарифмическая функция, О, если вычисляется экспоне нциа льная функция. На коммутаторах 16 и 17 формируется значение знака fg, который при вычислении экспоненциальной функции определяется знаковым разрядом регист ра 14, а при вычислении логарифмической фуйсции - разрядом, отображающим цепую часть регистра 13. Это следует из того, что знак (1- у.} сятределяетс ИЗ соотношения . 1, )|-l, П)р(иэводить операцию вычитания и последующего анализа знака получившейся разности нет необходимости, так как для функции Епх величина аргумента вс,егда положительная, причем значение V не превышает двух, т.е. число У,ожет иметь пищь один двоичный разряд для отображения его целой части. Следовательно, появление единиць в paзpядeJ тображающем целую часть, говорит о превышении г; значения единицы, т.е. об отрицательном знаке разности, а нуль оворит о положительном знаке разности (). Если вычисляется логарифмическая функция, то сигнал с прямого выхода триггера 15 пропускает через коммутатор 16 прямое значение разряда целой части регистра 13, а через коммутатор 17 - инверсное значение разряда целой части регистра 13. Если вычисляется экспоненциаль 1ая функция, то сигнал с инверсного выхода триггера 15 пропускает через коммутаторы 16 и 17 соответственно инверсное и прямое значение знакового разряда регистра .14. Таким образом, на выходах коммутаторов 16 и 17 получается значение sicrn О. Если знак Q отрицательный, то через коммутатор 18 на сумматор 2О по сигналу с выхода коммутатора 17 проходит инверсный код содержимого регистра 13, сдвинутый на один разряд вправо, где суммируется с значением ад , а через коммутатор 19 по тому же управляющему сигналу на сумматор 21 поступает обратный код числа Кп (1 + + ). На сумматоре 20 форьл1руется выражение - :)- 2 сумматоре 21 - выражение X -еп(1-2-). Если же знак о положительный, то через коммутатор 18 на сумматор 20 по сигналу с выхода кo tмyтaтopa 16 проходит прямой код содержимого регистра 13, сдвинутый на один разряд вправо, а через коммутатор 19 по тому же управляющему сигналу на сумматор 21 проходит код Еп (1 +2), образованный, как и код бп (), на информационных входах коммутатора 19 монтажным способом. На сумматоре 20 формируется 2-, а на выражение :/. сумматоре 21 - выражение X . XQ - Вп(1 + 2-4). Во втором такте производится запись результатов вычисления из первого блока 1 вычисления итерации во второй: запись полученного на сумматоре 20 числа :у в регистр 13 второго блока 1 и числа Х- из сумматора 21 в регистр 14, а также перезапись содержимого триггера 15 первого блока 1 в триггер 15 второго блока. Одновременно в первый блок 1 вычиспения итерации поступает второй операнд в код выпопняемой над ним операции, В первом бпоке 1 производится выпопнение первой итерации над вторым операндом, анапогично выполненной в первом также над первым операндом, а во втором бпоке 1 выпопняется вторая итераиия над первым операндом, и на сумматоре 20 попучается чиспо Vo и на сумматоре . 21 - X,j.. В т ютьем такте резупьтаты вычиспений, подученные во втором бпоке 1, и код операции записываются в третий бпок 1 вычиспения итерации, а резупьтаты из первого бпока и код операции - во второй. В. первый бпок поступает третий операнд и код выполняемой над ним операции. В дапьнейшем резупьтаты предыдущих блоков и коды операций поступают в поспедующие бпоки, а в первый бпок посту/паат новый операнд и код операции и т.д., причем в каждом четном и спедую щем за ним бпоке промежуточные резупьтагы с коммутатора 18 поступают на сумматор 20 со сдвигом на один разряд вправо бопьшим, чем в предыдущих двух б пока X, а в выражениях погарифмов, которые подаются монтажным способом на коммутатор 19, степень двойки возрастает на еди1Ш«,х. В 2 К-м такте на выходе 10 поспеднего 2К-ГО вычисггитепьного бпока 1 при 1 226 вычиспешга погарифмической функции и на выходе 11 при вычиспешш экспонен-, шюпьной функции попучается первый резудьтаг, а в дадьнейшем в каждом такте на выходе будет появпяться новый резупьтат. Тактовые импупьсы, управпяюшие ра-, ботой устройства, вырабатывает генератор 2 тактовых импупьсов, который запускается и останавпивается сигналом, поступающим по шине 3 из ЭВМ ипи из пупьта управления. Технико-экономическая эффективность предлагаемого устройства закпючается в том, что устройство работает по ко№вейерному принципу, поэтому в каждом такте в него можно вводить новый операнд, а на выходе подучать новый резупьтат вычисления. Кроме того, так как в вместе с операндом,по конвейеру движется и код выполняемой над ним операции, то на разных ступенях конвейера можно одновременно над разжши операндами выполнять разные операции, т.е. такое устройство относится к устройствам типа МКМД (множественный поток команд - множественный поток данных), являющихся наиболее производитепьными. Устройство характеризуется простотой управлеаия, так как управление устройством сводится к выработке-Последовательности тактовых импульсов.

ф 4 W

4J

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления функции @ = @ | 1982 |

|

SU1062693A1 |

| Конвейерное устройство для вычисления функции @ = @ | 1981 |

|

SU964635A1 |

| Устройство для вычисления функции @ = @ | 1982 |

|

SU1034033A1 |

| Устройство для реализации алгоритма Волдера | 1983 |

|

SU1115049A1 |

| Вычислительное устройство | 1980 |

|

SU957203A1 |

| Конвейерное устройство для вычисления функции Y=е @ | 1981 |

|

SU962927A1 |

| Конвейерное устройство для вычисления функций синуса и косинуса | 1981 |

|

SU1003080A1 |

| Арифметико-логическое устройство | 1988 |

|

SU1599853A1 |

| Процессор быстрого преобразования Фурье | 1985 |

|

SU1247891A1 |

| Устройство для вычисления функции х= а + в | 1976 |

|

SU646330A1 |

КОНВЕЙЕРНОЕ УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ЛОГАРИФМИЧЕСКОЙ И ЭКСПОНЕНЦИАЛЬНОЙ ФУНКЦИИ, содержащее первый бпок вычисления итерации, включающий первый и второй ререгистры, прямые выходы которых соедивены срответственно с первыми входами первого и второго сумматоров, первый к второй коммутаторь и триггер, отличающееся тем, что, с цепью повышения быстродействия, в iero введены генератор тактовых импульсов и 2к-1 блоков вычисления итерадий, причем кажшлй из 2к блоков вычисления итераций (к - разрядность аргумента) содержит дополнительно третий и четвертый коммутаторы, первый информационный вход первого коммутатора соединен с прямым выходом знакового разряда первого регистра, инверсный выход которого соединен с первым информационным входом второго коммутатора, вторые ин формаиионные входы первого и второго коммутаторов соединены соответственно с инверсным и прямым выходами знако- . вого разряда второго регистра, выход первого коммутатора соединен с первым и вторым управляющими входами соответственно третьего и четвертого коммутаторов, второй и первый управляющие входы которых подключены соответстве но к выходу второго коммутатора, и второй информационные входы . третьего коммутатора соединены соответственно с прямым и инверсным выходами первого регистра со сдвигом на К разрядов вправо, К 1/2 + i, при 1 -четном блоке вь1числения итерации и К (| +1)/2 при i -нечетном бпоке вы- :числения итерации, i-номер бпока вычиопения итерации, г, 2,...,2к), выход третьего коммутатора соединен с вторым входом первого сумматора, первый и второй информационные входы четвертого ксйугмутатора соединены соответственно с входами констант Рп

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| ПУТЕВОЕ ТОРМОЗНОЕ УСТРОЙСТВО | 1927 |

|

SU7639A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

Авторы

Даты

1983-07-07—Публикация

1982-01-29—Подача