Изобретение относится к вычислительной технике и может быть использовано в качестве специализированного процессора вычислительной системы высокой производительности, построенной на основе больших интегральных схем, для вычисления функции 7 6,

При цифровой обработке сигналов, например в задачах, связанных с обработкой физической информации, требуется выполнять операции вычисления экспоненциальной функции над массивами чисел. Причем в системах реального времени при исследовании быстропротекающих. процессов требования к быстродействию выполнения данной операции очень высоки.

Известно устройство для вычисления функции вида у е , содержащее регистр аргумента, блок маскирования аргумента, блок постоянной памяти, блок оперативной памяти, блок выделения младшей зоны аргумента, блок управления, блок определения нулевых значений аргумента, блок умножения t13

Недостатком известного устройства является низкое быстродействие, поскольку экспоненциальная функция

здесь, вычисляется по итерационной формуле, причем, в каждой итерации используется времяемкая операция умножения.

Наиболее близким по технической сущности к изобретению является устройство, содержащее первый и второй регистры, первый и второй сумматоры, блок сдвига, промежуточный регистр

10 для кратковременного хранения констант , блок памяти для хранения .констант, счетчик адреса, блок микропрограммного управления.

Данное устройство аппаратно реали15зует операцию вычисления функции у е . Быстродействие данного устройства при вычислении функции у 6 не превышает времени Т. 2,5nt(., где п - разрядность обрабатываемых

20 операндов, t, - время суммирования

двух чисел на сумматоре. При реализации данного устройства необходим блок пагляти для хранения 2п констант, .а также микропрограмм блока микро25 программнбго управления С21.

Недостатком известного устройства является низкое быстродействие и большие объемы дорогостоящих блоков памяти для хранения констант и

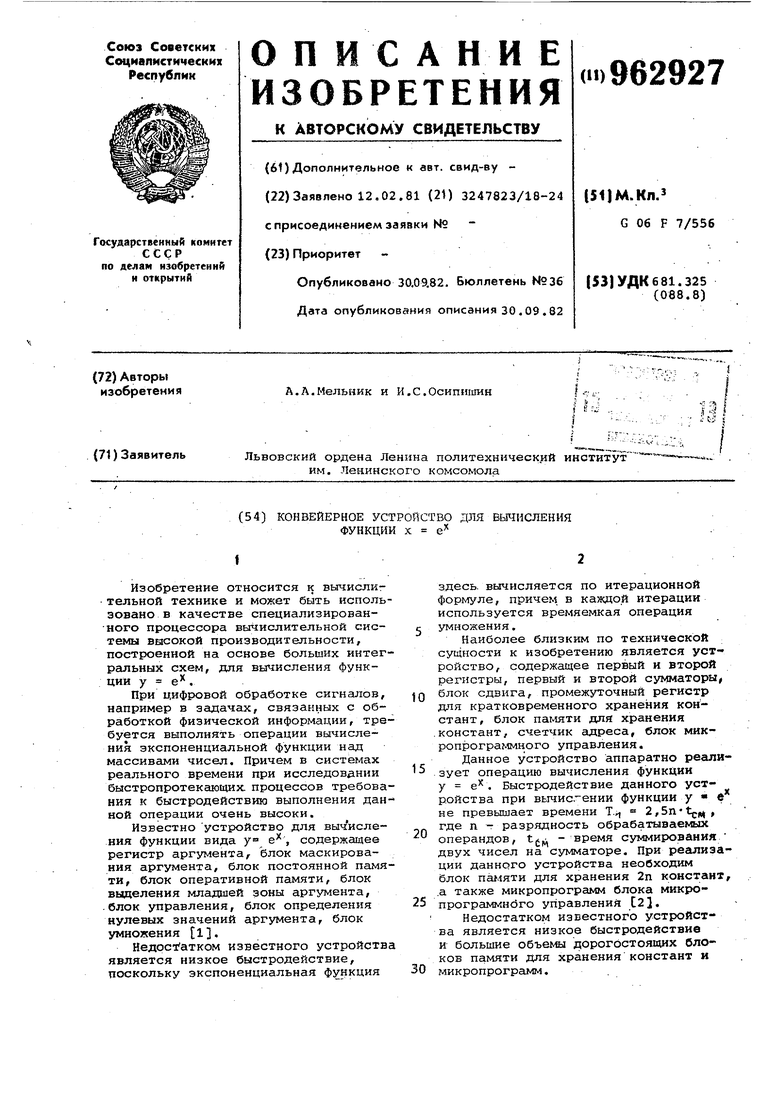

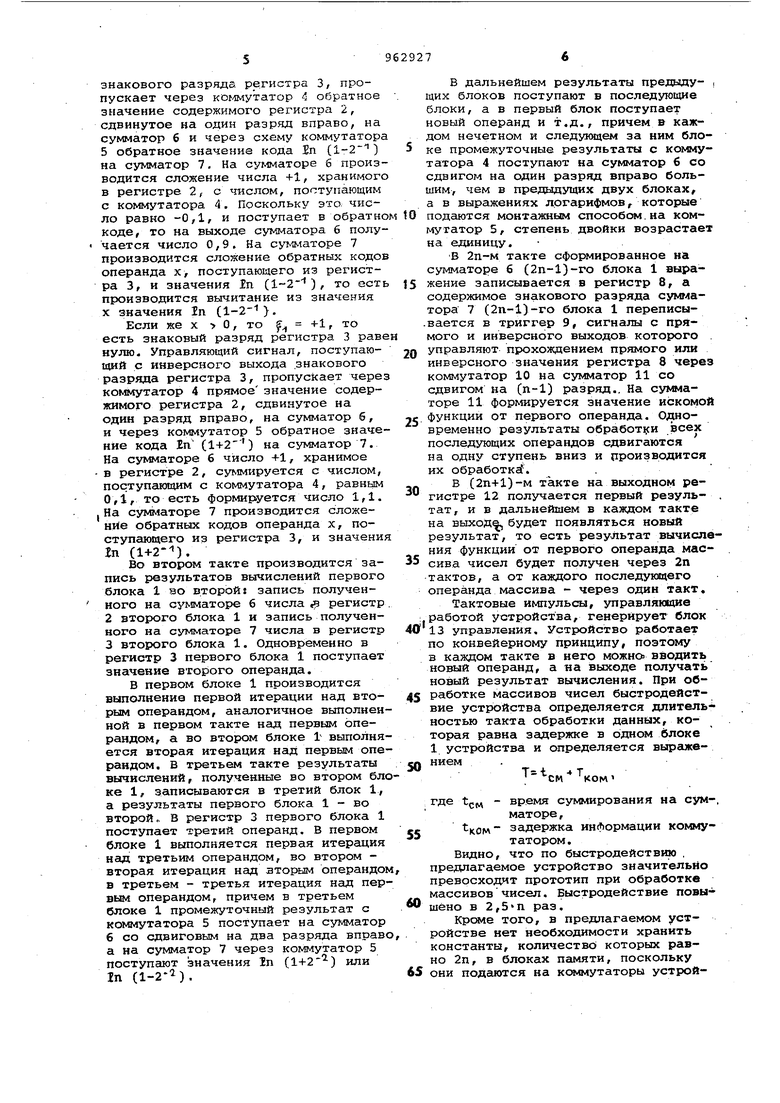

30 микропрограмм. Цель изобретения - повышение быст родейств.гя II сокращение объема памяти . Поставленная цель достигается тем, что в устройство, содержащее блок управления, промежуточный регистр и выходной сумматор, первый вход которого соединен с прямым выходом промежуточного регистра, дополнительно введены (2п-1) блоков вычисления итераций (где п - разрядность аргумента), триггер, выходI ной коммутатор и выходной регистр, выход которого является выходом устройства, управляющий и информационный вхо.ды выходного регистра соединены соответственно с выходом бло ка управления и выходом выходного су1 1матора, второй вход которого соединен с выходом выходного коммутато ра, первый и второй управляющие входы которого соединены соответственно синверсным и прямым выходами тригге ра, первый и второй информационные входы выходного коммутатора соединены соответственно с прямым и инверсным выходами промежуточного регистра первый и второй входы блока управления соединены соответственно с входом задания длины массива и пуска устройства, -камсцый блок вычисления итерации i содержит два входных ре гйстра, два промежуточных коммутатора и два промежуточных сумматора, причем первый и второй входы каждого промежуточного сумматора соединены соответственно с пряглым выходом соответствующего входного регистра и выходом соответствующего промежуточного коммутатора, первый и второй управляющие входы промежуточных коммутаторов соединены соответственно с инверсным и прямым выходами второго входного регистра, первый и второй информационные аходы первого промежу точного коммутатора соединены соответственно с прямым и инверсным выхо цзмн первого входного регистра, упра ляющие входы первого и второго входных регистров соединены с выходом блока управления, информационные входы первого и второго входных регистров первого блока вычисления итерации соединены соответственно с входом начального значения функции и входом аргумента устройства, выходы первого и второго промежуточных сумматоров К-го блока вычисления итерации (,2...2п-2) соединены с информационными входами соответствен но первого и второго входных регистров (К+1)-го блока вычисления итерации, выходы первого и второго промежуточных сумматоров (2п-1)-го блока вычисления итерации соединены с информационными входами соответственно промежуточного регистра и триггера, управляющие входы которых соединены с выходом блока управления, первый и второй информационные входы второго промежуточного коммутатора К-го блока вычисления итерации соединены с входами задания констант соответственно In (1+2) и 2п (1-2 ) устройства. Блок управления: содержит счетчик, элемент ИЛИ-НЕ, триггер, генератор импульсов и элемент И, выход которого соединен с выходом блока управлений и счетным входом счетчика, информационный вход и выход которого соединены соответственно с первым входом блока управления и входом элемента ИЛИ-НЕ, выход которого соединен с первым входом триггера, второй вход и выход которого соединены соответственно с вторым входом блока управления и первым входом элемента И, второй вход которого соединен с выходом генератора импульсов. На фиг. I дана блок-с5 ема конвейерного устройства на фиг. 2 - схема блока управления. Конвейерное устройство для вычисления функции у е содержит блок 1 вычисления итерации, регистры 2 и 3 входные, коммутато1жл 4 и 5 промежуточные, сумматоры 6 и 7 промежуточные, регистр 8, промежуточный триггер 9, коммутатор 10 выходной, сумматор 11 выходной, регистр 12 выход,иой, блок 13 управления, входы 14 и 15 блока управления и выход 16 блока управления. Блок 13 управления содержит триггер 17, генератор 18 импульсе, J, элемент И 19, счетчик 20- к элемент ИЛИ-НЕ 21. Алгоритм вычисления е описывается следующими итерационными формулами;. V. х,.,, х.-е„(1..1-() .tsicjnx. , 1 I + 1 при i четном; где K(.i) (V) при i нечетном; которые при начальных значениях уо 1, Хо X дают после 2п итераций У1п eJ. Устройство работает следующим образом. в первом также в регистр 2 первого блока 1 записывается константа +1, а в регистр 3 поступает значение операнда х в обратном коде в форме с фиксированной запятой. Если , то 4 г то есть знаковый разряд регистра 3 равен единице. Управлянвдий сигнал, поступающий с прямого выхода

знакового разряда регистра 3/ пропускает через коглмутатор 4 обратное значение содержимого регистра 2, сдвинутое на одни разряд вправо, на сумматор б и через схему коммутатора

5обратное значение кода Sn () 5 на сумматор 7. На сумматоре 6 производится сложение числа +1, хранимого

в регистре 2, с числом, поступающим с коммутатора 4. Поскольку это, число равно -0,1, и поступает в обратном 10 коде, то на выходе сумматора 6 получается число 0,9. На су Фшторе 7 производится сложение обратных кодов операнда х, поступающего из регистра 3, и значения In (1-2), то есть 15 производится вычитание из значения X значения In (,

Если же X О, то 4-1, то есть знаковый разряд регистра 3 равен нулю. Управляющий сигнал, поступаю- 20 1дий с инверсного выхода знакового разр5ща регистра 3, пропускает через коммутатор 4 прямое значение содержимого регистра 2, сдвинутое на один разряд вправо, на сумматор б, 25 и через коммутатор 5 обратное значение кода 2п (1+2) на сумматор 7. На сумматоре 6 число +1, хранимое в регистре 2, cy миpyeтcя с числом, поступающим с коммутатора 4, равным 0,1, то есть формируется число 1,1. На сумматоре 7 производится сложение обратных кодов операнда х, поступающего из регистра 3, и значения Ь (1+2-).

Во втором такте производится за- ло пись результатов вычислений первого блока 1 ао второй: запись полученного на сумматоре б числа регистр.

2второго блока 1 и запись получен- : кого на сумматоре 7 числа в регистр 40

3второго блока 1. Одновременно в регистр 3 первого блока 1 поступает значение второго операнда.

В первом блоке 1 производится выполнение первой итерации над вто- 45 рым операндом, аналогичное выполненной в первом такте над первым операндом, а во втором блоке 1 выполняется вторая итерация над первым операндом. В третьем такте результаты 50 вычислений, полученные во втором блоке 1, записываются в третий блок 1, а результаты первого блока 1 - во второй„ В регистр 3 первого блока 1 поступает третий операнд. В первом « блоке 1 выполняется первая итерация над третьим операндом, во втором вторая итерация над зторым операндом, в третьем - третья итерация над первым операндомf причем в третьем блоке 1 промежуточный результат с коммутатора 5 поступает на сумматор

6со сдвиговым на два разряда вправо, а на сумматор 7 через коммутатор 5 поступают значения In (1+2) или

In (1-2).65

В дальнейшем результаты предыду1ЦИХ блоков поступают в последующие блоки, а в первый блок поступает новый операнд и т.д., причем в каждом нечетном и следующем за ним блоке промежуточные результаты с коммутатора 4 поступают на сумматор б со сдвигом на один разряд вправо большим, чем в предыдущих двух блоках, а в выражениях логарифмов f которые подаются монтажным способом.на коммутатор 5, степень двойки возрастае на единицу.

В 2п-м такте сформированное на сумматоре б (2п-1)-го блока 1 выражение записывается в регистр 8, а содержимое знакового разряда сумматора 7 (2п-1)-го блока 1 переписы.вается в триггер 9, сигналы с прямого и инверсного выходов которого управляют прохождением прямого или инверсного значения регистра 8 чере коммутатор 10 на сумматор 11 со сдвигом на (п-1) разряд.. На сумматоре 11 формируется значение искомо функции от первого операнда. Одновременно результаты обработкой iecex последующих операндов сдвигаются на одну ступень вниз и производится их обработке.

В (2п+1)-м такте на выходном регистре 12 получается первый результат, и в дальнейшем в каждом такте на выходу будет появляться новый результат, то есть результат вычислния функции от первого операнда массива чисел будет получен через 2п тактов, а от каждого последующего операнда массива - через один такт,

Тактовые импульсы, управляющие работой устройства, генерирует блок 13 управления. Устройство работает по конвейерному принципу, поэтому в каждом такте в него можно- вводить новый операнд, а на выходе получать новый результат вычисления. При обработке массивов чисел быстродействие устройства определяется длительностью такта обработки данных, которая равна задержке в одном блоке 1 устройства и определяется выражением .

см ком

где tpM - время суммирования на сум

маторе,

ком задержка информации коммутатором.

Видно, что по быстродействию . предлагаемое устройство значительно превосходит прототип при обработке массивов чисел. Быстродействие повышено в 2,5«п раз.

Креме того, в предлагаемом устройстве нет необходимости хранить константы, количество которых равно 2п , в блоках памяти, поскольку они подаются на кслимутаторы устройства монтажным способом, а также не нужен блок памяти для хранения микропрограмм сложного блока микропроrpaiMMHoro управления, так как управ ление устройством осуществляется от простого блока управления. Формула изобретения 1. Конвейерное устройство для вы числения функции У е , содержащее блок управления, промежуточный регистр и выходной сумматор, первый вход которого соединен с прямым выходом промежуточного регистра, о Фличающееся тем, что, с целью повышения быстродействия, в него введены (2п-1) блоков вычисления итераций (где п - разрядность аргумента) , триггер, выходной коммутатор и выходной регистр, выход которого является выходом устройства, управляющий и информационный входы выходного регистра соединены соответственно с выходом блока управления и выходом выходного сумматора, второй вход которого соединен с выходом выходного коммутатора, первый и второй управляющие входы которого соединены соответственно с ин.версным и прямым выходами триггера, первый и второй информационные входы выходного коммутатора соединены соответственно с прямым и инверсным выходами промежуточного регистра, первый и второй входы блока управления соединены соответ;ственно с входом задания длины массива и пуска устройства, каждый блок вычисления итерации содержит два входных регистра, два промажуточных коммутатора и два промежуточных сумматора, причем первый и второй входы каждого промежуточного сумматора соединены соответственно с прямым выходом соответствующего входного регистра и выходом соотве ствующего промежуточного коммутато ра, первый и второй управляющие входы промежуточных коммутаторов соединены соответственно с инверсньм и прямым выходами второго вход ного регистра, первый и второй информационные входы первого прсмлежу точного коммутатора соединены соответственно с прямым и инверсным выходами первого входного регистра, управляющие входы первого и второго входных регистров соединены с выходом блока управления/ информационные входы первого и второго входных регистров первого Ьлока вычисления итерации соединены соответственно с входом начального значения функции и входом аргумента устройства, выходаа первого и второго промежуточных сумматоров К-го блока вычисления итерации (,2,..,2п-2) соединены с информационными входами соответственно первого и второго входных регистров (К+1)-го блока вычисления итерации, выходы первого и второго промежуточных сумматоров (2п-1)-го блока вычисления итерации соединены с информационными входами соответственно промежуточного регистра и триггера, управляющие входы которых соединены с выходом блока управления, первый и второй информационные входы второго промежуточного коммутатора К-го блока вычисления итерации соединены с входагли задания констант соответственно 2п (1+2-) и 2п (1-2) устройства. 2. Устройство по п.1, о т л и чающееся тем, что блок управ- . ления содержит счетчик, элемент ИЛИ-НЕ, триггер, генератор импульсов и элемент И, выход которого соединен с выходом блока управления и счетным входом счетчика, информационный вход и выход которого соединены соответственно с первым входом блока управления и входом элемента ИЛИ-НЕ, выход которого соединен с первым входом триггера, второй вход и выход .которого соединены соответственно с вторым входом блока управления и первым входом элемента И, второй вход которого соединен с выходом генератора импульсов. Источн жи информации, принятые во внимание при экспертизе 1,Авторское свидетельство СССР №631924, кл. G 06 F 7/556, 1978. 2.Байков В.Д., Смолов В.Б. Аппаратурная реализация элементарных функций в УВМ. Из-во Ленинградского университета, 1975.

/J

/Л

го I

| название | год | авторы | номер документа |

|---|---|---|---|

| Конвейерное устройство для вычисления функции @ = @ | 1981 |

|

SU964635A1 |

| Конвейерное устройство для вычисления функций синуса и косинуса | 1981 |

|

SU1003080A1 |

| Конвейерное устройство для вычисления гиперболических функций | 1981 |

|

SU1026141A1 |

| Устройство для вычисления функции @ = @ | 1982 |

|

SU1062693A1 |

| Устройство для вычисления функции @ = @ | 1982 |

|

SU1034033A1 |

| Конвейерное устройство для вычисления логарифмической и экспоненциальной функций | 1982 |

|

SU1027722A1 |

| Устройство для логарифмирования | 1981 |

|

SU962926A1 |

| Устройство для вычисления функций | 1989 |

|

SU1705822A1 |

| Устройство для вычисления тригонометрических функций | 1984 |

|

SU1166103A1 |

| Устройство для деления | 1981 |

|

SU987621A1 |

/5

-

/5

Авторы

Даты

1982-09-30—Публикация

1981-02-12—Подача