Изобретение относится к технике передачи цифровой информации и может быть использовано для сокращения времени на передачу сообщений в устройствах помехозащитенной передачи двоичной информации.

Известно устройство для передачи и приема двоичных сигналов, содержащее на передающей стороне распределитель импулъсрв, источник сигналов, генератор, модулятор, блок управления и блок синхронизации, а на приемной стороне распределитель импульсов, элементы И, НЕ tilНедостаток известного устройства значительное время передачи и приема информации, обусловленное необходимостью двукратной передачи всех двоичных сигналов кодовых последовательностей .. .

Наиболее близким к предлагаемому по технической сущности является устройство для передачи и приема двоич ных сигналов, содержащее на передающей стороне источник информации, выход которого подключен к входу информационного регистра, выходы которого срединены с соответствующими первыми входами первой группы элементов И, выходы которых подключены

к входам первого элемента ИЛИ, выход первого элемента ИЛИ соединен с первым входом модулятора, к второму входу которого подключен выход второго элемента ИЛИ, генератор,выход которого соединен с третьим входом модулятора и с входом блока управ ления, выходы которого подключены к входам распределителя импульсов,

10 выходы распределителя импульсов соединены с вторыми входами первой группы элементов И и с входами второго элемента ИЛИ, выход модулятора через линию связи на приемной стороне

15 подключен через демодулятор к входу блока синхронизации и управления и. к первым входам регистра памяти, аыходы блока синхронизации и .управления соединены с входами распредели20теля импульсов, первые выхода кото-° рого подключены к соответствующим вторым входам регистра памяти, первые выходы регистра памяти соединены с первыми входами элемента срав25нения кодов, втоЕяле регистра памяти подключены к входам первых элементов НЕ и к первым входам элементов И, выходы которых соединены с информационными выходами

0 устройства, выход элемента сравнения

кодов соединен с вторыми-входами первых элементов И и через второй элемент НЕ с первым входом второго элемента И, к второму входу которого подключен первый выход распределителя импульсов, выход второго элемента И соединен с дополнительным выкодом устройства 2 .

Недостатком известного устройства является его низкая информативность.

Цель изобретения - повышение информативности путем сокращения времени повторной передачи сигналов.

Поставленная цель достигается тем, что в устройство для передачи и приема двоичных сигналов, содержащее на передающей стороне источник информации, выход которого подключен к входу информационного регистра, выходы которого соединены с соответствующими первыми входами первой группы элементов И,выходы которых под;ключены к входам первого элемента ИЛИ, выход первого элемента ИЛИ соединен с рервым входом модулятора, к второму входу которого подключен выход элемента ИЛИ, генератор, выход которого соединен с третьим входом модулятора и с входом блока управления, выходы которого подключены к входа1М распределителя импульсов, выходы распределителя импульсов соединены с вторыми входами первой группы элементов И и с входами второго элемента ИЛИ. выход модулятора через линию связи на приемной стороне подключен через демодулятор к входу блока синхронизации и управления и к первым входам регистра памяти, выходы блока синхронизации и управления соединены с входами распределителя (импульсов, первые выходы которого подключены к соответствующим вторым входам регистра памяти, первые выходы регистра памяти соединены с первыми входами элемента сравнения кодов , вторые выходы регистра памяти подключены к входам первых элементов НЕ и к первым входам первых элементов И, выходы которых соединены с информационными выходами устройства, выход элемента сравнения кодов соединен с вторыми входами первых элементов И и через второй элемент НЕ с первым входом второго элемента И, к второму входу которого подключен первый выход распределителя импульсов; выход второго элемента И соединен с дополнительным выходом устройства, на передающей стороне в устройство введены двоичные сумматоры, первые ч, вторые входы кото- рых соединены с соответствующими выходс1ми информационного регистра, входы переноса младшего разряда двоичных сумматоров подключены к нулевому выводу источника;питания, выходы двоичных сумматоров соединены с соответствующими третьими входами первой группы элементов И, на приемной стороне введены двоичные сумматоры, первые входы которых подключены к соответствующим выходам регистра памяти, к,вторым входам двоичных сумматоров подключены вы:ходы соответствующих первых элементов НЕ, входы переноса младшего разряда двоичного сумматора соединены с положительным выводом источника питания, выходы двоичных сумматоров подключены к соответствующим вторым входам элемента сравнения и к .соответству ощим четвертым входам первых элементов И.

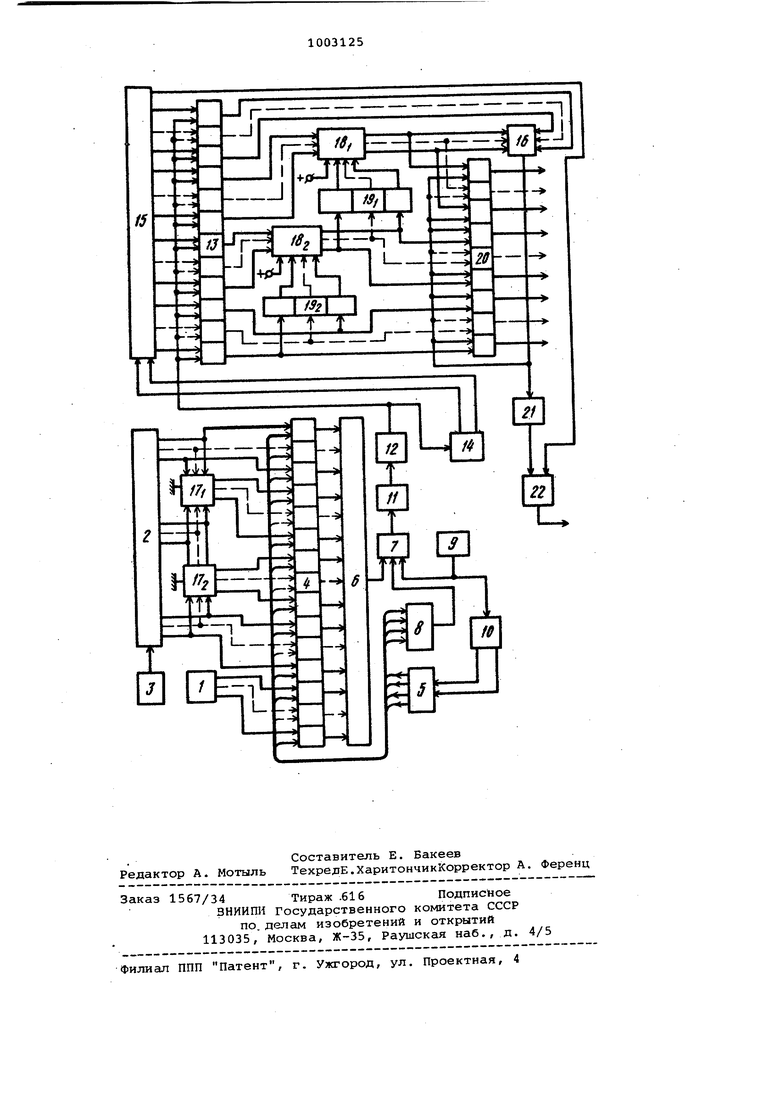

На чертеже схематично изображено устройство.

Устройство для передачи и приема двоичных сигналов содержит на передающей стороне регистр 1 памяти, информационный регистр 2, источник 3 информации, первую группу элементов И 4, распределитель 5 импульсов, первый элемент ИЛИ 6, модулятор 7, второй элемент ИЛИ 8, .генератор 9, блок 10 управления, линию 11 связи, на приемной стороне демодулятор 12, регистр 13 памяти, блок 14 синхронизации и управления, распределитель 15 импульсов, элемент 16 сравнения ко.дов, двоичные сумматоры 17 - 170 и 18 - 189 f первые элементы НЕ I9jj 192/ первые элементы И 20, второй элемент НЕ 21 и второй элемент И 22

Устройство для передачи и приема двоичных сигналов работает следуняцим образом.

Записанная в передающий регистр 2 памяти информации кодовая последовательность делится на кодовые слова, содержащие одинаковое число разрядов. Для определенности положим, что длина каждого кодового слова равна одному байту. Это деление является условным и может быть изменено как в сторону удлинения, так и в сторону укорочения кодовых слов Пусть требуется передать кодовое сообщение, содержащее К-3 байта информации. Для примера запишем их произвольно

. 110011101 10011001 01011011

В первом двоичном сумматоре 17 происходит сложение первого байта с вторым

11001101 10011001 1.01100110

Во втором двоичном сумматоре 18 происходит сложение второго и третьго байтов информации

10011001

01011011

0.11110100

При сложении первых двух байтов информации .возникает единица девятого разряда, учитывать и передавать ее нет необходимости, так как на

приемной стороне для восстановления сообщения эта единица не нужна. При этом сохраняется байтовая структура кодовых слов.

Таким образом, при необходимости передачи К байтовинформации по предлагаемому способу после суммирования смежных байтов получается дополнительный байт, в результате чего подготовленная к передаче информация содержит К + 1 байт. Эта информация

.ПОДВОДИТСЯ на первые входы первой группы элементов И 4, причем первый и последний байты подводятся без каких-либо преобразований

11001101 01100110 11110100 01011011 По команде/ поступающей с первого блока 10 управления, запускается передающий распределитель 5 иглпульсов и на второй вход модулятора 7 с второго элемента ИЛИ 8 последовательно поступают код синхронизации, код начала и приведенные четыре байта информации. Через линию 11 связи переданное сообщение поступает на демодулятор 12, с выхода которого поступает на блок 14 синхронизации, и управления, чем обеспечивается его синхронная работа. После прихода кода начала сигнал с выхода блока 10 управления фазирует делитель частоты и обеспечивает полачу тактовых импульсов на вход распределителя 15 импульсов. Принятые 1етыре байта информации записаны в регистре 13 памяти, с выхода которого первый байт поступает без преобразований на первые входы элементов И 20 и через первую группу элементов НЕ 19 на первые входы двоичного сумматора 18., на вторые разрядные входы которого поступает второй байт информации. На входы перенос младшего разряда двоичных сумматоров 18 подается сигнал 1. Таким образом, на выходе первого из двоичных сумматоров 18., образуется байт информации, представляющий второе кодовое слово

01100110

00110010

1

10011001

Сопоставляя его, видим, что он в точности равен второму байту, подлежащему передаче. Информация этого байта с выхода первого суглматора 18 поступает на первые входы группы элементов И 20 и одновременно через группу элементов НЕ 192 первые входы двоичного сумматора 182/ вторые входы которого поступает третий байт принятого ообщения. Байт информации, получаемый на выходе двоичного сумматора182, равен следующей величине:

01100110 11110100

1

1.01011011

Так как девятый разряд полученно0 го кода не учитывается, то полученный байт информации в точности соответствует байту, подлежащему передаче и переданному последним четвертым. С выходов сумматора 182 е байт подается на первые входы группы элементов И 20 и одновременно на первые входы элемента 16 сравнения кодов, на вторые входы которого подводится такой же четвертый байт с выходов приемного регистра памяти. 0 в результате сравнения кодов на выходе элемента .16 сравнения кодов образуется сигнал 1. Этот сигнал поступает на вторые входы группы элементов И 20 и на выходах этих эле ментов образуются три неискаженных байта информации, т.е. три кодовых I слова. При .возникновении одной или многих ошибок последний байт информации, полученный вычитанием на выходе сумматора 182/ ® совпадет ,с последним переданным байтом информации и на выходе элемента 16 сравнения кодов сигнал сохраняется равным О, который, инвертируясь. 5 элементом НЕ 21/ поступает в виде сигнала 1 на первый вход элемента И 22, на второй вход которого поступает сигнсш 1 с дополнительного выхода приемного распределителя 15 0 импульсов, в результате чего на

выходе элемента И 22 возникает сигнал 1 - запрос на повторную передачу.

Предлагаемый способ передачи 5 двоичной информации с защитой

от помех по помехоустойчивости эквивалентен известному способу передачи двоичной информации с повторением каждого кодового слова. Применение его для передачи К кодовых

0 слов (байтов) информации позволяет сократить время передачи, на величину К - 1/Т/с), где Т - время передачи . одного кодового слова (байта информации ). В предлагаемом устройстве,

5 как и в известном, к 1ждое кодовое слово повторяется дважда, что легко видеть при буквеннс обозначении кодовых слов. Обозначим три кодовых слова, подлёжсицих, передаче, 0 буквами а, Ь и с . в действительности, по предлагаемому способу передаются а,(а + Ь) /СЬ+с) ,с , откуда видно/ что каждое передаваемое слово повторяется дважды. При этом число |Ь5 разрядов предстсшленных здесь сумм/ полученных после сложения кодовых слов, не увеличивается, так как нет необходимости учитывать единицу старшего разряда. При передаче этой информации, как обЕЛчно, может быть применена зеодита по паритету. При передаче информации предлагаемым устройством, так же как и известным, сшибка не обнаруживается, если искажения происходят в одних и тех же разрядах, переданных смежным бай том..При этом ошибочно будет принято только одно кодовое слово. Таким образом, основное преимущество предлагаемого устройства передачи двоичных сигналов с защито от помех заключается в сокращении времени на передачу информации по сравнению с известным. Аппаратурная реализация предлага емого устройства значительно проще, а кодирование и декодирование сообщений осуществляется в статическом режиме, в отличие от кодирования и декодирования циклических кодов, осуществляемого в динамике с исполь зованием регистров сдвига. При расринхронизации приемного и передающе распределителей импульсов, в отличи Ьт передачи информации с использова нием циклического кода, в предлагаемом способе ошибка всегда будет обнаружена. Формула изобретения Устройство для передачи и приема двоичных сигналов, содержащее на пе редающей стороне источник информации выход которого подключен к входу ИИ формационного регистра, выходы кото рого соединены с соответствующими первыми входами первой группы элементов И, выхода которых подключены к входсц первого элемента ИЛИ, выход первого элемента ИЛИ соединен с пер вым входом модулятора, к второму вхо ду которого подключен выход второго элемента ИЛИ, генератор, выход которого соединен с третьим входом модулятора и с входом блока управления, выходы которого подключены к анодам распределителя импульсов, выходы рас пределителя импульсов соединены с втор|ыми входами первой группы элемен тов И и с входами второго элемента ИЛИ, выход модулятора через линию связи на приемной стороне подключен через демодулятор к входу блока синхронизации и управления и к первым входам регистра памяти, выходы блока синхронизации и управления соединены с входами распределителя импульсов, первые выходы которого подключены к соответствукнцим вторым входам регистра памяти, первые выходы регистра памяти соединены с первыми входами элемента сравнения кодов, BTop&je выходы регистра памяти подключены к входам первых элементов НЕ и к первым входам первых элементов И, выходы которнлх соединены с инфо1.1ационными выходами устройства, выход элемента сравнения кодов соединен с вторыми входами первых элементов И и через второй элемент НЕ с первым входом второго элемента И, к второму входу которого подключен первый выход распределителя импульсов, выход второго элемента И соединен с дополнительным выходом устройства, отличающееся тем, что, с целью повышения информативности путем сокращения времени повторной передачи сигналов, в устройство на передающей стороне введены двоичные сумматоры, первые и вторые входы которых соединены с соотззетствующими выходами информационного регистра, входы переноса младшего разряда двоичных сумматоров подклю.чены к нулевому выводу источника питания, выходы двоичных сумматоров соединены с соответствующими третьими входами первой группы элементов И, на приемной стороне введены двоичные |сумматоры, первые входы которых подключены к соответствующим выходам регистра пг1мяти, к вторым входам двоичных сумматоров подключены выходы соответствующих первых элементов НЕ, входы переноса младшего разряда двоичных сумматоров соединены с положительным выводом источника питания, выходы двоичных сукматоров подключены к соответствующим вторым входам элемента сравнения кодов и к соответствующим четвертым входам первых элементов И, Источники информации, принятые во внимание при экспертизе 1.Патент США 4070648, кл.Q 08 С 25/02, опублик. 1978. 2,ТЬиеничников A.M. и Портнов М.Л. Телемеханические системы на интег 5альных микросхемах. М., Энергия, 1977, с. 169-172 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальная кодоимпульсная система телесигнализации | 1986 |

|

SU1325544A1 |

| Способ многодорожечной цифровой магнитной записи и устройство для его осуществления | 1990 |

|

SU1732380A1 |

| Система для передачи и приема дискретной информации | 1979 |

|

SU903850A1 |

| Коррелятор | 1986 |

|

SU1339584A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| СПОСОБ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ ДАННЫХ ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА И ДЕКОДЕР ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА | 1994 |

|

RU2108667C1 |

| СПОСОБ ПЕРЕДАЧИ ИНФОРМАЦИИ В СИСТЕМАХ С КОДОВЫМ РАЗДЕЛЕНИЕМ КАНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2001 |

|

RU2234191C2 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| Способ многодорожечной цифровой магнитной записи и устройство для его осуществления | 1988 |

|

SU1606996A1 |

| Система для передачи и приема цифровой информации | 1989 |

|

SU1637025A1 |

Авторы

Даты

1983-03-07—Публикация

1981-04-24—Подача