Изобретение относится к цифровой электроизмерительной технике и предназначено для аппаратурного определения в масштабе реального времени кор- реляционной функции с симметричными разнополярными сдвигами случайных процессов.

Цель изобретения - расширение частотного диапазона обрабатываемых сиг- ю торые являются входами дельта-модуляторов 3 и 4. Дельта-кодовые последовательности с выходов дельта-модуляторов 3 .и 4 поступают на входы одноразрядных регистров 5 и 6 сдвига.

налов.

Сущность изобретения заключается в том что входные величины, подаваемые на цифровую часть коррелятора, представлены в виде т-разрядного дво- 15 Под действием переднего фронта каждо- ичного кода и одноразрядной дельта- го импульса, поступающего с первого кодовой последовательности с частота- выхода блока 15, в регистрах 5 и 6 ми дискретизации, равными частоте сдвига происходит сдвиг дельта-ко- дискретизации при импульсно-кодовой довой двоичной последовательности, модуляции и частоте дискретизации при 20 Число выходов блоков 5 и 6 равно чисдельта-модуляции соответственно.

При этом операция умножения заменяется -простой логической операцией

лу сдвигов корреляционной функции одной полярности р. Длина регистров 5 и 6 равна , где /х Т /Т ; Т и Т - соответственно частоты дискр

Исключшощее ШШ с отрицанием знако- 25 тизации при дельта-модуляции и им- вых битов (старших разрядов) многоразрядного двоичного кода и одноразрядной дельта-кодовой последовательности, а традиционный умножитель многоразрядных отсчетов - схемой ИСК11Ю- 30 ЧАЮЩЕЕ ИЛИ-НЕ. Это существенно повышает быстродействие схемы коррелятора в целом.

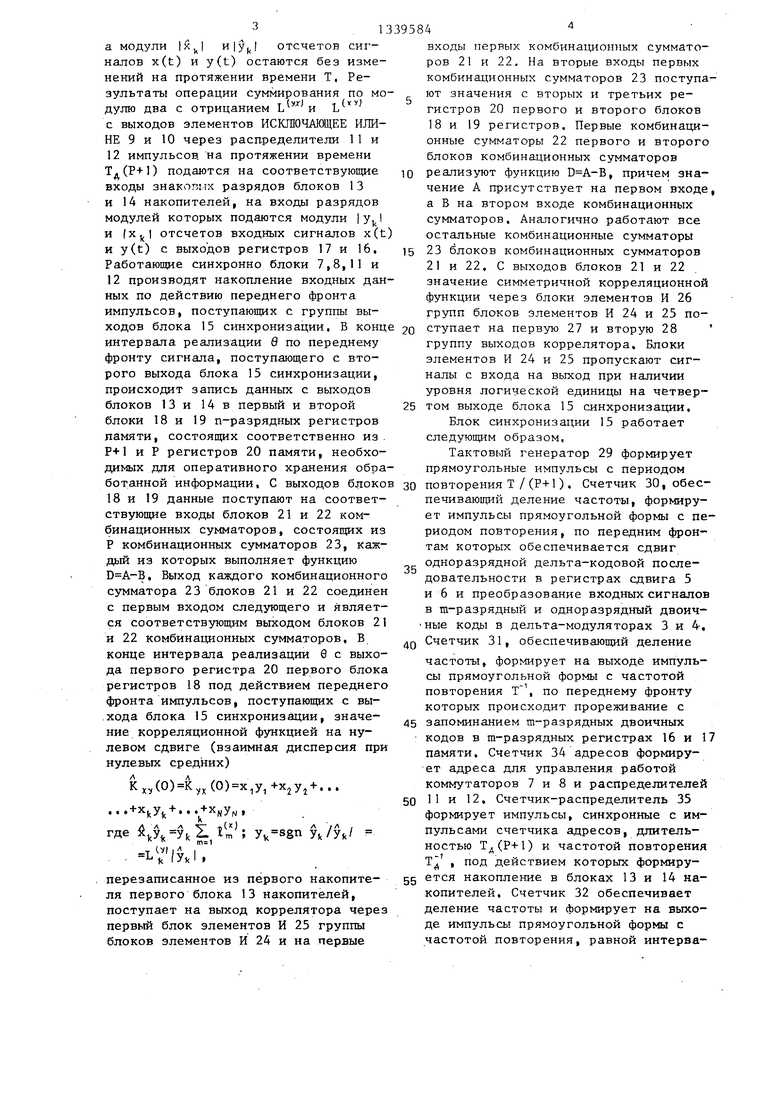

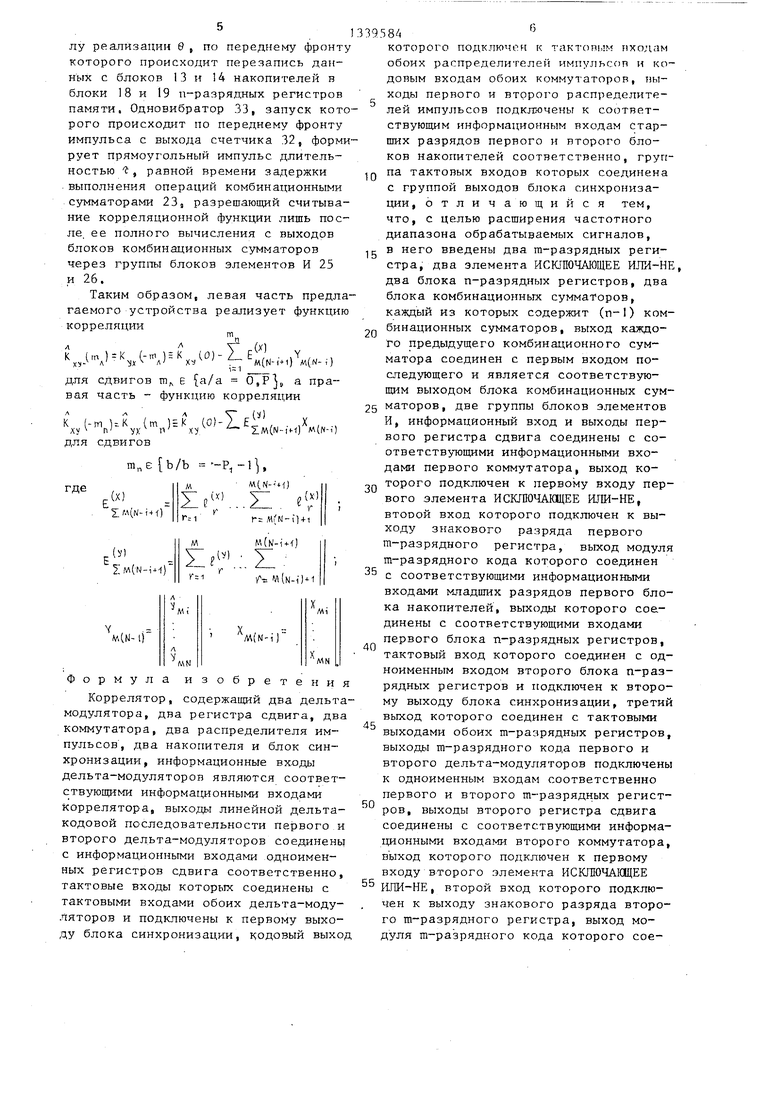

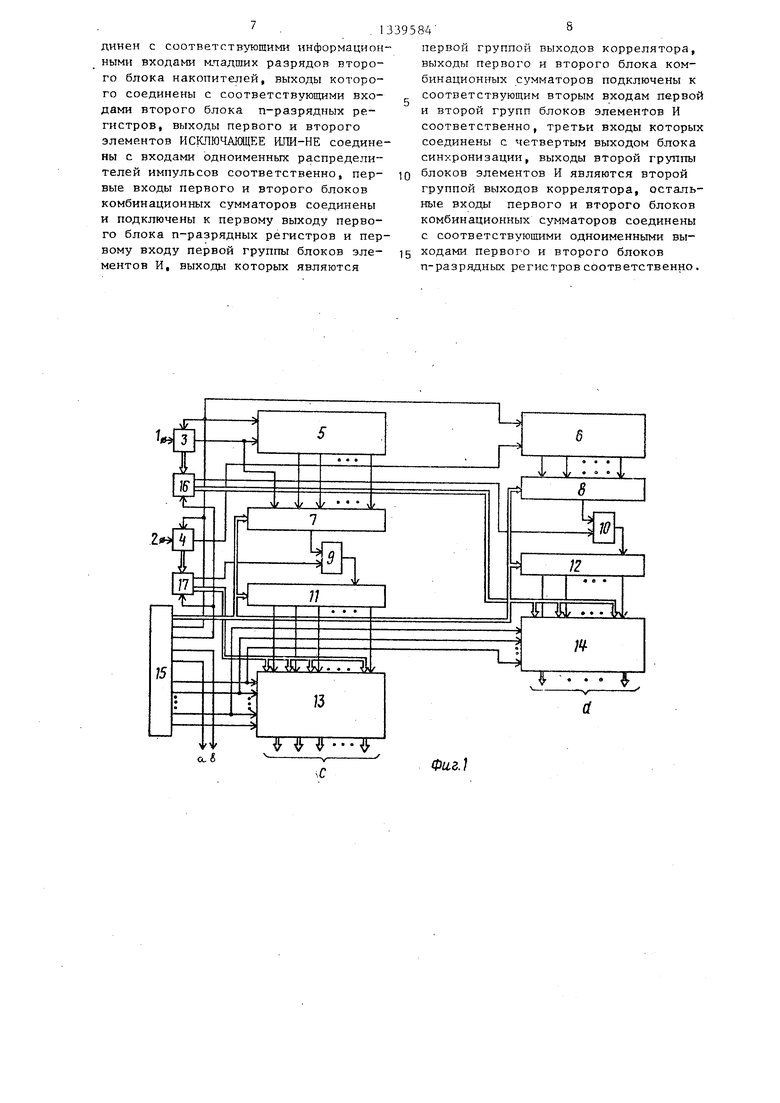

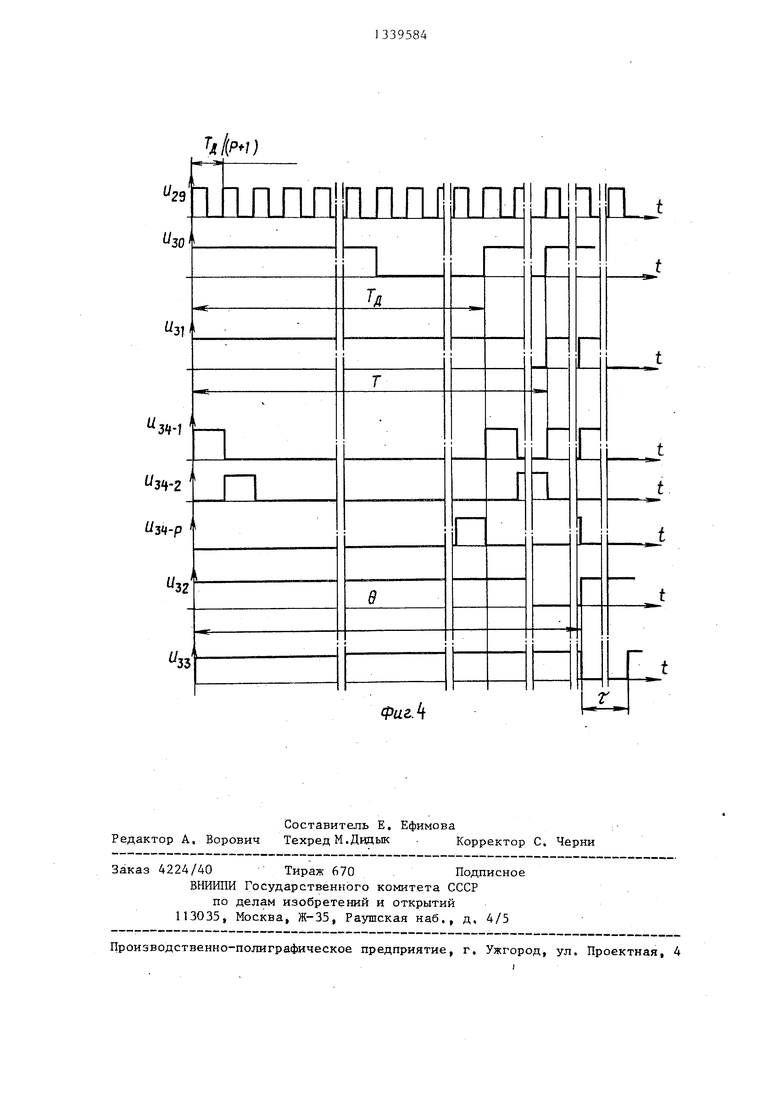

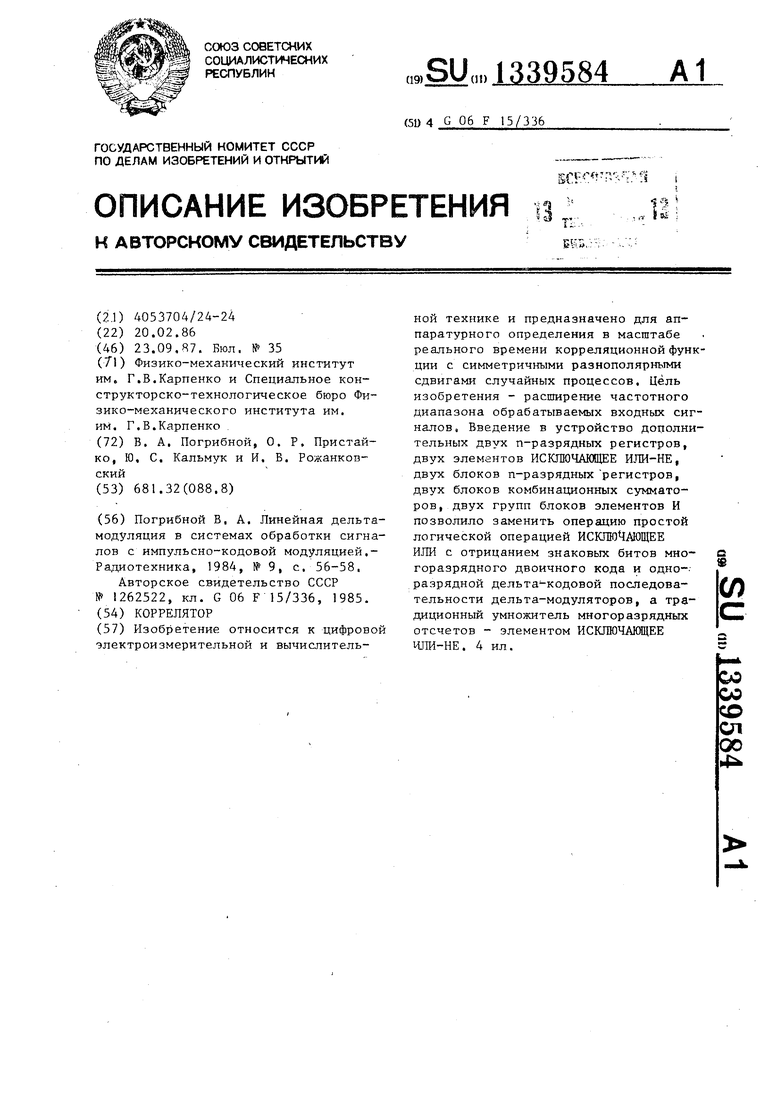

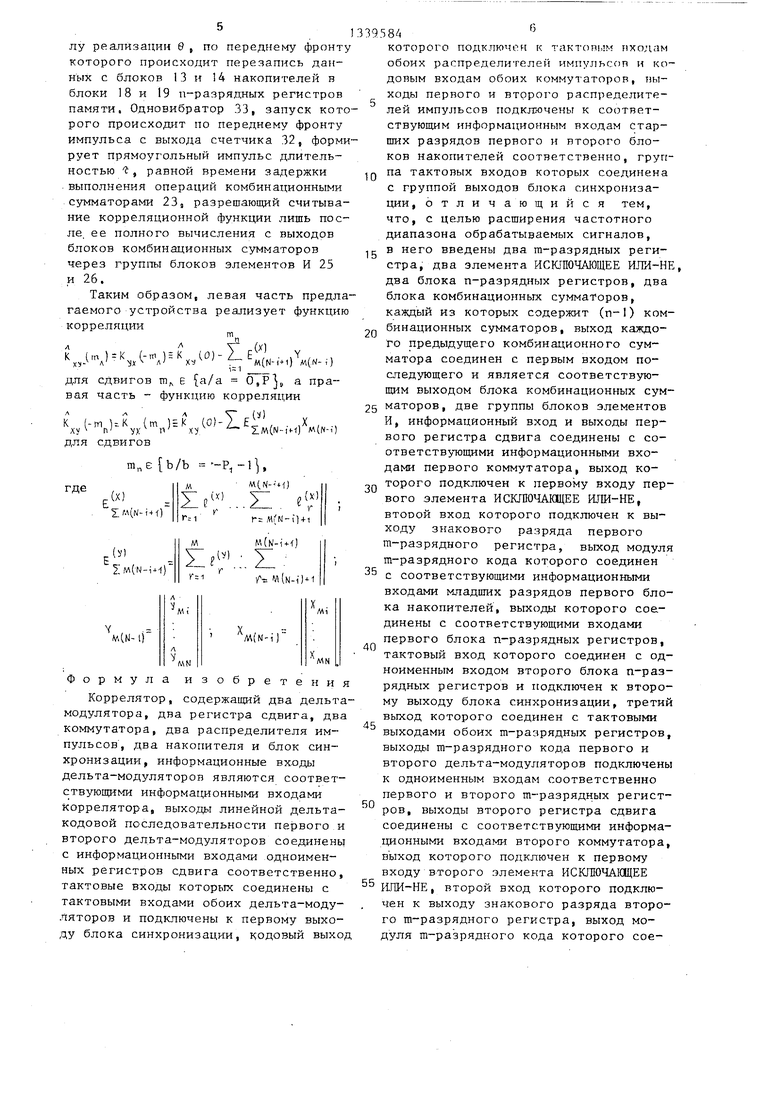

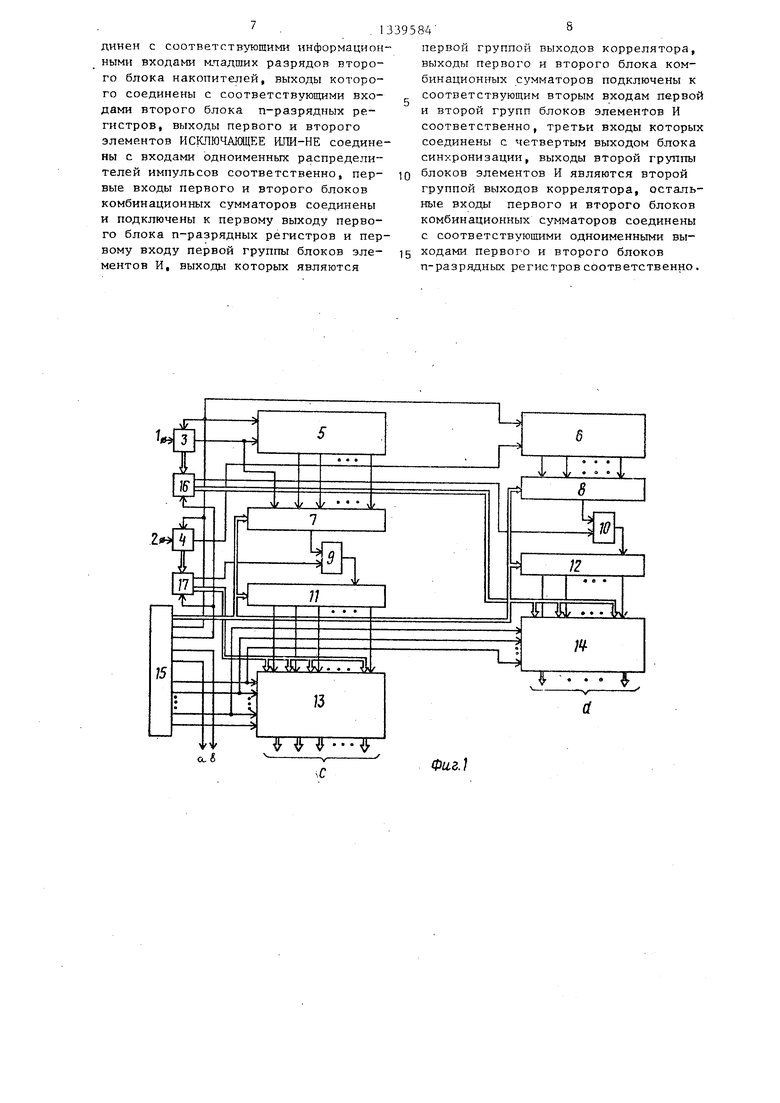

На фиг. 1 и 2 изображена, структур- 35 ная схема коррелятора; на фиг. 3 - схема блока синхронизации; на фиг, 4 - диаграмма работы блока синхронизации.

Коррелятор содержит первый 1 и второй 2 информационные входы, пер- 40 вый 3 и второй 4 дельта-модуляторы, первый 5 и второй 6 регистры сдвигар первый 7 и второй 8 коммутаторы, первый 9 и второй 10 элементы ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ, первый 11 и второй 12 45 распределители импульсов, первый 13 и второй 14 блоки накопителей, блок 15 синхронизации, первый 16 и второй 17 т-разрядные регистры, первый 18 и второй 19 блоки п-разрядных регист- 50 ров в виде регистров 20, первый 21 и второй 22 блоки комбинационных сумматоров в виде комбинационных сумматоров 23, первую 24 и вторую 25 группы блоков элементов И в виде бло- gg ков элементов И 26, первую 27 и вторую 28 группу выходов коррелятора.

Блок синхронизации (фиг. 3) содержит генератор 29 тактовых импульсов.

пульсно-кодовои модуляции.

Отсчеты входных сигналов x(t) и y(t) с выходов дельта-модуляторов 3 и 4 в виде т-разрядных двоичных код представленных модуляторами | х и у fj и битами знаков Ь . L, по ступают на входы т-разрядных регис ров 16 и 17 памяти. Блоки 16 и 17 обеспечивают прореживание и запомин ние на время Т, равное периоду дискретизации при импульсно-кодовой мо дуляции, указанных оцифрованных отсчетов, под воздействием переднего фронта импульсов, поступающих с тре тьего выхода блока 15 синхронизации С выходов т-разрядных регистров 16 17 памяти биты знаков (старшие разр ды) L j, и L отсчетов входных сигналов x(t) и y(t) поступают на вторые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ 10 и 9 соответственно, на пе вые входы которых через коммутаторы 8 и 7 на протяжении времени Т(Р+1) поступают дельта-кодовые последовательности с выходов регистров 6 и 5 сдвигов. Таким образом, умножение реализовано как суммирование по мо дулю два с отрицанием на элементах ИСЮБОЧА10ЩЕЕ ИЛИ-НЕ 9 и 10 знаковых битов (старших разрядов) т-разрядны двоичных кодов и одноразрядных линейных дельта-кодовых последовател ностей

(xv)

1/;; ; © LV,

первый счетчик 30, BTcipoii счетчик 41, третий счетчик 32, однонибрлтор 33, счетчик 34 адресов, четвертый счетчик-распределитель 35.

Коррелятор работает апедующим образом.

Входные сигналы x(t) и y(t) подаются на входы 1 и 2 коррелятора, коляторов 3 и 4. Дельта-кодовые последовательности с выходов дельта-модуляторов 3 .и 4 поступают на входы одноразрядных регистров 5 и 6 сдвига.

Под действием переднего фронта каждо- го импульса, поступающего с первого выхода блока 15, в регистрах 5 и 6 сдвига происходит сдвиг дельта-ко- довой двоичной последовательности, Число выходов блоков 5 и 6 равно числу сдвигов корреляционной функции одной полярности р. Длина регистров 5 и 6 равна , где /х Т /Т ; Т и Т - соответственно частоты дискретизации при дельта-модуляции и им-

пульсно-кодовои модуляции.

Отсчеты входных сигналов x(t) и y(t) с выходов дельта-модуляторов 3 и 4 в виде т-разрядных двоичных кодо представленных модуляторами | х и у fj и битами знаков Ь . L, поступают на входы т-разрядных регистров 16 и 17 памяти. Блоки 16 и 17 обеспечивают прореживание и запоминание на время Т, равное периоду дискретизации при импульсно-кодовой модуляции, указанных оцифрованных отсчетов, под воздействием переднего- фронта импульсов, поступающих с третьего выхода блока 15 синхронизации. С выходов т-разрядных регистров 16 и 17 памяти биты знаков (старшие разряды) L j, и L отсчетов входных сигналов x(t) и y(t) поступают на вторые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ 10 и 9 соответственно, на первые входы которых через коммутаторы 8 и 7 на протяжении времени Т(Р+1) поступают дельта-кодовые последовательности с выходов регистров 6 и 5 сдвигов. Таким образом, умножение реализовано как суммирование по модулю два с отрицанием на элементах ИСЮБОЧА10ЩЕЕ ИЛИ-НЕ 9 и 10 знаковых битов (старших разрядов) т-разрядных двоичных кодов и одноразрядных линейных дельта-кодовых последовательностей

(xv)

1/;; ; © LV,

а модули и|у отсчетов сигналов x(t) и y(t) остаются без изменений на протяжении времени Т, Результаты операции суммирования по модулю два с отрицанием L и L с выходов элементов ИСКЛЮЧАЩЕЕ ИЛИ- НЕ 9 и 10 через распределители 11 и 12 импульсов, на протяжении времени Тд(Р+1) подаются на соответствующие входы знаковых разрядов блоков 13 и 14 накопителей, на входы разрядов модулей которых подаются модули и ( отсчетов входных сигналов x(t) и y(t) с выходов регистров 17 и 16, Работающие синхронно блоки 7,8,11 и 12 производят накопление входных данных по действию переднего фронта импульсов, поступающих с группы выходов блока 15 синхронизации, В конц интервала реализации б по переднему фронту сигнала, поступающего с второго выхода блока 15 синхронизации, происходит запись данных с выходов блоков 13 и 14 в первый и второй блоки 18 и 19 п-разрядных регистров памяти, состоящих соответственно из. Р-И и Р регистров 20 памяти, необходимых для оперативного хранения обработанной информации, С выходов блоко 18 и 19 данные поступают на соответствующие входы блоков 21 и 22 комбинационных сумматоров, состоящих из Р комбинационных сумматоров 23, каждый из которых выполняет функцию , Выход каждого комбинационного сумматора 23 блоков 21 и 22 соединен с первым входом следующего и является соответствующим выходом блоков 21 и 22 комбинационных сумматоров, В конце интервала реализации 9 с выхода первого регистра 20 первого блока регистров 18 под действием переднего фронта импульсов, поступающих с вы- .хода блока 15 синхронизации, значение корреляционной функцией на нулевом сдвиге (взаимная дисперсия при нулевых средних)

К ,,(0)К„ (0) +Х2У + , ,,

,У +

где . ,/,/

- . L, i,rr

перезаписанное из первого накопителя первого блока 13 накопителей, поступает на выход коррелятора через первый блок элементов И 25 группы блоков элементов И 24 и на первые

входы первых комбинационных сумматоров 21 и 22. На вторые входы первых комбинационных сумматоров 23 поступают значения с вторых и третьих регистров 20 первого и второго блоков 18 и 19 регистров. Первые комбинационные сумматоры 22 первого и второго блоков комбинационных сумматоров

реализуют функцию , причем значение А присутствует на первом входе, а В на втором входе комбинационных сумматоров. Аналогично работают все остальные комбинационные сумматоры

5 23 блоков комбинационных сумматоров 21 и 22, С выходов блоков 21 и 22 значение симметричной корреляционной функции через блоки элементов И 26 групп блоков элементов И 24 и 25 по0 ступает на первую 27 и вторую 28 группу выходов коррелятора. Блоки элементов И 24 и 25 пропускают сигналы с входа на выход при наличии уровня логической единицы на четвер5 том выходе блока 15 синхронизации. Блок синхронизации 15 работает следующим образом,

Тактовый генератор 29 формирует прямоугольные импульсы с периодом

0 повторения Т/(Р+1), Счетчик 30, обеспечивающий деление частоты, формирует импульсы прямоугольной формы с периодом повторения, по передним фронтам которых обеспечивается сдвиг одноразрядной дельта-кодовой последовательности в регистрах сдвига 5 и 6 и преобразование входных сигналов в т-разрядный и одноразрядный двоич- ные коды в дельта-модуляторах 3 и 4,

Q Счетчик 31, обеспечивающий деление

частоты, формирует на выходе импульсы прямоугольной формы с частотой повторения Т , по переднему фронту которых происходит прореживание с

5 запоминанием т-разрядных двоичных : кодов в т-разрядных регистрах 16 и 17 памяти. Счетчик 34 адресов формирует адреса для управления работой коммутаторов 7 и 8 и распределителей

0 11 и 12, Счетчик-распределитель 35 формирует импульсы, синхронные с импульсами счетчика адресов, длительностью Т,(Р+1) и частотой повторения

1 . Тд , под действием которых формиру-

5 ется накопление в блоках 13 и 14 накопителей. Счетчик 32 обеспечивает деление частоты и формирует на выходе импульсы прямоугольной формы с частотой повторения, равной интервалу реализации в , по передне1 у фронт которого происходит перезапись данных с блоков 13 и 14 накопителей в блоки 18 и 19 п-разрядных регистров памяти. Одновибратор 33, запуск котрого происходит по переднему фронту импульса с выхода счетчика 32, формрует прямоугольный импульс длительностью , равной времени задержки выполнения операций комбинационными сумматорами 23, разрешающий считывание корреляционной функции лишь после, ее полного вычисления с выходов блоков комбинационных сумматоров через группы блоков элементов И 25 и 26.

Таким образом, левая часть предлгаемого устройства реализует функци корреляции

п

(X)

, .. I: N I U) - / С Х Л

1- 1

ДЛЯ сдвигов т Е а/а 0, а правая часть - функцию корреляции

ллл ()

.,(N-,ч/(.ч,

для

К (in

Х51 К.

,(-.MHK(o)-i:E;7,.,,,,v.-)

сдвигов

т„е Ь/Ъ -Р

где

Лх)

(

(V)

2. wCN-i + l)

М

ч.

МИ- М)

Г-1

,lv) г

П г

Г M W-i l + i M(N -i + l)

Z

1 A(N-i)1

M;

Mi

Y

M(W-lj

M(N

MM

и

MN

Формула изобретения Коррелятор, содержащий два дельта модулятора, два регистра сдвига, два коммутатора, два распределителя импульсов, два накопителя и блок синхронизации, информационные входы дельта-модуляторов являются соответствующими информагщонными входами коррелятора, выходы линейной дельта- кодовой последовательности первого и второго дельта-модуляторов соединены с информационными входами одноименных регистров сдвига соответственно, тактовые входы которых соединены с тактовыми входами обоих дельта-модуляторов и подключены к первому выходу блока синхронизации, кодовый выход

10

15

20

39584

которого подключен к тактовым т)ходам

обоих распределителей импульсоп и кодовым входам обоих коммутаторов, Т)Ы- ходы первого и второго распределителей импульсов подключены к соответствующим информационным входам старших разрядов первого и второго блоков накопителей соответственно, группа тактовых входов которых соединена с группой выходов блока синхронизации, 6 тли ч ающий с я тем, что, с целью расширения частотного диапазона обрабатываемых сигналов, в него введены два га-разрядных регистра, два элемента ИСКГПОЧАЮЩЕЕ ИЛИ-НЕ, два блока п-разрядных регистров, два блока комбинационных сумматоров, каждый из которых содержит (п-1) комбинационных сумматоров, выход каждого предыдущего комбинационного сумматора соединен с первым входом последующего и является соответствующим выходом блока комбинационных сум25 маторов, две группы блоков элементов И, информационный вход и выходы первого регистра сдвига соединены с соответствующими информационными входами первого коммутатора, выход которого подключен к первому входу первого элемента ИСКЛЮЧАЩЕЕ ИЛИ-НЕ, втооой вход которого подключен к выходу знакового разряда первого т-разрядного регистра, выход модуля т-разрядного кода которого соединен с соответствующими информационны ш входами младщих разрядов первого блока накопителей, выходы которого соединены с соответствующими входами первого блока п-разрядных регистров, тактовый вход которого соединен с одноименным входом второго блока п-разрядных регистров и подключен к второму выходу блока синхронизации, третий выход которого соединен с тактовыми выходами обоих га-разрядных регистров, выходы га-разрядного кода первого и второго дельта-модуляторов подключены к одноименным входам соответственно первого и второго га-разрядных регистров, выходы второго регистра сдвига соединены с соответствующими информационными входами второго коммутатора, выход которого подключен к первому входу второго элемента ИСКЛЮЧАЮЩЕЕ

11ЯИ-НЕ, второй вход которого подключен к выходу знакового разряда второго га-разрядного регистра, выход модуля га-разрядного кода которого сое30

35

40

45

50

динен с соответствующими информациоН ными входами младших разрядов второго блока накопителей, выходы которого соединены с соответствующими входами второго блока п-разрядных регистров, выходы первого и второго элементов ИСКЛЮЧАЩЕЕ 11ЛИ-НЕ соедине ны с входами одноименных распределителей импульсов соответственно, первые входы первого и второго блоков комбинационных сумматоров соединены и подключены к первому выходу первого блока п-разрядных регистров и пер вому входу первой группы блоков элементов И, выходы которых являются

4 °

первой группой выходов коррелятора, выходы первого и второго блока комбинационных сумматоров подключены к соответствующим вторым входам первой и второй групп блоков элементов И соответственно, третьи входы которых

соединены с четвертым выходом блока синхронизации, выходы второй группы блоков элементов И являются второй группой выходов коррелятора, остапь- ные входы первого и второго блоков комбинационных сумматоров соединены с соответствующими одноименными выходами первого и второго блоков

п-разрядных регистров соответственно.

И-р rfp пЗ пЗ

27

Фиг

28

| название | год | авторы | номер документа |

|---|---|---|---|

| Коррелятор | 1985 |

|

SU1262522A1 |

| Коррелятор | 1986 |

|

SU1425711A1 |

| Коррелятор | 1988 |

|

SU1705835A1 |

| Дельта-модулятор | 1987 |

|

SU1508350A2 |

| Устройство для вычисления порядковых статистик последовательности двоичных чисел | 1984 |

|

SU1239708A1 |

| Дельта-модулятор | 1986 |

|

SU1345349A2 |

| Адаптивный автокоррелятор | 1990 |

|

SU1774345A1 |

| Дельта-модулятор | 1988 |

|

SU1543547A1 |

| Анализатор активности непрерывных сигналов | 1989 |

|

SU1658386A1 |

| Цифровой фильтр | 1985 |

|

SU1244786A1 |

Изобретение относится к цифровой электроизмерительной и вычислительной технике и предназначено для аппаратурного определения в масштабе реального времени корреляционной функции с симметричными разнополярными сдвигами случайных процессов. Цель изобретения - расширение частотного диапазона обрабатываемых входных сигналов. Введение в устройство дополнительных двух п-разрядных регистров, двух элементов ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ, двух блоков п-разрядных регистров, двух блоков комбинационных сумматоров, двух групп блоков элементов И позволило заменить операцию простой логической операцией ИСКЛЮЧАЮЩЕЕ ИЛИ с отрицанием знаковых битов многоразрядного двоичного кода и одно-.- разрядной дельта кодовой последовательности дельта-модуляторов, а традиционный умножитель многоразрядных отсчетов - элементом ИСКЛЮЧАЩЕЕ ИЛИ-НЕ. 4 ил. О) со со со ел 00 4

Фиг.З

изо

з/f-i

ЗЦ-2 ИЗЧ-Р

Составитель Е, Ефимова Редактор А. Ворович Техред М.Дидык . Корректор С. Черни

Заказ 4224/40 Тираж 670Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Погрибной В, А | |||

| Линейная дельта- модуляция в системах обработки сигналов с импульсно-кодовой модуляцией.- Радиотехника, 1984, №9, с | |||

| Приспособление для разматывания лент с семенами при укладке их в почву | 1922 |

|

SU56A1 |

| Коррелятор | 1985 |

|

SU1262522A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-09-23—Публикация

1986-02-20—Подача