4

СО

со

05

4;;

Изобретение относится к области автоматики и вычислительной техники и может быть использовано для коммутации двунаправленных каналов с дис- кретными и аналоговыми сигналами в магистралях мелсмодулыюго обмена, в устройствах управления скользящим ре- зерззом, а также . в качестве процессора преобразования структур данных, выполняющего операции расширения и сжатия логических лекторов.

Целью изобретения является расиш- рение функциональных возможностей за счет обеспечения двунаправленной передачи дискретных и з шлоговых сигналов по коммутируемым каналам.

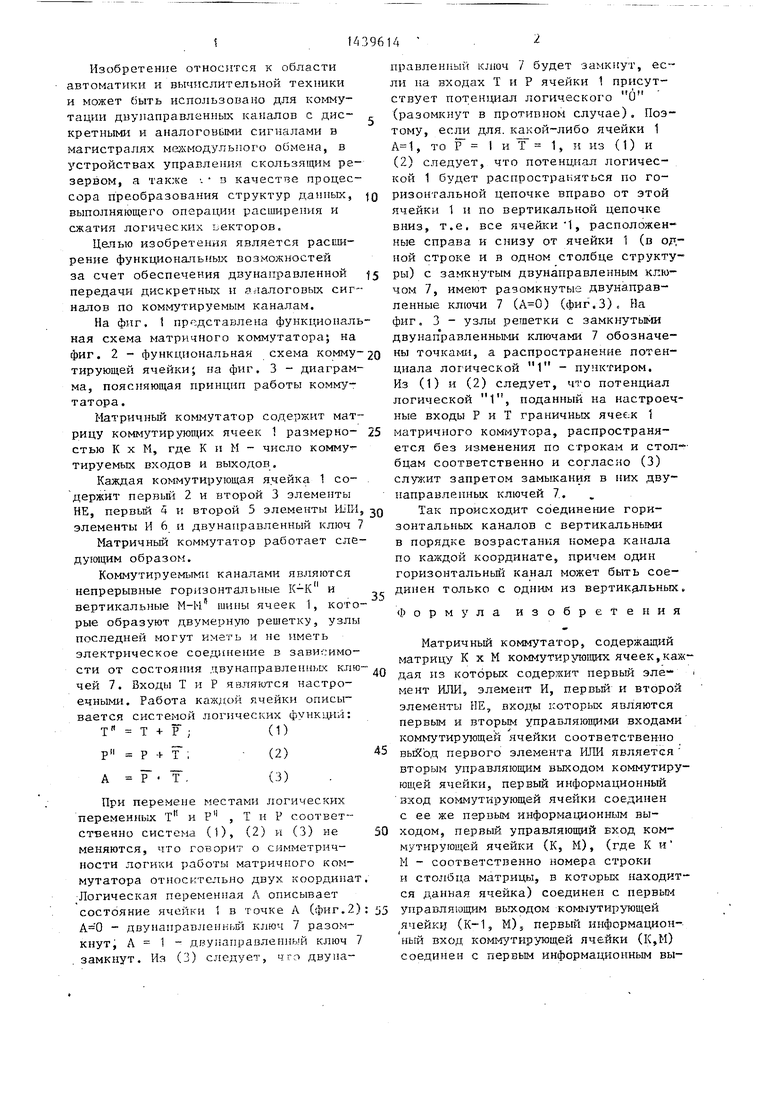

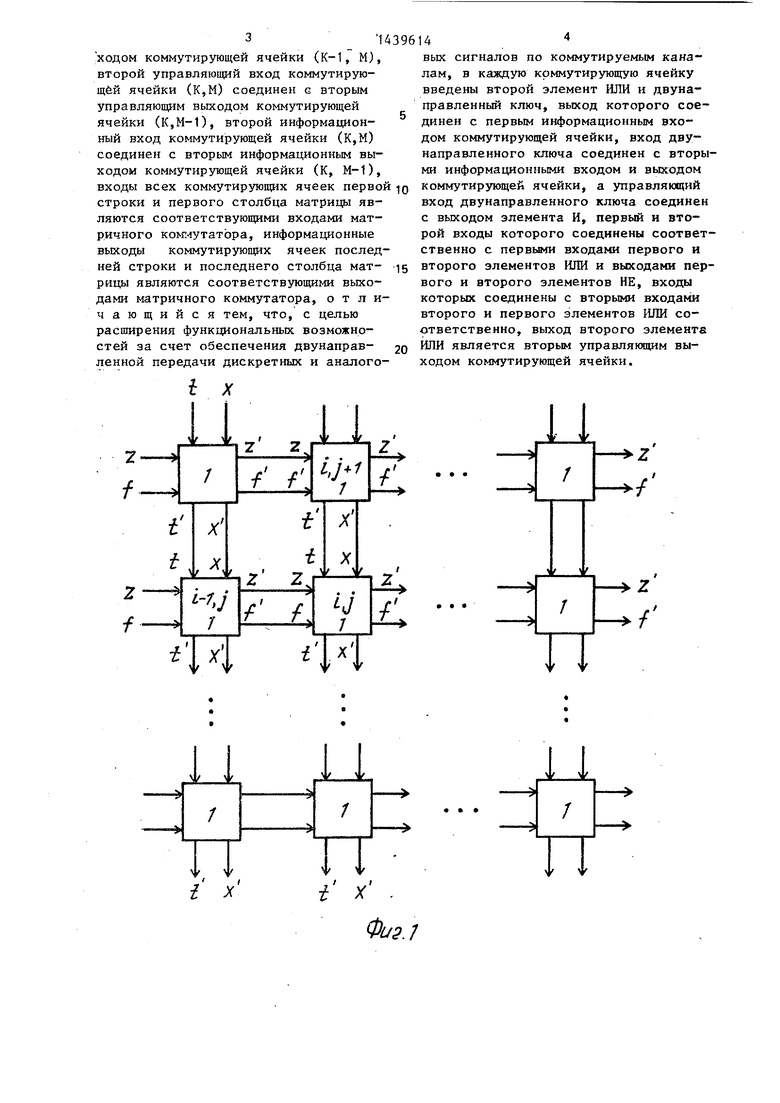

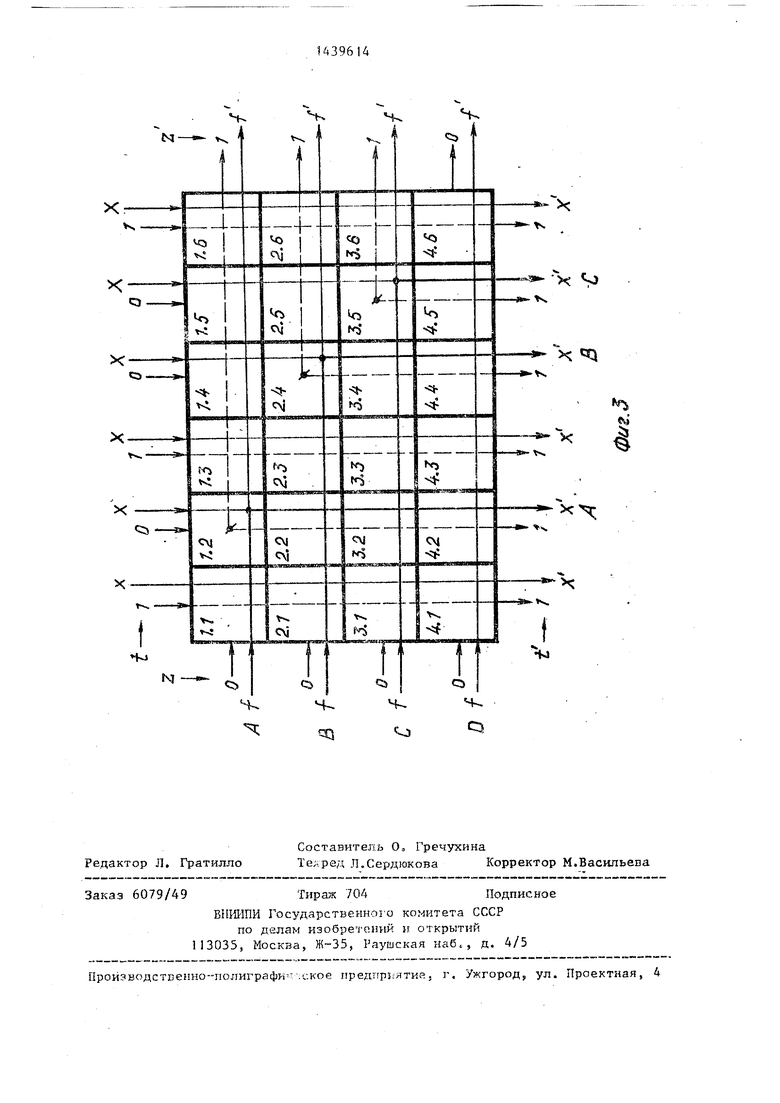

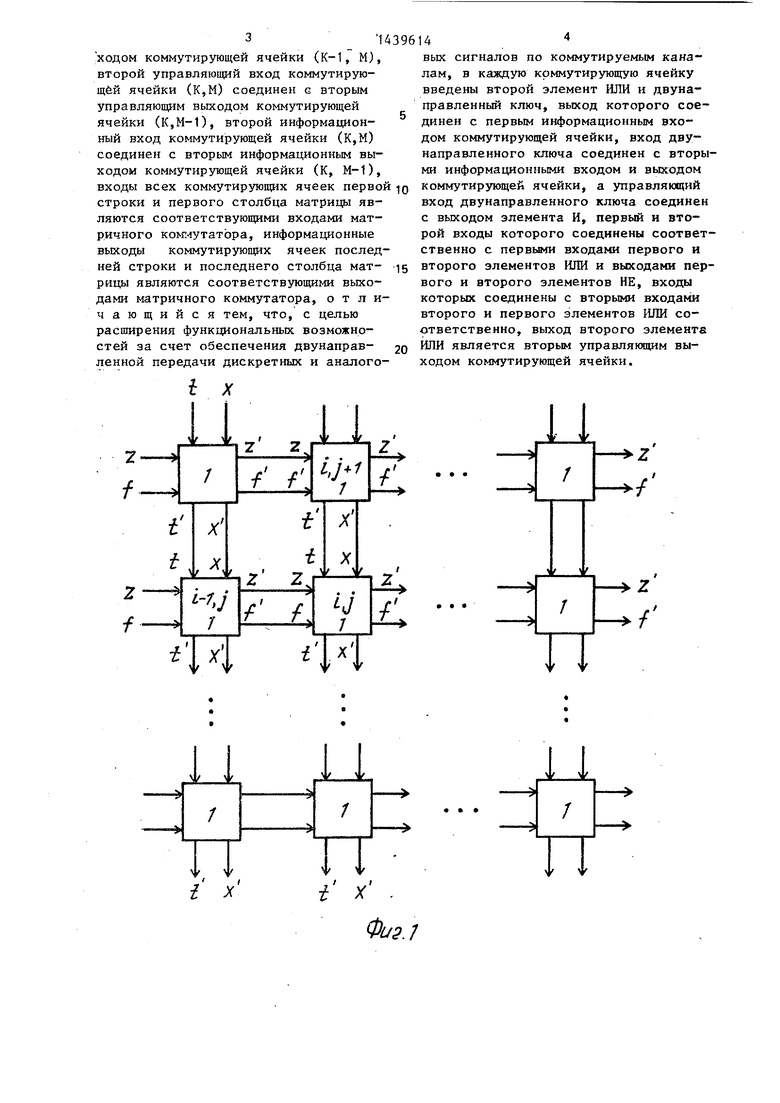

На фиг, 1 представлена функциональная схема матричного коммутатора; на фиг. 2 - функциональная схема коммутирующей ячейки; на фиг. 3 - диаграмма, поясняющая принцип работы коммутатора.

1-1атричный коммутатор содержит матрицу коммутирующих ячеек 1 размерно- стью К X М, где К и М - число коммутируемых входов и выходов.

Каждая коммутирующая ячейка 1 содержит первый 2 и второй 3 элементы НЕ, первьй 4 и второй 5 элементы ШШ элементы И 6 и двунаправленный ключ 7

Матричный коммутатор работает следующим образом.

Коммутируемыми каналами являются непрерывные горизонтальн.ые К-К и

вертикальные шины ячеек 1, которые образуют двумерную решетку, узлы последней могут иметь и не иметь электрическое соединение в зависимости от состояния двунаправленньЕк клю чей 7. Входы Т и Р являются настроечными. Работа каждой ячейки описывается системой логических функций: Т Т + F ; (1)

Р Р -ь Т ; А .

(2) (3)

При перемене местами логических переменных Т и Р , Т и Р соответственно система (1), (2) и (3) не меняются, что говорит о симметричности логики работы матричного коммутатора относительно двух координат. Логическая переменная Л описывает состояние ячейки 1 в точке А (фиг.2): - двунанравленкьБ ключ 7 разомкнут, А 1 - двунаправленный ключ 7 замкнут. Из (3) следует, ч го двупа

g

5

Q

5

0 5

правлен11ый ключ 7 будет замкнут, если на входах Т и Р ячейки 1 присутствует потенциал логического О (разомкнут в противном случае). Поэтому, если для. какой-либо ячейки 1 , то Р 1 и Т 1, и из (1) и (2) следует, что потенциал логической 1 будет распространяться по горизонтальной цепочке вправо от этой ячейки 1 и по вертикальной цепочке вниз, т.е. все ячейки 1, расположенные справа и снизу от ячейки 1 (в одной строке и в одном столбце структуры) с замкнутым двунаправленным ключом 7, имеют разомкнутые двунаправленные ключи 7 () (фиг.З), На фиг, 3 - узлы решетки с замкнутыми двунаправленными ключами 7 обозначены точками, а распространение потенциала логической 1 - пунктиром. Из (1) и (2) следует, что потенциал логической 1, поданный на настроечные входы Р и т граничных ячее:К 1 матричного коммутора, распространяется без изменения по строкам и столбцам соответственно и согласно (3) запретом замыкания в них двунаправленных ключей 7. ,

Так происходит соединение горизонтальных каналов с вертикальными в порядке возрастания номера канала по каждой координате, причем один горизонтальньш канал может быть соединен только с одн1-1м из вертикальных.

Формула изобретения

Матричный коммутатор, содержащий матрицу К X М коммутирующих ячеек,каждая из которых содержит первый эле- i мент ИЛИ, элемент И, первый и второй элементы НЕ, входы которых являются первым и вторым управляющими входами коммутирующей ячейки соответствен-но выХод первого элемента ИЛИ является вторым управляющим выходом коммутирующей ячейки, первый информационный вход коммутирующей ячейки соединен с ее же первым информационным выходом, первый управляющий вход коммутирующей ячейки (К, М), (где К и М - соответственно номера строки и столбца матрицы, в которых находится данная ячейка) соединен с первьв- управляющим выходом коммутир тощей ячейку (K-I, M)j первый информационный вход ком-гутирующей ячейки (К,М) соединен с первым информационным вы3 1

ходом коммутирующей ячейки (К-1, М), второй управляющий вход коммутирующей ячейки (К,М) соединен с вторым управляющим выходом коммутирующей ячейки (К,М-1), второй информационный вход коммутирующей ячейки (К,М) соединен с вторым информационным выходом коммутирующей ячейки (К, М-1), входы всех коммутирующих ячеек первой строки и первого столбца матрицы являются соответствующими входами матричного коьЕ.утатора, информационные выходы коммутирующих ячеек последней строки и последнего столбца мат- рицы являются соответствующими выходами матричного коммутатора, отличающийся тем, что, с целью расщирения функциональных возможностей за счет обеспечения двунаправ- ленной передачи дискретных и аналого1 . вых сигналов по коммутируемым каналам, в каждую коммутирующую ячейку введены второй элемент ИЛИ и двунаправленный ключ, выход которого соединен с первым информационным входом коммутирующей ячейки, вход двунаправленного ключа соединен с вторыми информационными входом и выходом коммутирующей ячейки, а управляющий вход двунаправленного ключа соединен с выходом элемента И, первый и второй входы которого соединены соответственно с первыми входами первого и второго элементов ИЛИ и выходами первого и второго элементов НЕ, входы которых соединены с вторыми входаьш второго и первого элементов ИЛИ соответственно, выход второго элемента ИЛИ является вторым управляющим выходом коммутирующей ячейки.

| название | год | авторы | номер документа |

|---|---|---|---|

| Матричный коммутатор | 1985 |

|

SU1275753A1 |

| Формирователь матричных команд | 2018 |

|

RU2707913C1 |

| Матричный индикатор | 1976 |

|

SU579639A1 |

| Матричный распределитель | 1987 |

|

SU1580377A1 |

| Устройство для отображения графической информации на газоразрядном матричном индикаторе | 1987 |

|

SU1495846A1 |

| Матричная ракетная двигательная система с индивидуальным цифровым управлением величиной тяги каждой двигательной ячейки для малоразмерных космических аппаратов | 2017 |

|

RU2660210C1 |

| РЕВЕРСИВНАЯ МАТРИЧНАЯ РАКЕТНАЯ ДВИГАТЕЛЬНАЯ СИСТЕМА С ИНДИВИДУАЛЬНЫМ ЦИФРОВЫМ УПРАВЛЕНИЕМ ВЕЛИЧИНОЙ ТЯГИ КАЖДОЙ РЕВЕРСИВНОЙ ДВИГАТЕЛЬНОЙ ЯЧЕЙКИ ДЛЯ МАЛОРАЗМЕРНЫХ КОСМИЧЕСКИХ АППАРАТОВ | 2017 |

|

RU2654782C1 |

| Матричный процессор | 1985 |

|

SU1354204A1 |

| Коммутатор | 1985 |

|

SU1248045A1 |

| ЯЧЕЙКА МАТРИЧНОГО КОММУТАТОРА С ПОТОКОВОЙ НАСТРОЙКОЙ | 2001 |

|

RU2194302C2 |

Изобретение относится к области автоматики и вычислительнЬй техники и может быть использовано для коммутации двунаправленных каналов с дискретными и аналоговыми сигналами в магистралях межмодульного обмена, в устройствах управления скользящим резервом, а также в качестве процессора преобразования структур данных, вьтолняющего операции расширения и сжатия логических векторов. Цель изобретения - расширение функциональных возможностей за счет обеспечения двунаправленной передачи дискретных и аналоговых сигналов по коммутируемым каналам. Для этого в каждую коммутирующую ячейку 1 матричного комь1ута- тора, содержащую первый 2 и второй 3 элементы НЕ, первый элемент ИЛИ 4, элемент И 6, дополнительно введены второй элемент ИЛИ 5 и двунаправленный ключ 7. 3 ил. Q (Л

i X

ФФ . у

И Пп

и и

и

/

Z

./

Z

IT

Н-.

CQ

Ч-. )

Ч-.

Q

| Фет Я.И | |||

| Функциональные возмож- «ости простых вычислительных средств | |||

| АВТ, 1974, № 3, с | |||

| Приспособление для автоматической односторонней разгрузки железнодорожных платформ | 1921 |

|

SU48A1 |

| Коммутатор | 1976 |

|

SU558399A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-11-23—Публикация

1987-02-11—Подача