ка памяти, выход которого соединен с первым входом второго регистра и является выходом устройства, введень триггер, элементы 2И-ПЛИ, 2-ИЛИ-И, второй дешифратор и преобразователь кода, первый вход которого,объединен с вторыми входами первого и второго регистрови подсоединен к вторрму выходу счетчика/второй вход - к выхо триггера, третий и четвертый входы преобразователя кода объединены с соответствующими входами первого элемента 2И-ИЛИ и соединены с выходами первого и второго регистров соответсвенно, пятый вход преобразователя кодов соединен с первым входом элемент 2ИЛИ-И и с выходом второго дешифратора, выход преобразователя кода соединевл с информационным входом блока, памяти второй вход элемента 2ИЛИ-И соединен с первым управляющим входом блока памяти и с вторым выходом счетчика, третий вход подключен к входу элемента 2И-ИЛИ, а выход - к второму управляющему входу блока памяти, выход первого дешифратора соединен с входом клавиатуры и с входом блока микропрограммного управления, выход которого подключен к входу второго дешифратора.

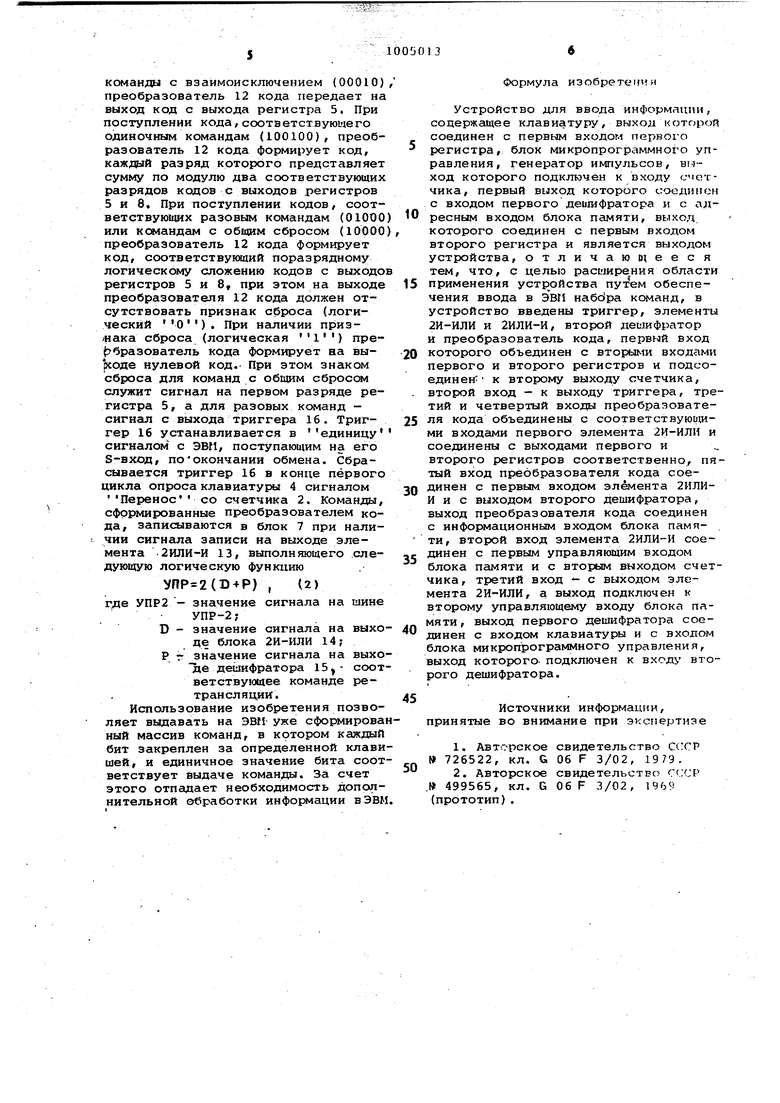

На фиг.1 изображена блок-схема предложенного устройства; на фиг.2 - временная диаграмма его работы.

Схема включает генератор 1, счетчик 2; первый де1аифратор 3, клавиатуру 4, первый регистр 5, логический блок б, блок 7 памяти, второй регист 8, блок 9 микропрограммного управления, шину 10 управления, шину 11 адреса, преобразователь 12 кода, элемент 2ИЛИ-И 13, элемент 2И-ИЛИ 14, второй дешифратор 15, триггер 16, информацию на шине 10 ЛД1Р, значения первого и второго-разрядов шины 11УПР-1, УПР-2, импульсы синхронизации ТО-Т4.

Устройство работает сдедующим

образом.

Генератор 1 и счетчик 2 формируют последовательность адресов на шине 1 и -импульсы синхронизации на шине 10 (см. фиг.2). Сигналами на шине 11 через дешифратор 3 производится опрос клавиатуры 4. Клавиши, подключенные к одному выходу дешифратора 3 образуют одну группу с определенным типом . Информация с группы клавиши переписывается во входной регистр 5 и поступает в логический блок б. Одновременно с опросом клавиатуры 4 дешифратор 3 осуществляет опрос блока 9, на выходе которого формируется код команды, который может принимать пять различных значений по числу типов команд, и который определяет алгоритм работы логическо1 О блока 6. Со старших разрядов- счетчика 2 по 1Л1не 11 колы номеров групп кнопок поступает на младшие адресные входы блока 7. Со страшего разряда шины 10-УПР-1 от счетчика 2 на старший разряд блока

7поступает логический уровень, не реключающий за время такта опроса клавиатуры 4 две области памяти бл ка 7: при логической единице oi новную, при логическом ( нуле вспомогательную (см.фиг.2). Но нет могательной области памяти хранятся состояния клави11 (нажата-не нажч та) предыдущего цикла опроса.

При этом под циклом опроса пони «.ется время между очередными опросами одной и той же группы клавиц.

8основной области блока памяти хра нятся команды, сформированные логическим блоком 6. После очередной смены адреса на шине 11 текущая информация (А) с группы клавиш переписывается в регистр 5 (интервал ТО-Т1 фиг.2) и из него поступает на прямые входы блока 2И-ИЛН 14, одновременно на инвертирующие входы этого блока с регистра 8 поступает код, соответствующий состоянию этой же группы клавиш в предыдущем цикле опроса. Сигнал на выходе блока 2И-ИЛ 14 определяется выражением

A,/VS)V(/I2AC2)V...V(,(1)

где АК - к-тый разряд А;

CK к-тый разряд кода на выходе регистра 8.

Единичный результат выполнения этой операции означает, что в данной группе клавиши с момента предыдущего цикла опроса блока нажата хотя бы одна клавиша. В интервале Т1-Т2 (см. фиг, 2) производится запись информации А во вспомогательную область памяти блока 7.

В интервале Т2-Т4 сигнал на УПР-1 имеет единичное значение (см. фиг.2) При этом производится обращение к ос новной области блока 7, с которого в регистр 8 переписывается команда (В), сформированная в предыдущем цикле опроса, и поступает с выходов регистра 8 на вход преобЕ азователя 12 кода. Преобразователь кодов формирует на информационных входах блока 7 код, зависящий от кодовой комбинации на его входах. При логичесьчл нуле на УПР-1 преобразовг тель 12 копа передает на выход код с выхода регистра 5. При логической единице на УПР-1 выполняет поразрядные логические операции с кодами, поступающими с регистров 5. Код команд(.1 поступающий с блока 9, дешифрируется дешифратором 15 и поступа(т на вход преобразователя 12 кода. При поступлении кода,соответствук)ще1-о команде ретрансляции (00001) или команды с взаимоисключением (00010) преобразователь 12 кода передает на выход код с выхода регистра 5. При поступлении кода,соответствующего одиночным командам (100100), преобразователь 12 кода формирует код, каждый разряд которого представляет сумму по модулю два соответствующих разрядов кодов с выходов регистров 5 и 8, При поступлении кодов, соответствую1дих разовым командам (01000 или командам с общим сбросом (10000 преобразователь 12 кода формирует код, соответствующий поразрядному логическому сложению кодов с выходо регистров 5 и 8, при этом на выходе преобразователя 12 кода должен отсутствовать признак сброса (логический О). При наличии призНака сброса (логическая 1 ) пре|7бразователь кода формирует на выЬсоде нулевой код. При этом знаком сброса для команд с общим сбросом служит сигнал на первом разряде регистра 5, а для разовых команд сигнал с выхода триггера 16. Триггер 16 устанавливается в единицу сигналом с ЭВП, поступающим на его S-вход, поокончании обмена. Сбрасывается триггер 16 в конце первого цикла опроса клавиатуры 4 сигналом Перенос со счетчика 2. Команды, сформированные преобразователем кода, записываются в блок 7 при наличии сигнала записи на выходе элемента 2ИЛИ-И 13, выполняющего следующую логическую функцию () , (2) г-де УПР2 - значение сигнала на шине УПР-2; D - значение сигнала на выхо де блока 2И-ИЛИ 14; Р г значение сигнала на выхо де дешифратора 15 - соот ветствующее команде ретрансляция. Использование изобретения позволяет выдавать на ЭЗП уже сформирова ный массив команд, в котором каждый бит закреплен за определенной клави шей, и единичное значение бита соот ветствует выдаче команды. За счет этого отпадает необходимость дополнительной обработки информации в ЭВМ Формула изобретении Устройство для ввода информации, содержащее клавиатуру, выход которой соединен с первым входом первого регистра, блок микропрограммного управления, генератор импульсов, ниход которого подключен к сходу смсггчика, первый выход которого сосдн и:;н с входом первого дешифратора и с адресным входом блока памяти, выход которого соединен с первым входом второго регистра и является выходом устройства, отличаю DieecH тем, что, с целью расширения области применения устр ойства путем обеспечения ввода в ЭВП набЬра команд, в устройство введены триггер, элементы 2И-ИЛИ и 2ИЛИ-И, второй деишфратор и преобразователь кода, первый вход которого объединен с входами первого и второго регистров и подсоединен к второму выходу счетчика, второй вход - к выходу триггера, третий и четвертый входы преобразователя кода объединены с соответствуюв ми входами первого элемента 2И-ИЛН и соединены с выходами первого и второго регистров соответственно, пятый вход преобразователя кода соединен с первым входом элемента 2ИЛИИ и с выходом второго дешифратора, выход преобразователя кода соединен с информационным входом блока памя- . ти, второй вход элемента 2ИЛИ-И соединен с первым управляющим входом блока памяти и с вторым выходом счетчика, третий вход - с выходом элемента 2И-ИЛИ, а выход подключен к второму управляющему входу блока памяти, выход первого дешифратора соединен с входом клавиатуры и с входом блока микропрограммного управления, выход которого- подключен к входу второго дешифратора. Источники информации, принятые во внимание при экспертизе 1.Авторскоесвидетельство СССР 726522, кл. G06 F 3/02, 1979. 2.Авторскоесвидетельство СССР . 499565, кл. G06 F 3/02, 19()9 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля знаний обучаемых | 1990 |

|

SU1758658A1 |

| Устройство для подготовки информации на перфоленте | 1977 |

|

SU684549A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Вероятностная вычислительная машина | 1986 |

|

SU1455344A1 |

| Устройство для подготовки данных | 1988 |

|

SU1617429A1 |

| Устройство для ввода информации | 1987 |

|

SU1424004A1 |

| Микропрограммное устройство для ввода-вывода информации | 1983 |

|

SU1144099A1 |

| Устройство выборки команд процессора | 1986 |

|

SU1410028A1 |

| Устройство для ввода информации в калькулятор | 1990 |

|

SU1791807A1 |

| Устройство для ввода информации | 1982 |

|

SU1048465A1 |

Авторы

Даты

1983-03-15—Публикация

1981-09-17—Подача