t1

Изобретение относится к вычисаи- тельной технике и может быть исполь™ ;зовано для выборки команд длиной в слово и полуслово при построении процессора сшгциалиг хрованной ЭВМ среднего быст1)одействия.

Цель изобретения - сокращение Iобъема оборудования,

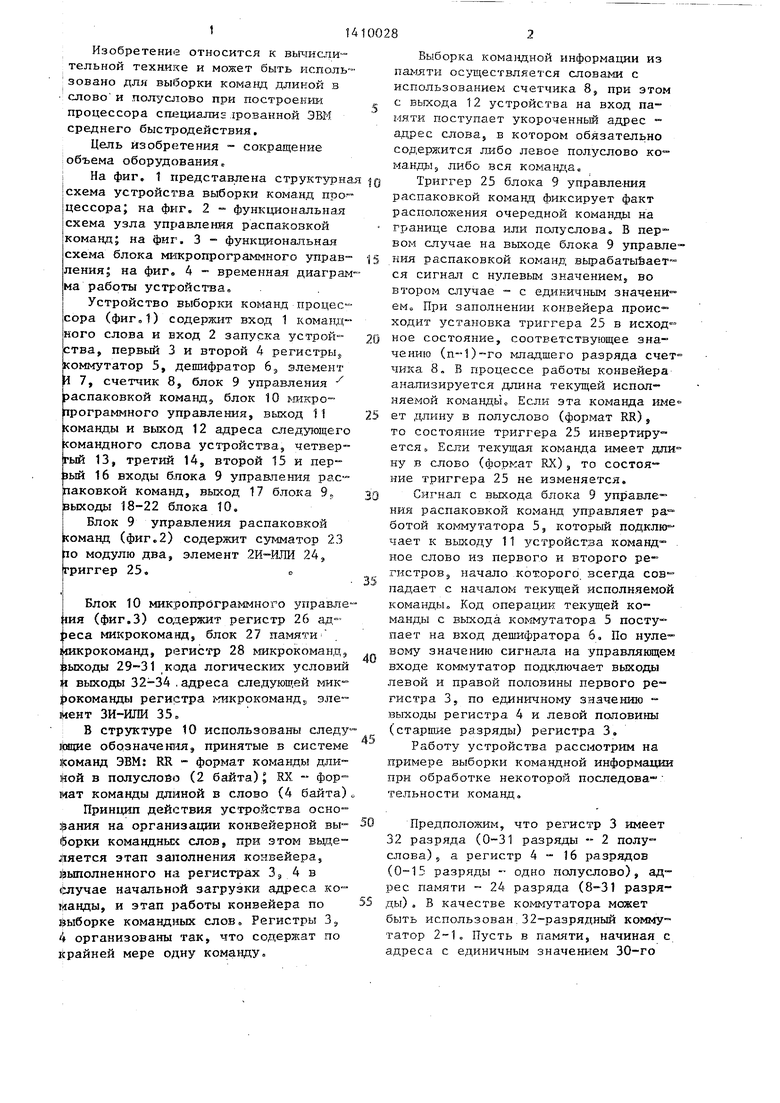

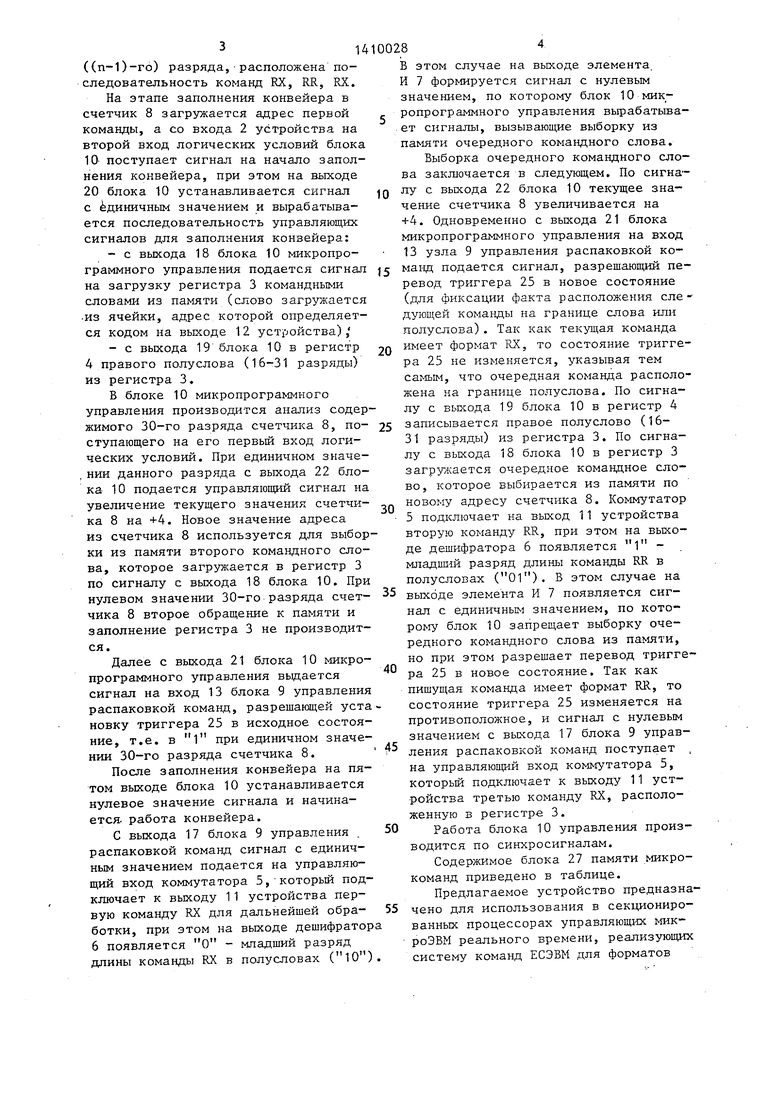

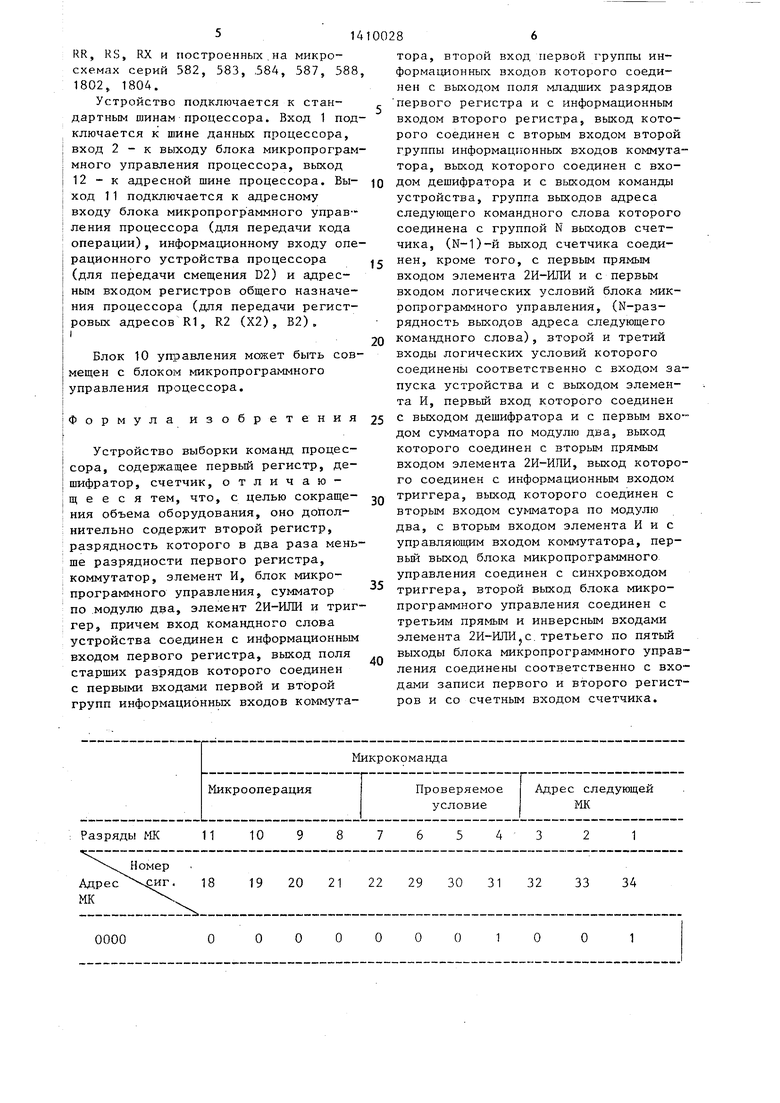

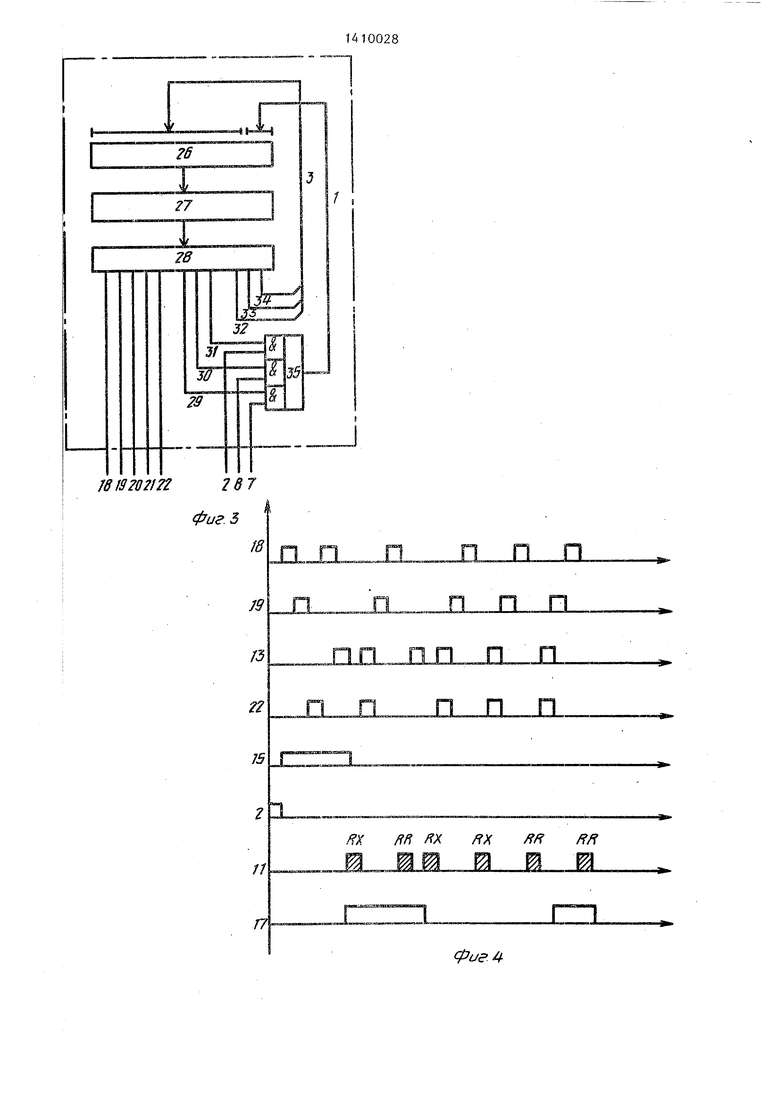

I На фиг, 1 представлена структурна схема устройства выборки команд процессора; на фиг. 2 - функциональная схема узла ущ авления распаковкой команд; на фиг. 3 - функциональная схема блока микропрограммного управ- ления; на фиг, 4 - временная диаграг ма работы устр Ойства

Устройство выборки коман,д процессора (фиге1) содержит вход 1 комавд- кого слова и вход 2 запуска устрой- ства, первый 3 и второй 4 регистрыj коммутатор 5, дешифратор 6,, элемент

7, счетчик 8, блок 9 управления распаковкой команд, блок 10 fflкpo гфограммного управления, выход 11 команды и выход 12 адреса следующего командного слова устройства, четвертый 13, третий 14, второй 15 и пер- зый 16 входы блока 9 управления распаковкой команд, выход 17 блока 9 вькоды 18-22 блока 10,

Блок 9 управления распаковкой команд (фиг.2) содержит сумматор 23 1о модулю два, элемент 2И-ЙЛИ 24, триггер 25.о

у

Блок 10 мик:ропрограммно1 о управле шя (фиг.З) содержит регистр 26 ад- зеса микрокоманд, блок 27 памяти . 1икрокоманд, регистр 28 микрокоманд, выходы кода логическт-пс условий выходы 32-34.адреса следующей микрокоманды регистра микрокоманду эле- йент ЗИ-ИПИ 35.

В структуре 10 использованы следу 1|мцие обозначеш-Шэ принятые в системе 5|соманд ЭВМ: RR - формат команды дли- 1(50й в полуслово (2 байта); RX - формат команды длиной в слово (4 байта)

Принцип действия устройства осно- на организации конвейерной вы- форки комакдны:с слов, при этом вьаде- дяется этап заполнешм конвейера, выполненного на регистрах 3 4 в (Ьлучае начальной загрузки адреса ко-- щанды, и этап работы конвейера по выборке командных слов. Регистры 3,, 4 организованы так, что содержат по Крайней мере одну комавду.

Выборка командной информации из осуществляется словами с использованием счетчика 8, при этом с выхода 12 устройства на вход памяти поступает укороченный адрес - адрес слова, в котором обязательно содержится либо левое полуслово команды, либо вся командас

Триггер 25 блока 9 управле-ния распаковкой команд фиксирует факт расположения очередной команды на границе слова или полуслова, В первом случае на выходе блока 9 управления распаковкой команд вьфабатыбает- ся сигнал с нулевьм значением, во втором случае - с единичным значением.. При заполнении конвейера происходит установка триггера 25 в исход

чению (п--1)го младшего разряда счетчика 8, В процессе работы конвейера анализируется длина текущей испол няемой команды. Если эта команда име« ет длину в полуслово (формат RR), то состояние триггера 25 инвертируется. Если текущая команда имеет дли ну в слово (форкат RX), то состоя

О

5

0

0

5

ние триггера 25 не изменяется.

Сигнал с выхода блока 9 управления распаковкой команд управляет работой ко1умутатора 5, который подклю чает к вьвсоду 11 з стройстза команд- . ное слово из первого и второго регистров j начало которого всегда сов падает с началом текущей исполняемой команды Код операции текущей команды с выхода ко яу1утатора 5 поступает на вход дешифратора в. По нулевому значению сигнала на управлянщем входе коммутатор подключает выхода левой и правой половины первого ре гистра 3j по единичному значению выходы регистра 4 и левой половины (старшие разряды) регистра 3.

Работу устройства рассмотрим на примере выборки командной информации при обработке некоторой последова- тельности команд.

Предположим, что регистр 3 имеет 32 разряда (0-31 разряды - 2 полуслова), а регистр 4-16 разрядов (0-15 разряды - одно полуслово), адрес памяти 24 разряда (8-31 разряды) . В качестве коммутатора может быть использован,32-разрядный коммутатор 2-1. Пусть в памяти, начиная с адреса с единичным значением 30-го

10

20

1410028

((n-l)-ro) разряда,расположена по- В следовательность команд RX, RR, RX. И

На этапе заполнения конвейера в счетчик 8 загружается адрес первой команды, а со входа 2 устройства на торой вход логических условий блока 10- поступает сигнал на начало заполнения конвейера, при этом на выходе 20 блока 10 устанавливается сигнал с Единичным значением и вырабатывается последовательность управляющих сигналов для заполнения конвейера:

-с выхода 18 блока 10 микропрограммного управления подается сигнал на загрузку регистра 3 командными словами из памяти (слово загружается

из ячейки, адрес которой определяется кодом на выходе 12 устройства),

-с выхода 19 блока 10 в регистр 4 правого полуслова (16-31 разряды) из регистра 3,

В блоке 10 микропрограммного управления производится анализ содеримого 30-го разряда счетчика 8, по- 25 ступающего на его первый вход логических условий. При единичном значе- НИИ данного разряда с выхода 22 блока 10 подается управляющий сигнал на увеличение текущего значения счетчи ка 8 на +4. Новое значение адреса з счетчика 8 используется для выборки из памяти второго командного слова, которое загружается в регистр 3 по сигналу с выхода 18 блока 10, При нулевом значении 30-го разряда счетика 8 второе обращение к памяти и заполнение регистра 3 не производится.

Далее с выхода 21 блока 10 микропрограммного управления выдается сигнал на вход 13 блока 9 управления распаковкой команд, разрешающей установку триггера 25 в исходное состояние, т.е. в 1 при единичном значеии 30-го разряда счетчика 8.

После заполнения конвейера на пятом выходе блока 10 устанавливается улевое значение сигнала и начинается- работа конвейера.

С выхода 17 блока 9 управления . 50 аспаковкой команд сигнал с единичным значением подается на управляюий вход коммутатора 5,-которьй подлючает к выходу 11 устройства первую команду RX для дальнейшей обра- 55 ботки, при этом на выходе дешифратора 6 появляется О - младший разряд лины команды RX в полусловах (10).

зн ро ет па

ва лу че +4 ми 13 J5 ма ре ду по им ра са же лу за 31 лу за во но 5 вт де мл по вы на ро ре но ра пи со пр зн ле на ко ро же

во

ко

че ва ро си

30

35

40

45

0

0

В И

5

0 5

этом случае на выходе элемента 7 формируется сигнал с нулевым значением, по которому блок 10 микропрограммного управления вырабатывает сигналы, вызывающие выборку из памяти очередного командного слова.

Выборка очередного командного слова заключается в следующем. По сигналу с выхода 22 блока 10 текущее значение счетчика 8 увеличивается на +4. Одновременно с выхода 21 блока микропрограммного управления на вход 13 узла 9 управления распаковкой ко- 5 мавд подается сигнал, разрешающий перевод триггера 25 в новое состояние (для фиксации факта расположения еле дующей комаьщы на границе слова итш полуслова). Так как текущая команда имеет формат RX, то состояние триггера 25 не изменяется, указывая тем самым, что очередная команда расположена на границе полуслова. По сигналу с выхода 19 блока 10 в регистр 4 записывается правое полуслово (16- 31 разряды) из регистра 3. По сигналу с выхода 18 блока 10 в регистр 3 загрулсается очередное командное слово, которое выбирается из памяти по новому адресу счетчика 8. Коммутатор 5 подключает на выход 11 устройства вторую команду RR, при этом на выходе дешифратора 6 появляется 1 - млaдIШiй разряд длины комаьщы RR в полусловах (01). В этом случае на выходе элемента И 7 появляется сигнал с единичным значением, по которому блок 10 запрещает выборку очередного командного слова из памяти, но при этом разрешает перевод триггера 25 в новое состояние. Так как пишущая команда имеет формат RR, то состояние триггера 25 изменяется на противоположное, и сигнал с нулевым значением с выхода 17 блока 9 управления распаковкой команд поступает , на управляюшдй вход коммутатора 5, который подключает к выходу 11 устройства третью команду RX, расположенную в регистре 3.

Работа блока 10 управления производится по синхросигналам.

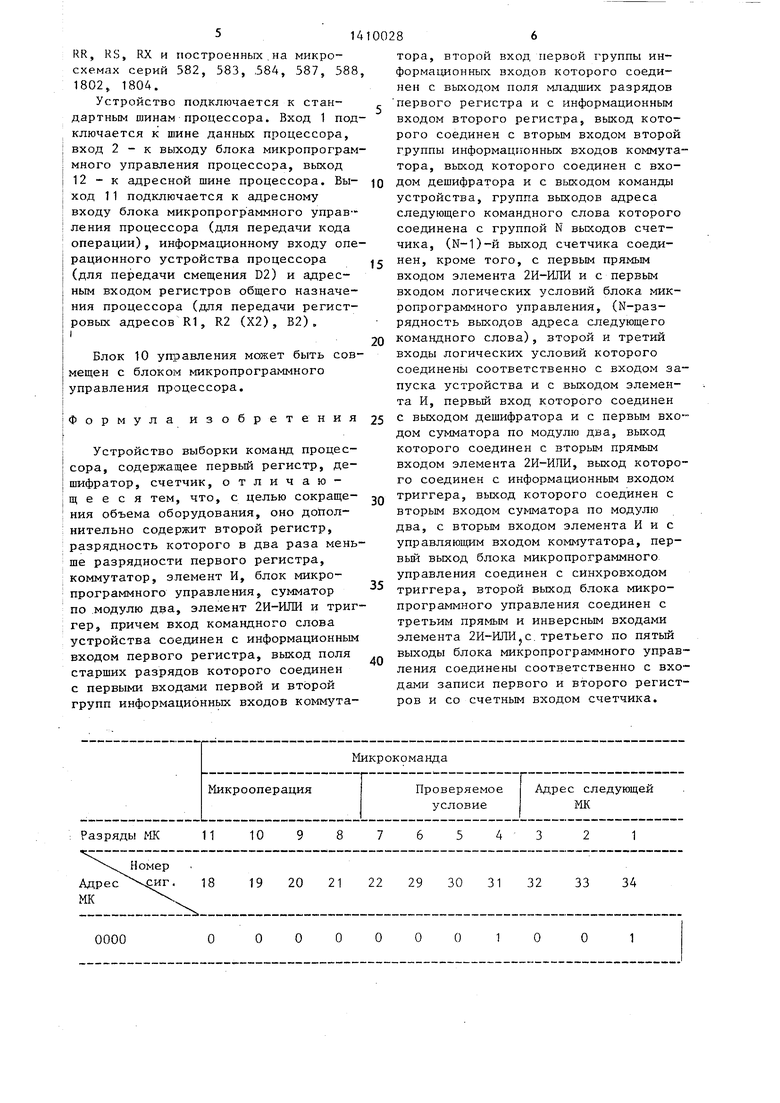

Содержимое блока 27 памяти микрокоманд приведено в таблице.

Предлагаемое устройство предназначено для использования в секционированных процессорах управляющих мик- роЭВМ реального времени, реализующих систему команд ЕСЭВМ для форматов

0

5

0

5

514

RR, RS, RX и построенных.на микросхемах серий 582, 583, ,584, 587, 588 1802, 1804.

Устройство подключается к стан- дартнь м шинам процессора. Вход 1 подключается к шине данных процессора, вход 2 - к выходу блока микропрограммного управления процессора, выход 12 - к адресной шине процессора. Выход 11 подключается к адресному входу блока микропрограммного управления процессора (для передачи кода операции), информационному входу операционного устройства процессора (для передачи смещения D2) и адресным входом регистров общего назначения процессора (для передачи регистровых адресов R1, R2 (Х2), В2). I

Блок 10 уп}равления может быть совмещен с блоком микропрограммного управления процессора.

Формула изобретения 25

Устройство выборки команд процессора, содержащее первый регистр, дешифратор, счетчик, отличающееся тем, что, с целью сокращения объема оборудования, оно дополнительно содержит второй регистр, разрядность которого в два раза меньше разрядности первого регистра, коммутатор, элемент И, блок микропрограммного управления, сумматор по модулю два, элемент 2И-ИЛИ и триггер, причем вход командного слова устройства соединен с информационным входом первого регистра, выход поля старших разрядов которого соединен с первыми входами первой и второй групп информационных входов коммута0

00286

тора, второй вход, первой группы ин- форма1угонных входов которого соединен с выходом поля младших разрядов первого регистра и с информационным входом второго регистра, выход которого соединен с вторым входом второй группы информационных входов коммутатора, выход которого соединен с входом дешифратора и с выходом команды устройства, группа выходов ащреса следующего командного слова которого соединена с группой N выходов счетчика, (Н-1)-й выход счетчика соеди5

0

5

0

5

0

нен, кроме того, с первым прямым входом элемента 2И-ИЛИ и с первым входом логических условий блока микропрограммного управления, (N-pas- рядность выходов адреса следующего командного слова), второй и третий входы логических условий которого соединены соответственно с входом запуска устройства и с выходом элемента И, первый вход которого соединен с выходом дешифратора и с первым входом сумматора по модулю два, выход которого соединен с вторым прямым входом элемента 2И-ИЛИ, выход которого соединен с информационным входом триггера, выход которого соединен с вторым входом сумматора по модулю два, с вторым входом элемента И и с управляюш;им входом коммутатора, пер- вьй выход блока микропрограммного управления соединен с синхровходом триггера, второй выход блока микропрограммного управления соединен с третьим прямым и инверсным входами элемента 2И-ИЛИ с.третьего по пятый выходы блока микропрограммного управления соединены соответственно с входами записи первого и второго регистров и со счетным входом счетчика.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство выборки команд процессора | 1987 |

|

SU1481758A1 |

| Устройство для управления буфер-НОй пАМяТью | 1979 |

|

SU840903A1 |

| Устройство для распаковки команд | 1981 |

|

SU972507A1 |

| Устройство для распаковки команд | 1984 |

|

SU1251075A1 |

| Устройство для буферизации команд | 1976 |

|

SU610109A1 |

| Устройство для распаковки команд | 1987 |

|

SU1464157A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Устройство центрального управления процессора | 1983 |

|

SU1136177A1 |

| Микропрограммное устройство для управления и обмена данными | 1983 |

|

SU1129601A1 |

| Микропрограммный процессор | 1978 |

|

SU744587A1 |

Изобретение относится к области вычислительной техники и может бь1ть использовано для выборки команд длиной в слово и полуслово при построении процессора спецналнзированной ЭВМ среднего быстродействия. Цель изобретения - сокращение объема оборудования. Устройство выборки команд содерлдат вход 1 командного слова, вход 2 запуска, первьш 3 и второй 4 регистры, комментатор 5, дешифратор 6, элемент И 7, счетчик 8, блок 9 управления распаковкой команд, блок 10 микропрограммного управления, выход 11 команды и выход 12 адреса следующего командного слова, входы 13- 16 и выход 17 блока 9 управления распаковкой комаьщ, выходы 18-22 блока микропрограммного управления. 4 ил. 1 табл.(Л ю СХ5 /г

0000

00000010

0010

О00001001О1

0011

000100001О

0100

1 О О 1 01 О О 1

0110

о01010000о1

0111

о00110001оо

1000

0001000011

1010

о о 1

1011

о01 о о с 00 ооо

1100

о1000000111

1110

100000000оо

Продолжение таблицы

00001

сри.2

78

Э2

1619 20 2} 22287

фиг. 5

/8

J9

/3

П

пп

ПП

ПП

| Коучи П.М | |||

| Архитектура конвейерных ЭВМ | |||

| М.: Радио и связь, 1985, с | |||

| Тепловой измеритель силы тока | 1921 |

|

SU267A1 |

| Устройство для буферизации команд | 1976 |

|

SU610109A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-07-15—Публикация

1986-11-26—Подача