Изобретение относится к вычислительной технике и может быть использовано при проектировании и оптимизации по критериям максимальной оперативности получаемых результатов на всех этапах технологических процессов обработки информации в АСУ, например, таких как заполнение документов исходными данными, перенос данных намгилинные носители, ввод информации в ЭВМ, логическая и а рифметическая обработка, контроль, вывод из ЭВМ и размножение результатов . .

Известно устройство для моделирования процесса сбора и обработки информации, содержащее блоки приема и формирования запроса, счетчик, дешифратор, элемент И, ИЛИ, триггеры и блок обработки запросов. Выходы блоков приема подключены к входам блока формирования запроса и счетчика, выход которого через де111ифратор и коммутатор подключен к входу блока обработки запросов. Выходы блока Формирования запросов подсоединены к единичным входам соответствующих триггеров-, выходы которых подключены к входам элементов и, выходы которых подключены

к входам блока обработки запросов 1

Недостатком устройства является невысокая точность моделирования реальных процессов обработки данных в современных АСУ из-за невозможности имитации обработки файлов, (массивов) информации в режимах, отли- . чающихся от тех, в которых исполь10зуется тфинцип последовательного доступа.

Наиболее близким по технической сущности к изобретению является уст15

ройство для моделирования процессов выполнения работы, содержащее генератор случайных напряжений, интегратор, блок сравнения, источник стабилизированного напряжения и блок регистра20ции, выход источника стабилизированного напряжения подключен к одному из входов блока сравнения, выход которого подключен к входу блока регистрации С 2.

25

С помощью данного устройства принципиально можно моделировать определенные процессы интегрированной обработки информации. Однако устройство не обеспечивает возможности полной

30

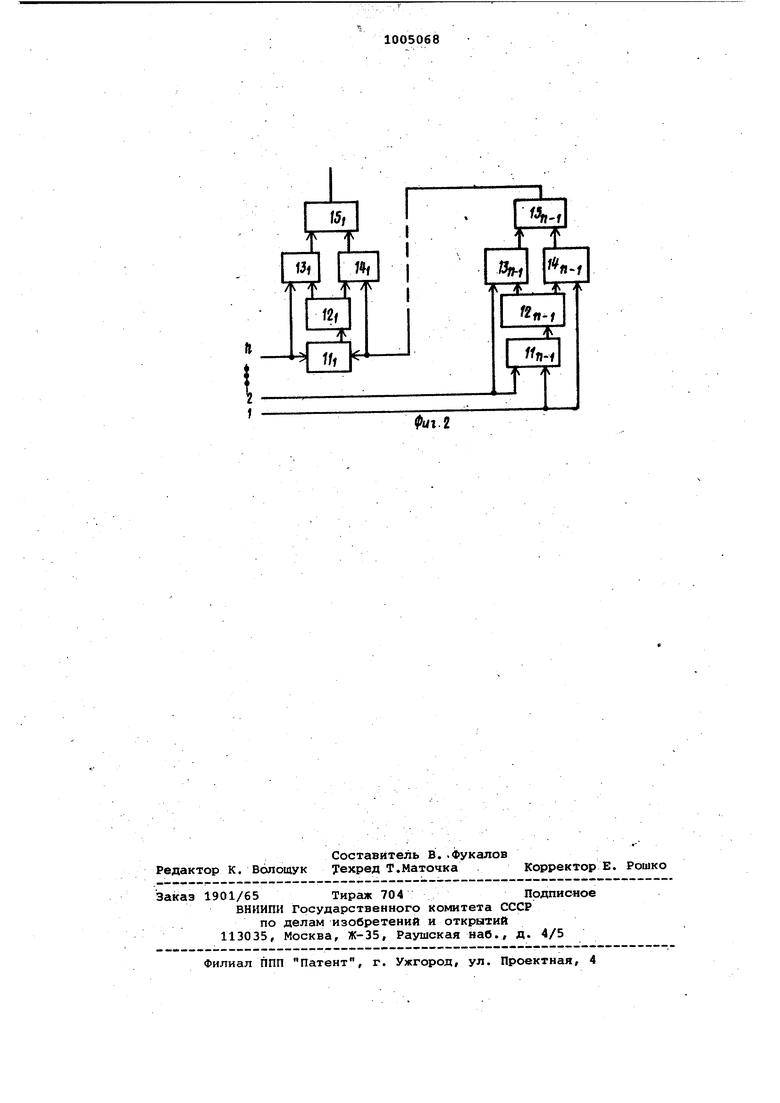

,имитации совместной и параллельной обработки нескольких файлов или блоков (порций) информации, как это производится согласно мультипрограммным режимам обеспечения ЭВМ третьего поколения. Цель изобретения - повышение быст родействия . Поставленная цель достигается тем, что в устройство, содержащее генератор случайных напряжений, коммутатор, блок сравнения, источник стабилизированного напряжения и блок регистрации, выход источника стабили зированного напряжения подключен к одному из входов блока сравнения, введены реле времени, коммутатор, дополнительный блок сравнения/ дополнительный коммутатор, п интеграторов и блок источников стабилизированндго напряжения, причем выход генератора случайных напряжений подключей через коммутатор к входам интеграторов, выходы которых подключены к входам первой группы дополнительного блока сравнения соответственно, к входам второй группы которого подключены выходы блока источников стабилизированного напряжения соответственно, выход дополнител ного блока сравнения соединен с управляющим входом коммутатора, к входу запуска которого подключен выход реле времени, - входы дополнител ного коммутатора подключены к выхода соответствующих интеграторов, а выход - к входу блока сравнения, выход которого подключен к входу блока регистрации. Кроме того, дополнительный коммутатор содержит (п-1) схем сравнения (п-1) триггеров, две группы по ( элементов И и (п-1) элементов ИЛИ, первый вход (п-1)-и схемы сравнения и первый вход (п-1)-го элемента И второй группы объединены и являются первым входом дополнительного коммутатора, второй вход (п-1)-и схемы сравнения соединен с первым входом (п-1)-го элемента И первой группы и является вторым входом дополнитель ного коммутатора, первый вход k-й схемы сравнения (kel, D-2) подключен к первому входу k-ro элемента И первой группы и является ()-ым входом дополнительного коммутатора, выходы схем сравнения соединены с. единичныг/ш входами соответствующих триггеров, «улевые выходы триггеров соединены с вторыми входами соответствующих элементов И первой группы, единичные выходы триггеров подключены к. ВТОРЫМ входам соответствующих элементов И второй группы, выход 1-ых элементов И первой и второй группы (i««1, п-1) соединены с входами i-ro элемента ИЛИ, выход первого элемента ИЛИ является выходом дополнительного коммутатора, а выход j-ro элемента ИЛИ соединен с вторыми Входами .(j-l)-ro элемента И второй группы и вторым входом (j-1)-й схемы сравнения. На фиг. 1 представлена структурная схема устройства для моделирования поточной системы обработки информации; на фиг. 2 - функциональ-. ная схема блока переключателей. Устройство содержит генератор 1 случайных напряжений, блок 2 сравне ния, источник 3 стабилизированного напряжения и блок 4 регистрации, выход источника 3 стабилизированного напряжения подключен к одному из входов блока сравнения, выход которого подключен к входу блока регистрации, реле 5 времени, коммутатор 6, дополнительный блок 7 сравнения, дополнительный коммутатор 8, блок 9 интеграторов и блок 10 источников стабилизированного напряжения, причем выход генератора случайных напряжений 1 подключен через коммутатор 6 к входам интеграторов 9 +9у, блока 9 интеграторов, выходы которых подключены к входам дополнительного блока 7 сравнения, к другим входам Которого подключены выходы блока 10 источников стабилизированного напряжения, выход дополнительного блока 7 сравнения подключен к второму входу коммутатора 6, к третьему входу которого подключен выход реле 5 времени, входы коммутатора подключены к соответствующим выходам блока 9 интеграторов, а выход - к входу блока 2 сравнения. Дополнительный коммутатор содер- , жит схемы сравнения 11 -11у, , триггеры ±2j , две группы элементов И , , 14.-14 , элементы ИЛИ IS, -ISh-t. Генератор 1 представляет собой типовой генератор случайных электрических напряжений инфранизкой частоты. Генератор случайных процессов вырабатывает реализацию случайного процесса изменения напряжения с требуемым законом распределейия. В блоке б используются транзисторные ключевые и переключающие схемы. В качестве реле времени блока 5 могут использоваться одновибраторы или подобные спусковые релаксационные генераторы. Блок 9 состоит из п типовых операционных усилителей, работающих в режиме интегрирования, число которых равно количеству моделируеких этапов обработки информации. В блоки 2 и 7 схем сравнения входят амплитудные селекторы. Устройство работает следующим обраэом. В исходном состоянии триггеры 12ц +12 ,i, находятся в иулевом состоянии и поддерживают в открытом состоянии элементы И 13;,-13у,. . Коммутатор б переключен в подготовительный режим, во время которого производится ввод случайного напряжения на интеграторы 9 +9у, блока 9 интеграторов. С выхода блока 5 реле времени через заданные интервалы времени на первый вход коммутатора б поступают последовательные, сигналы, в соответ ствии с которыми прекращается ввод случайных напряжений на интеграторы и блока 9. При поступлении последнего сигнала с выхода реле 5 времени на вход коммутатора б начин ется рабочий режим интегратора 9 . Линейно изменяющееся напряжение на выходе каждого интегратора предстайляет отдельную реализацию полуслучайной функции, моделирующей объем информации, обработанной на соответствующем этапе ее преобразования . Выходное напряжение, снимаемое с выходов блока 10 стабилизированно го напряжения, соответствует объему информации, который требуется обработать на определенном этапе технологического процесса, после которо начинается следующий этап. Напряжение с выхода источника стабилизированного напряжения 3 моделирует общий объем подлежащей обработке йнфорд4ации каждым интегратором. Процесс обработки оканчивается после ее Обработки последним интегратором . Линейно изменяющееся напряжение с выхода интегратора 9 блока 9 поступает на первый вход блока срав нения 7. В момент совпадения линейн изменяющегося напряжения и напряжения, поступающего с первого вьххода блока 10 источников стабилизированного напряжения на (п+1-)-й вход бло ка сравнения 7, на выходе блока 7 появляется сигнал, которьИ переключает коммутатор 6 таким образом, чтобы интегратор 9t блока 9 переше в рабочий режим. При этом интегратор 9 блока 9 продолжает генериро вать линейно изменяющееся напряжени Процесс последовательного переключения интеграторов в рабочий реж ,продолжается до тех пор, пока все интеграторы не начнут генерировать линейно изменяющееся напряжение. Появление на выходах блока 9 интегр торов одновременно нескольких линей но изменяющихся напряжений имитируе процесс совместного выполнения нескольких этапов технологического процесса обработки информации. Напряжения с выходов.интеграторов подается на вход коммутатора 8. На каждую из схем сравнения 11 поступает напряжение с выхода (п+1-i)-го интегратора и напряжение с выхода элемента ИЛИ . . На входы схемы сравнения 11ц-1 поступают напряжения с выходов интеграторов 9 и 9 блока 9. В момент равенства напряжений, поступающих на входы схемы сравнения 11, она формирует сигнал, переводящий триггер 12 в единичное состояние. При нулевом состоянии триггера 12 на выход элемента ИЛИ 15 проходит напряжение с выхода интегратора () блока 9. Единичное состояние триггера 12у запирает элемент И 13 и отпирает элемент И 14i. При этом на выходе элемента ИЛИ 15 появляется напряжение с выхода элемента ИЛИ 15;,.; или с выхода интегратора . . Выходное напряжение коммутатора 8, представляющее собой реализацию кусочно-линейной полуслучайной функции, моделирует случайный процесс появления на выходе системы потока обработанных данных. Напряжение с выхода коммутатора 8 поступает на первый вход блока 2 сравнения, на второй вход которого поступает нап ряжение с выхода источника 3 стабилизированного напряжения. При равенстве входных напряжений блок 2 формирует сигнал окончания обработки информации, который фиксируется в блоке регистрации и сбрасывает триггеры 12 и переводит коммутатор б в подготовительный режим. Такой принцип работы устройства позволяет моделировать процесс одновременной обработки нескольких файлов информации, имитируя тем сгшым мультипрограммный режим работы системы обработки данных. Введение дополнительных блоков позволяет расширить функциональные возможности устройства, моделирующего процессы обработки информации современными средствами, использующими мультипрограммной режим работы. Формула изобретения 1. Устройство для моделирования поточной системы обработки информации , содержащее генератор случайных напряжений, блок сравнения, источник стабилизированного напряжения и блок регистрации, выход источника стабилизированного напряжения подключен к одному из входов блока сравнения, отличающеес я тем, что, с целью повышения быстродействия, оно дополнительно содержит реле времени, дополнительный блок сравнения, дополнительный коммутатор п интеграторов и блок источников стабилизированного напряжения, причем выход генератора случайных напряжений подключен через коммутатор к входам интеграторов, выходы которых подключены к входам первой группы допрлниTeJibHoro блока сравнения соответственно, к входам второй группы которого подключены выходы блока источников стабилизированного напряжения соответственно, вьЬсод дополнительного блока сравнения соединен с управляющим входом коммутатора, к входу запуска которого подключен выход реле времени, входы дополнительного коммутатора подключены к выходам соответствующих интеграторов, а выход к входу блока сравнения, выход которого подключен к входу блока регистрации .

2. Устройство по П.1, отличающееся тем,, что дополнительный коммутатор содержит (п-1) схем сравнения, (п-1) триггеров, две группы по (п-1) элементов И и (п-1) элементов ИЛИ, первый вход (п-1)-и схемы сравнения и первый вход (n-l)-ro элемента И второй группы объединены и являются первым входом дополнительного коммутатора, второй вход (п-1)-и схемы сравнения соединен с первым входом (п 1) -го

элемента И первой группы и является вторым входом дополнительного коммутатора, первый вход k-й cxehoj сравнения (, п-2) подключен к первому входу k-ro элемента И первой группы

и является (n-1+k)-ЫM входом ДОПОЛ :

нительного коммутатора, выходы схем сравнения соединены с единичными входами соответствующих триггеров, нулевые выходы триггеров соединены с вторыми входси и соответствующих элементов И первой группы, единичные выходы триггеров подключены к вторым входам соответствующих элементов И второй группы, выходы i-ых элементов И первой и второй групп (, п-1) соединены с входами i-ro элемента ИЛИ, выход первого элемента ИЛИ является выходом дополнительного коммутатора, а выход j-ro элемента. ИЛИ (, п-1) соединен с вторыми входами (j-l)-ro элемента И второй группы и вторым входом (-1)схемы сравнения.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР №631925, кл. G 06 F 15/20, 1977,

2.Дружинин Г.В. Надежность автоматизированных систем. М., Энергия 1977, с. 503-506 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования систем обработки данных | 1982 |

|

SU1018129A1 |

| Устройство для моделирования технических систем | 1983 |

|

SU1179275A1 |

| Устройство для моделирования процессов движения поездов | 1982 |

|

SU1018130A1 |

| Устройство для моделирования процессов движения поездов | 1984 |

|

SU1196909A1 |

| Устройство для моделирования систем массового обслуживания | 1983 |

|

SU1164725A1 |

| Устройство для моделирования систем управления | 1980 |

|

SU935965A1 |

| Устройство для определения статистических параметров случайных сигналов | 1980 |

|

SU934486A2 |

| Устройство для контроля временных параметров реле | 1980 |

|

SU932464A1 |

| Многоканальное регистрирующее устройство | 1988 |

|

SU1698899A1 |

| Устройство для оценки профессиональной пригодности операторов автоматизированных систем управления | 1982 |

|

SU1068974A1 |

Авторы

Даты

1983-03-15—Публикация

1981-11-02—Подача