рых подключены соответственно к первым входам элементов И пятой группы, вторые входы которых соединены с выходом первой схемы сравнения и входом элемента НЕ, выход которого соединен с вторьм входом третьего элемента И четвертой группы элементов И, выходы элементов Н пятой группы соединены с вторыми входами элементов Ичетвертой группы соответственно, выход второго элемента И является выходом устройства, счетный вход второго, триггера является входом переключения режимов работы устройства, о т лич ающее с я тем, что, с целью повышения точности моделирования, оно двполнительно содержит третью схему сравнения, третий элемент И,

6909

сумматор, причем первый вход третьей схемы сравнения подключен к выходу интегратора, второй вход третьей схемы сравнения соединен с вторьм выходом источника опорных напряжений, выход третьей схемы сравнения подключен к первому входу третьего элемента И, второй вход которого соединен с выходом интегратора, выход третьего элемента И соединен с первым входом сумм тора, второй вход которого соединен с вторым выходом источника опорных напряжений, выход сумматора подключен к информационному входу запоминающего блока и второму входу второй схемы сравнения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования процессов движения поездов | 1982 |

|

SU1018130A1 |

| Многоканальный интерполятор функций | 1986 |

|

SU1361588A1 |

| Адаптивный амплитудный анализатор | 1982 |

|

SU1078435A1 |

| Устройство для моделирования поточной системы обработки информации | 1981 |

|

SU1005068A1 |

| Генератор функций | 1982 |

|

SU1057966A1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА ОБНАРУЖЕНИЯ И САМОНАВЕДЕНИЯ | 2010 |

|

RU2439608C1 |

| УСТРОЙСТВО АВТОЛиТИЧЕСКОГООБНАРУЖЕНИЯ ПЕРЕГРЕТЫХ БУКСПОДВИЖНОГО СОСТАВА | 1971 |

|

SU432029A1 |

| УСТРОЙСТВО ДЛЯ АВТОМАТИЧЕСКОГО КОНТРОЛЯ ГЕОМЕТРИЧЕСКИХ НЕРОВНОСТЕЙ КОЛЕСНЫХ ПАР ПОДВИЖНОГО СОСТАВА12 | 1973 |

|

SU384711A1 |

| Устройство для моделирования распространения возмущений в сложной системе | 1983 |

|

SU1130883A1 |

| Устройство для моделирования распространения возмущений | 1982 |

|

SU1056224A1 |

yGTPOfiGTBO ДЛЯ МОДЕЛИРОВАНИЯ nPOUECGOB ДВИЖЕНИЯ ПОЕЗДОВ, содержащее группу генераторов случайных напряжений, группу сумматоров, группу запоминающих блоков, интегратор, запоминающий блок, источник опорных напряжений, пять групп элементов И по три элемента И в каждой, элемент НЕ, две схемы, сравнения, первый и второй триггеры, элемент задержки, два элемента И, группу амплитудных дискриминаторов, дифференциальный усилитель, первый выход источника опорных напряжений подключен к первьв входам сумматоров группы, выходы генераторов случай ных напряжений соединены с вторыми, входами сумматоров группы, входы которых соединены соответственно с прямьми входами элементов И первой группы, инверсные входы которых соединены с выходом элемента задержки, первыми входами первого и второго элементов И, выходы элементов И первой группы подключены к входам соответствующих запоминающих блоков группы, выходы которых соединены с первь1ми входами элементов И второй группы, вторые входы которых подключены соответственно к выходам элементов И третьей группы, выходы элементов И второй группы соединены с входом интегратора, выход которого подключен к первому входу дифференциального усилителя, второй вход которого соединен с первым выходом запоминающего блока и первым входом первой схемы сравнения, второй вход которой подкхпочен к второму выходу источника опорных напряжений н первому входу второй схемы сравнения, вход разрещения считьюания запоминающего блока подключен к первому W выходу первого триггера и входу элемента задержки, вход запрещения считывания запоминающего блока соединен § с вькодом второй схемы сравнения и вторьм входом второго элемента И, второй выход запоминающего блока соединен с первьм входом первого тригсо о; гера, второй вход которого является входом запуска устройства, первые с входы элементов И четвертой группы о со соединены с выходом элемента задержки, выходы элементов И четвертой группы подключены соответственно к Первым входам элементов И третьей группы, вторые входы которых соединены с первым выходом второго триггера, второй выход которого подключен к второму входу первого элемента И, выхйд которого соединен с вторым входом третьего элемен1а И второй группы,, выход дифференциального усилителя соединен с входами амплитудных дискриминаторов группы, выходы кото

Изобретение относится к вычислительной технике и может быть использовано при моделировании сложных процессов движения транспортных средств, а также при составлении графиков движения поездов.

Цель изобретения - повышение точности .моделирования.

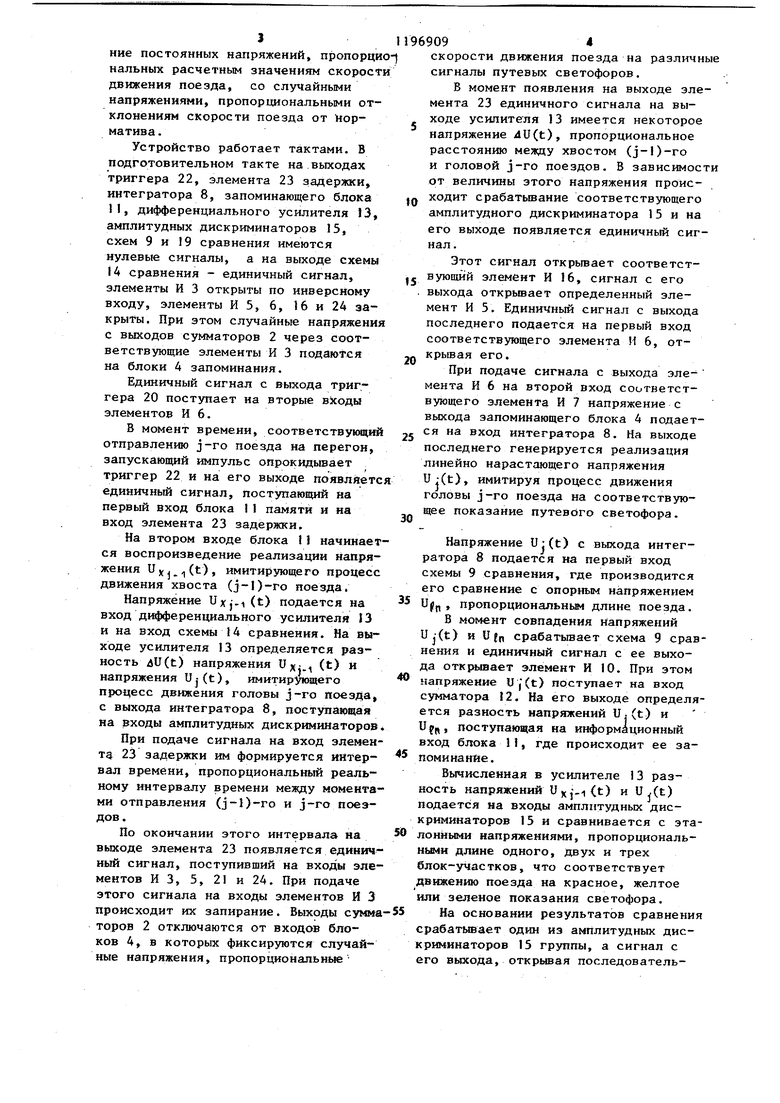

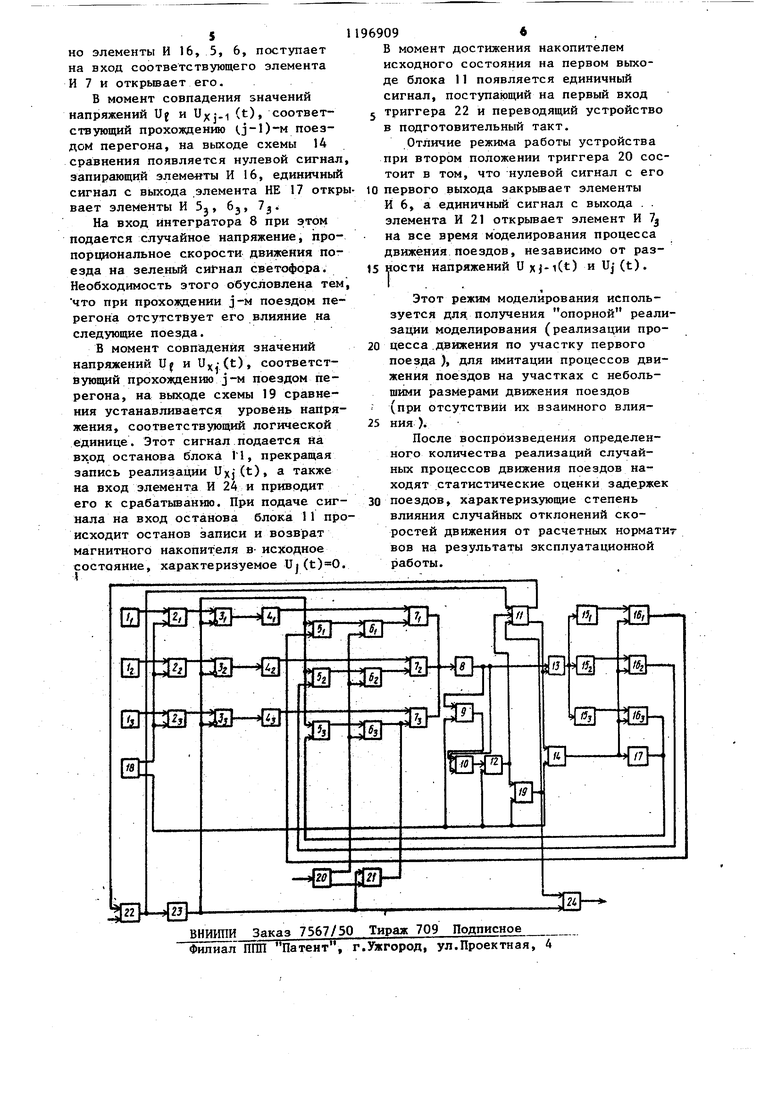

На чертеже представлена схема устройства для моделирования процессов движения поездов.

Устройство содержит группу генераторов 1 случайных напряжений, группу сумматоров 2, первую группу элементов И 3, первую группу запоминающих блоков 4, четвертую группу элементов И 5, третью 6 и вторую 7 группы элементов И, интегратор 8, третью схему 9 сравнения, третий элемент И 10, первый запоминшощий блок 11, второй сумматор J2, дифференциальный усилитель 13, первую схему 14 сравнения, группу амплитудных дискриминаторов 15, пятую группу элементов И 16, элемент НЕ 17 источник 18 опорных напряжений, вторую схему 19 сравнения, второй триггер 20, первый элемент И 21, первый триггер 22, элемент 23 задержки, второй элемент И 24.

Устройство для моделирования процессов движения поездов работает следующим образом.

- Триггер 20 два положения и задает режимы работы устройства. В первом положении на первом выходе триггера 20 имеется единичный сигнал, а на втором - нулевой. При этом

устройство имитирует процессы движения поездов с учетом их взаимного влияния, т.е. на различные (зеленые, желтые или красные ) показания путевых светофоров.

Во втором положении на первом выходе триггера 20 имеется нулевой сигнал, а на втором - единичный. В этом случае устройство моделирует

процесс движения поезда на зеленые показания светофоров. Необходимость использования данного режима работы связана с тем, что воспроизведенный устройством процесс движения первого

поезда является опорной реализацией моделирования.

Устройство при первом положении триггера 20 работает следукя м образом.

Каждый из генераторов 1 вырабатывает значения случайных напряжений, пропорциональные отклонениям от расчетной величины скорости движения поезда на зеленое (К), желтое

(1) и красное (Ц) показание путевого светофора. Эти напряжения подаются на входы соответствующих сумматоров 2, где происходит суммирова3

ние постоянных напряжений, пропорцио нальных расчетным значениям скорости движения поезда, со случайными напряжениями, пропорциональными отклонениям скорости поезда от Норматива .

Устройство работает тактами. В подготовительном Такте на выходах триггера 22, элемента 23 задержки, интегратора 8, запоминающего блока II, дифференциального усилителя 13, амплитудных дискриминаторов 15, схем 9 и 19 сравнения имеются нулевые сигналы, а на выходе схемы 14 сравнения - единичный сигнал, элементы И 3 открыты по инверсному входу, элементы И 5, 6, 16 и 24 закрыты. При этом случайные напряжения с выходов сумматоров 2 через соответствующие элементы И 3 подаются на блоки 4 запоминания.

Единичный сигнал с выхода триггера 20 поступает на вторые входы элементов И 6.

В момент времени, соответствующий отправлению j-ro поезда на перегон, запускающий импульс опрокидывает триггер 22 и на его выходе появляетс единичньй сигнал, поступающий на первый вход блока 11 памяти и на вход элемента 23 задержки.

На втором входе блока 11 начинается воспроизведение реализации напряжения (t), имитирующего процесс движения хвоста (j-I)-ro поезда.

Напряжение Uxj-i (t) подается на вход дифференциального усилителя 13 и на вход схемы 14 сравнения. На выходе усилителя 13 определяется разность 4U(t) напряжения ., (t) и напряжения Uj(t), имитирующего процесс движения головы j-ro поезда, с выхода интегратора 8, поступающая на входы амплитудных дискриминаторов

При подаче сигнала на вход элемента 23 задержки им формируется интервал време.ни, пропорциональный реальному интервалу времени между моментами отправления (j-l)-ro и j-ro поеэдов.

По окончании этого интервала на выходе элемента 23 появляется единичный сигнал, поступивший на входы элементов ИЗ, 5, 21 и 24. При подаче этого сигнала на входы элементов И 3 происходит их запирание. Выходы сумматоров 2 отключаются от входов блоков 4, в которых фиксируются случайные напряжения, пропорциональные

9094

скорости движения поезда на различные сигналы путевых светофоров.

В момент появления на выходе элемента 23 единичного сигнала на выходе усипителя 13 имеется некоторое напряжение 4U(t), пропорциональное расстоянию между хвостом (j-l)-ro и головой j-ro поездов. В зависимости от величины этого напряжения происходит срабатьшание соответствующего амплитудного дискриминатора 15 и на его выходе появляется единичный сигнал .

Этот сигнал открьгеает соответствующий элемент И 16, сигнал с его выхода открьшает определенный элемент И 5. Единичный сигнал с выхода последнего подается на первый вход соответствующего элемента И 6, открьшая его.

При подаче сигнала с выхода элемента И 6 на второй вход соответствующего элемента И 7 напряжение с выхода запоминающего блока 4 подается на вход интегратора 8. На выходе последнего генерируется реализация линейно нарастшощего напряжения U-(t), имитируя процесс движения

головы J-ro поезда на соответствующее показание путевого светофора.

Напряжение U: (t) с выхода интегратора 8 подается на первый вход схемы 9 сравнения, где производится его сравнение с опорным напряжением

, пропорциоиальн1Л4 длине поезда.

В момент совпадения Напряжений U;(t) и и fn срабатывает схема 9 сравнения и единичный сигнал с ее выхода открывает элемент И 10. При этом

напряжение U((t) поступает на вход сумматора 12. На его выходе определяется разность напряжений U.(t) и , поступающая на информационный вход блока 11J где происходит ее запоминание.

Вычисленная в усилителе 13 разность напряжений и (t) и UXt) подается на входы амплитудных дискриминаторов 15 и сравнивается с эталонными напряжениями, пропорциональньмн длине одного, двух и трех блок-участков, что соответствует движению поезда на красное, желтое или зеленое показания светофора.

На основании результатов сравнения срабатывает один из амплитудных дискриминаторов 15 группы, а сигнал с его выхода, открывая последователь

| Устройство для моделирования условий и режимов движения на автомобильной магистрали | 1972 |

|

SU451104A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для моделирования процессов движения поездов | 1982 |

|

SU1018130A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-12-07—Публикация

1984-06-08—Подача