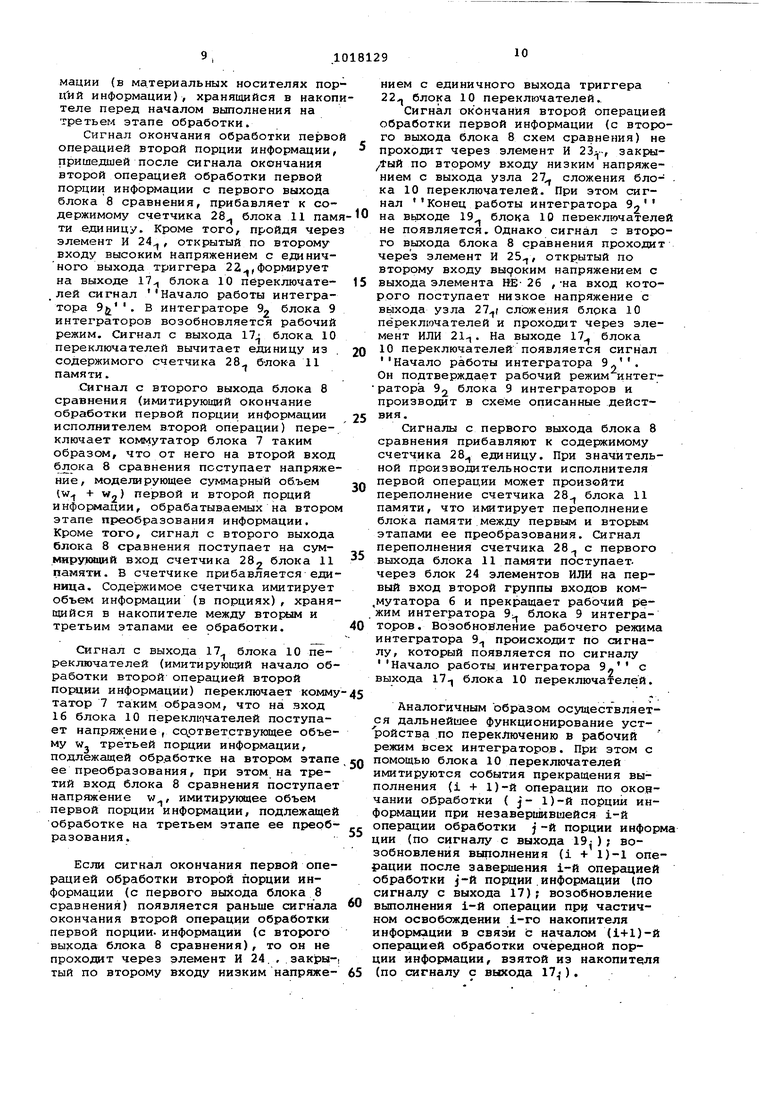

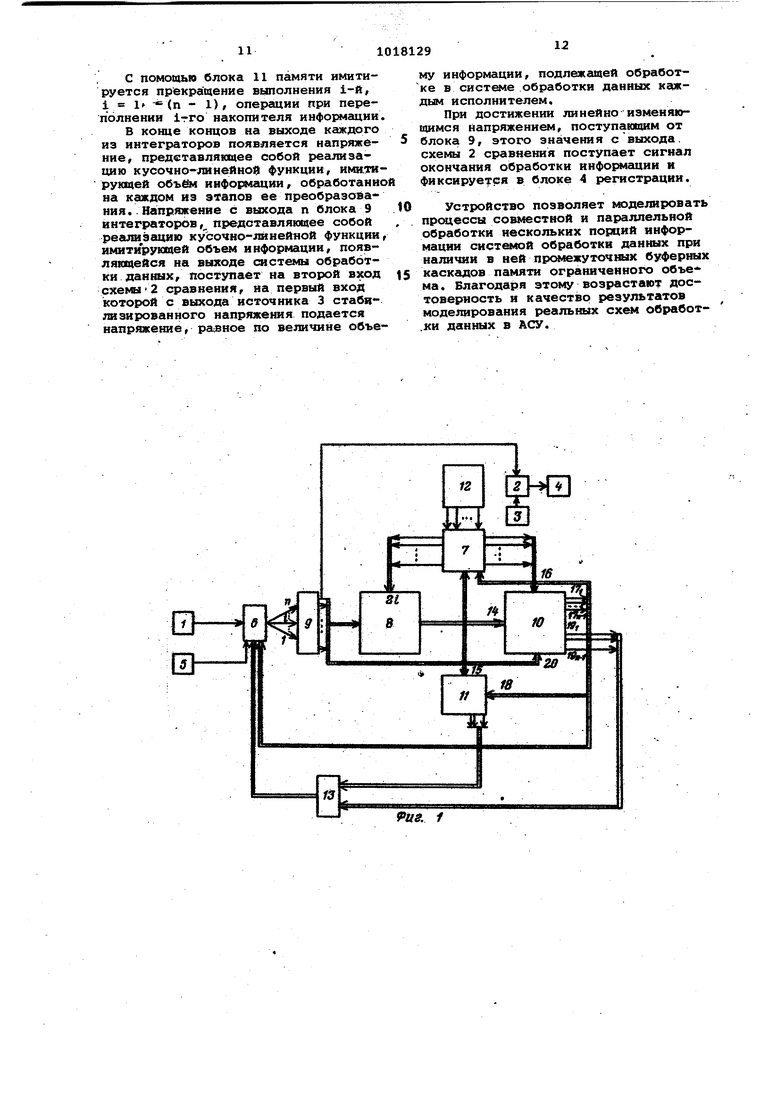

ветствующего элемента ИЛИ группы, второй вход которого соединен с выходом соответствующего элемента И третьей группы, первый вход которого подключен к выходу соответствующего элемента НЕ группы, второй вход соответствующего элемента И третьей группы подключен к первому входу Ьоответствующего элемента И первой группы, .выходы элементов ИЛИ группы являются выходами первой группы блока переключателей, второй группой выходов которого являются выхода элементов И первой группы, первым входом первой группы входов блока переключателей является второй вход первого элемента И второй группы, т-м входом первой группы входов блока переключателей {т 2 h -2) является второй вход {гп-1)-го элеме та И первой группы, который срединен с вторым входом т-го элемента И второй группы, последним ( п - 1)-м входом первой группы входов блока переключателей является второй вход последнего ( г -1 )-го элемента И первой группы, второй группой входов блока переключателей являются соответственно Первые входы узлов сложения группы, первым входом третьей группы входов блока переключателей является второй вход первого узла сложения группы, -м входом третьей группы входов блока переключателей ( ic 2, п - 1) является третий вход (. - 1)-го узла сложения группы который соединен с вторым входом (сто узла сложеяия группы/ последним ц-м входом третьей Группы, входов блока переключателей является третий вход (п- 1)-го узла сложения группы Изобретение относится к вычислительной технике и может быть использовано при проектировании систем обработки данных и оптимизации их структуры по критерию максимальной оперативности обработки информации в автоматизированных системах управления. Известно устройство для моделирования cиcteм сбора и обработки информации, содержащее блоки приема и формирования запроса, счетчик., дешиФ ратор, коммутатор, элементы И, ИЛИ, триггеры и блок обработки запросов. Выходы блоков приема подключены к входам блока формирования запроса и счетчика, которого через дешиф ратор и коммутатор подключен к входу блока обработки запросов. Выходы блока формирования запросов подсоеди нены к единичным входам соответствукяцих триггеров, выходы которых под ключены к входам элементов И, выходы которых подключены к входам блока обработки запросов Недостатком устройства является невысокая точность моделирования рюальных систем обработки данных нзза невозможности имитации совместной; и параллельной обработки нескольких порций инфОЕяиации при наличии в системе накопителей информации ограниченного объема. . ;.. Наиболее близким по технической сущности к изобретению является устройство для моделирования процессов пакетной обработки инфо алации. содержащее генератор случайных aianряжений, блок интеграторов, блок схем сравнения, источник стабилизированного напряжения, блок регистрации, реле времени, блок коммутаторов, блок переключателя, блок источт НИКОВ стабилизированного напряжения, схему сравнения, выход генератора случайных напряжений через блок коммутаторов соединен с входами блока интеграторов, выходы которого подключены соответственно к входам блока схем сравнения, выход источника стабилизированного напряжения соединен.с первым входом схемы сравнения, выход которого подключен к входу блока регистрации, выход реле времени подключен к первому управляющему входу блока коммутаторов. Устройство позволяет производить электрическое моделирование обработки пакетов данных 2 J. Недостатком устройства является невозможность его применения для моделирования многоэтапных систем обработки данных с промежуточными блоками памяти ограниченного объема, Цель изобретения - расширение функциональных возможностей устройства за счет воспроизведения режимов промежуточного накопления обработанной каждом из этапов инфор-, мации, Поставленная цель достигается тем, что в устройство для моделирования систем обработки данных,содержащеё генератор случайных напряжений, выход которого соединен с информационным входом первого .блока коммутаторов, выходы которого соединены соответственно с входами первой группы блока сравнения, выход реле времени соединен с управляющим входом первого блока коммутаторов, блок переключателей, блок источников стабилизированного напряжения, источник стабилизированного напряжения, выход которого соединен с первым входом схемы, сравнения, выход которой подключен к входу блока регистрации, блок интеграторов, -дсшолнительно введены второй блок коммутаторов, блок блок элементов ИЛИ, причем памятиi выходы блока источников стабилизированных напряжений соединены соответственно с первой группы второго блока коммутаторовfвыходы второй группы входов которого соединены соответственно с выходами блока срав нения, входами первой группы блока переключателей и входами первой группы блока памяти, входы второй группы входов которого подключены к выходам первой группы блока переключателей, входам.третьей группы второго блока коммутаторов и управляющим входам первой группы первого блока коммутаторов соответственно, выходы первой группы второго блока коммутаторов соединены соответственно с входами второй группы блока сравнения, выходы второй группы второго блока коммутаторов соединены соответственно с входами второй груп пы блока переключателей, входы третьей группы входов которого соединены соответственно .с выходами блока интеграторов, выходы второй группы блока переключателей подключены соответственно к входам первой группы блока элементов ИЛИ, входы второй группы входов которого соединены с выходами блока памяти соответственно, выходы блока элементов ИЛИ подключены к управляющим входам второй группы первого блока коммутаторов, h-fli выход блока интеграторов соединен с вторым входом схемы сравнения. Блок переключателей содержит группу триггеров, три группы элементов И, группу Элементов ИЛИ, группу элементов НЕ и группу узлов сложения причем выход каждого узла сложения г;руппы соединен с входами соответствующего элемента НЕ группы и элемента И первой группы, выход которого . подключен к единичному, входу соответствующего триггера группы, единичный выход которого соединен с первым входом соответствующего элемента И второй группы,, выход которо го подключен к нулевому входу соответствующего триггера группы и перво му входу соответствующего элемента ИЛИ группы,второй вход которого соединен с выходом соответствующего эле мента И третьей группы, первый вход которого подключен к выходу соответствующего элемента НЕ группы,второй вход соответствующего элемента И третьей группы подключен к первому входу соответствующего элемента И первой группы, выходы элементов ИЛИ группы являются выходами первой группы блока переключателей, второй группой выходов которого являются выходы элементов И первой группы, первым входом первой группы входов блока переключателей является второ вход первого элемента И второй груп пы, т-м входов первой группы входов блока переключателей (т 2, t%- 2) является второй вход (т- I)-го элемента И первой группы, соединен с вторым входом fn- го элемен та И второй группы, последним (и - 1)-м входом первой группы входов блока переключателей является второй вход последнего (h- 1)-го элемента И первой группы, второй группой входов блока переключателей являются соответственно первые входы узлов сложения группы, первым входом третьей группы входа блока переключателей вляется; второй вход первого узла сложения группы, К-м входом третьей группы входов блока переключателей (1 2, п -1) являет-, ся третий вход ( - 1)-го узла сложения группы, который соединен с вторым входом tc -го узла сложения группы, последним п -м входом третьей группы входов блока.переключателей является третий вход (п -.1)-го узла сложения группы. На фиг.1 приведена схема устройства для моделирования систем обработки данных; на фиг. 2 и 3 - функциональные схемы блока переключателей и блока памяти. Устройство содержит генератор 1 случайных напряжений, схему 2 сравнения j источник 3 стабилизированного напряжения и блок 4 регистрации, выход источника 3 стабилизированного напряжения подключен к первому входу схемы 2 сравнения, выход которой подключен к входу блока 4 регистрации, реле 5 времени, первый б и второй 7 блоки коммутаторов, блой 8 сравнения, блок 9 интеграторов, блок 10 переключателей, блок 11 памяти, блок 12 источников стабилизированного напряжения,блоки 13 элем нтов ИЛИ, причем выход генератора 1 случайных напряжений подключен через первый блок 6 коммутаторов к входам блока 9 интеграторов, выходы которого подключены к первой группе входов блока 8 сравнения, вторая группа входов блока 8 сравнения соединена через второй блок 7 коммутаторов с выходами блока 12 источников стабилизированного напряжения, выходы блока 8 сравнения соединены с первой группой входов 14 блока 10 (переключателей, с первой группой входов 15 блока 11 памяти и с второй группой входов-второго блока 7 коммутаторов, вторая группа входов 16 блока 10 переключателей соединена соответственно с второй группой выходов второго блока 7 коммутаторов, первая группа выходов 17 блока 10 переключателей соединена с первой группой управляюкдах входов первого блока 6 коммутаторов, второй группой входов 18 блока 11 памяти и третьей группой входов второго блока 7 KONMyTaTopOB, вторая группа выходов 19 блока 10 переключа:телей соединена через блок 13 элементов ИЛИ с второй группой -управляющих входов f

первого блока б коммутаторов, третья группа входов 20 блока 10 переключателей сое,цинена с выходами блока 9 интеграторов, выход п-го интегратора -подключен к второму входу схемы 2 сравнения, группа выхо лов блока 11 памяти соединена с соответствующими входами блока 13 элементов ИЛИ.

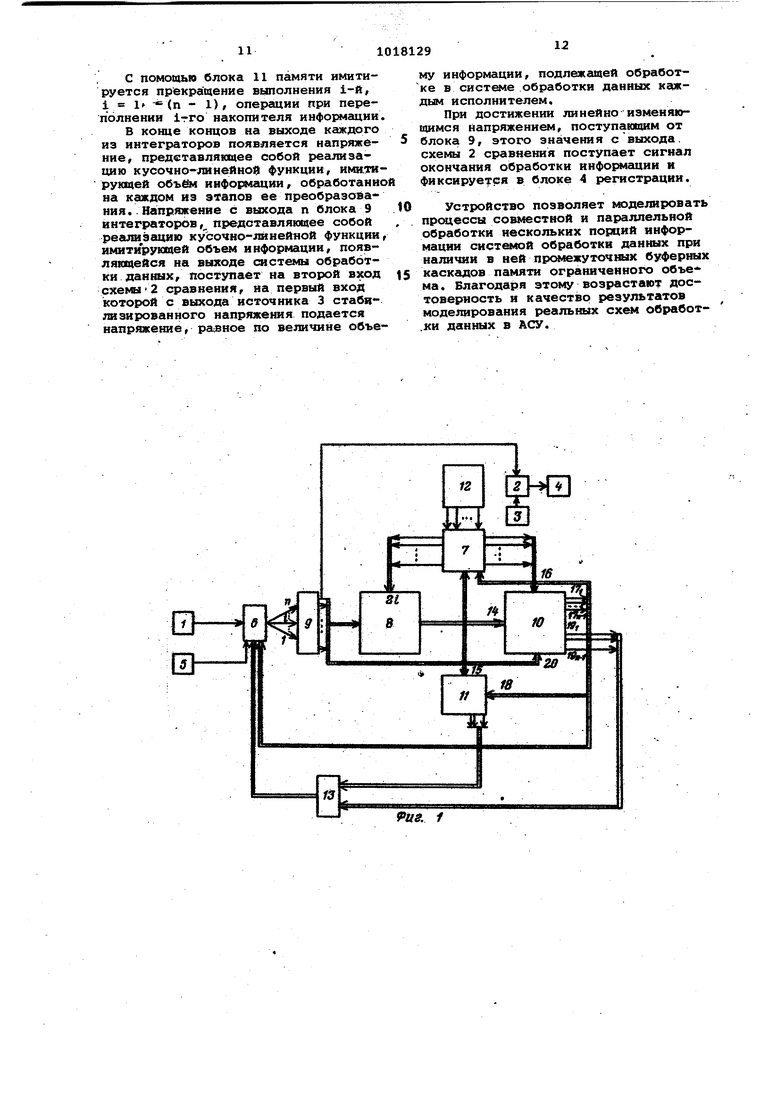

В блок 10 переключателей входят группа элементов ИЛИ 21, группа триг геров 22, первая группа элементов И 23, вторая группа элементов И 24, третья группа элементов И 25, группа элементов НЕ 26, группа узлов 27 сложения.

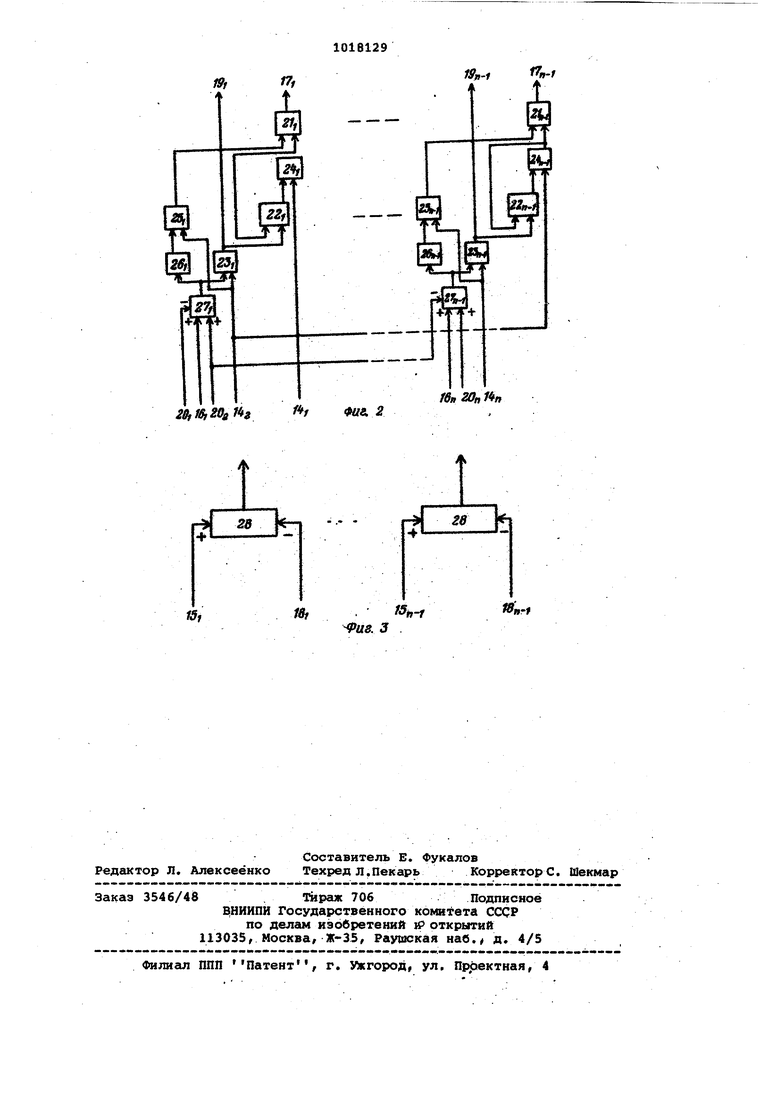

В блок 11 памяти входит группа реверсивных счетчиков 28. Объем каждого i-го счетчика имитирует объем памяти между i -м и (i + 1)-м этапами обработки и соответствует максимально возможному количеству размещаемых в памяти материальных носителей порций информации, число этапов равно.

Блок 12 содержит га источников ста билнзированного напряжения. Величина m равна количеству порций информации обрабатываемой в системе обработки данных. Электрические напряжения с выходов блока 12 моделируют объемы информации, содержащиеся в отдельных порциях информации, подлежащих обработке. Величина напряжения с выхода источника 3 стабилизированного напряжения равна общему объему обрабатываемой в системе обработки данных информации.

Сущность принципа действия данног устройства заключается в том, что объем информации, обработанной исполнителем i-й операции, имитируется электрическим напряжением,представляющим -собой реализацию полуслучайной кусочно-линейной функции. Скорость оста электрического напряжения пропорциональна значению произ водительности исполнителя операции. Величина скорости становится равной нулю в моменты времени, соответствующие окончанию 1-й операции обработки очередной ( j- 1)-1 порции инфор мации при незаверайвшейся обработке (i - 1)-й операцией j-и порции информации и переполнению i-ro блока памяти, расположенного между i-й и (i + 1)-й операциями обработки информации. В момент завершения (i 1)-й операции возобновляется рост линейно изменяющегося напряжения,, имитируюцего процесс обработки j-й порции информации 1-й операцией. В момент начала (i + 1)-й операции возобновляется рост линейно изменяющегося напряжения, имитирхющего процесс обработки информации i-й операцией.

в каждом такте моделирования воепроизводится одна реализация процесса функционирования системы обработки Данных, заключающаяся в выполнении п этапов обработки m порций информации. Суммарное количество данных, содержащихся в m порциях, представляет собой объем информации w, подлежащей обработке для вьтолнения задания. По множеству реализаций значений времени от начала выполнения первой до завершения выполнения последней операции последним исполнителем находятся статистическая функция распределения или среднее значение времени обработки информации.

Устройство работает следующим образом.

Генератор 1 случайных процессов вырабатывает реализацию случайного процесса изменения напряжения с требуемым законом распределения.

В подготовительном режиме с помощью коммутатора 6 производится вво случайных напряжений на интеграторы блока 9 интеграторов.

Исходное состояние блока 10 переключателей следующее: триггеры 22 .находятся в еди.ничном состоянии и поддерживают в открытом состоянии элементы И 24.

Исходное состояние блока 7 коммутаторов : коммутатор переключается таким образом, что на первый вход блока 8 сравнени.я поступает напряжение, имитирующее объем первой порции -информации, подлежащей обработке и с по л ни т ел ем первой операции.

Через заданные интервалы времени с вЕлхода реле 5 времени на управляющий вход блока б- коммутаторов поступают последовательности сигналов , в соответствии с которыми прекращается ввод начальных условий на интеграторы блока 9. При появлении последнего с выхода реле 5 времени начинается рабочий режим функционирования устройства. Последний сигнал с выхода реле 5 ВЕ5емёни поступает на вход блока 6 коммутаторов и переводит интегратор блока 9 интеграторов в рабочий режим. На выходе первого интегратора появляется линейно изменяющееся напряжение, которое имитирует объем информации,обработанный исполнителем на первом этапе ее преобразования.

При достижении значением моделирующего напряжения некоторого заданного уровня, равного объему первой порции информации,который необходимо обработать на первой операции до начала выполнения второй операции, на первом выходе блока 8 сравнения формируется сигнал, который поступает на вход 14 блока 10 переключателей и проходит через элемент И 24, открытый по второму входу высоким напряжением с единичного выхода триг гера 22. На выходе 17 блока 10 переключателей появляется сигнал начала работы второго интегратора. При этом триггер 22 10 переключателей сбрасывается. На выходе интегратора Sj блока -9 интеграторов появляется линейно изменяющееся напряжение, . мбделируквдее объем информации,обраб танный, исполнителем на втором этапе ее преобразования. При этом интегратор 9 блока 9 интеграторов продолжает jpa6oTy. Сигнал с первого выхода блока 8 сравнения, имитирующий окончание исполнителем первой операции обрабртки первой порции информации, переключа ет коммутатор 7 ..таким образом что на первый вход блока 8 сравнения от него поступает напряжение. моделирукадее суммарный объем ( w первой и второй порций информации, обрабатываемых на первом этапе преобразования информации. Кроме того, сигнал с первого выхо да блока 8 сравнения поступает на , вход .15 блока 1.1 памяти, являющийся суммирующим входом счетчика 28. В счётчик 28 заносится единица, что имитирует .объем информации (в порциях инфорладдии), хранящейся в накопителе между первым- и вторым этапами ее преобраэовани я. Сигнал с выхода 17 блока 10 переключателей, имитирующий начало обработки второй операцией первой порции информации переводит коммутатор 7 таким образом, что на вход 1б,блока ГО пе:реключателей поступает, напряжение w, имитирующее объем второй поЕадии информации, подлежащей обработке на первом этапе её преобразования, при этом на второй вход блока 8 сравнения поступает напряжение, имитирукицее объем первой порции информации, подлежащей обра ботке на втором эт.апе ее преобразования. Кроме того, сигнал с выхода 17 блока 10 переключателей поступает на вычитакяций вход счетчика 28 блока 11 памяти. В счетчике 28 усг танавливается ;0, что соответствует отсутствию ,информации, хранящейся в накопителе между 1 и 2-й операциями . Появление на выходах блока 9 одно временно двух, линейно изменяющихся напряжений имитирует процесс совмест ного выполнения .двух этапов технолог «/ЧПГЧ оьлтт ТТиоим Т TTTJTTv атчаттсчтэ т ла-ад-т лл ческого процесса обработки информации в системе обработки данных, причем на первом этапе обрабатывается вторая порция информации, а на .втором - первая. На входы узла 27 сложения блока 10 переключателей подаются напряжения с выходов интеграторов 9-, и 9 блока 9 интеграторов и от блока 12 источников напряжения через ксэммутатор 7 напряжения, моделирующие объем W2 втоЕ4ой порции информации, подлежащей обработке в системе обработки данных. с выхода узла 27 слоНапряжениежения блока 10 переключателейпредставляет собой разность значений суммы напряжения W-, напряжения с выхода интегратора 9 блока 9 интеграторов и напряжения с выхода интегратора 9 блока 9 интеграторов. Эта разность напряжений положительна, пока объем информации, ожидающий начала выполнения второй операции, не превышает значения w., Положительное напряжение с выхода узла 27-J сложения поддерживает в отк Ж1том состоянии элемент И 23 и, пройдя через элемент НЕ 26, запирает элемент И 25 блока 10 переключателей. В дальнейшем процесс функционирования устройства зависит от последовательности поступления сигналов окончания отдельных операций обработки различных погщий информации. Если сигнал (с второго выхода блока 8 сравнения) окончания второй операцией обработки первойпорции и 1формации появляется раньше сигнала (с первого выхода блока В сравнения) окончания первой операцией обработки второй порции информации,. то он проходит через элемент И.23 блока 10 переключателей, открытый по второму входу положительньам напря- жением с .выхода узла 27-, сложения. При этом триггер 22 переводится в единичное состояние, а на выходе 19 блока 10 переключателей формируется сигнал Конец работы интегратора 9 2 Интегратор 9 блока 9 интеграторов прекращает формирование линейно изменянвдегося напряжения. Прекращение работы интегратора 2 соответствует прекращению выполне второй операции по окончании обработки первой порции информации при неэаверишвшейся первой операцией обработки второй порции информации. Сигнал окончания второй операцией обработки первой порции информации JC второго выхода блока 8 сравнения проходит на суммирующий вход счетчика 282 блока 11 памяти и записывает в нем еди1шцу. Кроме того, он проходит через элемент и 242 блока 10 пе .. ...« . «.«....ч.. реключателей, открытый по второму входу высоким напряжением с единичного выхода триггера 22. На выходе 17 блока 10 переключателей появляется сигнал начала работы 3-го интегратора. При этом триггер 22 блока 10 переключателей сбрасывается. Сигнал с выхода 17 блока 10 переключателей вычитае1Т единицу из .содержимого счетчика 282 блока 11 памяти . Содержимое счетчика 28 имитирует объем информации (в материальных носителях порций информации), хранящийся в накопителе перед началом выполнения на третьем этапе обработки.

Сигнал окончания обработки перво операцией второй порции информации, пришедшей после сигнала окончания второй операцией обработки первой порции информации с первого выхода блока 8 сравнения, прибавляет к содержимому счетчика 28 блока 11 памяти единицу. Кроме того, пройдя через элемент И 24, открытый по второму входу высоким напряжением с единичного выхода триггера 22,формирует на выходе 17 блока 10 пёреключате лей сигнал Начало работы интегратора 9jj . В интеграторе 9 блока 9 интеграторов возобновляется рабочий режим. Сигнал с выхода 17 блока 10 переключателей вычитает единицу из содержимого счетчика 28 блока 11 памяти.

Сигнал с второго выхода блока 8 сравнения (имитирующий окончание обработки первой порции информации исполнителем второй операции) переключает коммутатор блока 7 таким образом, что от него на второй вход блока 8 сравнения поступает напряжение, моделирующее суммарный объем (w + Wj) первой и второй порций информации, обрабатываемых на втором этапе преобразования информации. Кроме того, сигнал с второго выхода блока 8 сравнения поступает на суммиру ощий вход счетчика 282 блока 11 памяти. В счетчике прибавляется единица. Содержимое счетчика имитирует объем информации (в порциях), хранящийся в накопителе между вторым и третьим этапами ее обработки.

Сигнал с выхода 17 блока 10 переключателей (имитирующий начало обработки второй операцией второй порции информации) переключает коммутатор 7 таким образом, что на вход 16 блока 10 переключателей поступает напряжение , сортветствующее объему Wj третьей порции информации, подлежащей обр.аботке на втором этапе ее преобразования, при этом на третий вход блока 8 сравнения поступает напряжение w , имитирующее объем первой порции информации, подлежащей обработке на третьем этапе ее преобразования.

Если сигнал окончания первой операцией обработки второй порции информации (с первого выхода блока 8 сравнения) появляется раньше сигнала окончания второй операции обработки первой порции, информации (с второго выхода блока 8 сравнения), то он не проходит через элемент И 24. , .закрытый по второму входу низким напряжением с единичного выхода триггера 22 блока 10 переключателей.

Сигнал окончанйя второй операцией обработки первой информации (с второго выхода блока 8 схем сравнения) не 5 проходит через элемент И , закры/tbifi по второму входу низким напряжением с выхода узла 27 сложения бло- . ка 10 переключателей. При этом сигнал Конец работы интегратора 2

0 на выходе 19 блока 10 переключателей не появляется. Однако сигнал с второго выхода блока 8 сравнения проходит через элемент И 25, открытый по второму входу ВЫ90КИМ напряжением с

5 выхода элемента НЕ-26 ,-на вход которого поступает низкое напряжение с выхода узла 27( сложения блока 10 переключателей и проходит через элемент ИЛИ 21. На выходе 17. блока

0 10 переключателей появляется сигнал Начало работы интегратора . Он подтверждает рабочий режим интегратора 9 блока 9 интеграторов и производит в схеме описанные дейст5 ВИЯ.

Сигналы с первого выхода блока 8 сравнения прибавляют к содержимому счетчика 28 единицу. При значительной производительности исполнителя

л первой операции может произойти переполнение счетчика 28 блока 11 памяти, что имитирует переполнение блока памяти между первым и вторым этапами ее преобразования. Сигнал переполнения счетчика 28 с первого

выхода блока 11 памяти поступаетчерез блок 24 элементов ИЛИ на первый вход второй группы входов ком,мутатора 6 и прекращает рабочий режим интегратора 9, блока 9 интеграторов. Возобновление рабочего режима интегратора 9 происходит по сигналу, который появляется по сигналу

Начало работы интегратора с выхода 17 блока 10 переключателей.

Аналогичным образом осуществляется дальнейшее функционирование устройства .по переключению в рабочий режим всех интеграторов. При этом с

помощью блока 10 переключателей

имитируются события прекращения выполнения (i + 1)-й операции по окончании обработки ( J- 1)-й порции информации при незавершившейся i-й

операции обработки j-и порции информа ции (по сигналу с выхода 19) ; возобновления выполнения (i + 1)-1 операции после завершения i-й операцией обработки j-й порции.информации (по сигналу с выхода 17); возобновление

выполнения i-й операции при частичном освобождении i-ro накопителя информации в связи с начался (1+1)-й операцией обработки очередной порции информации, взятой из накопителя

(по сигналу с выхода I,-), С ПОМОЩЬЮ блока 11 памяти имитируется прекращение выполнения i-й, i If - (п - l)t операщии при переполнении 1гго накопителя информации В конце концов аа выходе каждого из интеграторов появляется напряжение, представлякиее собой peatnHsaцию кусочно-линейное функции, имитирующей объа инфррмгщии, обработанно на каждом из этапов ее преобразойаНИН. Напряжение с выхода п блока 9 интеграторов, представляющее собой реализацию кусочно-линейной функции имитирукзцей объем информации, появляющейся на выходе системы обработки данных, поступает на второй вход схегш2 сравнения, на первый вход которой с выхода источника 3 стабилизированного напряжения подается напряжение, раданое по величине объе му информации, подлежащей обработке в системе обработки данных каждым исполнителем. При достижении линейно изменяющимся напряжением, поступающим от блока 9, этого значения с выхода, схемы 2 сравнения поступает сигнал окончания обработки информации и фиксируется в блоке 4 регистрации. Устройство позволяет моделировать соинестной и параллельной обработки нескольких порций информации систилой обработки данных при наличии в ней прс №жуточных буферных каскадов памяти ограниченного объема. Благодаря этому возрастают достоверность и качество результатов моделирования реальшлх схем обработ.ки данных в АСУ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования поточной системы обработки информации | 1981 |

|

SU1005068A1 |

| Аналого-цифровой преобразователь интегральных характеристик электрических величин | 1981 |

|

SU1035790A1 |

| Генератор функций | 1984 |

|

SU1166148A2 |

| Устройство для вычисления алгебраических выражений | 1979 |

|

SU864298A1 |

| Устройство для моделирования систем управления | 1980 |

|

SU935965A1 |

| Устройство для определения весового расхода и контроля качества сыпучего материала | 1982 |

|

SU1089425A1 |

| Устройство подготовки данных для машин управления процессами электронно-лучевой микрообработки | 1983 |

|

SU1154257A1 |

| Устройство для моделирования тракта передачи данных | 1980 |

|

SU926665A1 |

| Генератор функций | 1982 |

|

SU1057966A1 |

| Устройство для контроля цифровых узлов | 1981 |

|

SU1012263A1 |

1УСТ;РОЙСТВО ДЛЯ МОдаЛИРо1зАНИЯ СИСТЕМ ОВРАБО1ЖИ ДАННЫХ, содержащее Генератор случайных напряже НИИ, выход которого соединен с ин формационм1лл входом первого блока коммутаторов, выходы которого соединены соответственно с уходами первой группы блока сравнения, выход реле времени соеданён с управляющим входом первого блока коммутаторов, блок переключателей,, блок источников стабилизированного напряже11ия, источник стабилиэированного напряжения, выход которого соединен с перВБМ входом схекш сравнения, выход которой подключен к входу блока регистрации, блок интеграторов, о т п ли ч а ю щ ее С я- тем, что, с целью асширения функциональных возмржностей за счет воспроизведения реГжимов промежуточного накопления обработанной на каждом из этапов информации, оно дополнительно содержит второй блок коммутаторов, блок памяхи, блок элементов , причем выходы блока источников стабилизированных нап{)яжений соеда нены соответственно с входами первой группы второго блока коммутаторов, входы второй группы входов которого соединены соответственно с выходами блокд сравнения, входги и первой группы блока переключателей и входами первой группы блока памяти, входы второй группы которого подключены к выходам первой группы блока переклю чателей, входам третьей группы второго блока коммутаторов и управляющим входам первой группы первого блока коммутаторов соответственно, выходы первой группы второго блока коммутаторов соединены соответственно с входами второй группы блока сравнения, выходы второй группы второго блока коммутаторов соединены соответственно с входами второй группы блока переключателей, входы Третьей группы входов которого соедшнены соответственно с вькодами блока интеграторов, выходы второй группы блока переключателей подключены соответственно к входам первой группы блока элементов ИЛИ, входда второй группы входов которого соединены с выходами блока .памяти соответственно, выходы блока элементов ИЛИ подключены к управляю1191М входам второй группы первого блока коммутаторов, п-й выход блока интеграторов 00 соединен с вторым входом схемы сравнения.2. Устройство по п. 1, отлию чающееся тем, что блок переключателей содержит группу триггеров, тр|И группы элементов И, группу элементов ИЛИ, группу элементов НЕ и группу узлов сложения, причем выход каждого узла сложения группы соединен с входа1 а1 соответствующего элемента НЕ группы и элемента И первой группы, выход которого подключен к единичному входу соответствующего ;триггера группы, единичный выход i KuTOgpro соединен с первым входом соответствукедего элемента И второй группы, выход которого Ьодключен к нулевому входу соответствующего триггера группы и первому входу соот

2e,W, / Фиг. 2

2в

.

19 -117,

п-1

Ю«гОпПп

J .

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для моделирования процесса сбора и обработки информации | 1977 |

|

SU631925A1 |

| Авторское свидетельство CCCIP iio заявке 3305662/24, кл | |||

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-05-15—Публикация

1982-01-11—Подача