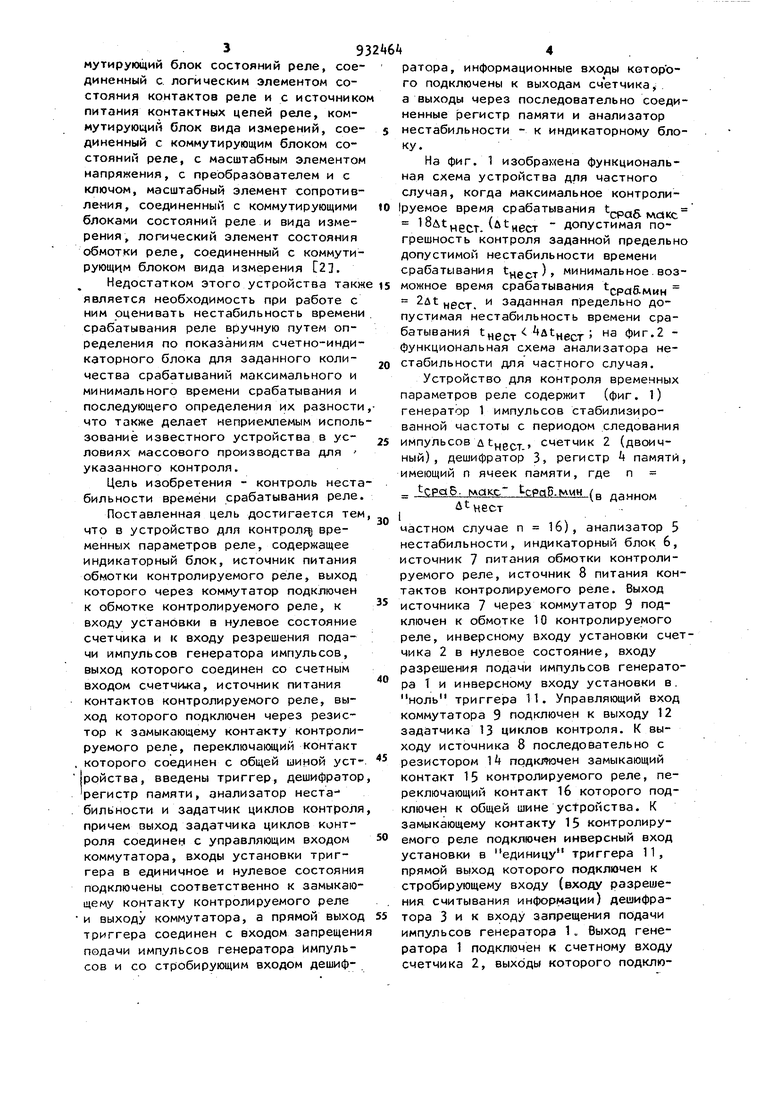

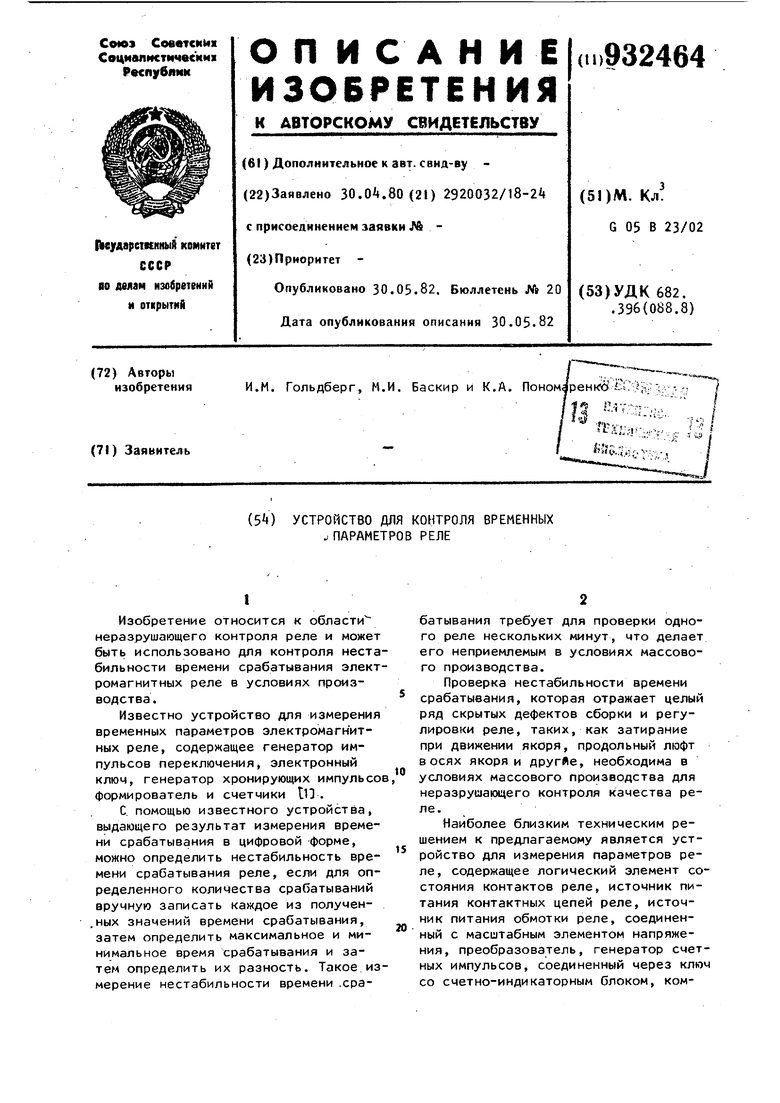

Изобретение относится к области неразрушающего контроля реле и может быть использовано для контроля неста бильности времени срабатывания элект ромагнитных реле в условиях производства. Известно устройство для измерения временных параметров электромагнитных реле, содержащее генератор импульсов переключения, электронный ключ, генератор хронирующих импульсо формирователь и счетчики ll . С. помощью известного устройства, выдающего результат измерения времени срабатывания в цифровой форме, можно определить нестабильность времени срабатывания реле, если для определенного количества срабатываний вручную записать каждое из получен.ных значений времени срабатывания, затем определить максимальное и минимальное время срабатывания и затем определить их разность. Такое из мерение нестабильности времени .срабатывания требует для проверки одного реле нескольких минут, что делает его неприемлемым в условиях массового производства. Проверка нестабильности времени срабатывания, которая отражает целый ряд скрытых дефектов сборки и регулировки реле, таких, как затирание при движении якоря, продольный люфт в осях якоря и другие, необходима в условиях массового производства для неразрушащего контроля качества реле. Наиболее близким техническим решением к предлагаемому является устройство для измерения параметров реле, содержащее логический элемент состояния контактов реле, источник питания контактных цепей реле, источник питания обмотки реле, соединенный с масштабным элементом напряжения, преобразователь, генератор счетных импульсов, соединенный через ключ со счетно-индикаторным блоком, коммутирующий блок состояний реле, сое диненный с логическим элементом состояния контактов реле и с источнико питания контактных цепей реле, коммутирующий блок вида измерений, соединенный с коммутирующим блоком состояний реле, с масштабным элементом напряжения, с преобразователем и с ключом, масштабный элемент сопротивления, соединенный с коммутирующими блоками состояний реле и вида измерения, логический элемент состояния обмотки реле, соединенный с коммутирующим блоком вида измерения 2. Недостатком этого устройства такж является необходимость при работе с ним оценивать нестабильность времени срабатывания реле вручную путем определения по показаниям счетно-индикаторного блока для заданного количества срабатываний максимального и минимального времени срабатывания и последующего определения их разности что также делает неприемлемым исполь зование известного устройства в условиях массового производства для указанного контроля. Цель изобретения - контроль неста бильности времени срабатывания реле Поставленная цель достигается тем что в устройство длл контрол временных параметров реле, содержащее индикаторный блок, источник питания обмотки контролируемого реле, выход которого через коммутатор подключен к обмотке контролируемого реле, к входу установки в нулевое состояние счетчика и к входу резрешения подачи импульсов генератора импульсов, выход которого соединен со счетным входом счетчи4 а, источник питания контактов контролируемого реле, выход которого подключен через резистор к замыкающему контакту контролируемого реле, переключающий контакт которого соединен с общей шиной устройства, введены триггер, дешифратор регистр памяти, анализатор неста бильности и задатчик циклов контроля причем выход задатчика циклов контроля соединен с управляющим входом коммутатора, входы установки триггера в единичное и нулевое состояния подключены соответственно к замыкающему контакту контролируемого реле и выходу коммутатора, а прямой выход триггера соединен с входом запрещени подачи импульсов генератора импульсов и со стробирующим входом дешифратора, информационные входы которого подключены к выходам счетчика, а выходы через последовательно соединенные регистр памяти и анализатор нестабильности - к индикаторному блоку. На фиг. 1 изобраиена функциональная схема устройства для частного случая, когда максимальное контролиtpyeMoe время срабатывания t.«,,,e ..., 1 Q 1 4. / i.OwO- ГЛСЛ НС , - допустимая погрешность контроля заданной предельно допустимой нестабильности времени срабатывания ), минимальное. возможное время срабатывания t,.p, 2д1 нест. заданная предельно допустимая нестабильность времени срабатывания , ; на фиг.2 функциональная схема анализатора нестабильности для частного случая. Устройство для контроля временных параметров реле содержит (фиг. 1) генератор 1 импульсов стабилизированной частоты с периодом следования импульсов , счетчик 2 (двоичный), дешифратор 3, регистр 4 памяти, имеющий п ячеек памяти, где п ЧраВ- ГУЛОКС tcpqS. (g данном частном случае п 16), анализатор 5 нестабильности, индикаторный блок 6, источник 7 питания обмотки контролируемого реле, источник 8 питания контактов контролируемого реле. Выход источника 7 через коммутатор 9 подключен к обмотке 10 контролируемого реле, инверсному входу установки счетчика 2 в нулевое состояние, входу разрешения подачи импульсов генератора Т и инверсному входу установки в. ноль триггера 11. Управляющий вход коммутатора 9 подключен к выходу 12 задатчика 13 циклов контроля. К выходу источника 8 последовательно с резистором 14 замыкающий контакт 15 контролируемого реле, переключающий контакт 16 которого подключен к общей шине yctpoйcтвa. К замыкающему контакту 15 контролируемого реле подключен инверсный вход установки в единицу триггера 11, прямой выход которого подключен к стробирующему входу (входу разрешения считывания информа14ии) дешифратора 3 и к входу запрещения подачи импульсов генератора 1 с Выход генератора 1 подключен к сметному входу счетчика 2, выходы которого подключены к информационным входам дешифратора 3. Выходы дешифратора 3, соответствующие десятичным числам от трех до восемнадцати, подключены к входам установки в единицу ячеек памяти регистра , имеющих номера с первого по шестнадцатый, причем большему десятичному числу соответствует больший номер ячейки памяти регистра . Выходы ячеек памяти регистра k подключены к входам анализатора 5, выход которого подключен к входу индикаторного блока 6,

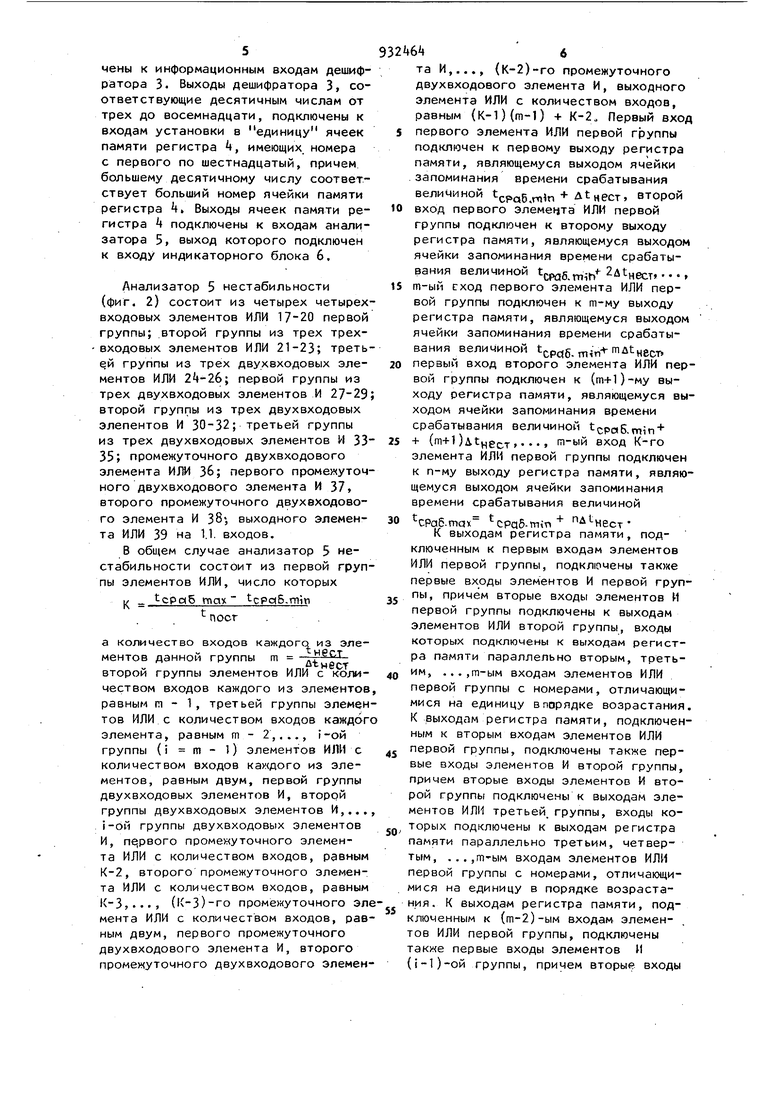

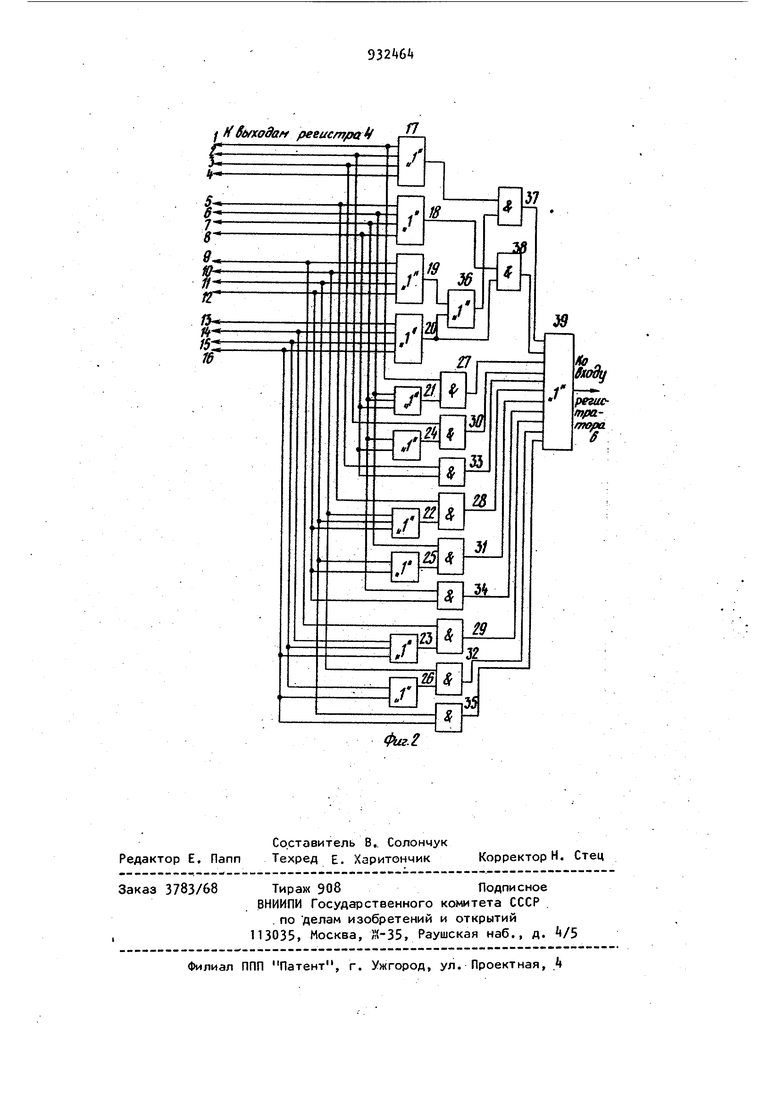

Анализатор 5 нестабильности (фиг. 2) состоит из четырех четырехвходовых элементов ИЛИ 17-20 первой группы; .второй группы из трех трехвходовых элементов ИЛИ 21-23; треть й группы из трех двухвходовых элементов ИЛИ первой группы из трех двухвходовых элементов И 27-29; второй группы из трех двухвходовых элепентов И 30-32; третьей группы из трех двухвходовых элементов И 3335; промежуточного двухвходового элемента ИЛИ 36; первого промежуточного двухвходового элемента И 37, второго промежуточного двухвходового элемента И 38, выходного элемента ИЛИ 39 на 1.1. входов.

В общем случае анализатор 5 нестабильности состоит из первой группы элементов ИЛИ, число которых

К - tcpgS max tcpqS.min nocr

а количество входов каждогс5 из элементов данной группы m д второй группы элементов ИЛИ с ко/в4чеством входов каждого из элементов равным m - 1, третьей группы элементов ИЛИ с количеством входов каждог элемента, равным m - 2,..., t-ой группы (i m - 1) элементов ИЛИ с количеством входов из элементов, равным двум, первой группы двухвходовых элементов И, второй группы двухвходовых элементов И,... i-бй группы двухвходовых элементов И, п€ рвого промежуточного элемента ИЛИ с количеством входов, равным К-2, второго промежуточного элемента ИЛИ с количеством входов, равным К-3,..., (1(-3)-го промежуточного эл мента ИЛИ с количеством входов, равным двум, первого промежуточного двухвходового элемента И, второго промежуточного двухвходового элемента И,..., (К-2)-го промежуточного двухвходового элемента И, выходного элемента ИЛИ с количеством входов, равным (К-1)(т-1) + К-2о Первый вход

5 первого элемента ИЛИ первой группы подключен к первому выходу регистра памяти, являющемуся выходом ячейки .запоминания времени срабатывания величиной tj.pQg,n + Att,ecT. второй

0 вход первого элемента ИЛИ первой группы подключен к второму выходу регистра памяти, являющемуся выходом ячейки запоминания времени срабатывания величиной tj.pQ5 . 2д1нест. .

5 m-ый сход первого элемента ИЛИ первой группы подключен к т-му выходу регистра памяти, являющемуся выходом ячейки запоминания времени срабатывания величиной t -pcig. rnin- -m tHecT.

0 первый вход второго элемента ИЛИ первой группы подключен к (т+1)-му выходу регистра памяти, являющемуся выходом ячейки запоминания времени срабатывания величиной ,

5 + (п1+0д1нест вход К-го элемента ИЛИ первой группы подключен к п-му выходу регистра памяти, являющемуся выходом ячейки запоминания времени срабатывания величиной

сраб.тах сраб-шгп

К выходам регистра памяти, подключенным к первым входам элементов ИЛИ первой группы, подключены таюхе первые входы элементов И первой группы, причем вторые входы элементов И первой группы подключены к выходам элементов ИЛИ второй группы, входы которых подключены к выходам регистра памяти параллельно вторым, треть.,т-ым входам элементов ИЛИ

им,

первой группы с номерами, отличающимися на единицу в порядке возрастания. К выходам регистра памяти, подключенным к вторым входам элементов ИЛИ первой группы, подключены также первые входы элементов И второй группы, причем вторые входы элементов И второй группы подключены к выходам элементов ИЛИ третьей, группы, входы которых подключены к выходам регистра памяти параллельно третьим, четвертым, ... ,т-ым входам элементов ИЛИ первой группы с номерами, отличающимися на единицу в порядке возрастания. К выходам регистра памяти, подключенным к (т-2)-ым входам элементов ИЛИ первой группы, подключены также первые входы элементов И (-1)-ой группы, причем вторые входы элементов И (-1)-ой группы подключены к выходам элементов ИЛИ i-ой группы, входы которых подключены к выходам регистра памяти параллельно (т-1)-ым и т-ым входам элементов ИЛИ первой группы с номерами, отличающи мися на единицу в порядке возрастания. К выходам регистра памяти, подключенным к (т-1)-ым входам элементов ИЛИ первой группы, подключены также первые входы элементов И i-ой группы, причем вторые входы элементов И 5-ой группы подключены к выхо дам регистра памяти параллельно т-ым входам элементов ИЛИ первой группы с номерами, отличающимися на единицу в порядке возрастания. К выходу первого элемента ИЛИ пер вой группы подключен первый вход первого промежуточного элемента И, второй вход которого подключен к вы ходу первого промежуточного элемента ИЛИ, входы которого подключены к выходам третьего, четвертого, ..., К-го элементов ИЛИ первой группы, к выходу второго элемента ИЛИ первой группы подключен первый вход второго промежуточного элемента И, второй вход которого подключен к выходу вто рого промежуточного элемента ИЛИ, входы которого подключены к |ыходам четвертого, пятого, ..., К-го элементов ИЛИ первой группы. К выходу {К-3)-го элемента ИЛИ первой группы подключен первый вход (К-З)-го промежуточного элемента И, второй вход которого подключен к выходу (К-З)-го промежуточного элемента ИЛИ, входы которого подключены к выходам (K-l)-ro и К-го элементов ИЛИ первой группы. К выходу (К-2)-го элемента ИЛИ первой группы подключен первый вход (К-2)-го промежуточного элемента И, второй вход которого под ключен к выходу К-го элемента ИЛИ первой группы. Выход каждого элемента И подключен к соответствующему входу выходного элемента ИЛИ, выход которого является выходом анализатора 5 нестабильности. Работает устройство следующим образом. Напряжение источника 7 подается на обмотку 10 через коммутатор 9, причем частота импульсов коммутации и количество импульсов задаются задатчиком 13. Длительность выходных, импульсов задатчика 13 выбирается 9 заведомо большей максимального возможного времени срабатывания реле. 8момент времени, когда коммутатор 9подключает к источнику 7 обмотке 10подается сигнал единица на вход разрешения подачи импульсов генератора 1 и на инверсный вход установки счетчика 2 в нулевое состояние, после чего импульсьг генератора 1, длительность периода которых составляет Д поступают в счетчик 2, который начинает производить их подсчете В момент срабатывания проверяемого реле, когда контакт 15 замыкается с контактом 16, триггер 11, находившийся до этого в состоянии ноль, переходит в состояние единица, в результате чего прекращается подача импульсов генератора в/счетчик 2. Одновременно с этим выходной сигнал единица триггера 11 поступает на стробирующий вход дешифратора 3. Таким образом, на одном из выходов дешифратора 3 появляетсл сигнал единица, соответствующий имевшему место определенному времени срабатывания реле, измеренному счетчиком 2. Сигнал единица, появившийся на выходе дешифратора 3, воздействует на вход установки в единицу соответствующей ячейки памяти регистра , который перед началом проверки реле установлен в состояние ноль. Таким образом, указанная ячейка памяти регистра 4 переводится в состояние единица, в котором она продолжает оставаться в течение всей последующей проверки реле. В момент времени, когда коммутатор 9 отключает от источника 7 обмотку 10,подается сигнал ноль на инверсный вход установки счетчика 2 в нулевое состояние и на инверсный вход установки в ноль триггера 11. Вследстие этого счетчик 2 устанавливается в нулевоессостояние, а также переводится в состояние ноль триггер 11, выходной сигнал которого при этом запрещает работу дешифратора 3. В указанном состоянии схема устройства продолжает находиться до момента времени, когда коммутатор 9 вновь подает напряжение на обмотку 10. При последующих подключениях обмотки 10 к источнику 7 и отключениях от него работа устройства протекает аналогично описанной выше. Описанный процесс коммутации реле производится пределенное число раз, например, десять, после чего задатчик 13 запрещает дальнейшую коммутацию реле, а также выдает сигнал об окончании цикла проверки реле. В течение цикла проверки реле пос ле каждого срабатывания контролируемого реле измеренная счетчиком 2 вел чина времени срабатывания запоминает ся регистром 4, в котором каждая из ячеек памяти, оказавшаяся в состоянии единица, характеризует конкрет ное время срабатывания реле, величина которого соответствует номеру ячейки памяти (номеру выхода регистра) . Если в процессе проверки реле имеют место два времени срабатывания, отличающиеся на четыре и более периодов импульсов генератора 1, т.е имеет место превышение заданной предельно допустимой нестабильности вре мени срабатывания, то соответствующи этим временным интервалам два из выходов регистра А, оказавшиеся в состоянии единица и порядковые номера которых отличаются на четыре и более, выявляются анализатором 5. В анализаторе 5 производится сопоставление между собой результатов всех замеров величин времени срабатывания, полученных в Г|1роцессе цикла проверки. Таким образом, любая комбинация двух номеров выходов регистра 4, которые оказались в состоянии единица и порядковые номера которых отличаются на четыре и более, приводит к появлению сигнала единица, на одном из входов выходнрго элемента ИЛИ ЗЭ, в результате чего на его выходе появляется сигнал единица, что приводит к срабаты- ванию блЬка 6. Введение в схему устройства задатчика циклов контроля, дешифратора, триггера, регистра памяти и анализатора нестабельности позволяет автоматизировать процесс контроля нестабильнос/и времени срабатывания реле и сократить время контроля с нескольких минут до долей секунд. Учитывая, что нестабильность времени срабатывания очень точно отражает различные нарушения сборки и регулировки микроминиатюрных электромагнитных реле, такие, как затирание при движении якоря, продольный люфт в осях якоря и другие контроль указанного параметра с помощью автоматических приборов позволяет выявить скрытые дефекты производства у выпускаемых серийно реле и, таким образом, позволяет повысить качество выпускаемых реле. Предлагаемая схема анализатора нестабильности обеспечивает выявление двух значений времени срабатывания, если величина их разности выходит за пределы заданной величины, причем выявление заданной разности производится при любых абсолютных значениях времени срабатывания во всем диапазоне возможных величин, Указанная схема анализатора нестабильности универсальна и позволяет создавать устройства для любых реле с любым временем срабатывания, а также обеспечивает необходимую точность в зависимости от выбора шага дискретности и обеспечивает контроль любого количества проверяемых времен срабатывания. Формула изобретения Устройство для контроля временных параметров реле, содержащее индикаторный блок, источник питания обмотки контролируемого реле, выход которого через коммутатор подключен к обмотке контролируемого реле, к входу установки в нулевое состояние счетчика и к входу разрешения подачи, импульсов генератора импульсов, выход которого соединен со счетным входом счетчика, источник питания контактов контролируемого реле, выход которого подключен через резистор к замыкающему контакту контролируемого реле, переключающий контакт которого соединен с общей шиной устройства , отличающееся тем, что, с целью контроля нестабильности времени срабатывания реле, в устройство введены триггер, дешифратор, регистр памяти, анализатор нестабильности и задатчик циклов контроля, причем выход задатчика циклов контроля соединен с управляющим входом коммутатора, входы установки триггера в единичное и нулевое состояния подключены соответственно, к замыкающему контакту контролируемого реле и выходу коммутатора, а прямой выход триггера соединен с входом запрещения подачи импульсов генератора импульсов и со стробирую-. щим входом дешифратора, информационные входы которого подключены к вь ходам счетчика, а выходы через после11932 б

довательно соединенные регистр памяти

и анализатор нестабильности - к индикаторному блоку.

Источники информации, принятые во внимание при экспертизе

К Авторское свидетельство СССР № 284175, кл. G 05 В 23/02, 1966.

2. Авторское свидетельство СССР № i 09201, кл. G 05 В 23/02, 1970 5 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля состояния диагностируемых цепей | 1985 |

|

SU1316002A1 |

| Устройство для селекции признаков подвижных объектов | 1989 |

|

SU1691860A1 |

| Устройство для регистрации сейсмической информации | 1990 |

|

SU1811615A3 |

| Устройство для автоматического поиска дефектов в логических блоках | 1982 |

|

SU1108451A1 |

| Устройство для контроля цифровых узлов | 1981 |

|

SU1013960A1 |

| УСТРОЙСТВО АВТОВЫБОРА ДИСКРЕТНОГО КАНАЛА | 2011 |

|

RU2488222C1 |

| Устройство для управления распределенным объектом | 1986 |

|

SU1363144A1 |

| Устройство для автоматизированного контроля параметров реле | 1985 |

|

SU1265704A1 |

| Устройство для контроля логических блоков | 1985 |

|

SU1305687A1 |

| Устройство для контроля и диагностики цифровых узлов | 1987 |

|

SU1587513A1 |

Устано ма ,ff

Авторы

Даты

1982-05-30—Публикация

1980-04-30—Подача