2. Синтезатор по п.1, отличающийся тем, что формирователь управляющих сигналов содержит последовательно соединенные элемент задержки, первый формирователь импульсов и первый элемент ИЛИ, последовательно соединенные второй формирователь импульсов и второй элемент ИЛИ и последовательно соединенные третий формирователь импульсов и элемент И, а также О-триггер, которого является входом формирователя управляющих сигнашов.

прямой выход. О-триггера подключен к другим входам первого и второго элементов ИЛИ, а инверсный выход D-триггера соединен с другим входом элемента И, тактовый вход D-триггера и входы элемента задержки, второго и третьего формирователей объединены и подключены к выходу мультивибратора, при этом выходы элемента И, второго элемента ИЛИ й первого эле-, мента ИЛИ являются соответственно первым, вторым и третьим выходами формирователя управляющих сигналов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой синтезатор частоты | 1982 |

|

SU1109914A1 |

| Синтезатор частот | 1989 |

|

SU1730720A1 |

| Синтезатор частоты | 1984 |

|

SU1257845A1 |

| Цифровой синтезатор частот | 1980 |

|

SU1042188A1 |

| Цифровой синтезатор частоты с частотной модуляцией | 1989 |

|

SU1771068A1 |

| Цифровой синтезатор частот | 1981 |

|

SU1077057A1 |

| Цифровой синтезатор частоты | 1980 |

|

SU987817A1 |

| Цифровой синтезатор частот | 1984 |

|

SU1197073A2 |

| Синтезатор частот | 1985 |

|

SU1327288A1 |

| Цифровой синтезатор частоты | 1981 |

|

SU1054908A1 |

1. СИНТЕЗАТОР ЧАСТОТЫ, со держащий последовательно соединенны опорный генератор, делитель частоты и частотно-фазовый детектор, последовательно соединенные фазовый корректсф, интегратор, фильтр нижних частот, управляемый генератор и делитель частоты с переменным коэффициентом деления, выход которого сое динен с другим сигнальным входом ча тотно-фазового детектора, а также формирователь импульсов, вход и выход которого соответственно соеди нены с другим выходом делителя частоты и управлякицим входом фазового корректора, отличающийся тем, что, с целью уменьшения потреб ления энергии питания, введены первый и второй ключи и последовательн соединенные датчик синхронизма, формирователь управляющих сигналов и третий ключ, другой вход которого подключен к шине питания, первые управляющие входы частотно-фазового детектора, делителя tacToxtj рователя импульсов и делителя частоты с nepeffieHHfcJM коэффициентом деления объединены и подключены , к выходу третьего ключа, вторые управляющие входы частотно-фазового детектора, делителя частоты, формирователя импульсов и делителя частоты с переменным коэффициентом деления объединены и подключены к второму выходу формирователя управляктщх сигнгшов, первый ключ включен между первым выходом частотнофазового детектора и первым входом фазового корректора, а второй ключ включен между вторым выходом частотно-фазового детектора и вторым входом фазового корректора, управляющие входы первого и второго ключей объединены и соединены с третьим выходом формирователя управляющих сигналов, а входы датчика синхронизма подключены соответственно к первому и второму выходам частотно-фазового детектс«)а.

Изобретение относится к радиотехнике и может быть использовано,, например, в приемопередающей аппаратуре связи.

Известны синтезаторы частоты, содержащие группу перестраиваемых генераторов с коммутируемой цепью управления, включающей в себя делитель частоты с переменным коэффициентом деления, фазовый детектор, филь нижних частот и ключи 1 . Недостатком этого синтезатора является болыиое потребление энергии питания. Наиболее близким по технической сущности к изобретению является син тезатор частот, содержащий последовательно соединенные опорный генера тор, делитель частоты и частотнофазовый детектор, последовательно соединенные фазовый корректор, инте ратор, фильтр нижних частот, управл емый генератор и делитель частоты с переменньгм коэффициентом деления, выход которого соединен с другим сигнальным входом частотно-фазового детектора, а также формирователь импульсов, вход и выход которого соответственно соединен с другим выходом делителя частоты и управляющим входом фазового корректора 2 Однако известный синтезатор такж потребляет большое количество энерг от источника питания. Цель изобретения - уменьшение потребления энергии питания. Поставленная цель достигается тем, что в синтезатор частоты, соде жащий последовательно соединенные опорный генератор, делитель частоты и частотно-фазовый.детектор, п®следовательно соединенные фазовый корректор, интегратор, фильтр нижних частот, управляемый генератор и делитель частоты с переменным коэффициентом деления, выход которого- сое

динен с другим сигнальным входом частотно-фазового детектора, а также формирователь импульсов, вход и выход которого соответственно соединены с другим выходом делителя частоты и управляющим входом фазового корректора, введены первый и второй ключи и последовательно соединенные датчик синхронизма, формирователь управляющих сигналов и третий ключ. другой вход которого подключен к шине питания, первые управляющие входы частотно-фазового детектора, делителя частоты, формирователя импульcos и делителя частоты с переменным коэффициентом деления объединены и подключены к выходу третьего ключа, вторые управляющие входы частотнофазового детектора, делителя частоты, формирователя импульсов и делителя частоты с переменным коэффициентом деления объединены и подключены к второму выходу формирователя управляющих сигналов, первый ключ включен между первым выходом частотно-фазового детектора и первым входом фазового корректора, а второй ключ включен между вторьм выходом частотно-фазового детектора и вторым входом фазового корректора, управляющие входы первого и второго ключей объединены и соединены с третьим выходом формирователя управляющих сигналов, а входы датчика синхронизма подключены соответственно к первому и второму выходам частотно-фазового детектора. Кроме того, формирователь управляющих сигналов содержит последовательно соединенные элемент задержки, первый формирователь импульсов и первый элемент ИЛИ, последовательHO срединенные второй формирователь импульсбв и второй элемент ИЛИ и последовательно соединеннее третий Формирователь и мпульсов и элемент il,

а также D-триггер, .S-вход которого, является входом формирователя управляющих сигналов, прямой выход 0 триггера подключен к другим входам первого и второго элементов lUlH, а инверсный выход D -триггера соединен с другим входом элемента И тактовый вход D-триггера и входы элмента задержки, второго и третьего формирователей объединены и подключены к выходу мультивибратора, при этом выходы элемента И, второго элемента ИЛИ и первого элемента ИЛИ являются соответственно первым, вторым и третьим выходами формирователя управляющих сигналов.

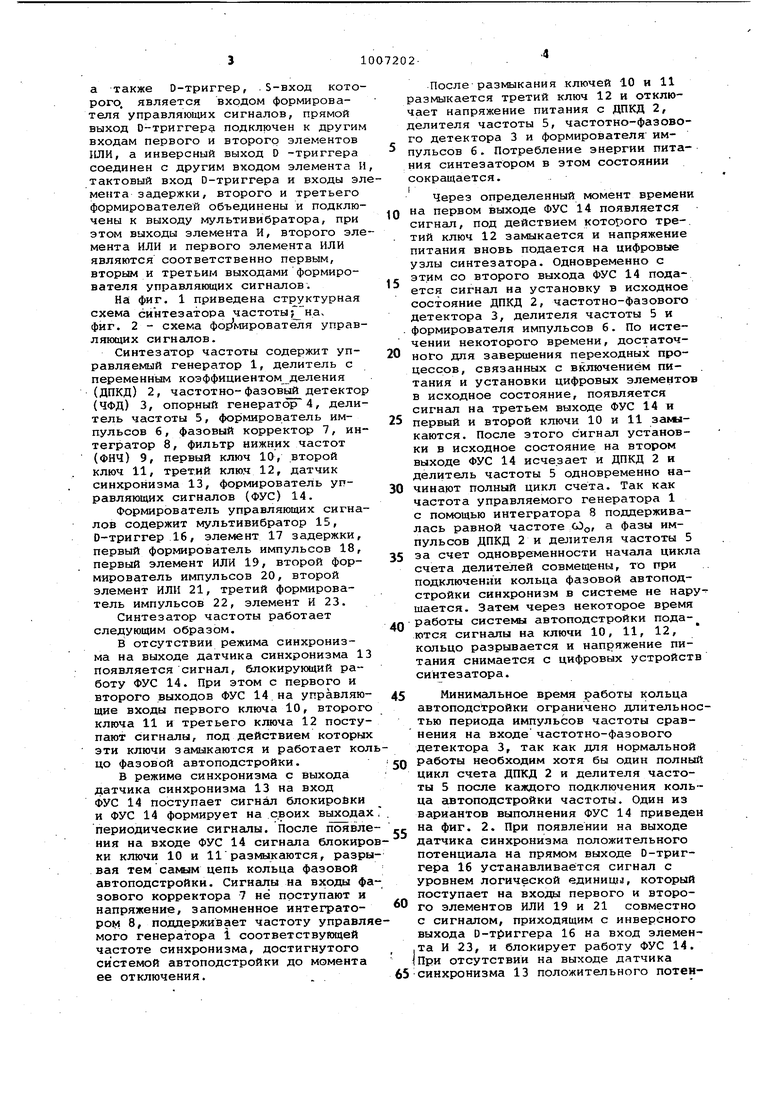

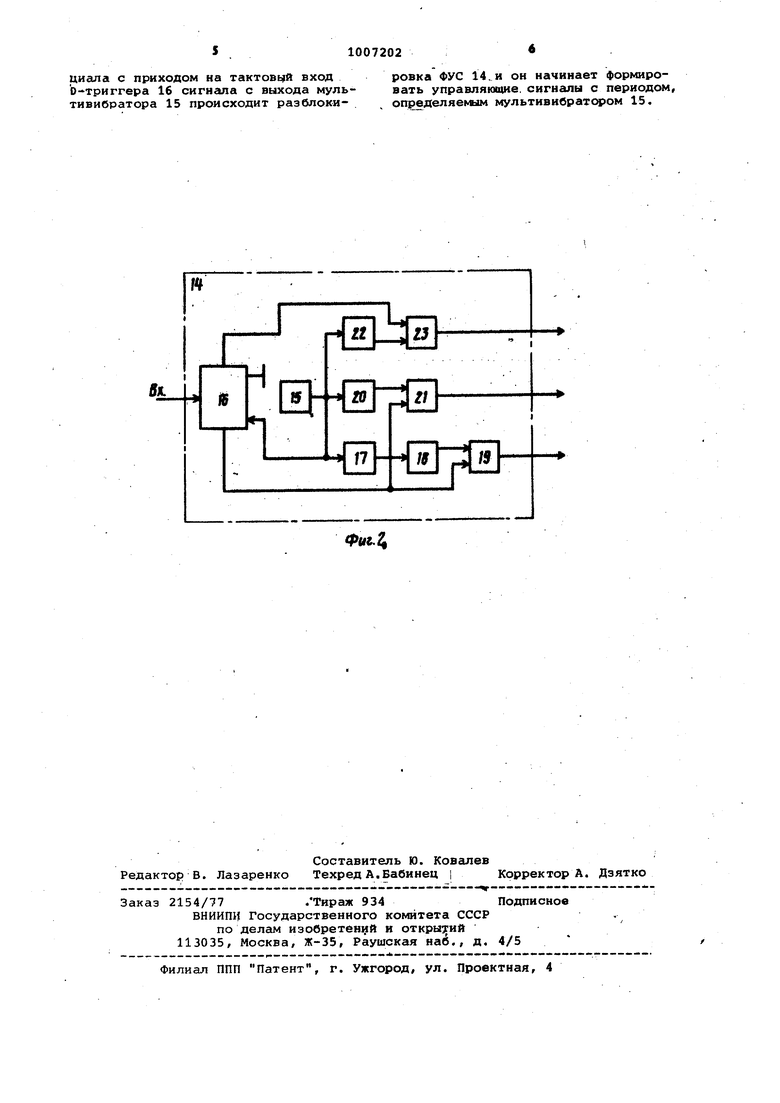

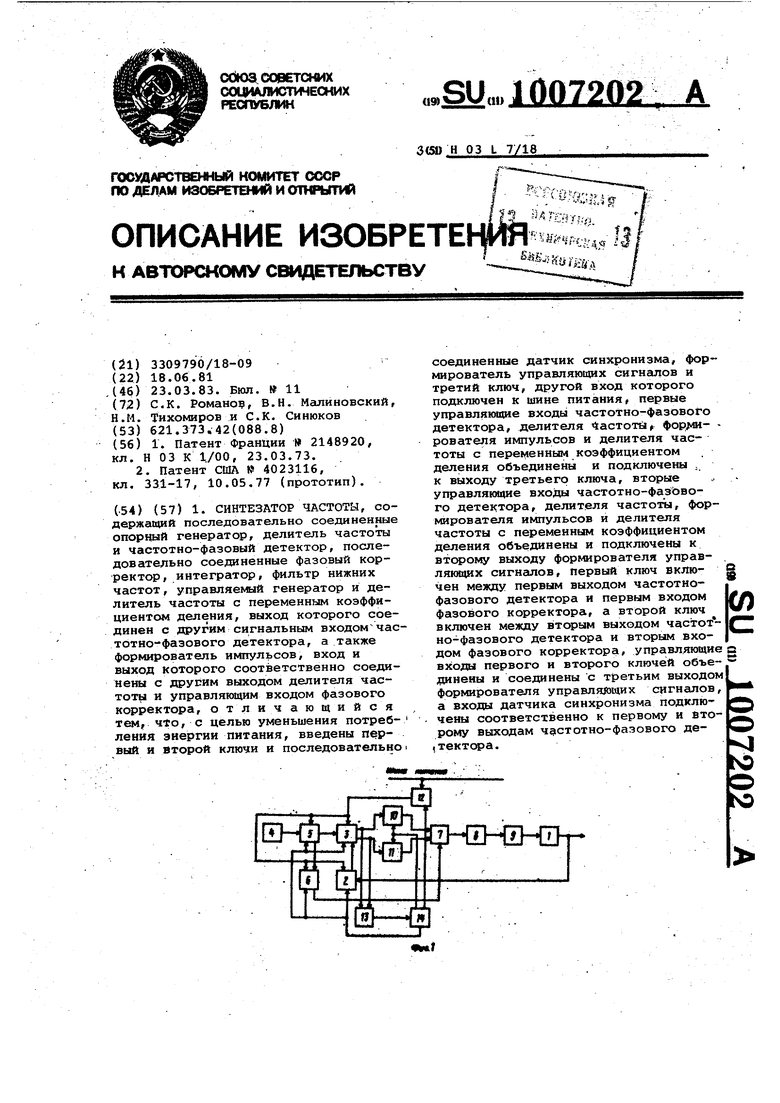

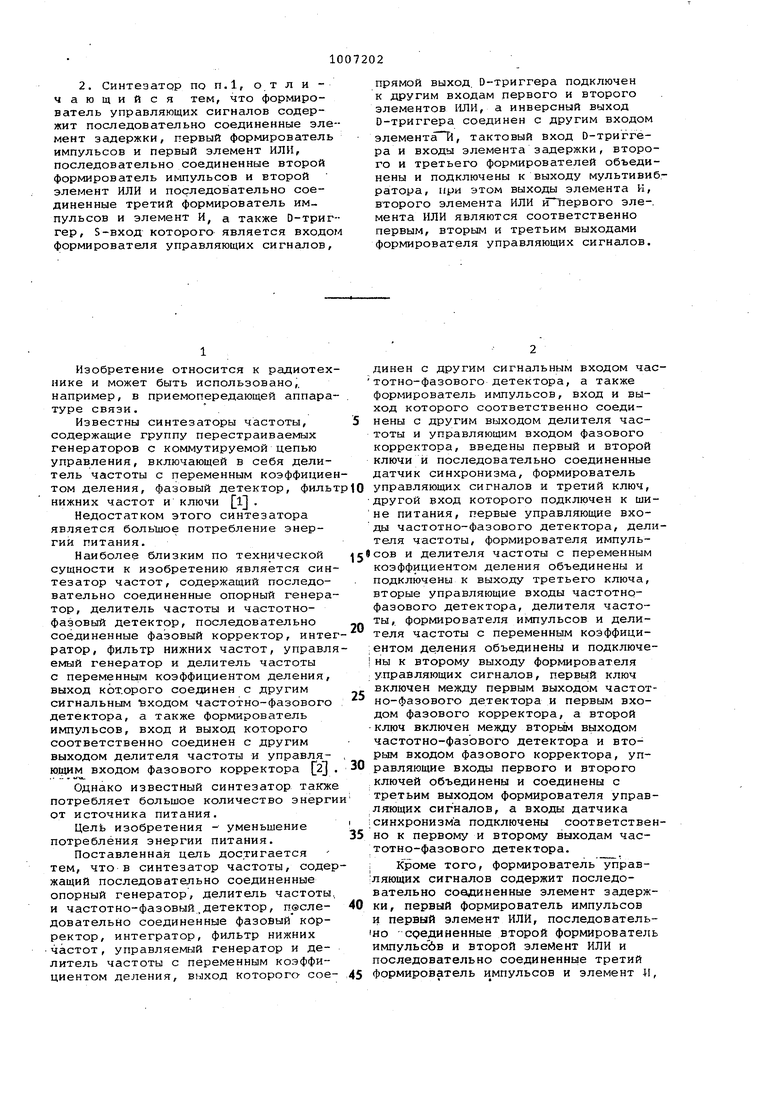

На фиг. 1 приведена структурная схема синтезатора частоты; на. фиг. 2 - схема фoE шpoвaтёля управляющих СИГНсШОВ.

Синтезатор частоты содержит управляемый генератор 1, делитель с переменным коэффициентом деления (ДПКД) 2, частотно-фазовый детектор (ЧФД) 3, опорный генерат(4, делитель частоты 5, формирователь импульсов 6, фазовый корректор 7, интегратор 8, фильтр нижних частот (ФНЧ) 9, первый ключ 10, второй ключ 11, третий клю.ч 12, датчик синхронизма 13, формирователь управляющих сигналов (ФУС) 14.

Формирователь управляющих сигналов содержит мультивибратор 15, D-триггер 16, элемент 17 задержки, первый формирователь импульсов 18, первый элемент ИЛИ 19, второй формирователь импульсов 20, второй элемент ИЛИ 21, третий формирователь импульсов 22, элемент И 23.

Синтезатор частоты работает следующим образом.

В отсутствии режима синхронизма на выходе датчика синхронизма 13 появляется сигнал, блокирукядий работу ФУС 14. При этом с первого и второго выходов ФУС 14. на управляющие входы первого ключа 10, второго ключа 11 и третьего ключа 12 поступают сигналы, под действием которых эти ключи замыкаются и работает колцо фазовой автоподстройки.

В режиме синхронизма с выхода датчика синхронизма 13 на вход ФУС 14 поступает сигнал блокировки и ФУС 14 формирует на своих выходах периодические сигналы. После появления на входе ФУС 14 сигнала блокироки ключи 10 и 11размыкаются, разрывая тем самлм цепь кольца фазовой автоподстройки. Сигналы на входы фазового корректора 7 не поступают и напряжение, запомненное интегратоpoiyi 8, поддерживает частоту управлямого генератора i соответствующей частоте синхронизма, достигнутого системой автоподстройки до момента ее отключения.

После размыкания ключей 10 и 11 размыкается третий ключ 12 и отключает напряжение питания с ДПКД 2, делителя частоты 5, частотно-фазового детектора 3 и формирователя импульсов б, Потребление энергии питания синтезатором в этом состоянии

сокращается. I

Через определенный момент времени

на первом выходе ФУС 14 появляется сигнал, под действием которого тре-. тий ключ 12 замыкается и напряжение питания вновь подается на цифровые узлы синтезатора. Одновременно с этим со второго выхода ФУС 14 подается сигнал на установку в исходное состояние ДПКД 2, частотно-фазового детектора 3, делителя частоты 5 и . формирователя импульсов 6. По истечении некоторого времени, достаточного для завершения переходных процессов, связанных с включением питания и установки цифровых элементов в исходное состояние, появляется сигнсш на третьем выходе ФУС 14 и первый и второй ключи 10 и 11 замыкаются. После этого сигнсш установки в исходное состояние на втором выходе ФУС 14 исчезает и ДПКД 2 и делитель частоты 5 одновременно начинают полный цикл счёта. Так как

0 частота управляемого генератора 1 с помощью интегратора 8 поддерживалась равной частоте Од, а фазы импульсов ДПКД 2 и делителя частоты 5 за счет одновременности начала цикла счета делителей совмещены, то при подключении кольца фазовой автоподстройки синхронизм в системе не нарушается. Затем через некоторое время работы системы автоподстройки подаются сигналы на ключи 10, 11, 12, кольцо разрывается и напряжение питания снимается с цифровых устройств синтезатора.

Минимальное время работы кольца автоподсгройки ограничено длительностью периода импульсов частоты сравнения на входе частотно-фазового детектора 3, так как для нормальной работы необходим хотя бы один полный цикл счета ДПКД 2 и делителя частоты 5 после каждого подключения кольца автоподстройки частоты. Один из вариантов выполнения ФУС 14 приведен на фиг. 2. При появлении на выходе датчика синхронизма положительного потенциала на прямом выходе D-триггера 16 устанавливается сигнал с уровнем логической единишл, который поступает на входы первого и второго элементов ИЛИ 19 и 21 совместно с сигналом, приходящим с инверсного выхода D-триггера 16 на вход элемен.та И 23, и блокирует работу ФУС 14. при отсутствии на выходе датчика

-синхронизма 13 положительного потенциала с приходом на тактовой вход Ь-триггера 16 сигнгша с выхода мультивибратора 15 происходит разблокировка ФУС 14.и он начинает формировать управляющие, сигналы с периодом, определяемым мультивибратором 15.

tput.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| СПОСОБ ПРОИЗВОДСТВА МОЛОЧНОЙ КАШИ | 1999 |

|

RU2148920C1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Патент США 4023116, кл | |||

| Накладной висячий замок | 1922 |

|

SU331A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1983-03-23—Публикация

1981-06-18—Подача