вого 1)-триггера, выход формирователя импульсов, прямой выход RS-триггера и выход второго D-триггера являются соответственно выходом сигнала управления напряжением питания, первым

I

Изобретение относится к радиотехнике и может быть использовано в при емо-передающей аппаратуре систем радиосвязи.

Цель изобретения - повьппение ста- бильности частоты выходного сигнала.

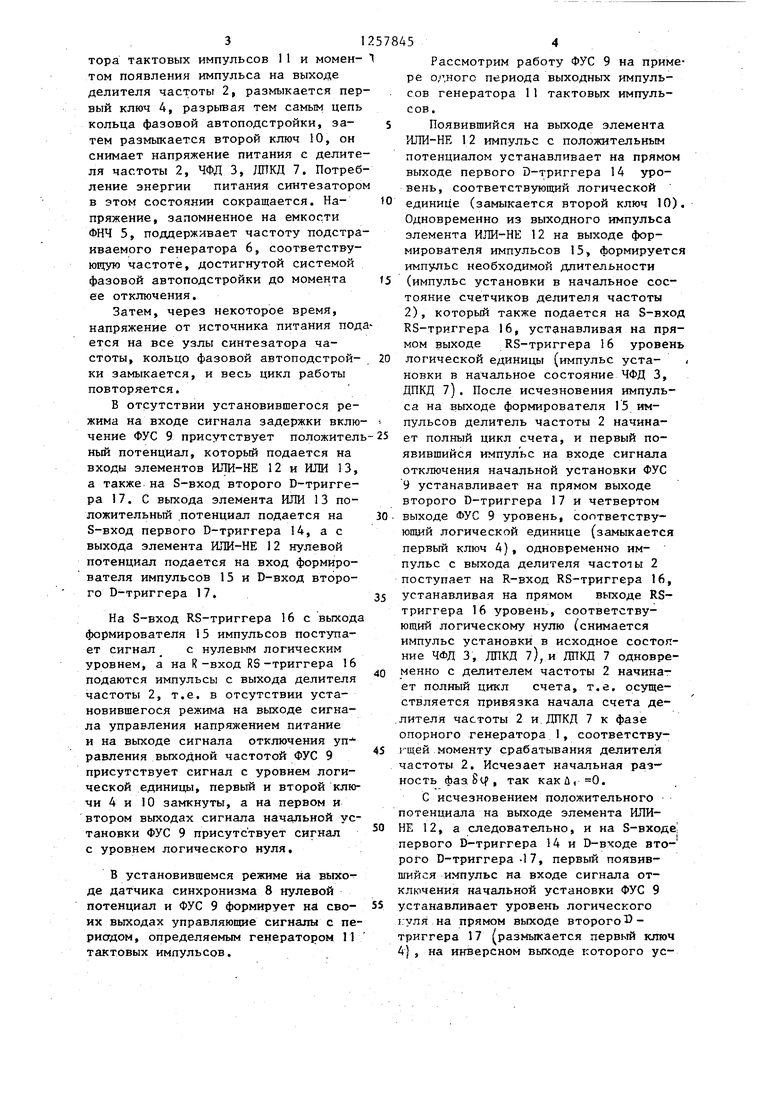

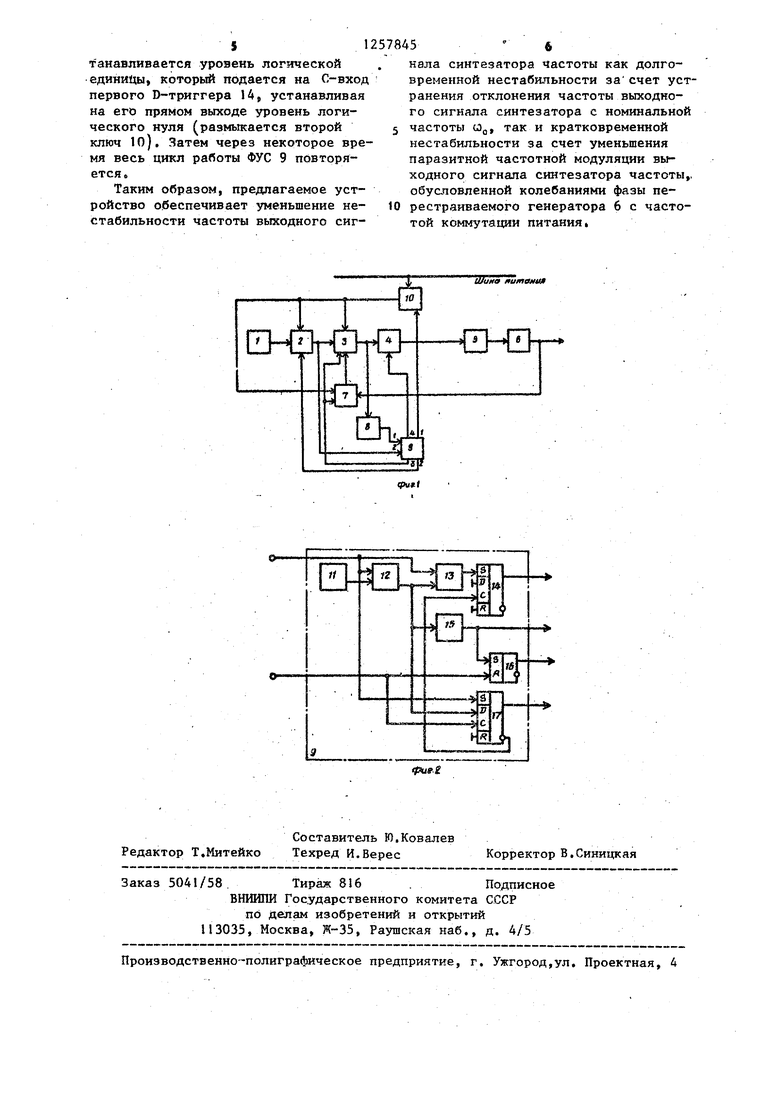

На фиг. 1 представлена электрическая структурная схема синтезатора частоты, на фиг, 2 - схема формирователя управляющих сигналов.

Синтезатор частоты содержит опорный генератор 1, делитель частоты 2, частотно-фазовый детектор (ЧФД) 3, первый ключ 4, фильтр 5 нкясних частот (ФНЧ), перестраиваемый генератор 6, делитель 7 частоты с переменным коэффициентом деления (ДПКД), датчик синхронизма 8, формирователь 9 управляющих сигналов (ФУС), второй ключ 10, При этом формирователь 9 уп равляющих сигналов содержит генератор 11 тактовых импульсов, элемент ИЛИ-НЕ 12, элемент ИЛИ 13, первый D-триггер 14, формирователь 15 импульсов, RS-триггер 16, второй D- триггер 17,

Синтезатор частоты работает следующим образом,

В отсутствии установившегося режима на выходе датчика синхронизма 8 появляется сигнал, блокирующий работу ФУС 9, При этом с выхода сигнала управления напряжением питания и С выхода сигнала отключения управления выходной час-тотой ФУС 9 на управляющие входы первого 4 и второго 10 ключей поступают сигналы, под действием которых эти ключи замыкаются и работает кольцо.фазовой автоподстройки,

Б установивщемся режиме с выхода датчика синхронизма 8 на вход сигнала задержки включения ФУС 9 поступает сигнал разблокировки,и ФУС 9

выходом сигнала начальной установки, вторым выходом сигнала начальной установки и выходом сигнала отключения начальной установки формирователя управляющих сигналов.

0

5

0 5 0

5

формирует на своих выходах периодические сигналы. В установившемся режиме в определенный момент времени на выходе сигнала управления напряжением питания ФУС 9 появляется сигнал, под действием которого- второй ключ 10 замыкается, и напряжение питания подается на делитель частоты 2, ЧФД 3, ДПКД 7, с первого и второго выходов сигналов начальной установки ФУС 9 подаются сигналы на установку в исходное состояние делителя частоты 2, ЧФД 3, ДПКД 7. Длительность сигнала установки в исходное состояние делителя частоты 2 равна интервалу времени, достаточного для завершения переходных процессов, связанных с включением питания и установкой цифровых элементов в исходное состояние. Цосле исчезновения первого сигнала начальной установки делитель частоты 2 начинает, полный цикл счета.. С появлением первого импульса на вьгходе делителя частоты 2 снимается второй сигнал начальной установки в исходное состояние ЧФД 3, ДПКД 7, замыкается первый ключ 4, В результате этого делитель частоты 2 и ДПКД 7 одновременно начинают полный цикл счета, т.е, осуществляется привязка начала счета делителя частоты 2 и ДПКД 7 к фазе колебания опорного генератора 1, соответствующей моменту срабатывания делителя частоты 2. В результате исчезает начальная разность фаз сигналов, поступающих на ЧФД 38(у, так как Л, 0, а следо- вательно уменьшается нестабильность частоты выходного сигнала синтезатора частоты в установившемся режиме.

Через некоторое время, определенное скважностью сигнала генера31257845

тактовых импульсов 1 1 и момен- Т появления импульса на выходе теля част оты 2, размыкается перключ 4, разрывая тем самым цепь ца фазовой автоподстройки, за- $ размыкается второй ключ 10, он ает напряжение питания с делитеастоты 2, ЧФД 3, /ШКД 7. Потребе энергии питания синтезатором ом состоянии сокращается. На- 10 ение, запомненное на емкости 5, поддерживает частоту подстрамого генератора 6, соответствусс

п вы ве ед Од эл ми им то 2) RS мо ло но ДП са пу ет яв от 9 вт вы ющ пе пу по ус тр ющ им ни ме ет ст ли оп гщ ча но

ющую частоте, достигнутой системой фазовой автоподстройки до момента ее отключения.

Затем, через некоторое время, напряжение от источника питания подется на все узлы синтезатора частоты, кольцо фазовой автоподстрой- ки замыкается, и весь цикл работы повторяется.

В отсутствии установившегося режима на входе сигнала задержки вклю чение ФУС 9 присутствует положител ный потенциал, который подается на входы элементов ИЛИ-НЕ 12 и ИШ 13, а также на S-вход второго D-тригге- ра 17. С вьпсода элемента ИЛИ 13 положительный .потенциал подается на S-вход первого D-триггера 14, а с выхода элемента ИЛИ-НЕ 12 нулевой потенциал подается на вход формирователя импульсов 15 и D-вход второго D-триггера 17.

На S-вход RS-триггера 16 с выхода формирователя 15 импульсов поступает сигнал с нулевым логическим уровнем, а на R-вход RS-триггера 16 подаются импульсы с выхода делителя частоты 2, т.е. в отсутствии установившегося режима на выходе сигнала управления напряжением питание и на выходе сигнала отключения уп- равления выходной частотой ФУС 9 присутствует сигнал с уровнем логической единицы, первый и второй ключи 4 и 10 замкнуты, а на первом и втором выходах сигнала начальной установки ФУС 9 присутствует сигнал с уровнем логического нуля,

В установившемся режиме на выходе датчика синхронизма 8 нулевой потенциал и ФУС 9 формирует на своих выходах управляющие сигналы с периодом, определяемым генератором 11 тактовых импульсов.

$ 10

15

20

25 30.

5

0

5

0

5

Рассмотрим работу ФУС 9 на примере периода выходных импульсов генератора 11 тактовых импульсов.

Появившийся на выходе элемента ИЛИ-НЕ 12 импульс с положительным потенциалом устанавливает на прямом выходе первого D-триггера 14 уровень, соответствующий логической единице (замыкается второй ключ 10). Одновременно из выходного импульса элемента ИЛИ-НЕ 12 на выходе формирователя импульсов 15, формируется импульс необходимой длительности (импульс установки в начальное состояние счетчиков делителя частоты 2), который также подается на S-вход RS-триггера 16, устанавливая на прямом выходе RS-триггера 16 уровень логической единицы (импульс уста- новки в начальное состояние ЧФД 3, ДПКД 7). После исчезновения импульса на выходе формирователя 15 импульсов делитель частоты 2 начинает полный цикл счета, и первый появившийся импульс на входе сигнала отключения начальной установки ФУС 9 устанавливает на прямом выходе второго D-триггера 17 и четвертом выходе ФУС 9 уровень, соответствующий логической единице (замыкается первый ключ 4), одновременно импульс с выхода делителя частоты 2 поступает на R-вход RS-триггера 16, устанавливая на прямом выходе RS- триггера 16 уровень, соответствующий логическому нулю (снимается импульс установки в исходное состояние ЧФД 3, ДПКД 7), и ДПКД 7 одновременно с делителем частоты 2 начинает полный цикл счета, т.е. осуществляется привязка начала счета делителя частоты 2 и ДПКД 7 к фазе опорного генератора 1, соответству- гщей моменту срабатывания делителя частоты 2. Исчезает начальная раз- ность фазЙМ так как и, 0.

С исчезновением положительного потенциала на выходе элемента РШИ- НЕ 12, а следовательно, и на S-BxoAei первого D-триггера 54 и D-входе вто- роГо D-триггера -17, первый появившийся импульс на входе сигнала отключения начальной установки ФУС 9 устанавливает уровень логического 1:уля на прямом выходе второго I)- триггера 17 (размыкается первый ключ 4), на инверсном выходе которого устанавливается уровень логической единицы, который подается на С-вход первого D-триггера 14, устанавливая на его прямом выходе уровень логического нуля (размыкается второй ключ 10), Затем через некоторое время весь цикл работы ФУС 9 повторяется .

Таким образом, предлагаемое устройство обеспечивает уменьшение нестабильности частоты выходного сигКЗгЕЫ Т

Редактор Т.Митейко

Составитель Ю.Ковалев Техред И.Верес

Заказ 5041/58 . Тираж 816 . Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород,ул. Проектная, 4

кала синтезатора частоты как долговременной нестабильности за счет устранения отклонения частоты выходного сигнала синтезатора с номинальной частоты QO, так и кратковременной нестабильности за счет уменьшения паразитной частотной модуляции выходного сигнала синтезатора частоты,, обусловленной колебаниями фазы перестраиваемого генератора 6 с частотой коммутации питания,

Г

Шина ituintUHW

Корректор В.Синицкая

| название | год | авторы | номер документа |

|---|---|---|---|

| Синтезатор частот | 1989 |

|

SU1730720A1 |

| Синтезатор частоты | 1981 |

|

SU1007202A1 |

| Цифровой синтезатор частоты | 1982 |

|

SU1109914A1 |

| Цифровой синтезатор частот Усачева И.П. | 1986 |

|

SU1417186A2 |

| СИНТЕЗАТОР ЧАСТОТ | 2009 |

|

RU2394367C1 |

| СИНТЕЗАТОР ЧАСТОТ | 2010 |

|

RU2434322C1 |

| Цифровой синтезатор частот | 1985 |

|

SU1252940A1 |

| Цифровой синтезатор частоты с частотной модуляцией | 1989 |

|

SU1771068A1 |

| Цифровой синтезатор частот | 1987 |

|

SU1510080A1 |

| АДАПТИВНЫЙ СИНТЕЗАТОР ЧАСТОТ С КОММУТАЦИЕЙ ЭЛЕМЕНТОВ КОЛЬЦА ФАЗОВОЙ АВТОПОДСТРОЙКИ | 2010 |

|

RU2419201C1 |

| СПОСОБ ПРОИЗВОДСТВА МОЛОЧНОЙ КАШИ | 1999 |

|

RU2148920C1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| ТУРБИНА ВНУТРЕННЕГО ГОРЕНИЯ СО СВОБОДНЫМ ПОРШНЕМ | 1925 |

|

SU7202A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-09-15—Публикация

1984-07-05—Подача