vj со о XI го о

Изобретение относится к радиотехнике и может быть использовано в приемопередающей радиоаппаратуре.

Целью изобретения является уменьшение нестабильности частоты выходных колебаний.

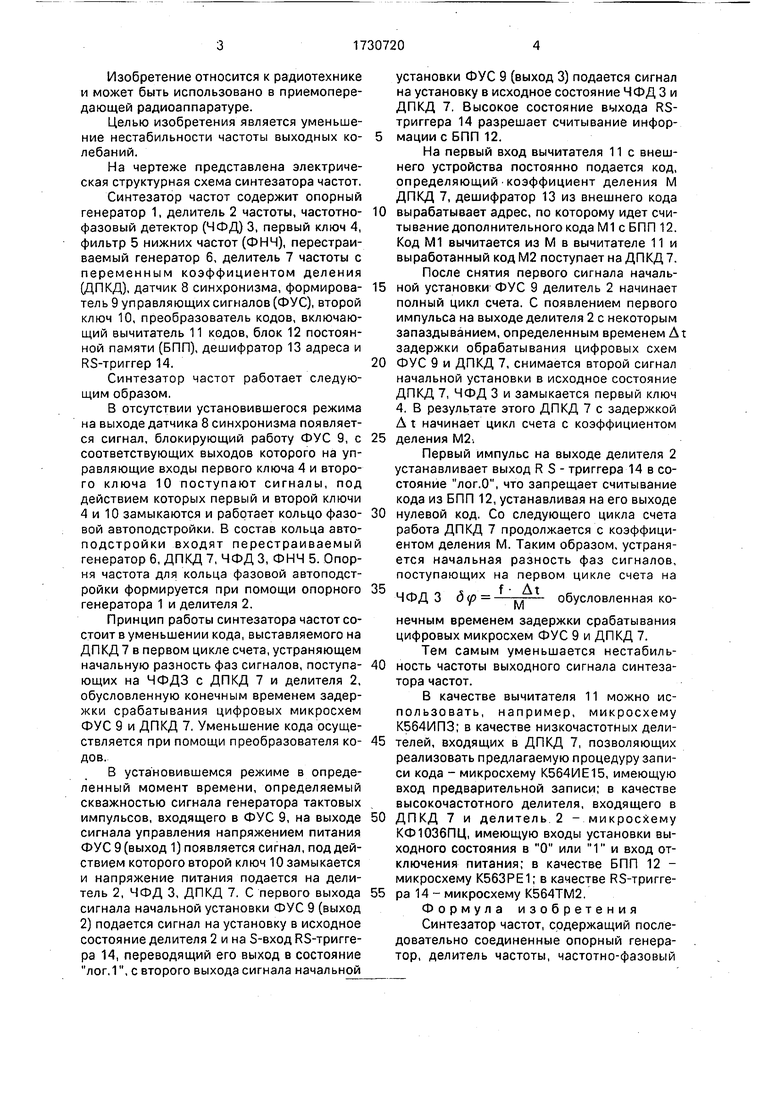

На чертеже представлена электрическая структурная схема синтезатора частот,

Синтезатор частот содержит опорный генератор 1, делитель 2 частоты, частотно- фазовый детектор (ЧФД) 3, первый ключ 4, фильтр 5 нижних частот (ФНЧ), перестраиваемый генератор 6, делитель 7 частоты с переменным коэффициентом деления (ДПКД), датчик 8 синхронизма, формирователь 9 управляющих сигналов (ФУС), второй ключ 10, преобразователь кодов, включающий вычитатель 11 кодов, блок 12 постоянной памяти (БПП), дешифратор 13 адреса и RS-триггер 14.

Синтезатор частот работает следующим образом.

В отсутствии установившегося режима на выходе датчика 8 синхронизма появляется сигнал, блокирующий работу ФУС 9, с соответствующих выходов которого на управляющие входы первого ключа 4 и второго ключа 10 поступают сигналы, под действием которых первый и второй ключи 4 и 10 замыкаются и работает кольцо фазовой автоподстройки. В состав кольца автоподстройки входят перестраиваемый генератор 6, ДПКД 7, ЧФД 3, ФНЧ 5. Опор- ня частота для кольца фазовой автоподстройки формируется при помощи опорного генератора 1 и делителя 2.

Принцип работы синтезатора частот состоит в уменьшении кода, выставляемого на ДПКД 7 в первом цикле счета, устраняющем начальную разность фаз сигналов, поступающих на ЧФДЗ с ДПКД 7 и делителя 2, обусловленную конечным временем задержки срабатывания цифровых микросхем ФУС 9 и ДПКД 7, Уменьшение кода осуществляется при помощи преобразователя кодов.

В установившемся режиме в определенный момент времени, определяемый скважностью сигнала генератора тактовых импульсов, входящего в ФУС 9, на выходе сигнала управления напряжением питания ФУС 9 (выход 1) появляется сигнал, под действием которого второй ключ 10 замыкается и напряжение питания подается на делитель 2, ЧФД 3, ДПКД 7. С первого выхода сигнала начальной установки ФУС 9 (выход 2) подается сигнал на установку в исходное состояние делителя 2 и на S-вход RS-тригге- ра 14, переводящий его выход в состояние лог,1, с второго выхода сигнала начальной

установки ФУС 9 (выход 3) подается сигнал на установку в исходное состояние ЧФД 3 и ДПКД 7. Высокое состояние выхода RS- триггера 14 разрешает считывание информации с БПП 12.

На первый вход вычитателя 11 с внешнего устройства постоянно подается код, определяющий-коэффициент деления М ДПКД 7, дешифратор 13 из внешнего кода

0 вырабатывает адрес, по которому идет считывание дополнительного кода М1 с БПП 12. Код М1 вычитается из М в вычитателе 11 и выработанный код М2 поступает на ДПКД 7. После снятия первого сигнала началь5 ной установки ФУС 9 делитель 2 начинает полный цикл счета. С появлением первого импульса на выходе делителя 2 с некоторым запаздыванием, определенным временем At задержки обрабатывания цифровых схем

0 ФУС 9 и ДПКД 7, снимается второй сигнал начальной установки в исходное состояние ДПКД 7, ЧФД 3 и замыкается первый ключ 4. В результате этого ДПКД 7 с задержкой A t начинает цикл счета с коэффициентом

5 деления М2-.

Первый импульс на выходе делителя 2 устанавливает выход R S - триггера 14 в состояние лог.О, что запрещает считывание кода из БПП 12, устанавливая на его выходе

0 нулевой код. Со следующего цикла счета работа ДПКД 7 продолжается с коэффициентом деления М. Таким образом, устраняется начальная разность фаз сигналов, поступающих на первом цикле счета на

ЧФДЗ -гт- обусловленная конечным временем задержки срабатывания цифровых микросхем ФУС 9 и ДПКД 7. Тем самым уменьшается нестабиль0 ность частоты выходного сигнала синтезатора частот.

В качестве вычитателя 11 можно ис- пользовать, например, микросхему К564ИПЗ; в качестве низкочастотных дели5 телей, входящих в ДПКД 7, позволяющих реализовать предлагаемую процедуру записи кода - микросхему К564ИЕ15, имеющую вход предварительной записи; в качестве высокочастотного делителя, входящего в

0 ДПКД 7 и делитель 2 - микросхему КФ1036ПЦ, имеющую входы установки выходного состояния в О или 1 и вход отключения питания; в качестве БПП 12 - микросхему К563РЕ1; в качестве RS-тригге5 ра 14 - микросхему К564ТМ2.

Формула изобретения Синтезатор частот, содержащий последовательно соединенные опорный генератор, делитель частоты, частотно-фазовый

детектор, первый ключ, фильтр нижних частот, перестраиваемый генератор и делитель частоты с переменным коэффициентом деления, выход которого подключен к второму входу частотно-фазового детектора, после- довательно соединенные датчик синхронизма, формирователь управляющих сигналов и второй ключ, второй вход которого является входом сигнала питания синтезатора частот, выход второго ключа соединен с третьим входом частотно-фазового детектора, вторым входом делителя частоты с переменным коэффициентом деления и с вторым входом делителя частоты, третий вход которого подключен к вто- рому выходу формирователя управляющих сигналов, третий выход которого соединен с третьим входом делителя частоты с переменным коэффициентом деления и с четвертым входом частотно-фазового детектора,

второй вход и четвертый выход формирователя управляющих сигналов подключены соответственно к выходу делителя частоты и к второму входу первого ключа, а вход датчика синхронизма соединен с выходом частотно-фазового детектора, отличающий- с я тем, что, с целью уменьшения нестабильности частоты выходных колебаний, введен преобразователь кодов, который выполнен в виде последовательно соединенных дешифратора адреса, блока постоянной памяти и вычи- тателя кодов, а также введен RS-триггер, первый, второй вход и выход которого соответственно подключены к выходу делителя частоты, к второму выходу формирователя управляющих сигналов и к управляющему входу блока постоянной памяти, вход дешифратора адреса объединен с вторым входом вычитателя кодов и является кодовым входом синтезатора частот.

| название | год | авторы | номер документа |

|---|---|---|---|

| Синтезатор частоты | 1984 |

|

SU1257845A1 |

| Цифровой синтезатор частоты | 1982 |

|

SU1109914A1 |

| СИНТЕЗАТОР ЧАСТОТ | 2010 |

|

RU2434322C1 |

| Синтезатор частоты | 1981 |

|

SU1007202A1 |

| Цифровой синтезатор частот Усачева И.П. | 1986 |

|

SU1417186A2 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ | 2008 |

|

RU2379830C1 |

| СИНТЕЗАТОР ЧАСТОТ | 2009 |

|

RU2394367C1 |

| СИНТЕЗАТОР ЧАСТОТ | 2009 |

|

RU2395899C1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ | 2009 |

|

RU2416158C1 |

| Цифровой синтезатор частот | 1987 |

|

SU1510080A1 |

Изобретение относится к области радиотехники. Цель изобретения - уменьшение нестабильности частоты выходных колебаний. Синтезатор частот содержит опорный генератор 1, делитель 2 частоты, частотнофазовый детектор (ЧФД) 3, первый ключ 4, фильтр 5 нижних частот (ФНЧ), перестраиваемый генератор 6, делитель 7 частоты с переменным коэффициентом деления (ДПКД), датчик 8 синхронизма, формирователь 9 управляющих сигналов (ФУС), второй ключ 10, преобразователь кодов, включающий вычитатель 11 кодов, блок 12 постоянной памяти (БПП), дешифратор 13 адреса, и RS- триггер 14. Принцип работы синтезатора частот состоит в уменьшении кода, выставляемого на ДПКД 7 в первом цикле счета, устраняющем начальную разность фаз сигналов. Уменьшение кода осуществляется при помощи дешифратора 13, БПП 12 и вычитателя 11 по команде с RS-триггера 14. Управление RS-триггера 14. Управление RS-триггером 14 осуществляется с одного из выходов ФУС 9. 1 ил. 1 сл С

| Синтезатор частот | 1982 |

|

SU1150764A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Синтезатор частоты | 1984 |

|

SU1257845A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-04-30—Публикация

1989-07-24—Подача