2, Сумматор по п. 1, о т л и чающийс я тем, что блок контроля содержит триггер, первый и второй элементы ИЛИ-НЕ и первый, второй, третий, четвертый и пятый элементы И, причем первый вход блока соединен с первьгми входами первого элемента ИЛИ-НЕ, первого и второго элементов И, вьоходы которых соединены соответственно с первым, вторым и третьим входами второго элемента ИЛИ-НЕ, второй вход блока соединен с вторым входом первого элемента ИЛИ-НЕ, с втоpfcjM входом первого элемента И и с первым входом третьего элемента И, выход которого соединен с четвертым

входом второго элемента ИЛИ-НЕ, третий вход блока соединен с вторыми входами второго и третьего элементов И и с третьим входом первого элемента ИЛИ-НЕ, выход которого связан с первым входом четвертого элемента И, выход второго элемента ИЛИ-НЕ соединен с первым входом пятого элемента И, тактовый вход блока соединен с вторыми входами четвертого и пятого элементов И, выходы которых соедин ны соответственно с единичным и нулевым входами триггера,единичный и нулевой выходы которого являются соответственно первым и вторым выходами блока..

| название | год | авторы | номер документа |

|---|---|---|---|

| Табличный сумматор по модулю три с коррекцией ошибок | 1983 |

|

SU1124311A1 |

| Устройство для контроля и резервирования информационно-измерительных систем | 1990 |

|

SU1716628A1 |

| МОДУЛЬ ДЛЯ ОБМЕНА СООБЩЕНИЯМИ | 2003 |

|

RU2249849C1 |

| Табличный сумматор вычетов | 1987 |

|

SU1441396A1 |

| Устройство для обнаружения и исправления ошибок в непозиционном коде | 1983 |

|

SU1134941A1 |

| Счетчик импульсов | 1985 |

|

SU1298906A1 |

| Устройство для контроля логических блоков | 1982 |

|

SU1105897A1 |

| Устройство для контроля и резервирования информационно-измерительных систем | 1989 |

|

SU1709569A1 |

| СПОСОБ ПЕРЕДАЧИ ДИСКРЕТНОЙ ИНФОРМАЦИИ | 2006 |

|

RU2344544C2 |

| МОДУЛЬ ВВОДА-ВЫВОДА СИСТЕМЫ ЦИФРОВОГО УПРАВЛЕНИЯ | 1991 |

|

RU2032201C1 |

1

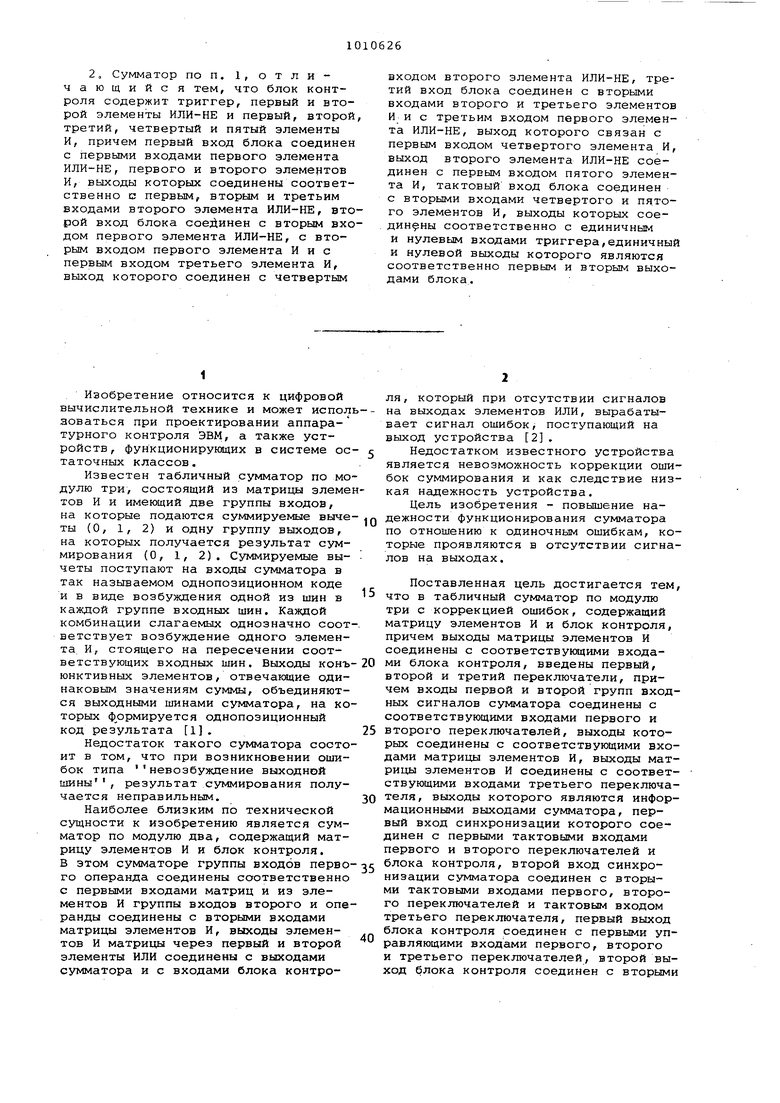

Изобретение относится к цифровой вычислительной технике и может исполь аоваться при проектировании аппаратурного контроля ЭВМ, а также устройств, функционируквдих в системе остаточных классов.

Известен табличный сумматор по модулю три, состоящий из матрицы элемен тов И и имеющий две группы входов/ на которые подаются суммируемые вычеты (О, 1, 2) и одну группу выходов, на которых получается результат суммирования (О, 1, 2). Суммируемые вычеты поступают на входы сумматора в так называемом однопозиционном коде и в виде возбуждения одной из шин в каждой группе входных шин. Каждой комбинации слагаемых однозначно соответствует возбуждение одного элемента И, стоящего на пересечении соответствующих входных шин. Выходы конъюнктивных элементов, отвечакидие одинаковым значениям суммы, объединяются выходными шинами сумматора, на которых ф ормируется однопозиционный код результата 1.

Недостаток такого сумматора состоит в том, что при возникновении ошибок типа невозбуждение выходной шины , результат суммирования получается неправильным.

Наиболее близким по технической сущности к изобретению является сумматор по модулю два, содержащий матрицу элементов И и блок контроля. В этом сумматоре группы входов первого операнда соединены соответственно с первыми входами матриц и из элементов И группы входов второго и операнды соединены с вторыми входами матрицы элементов И, выходы элементов И матрицы через первый и второй элементы ИЛИ соединены с выходами сумматора и с входами блока контроля, который при отсутствии сигналов на выходах элементов ИЛИ, вырабатывает сигнал ошибок, поступающий на выход устройства 2.

Недостатком известного устройства является невозможность коррекции ошибок суммирования и как следствие низкая надежность устройства.

Цель изобретения - повышение надежности функционирования сумматора по отношению к одиночным ошибкам, которые проявляются в отсутствии сигналов на выходах.

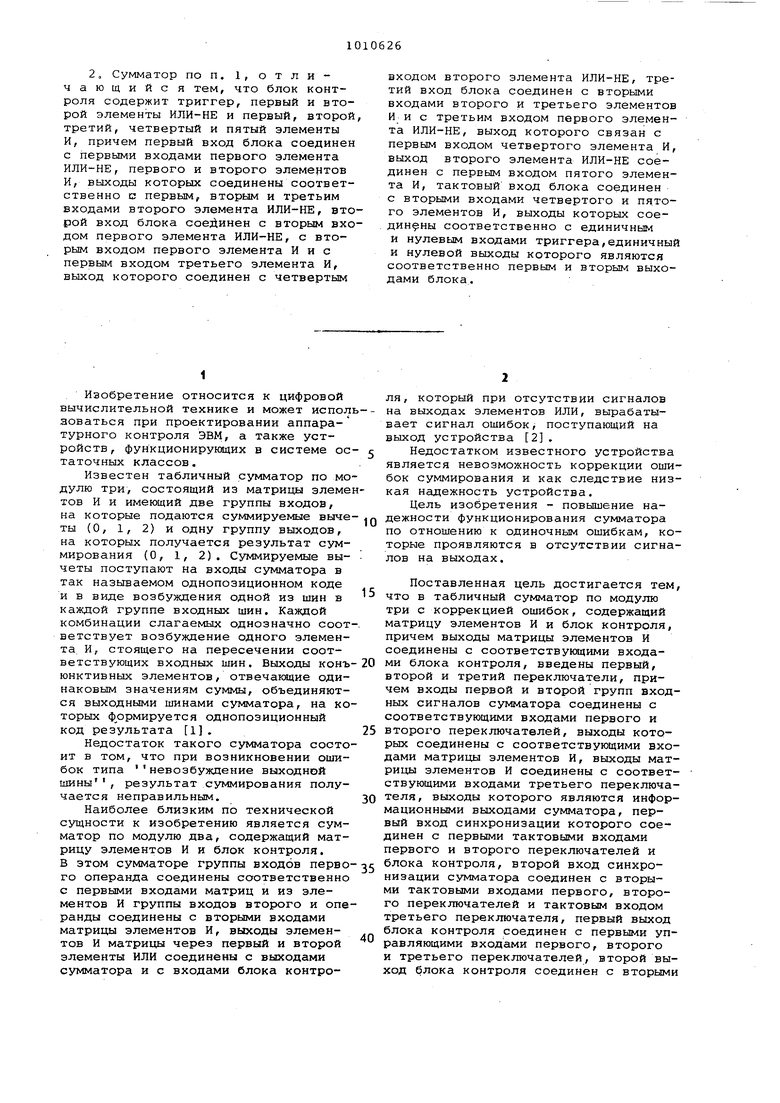

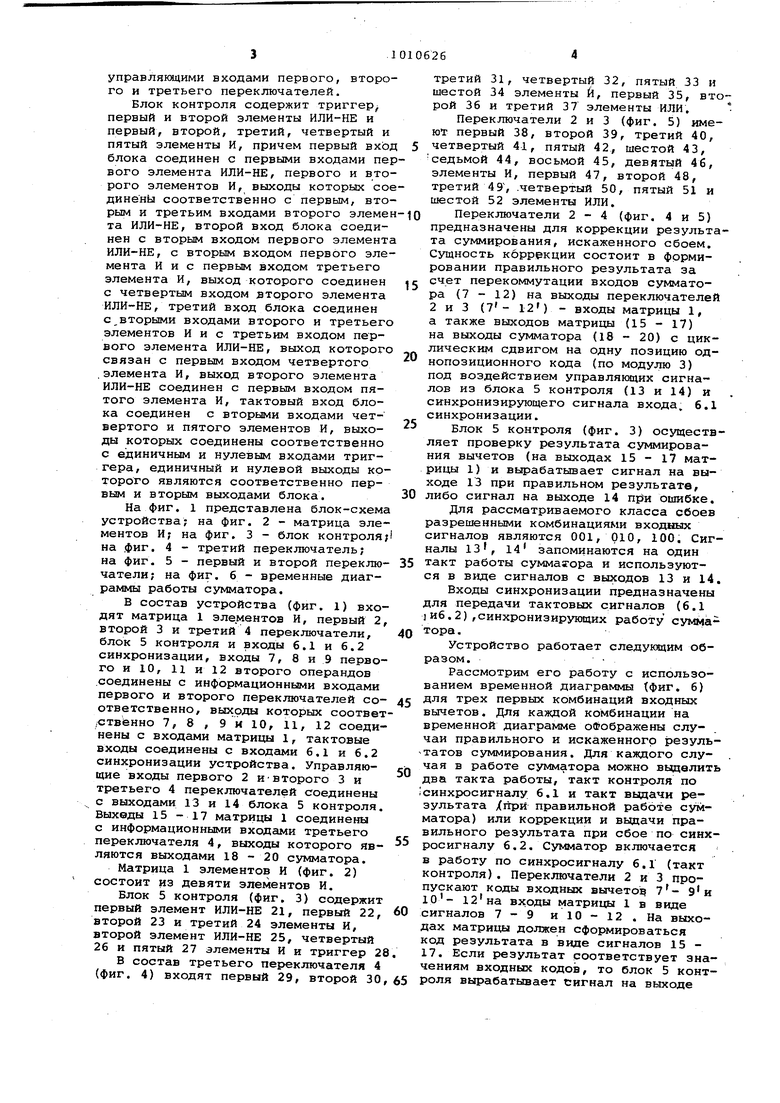

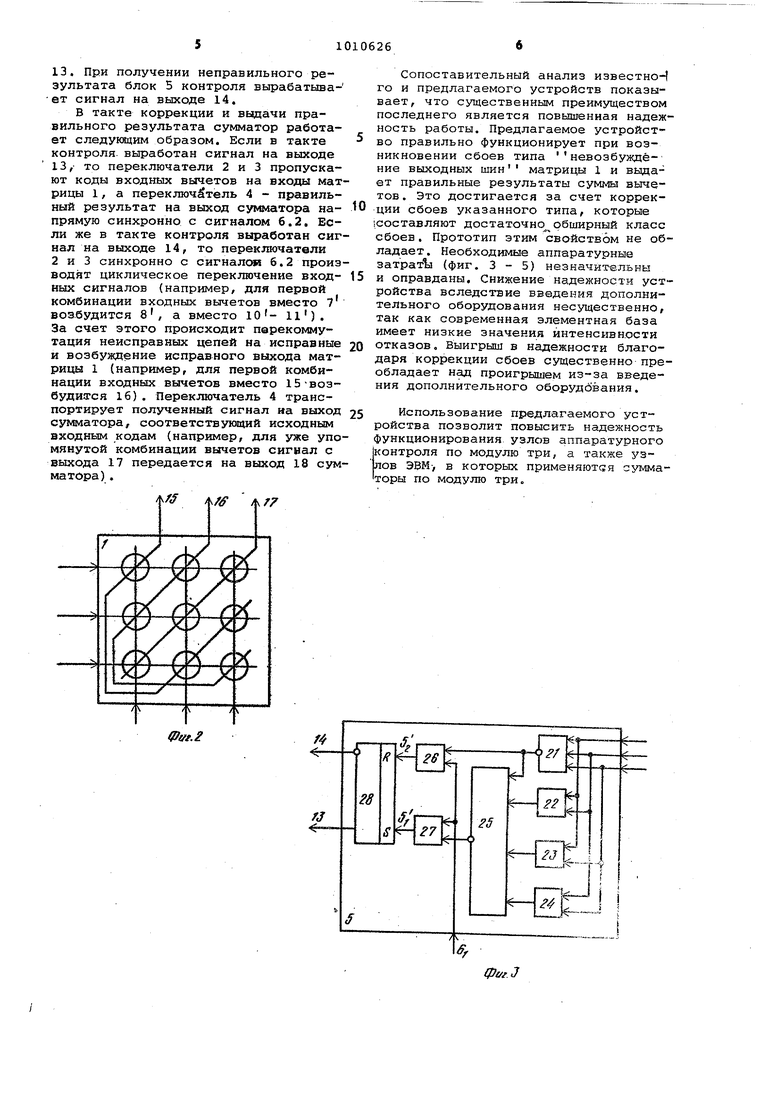

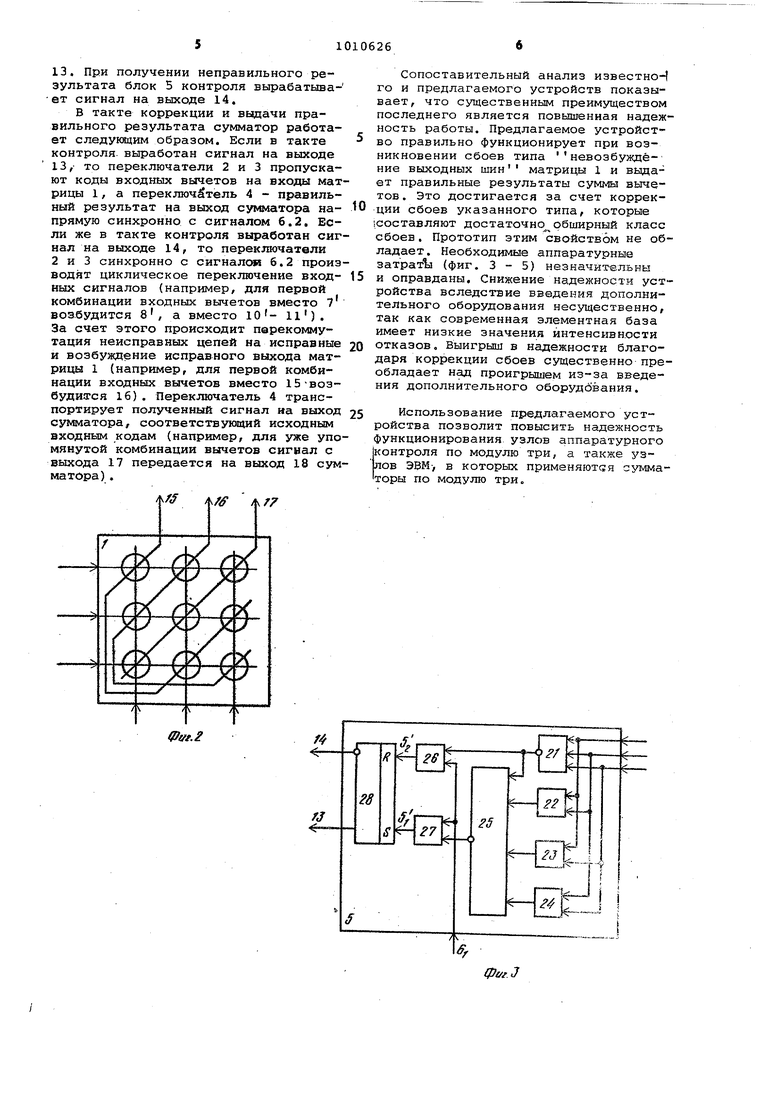

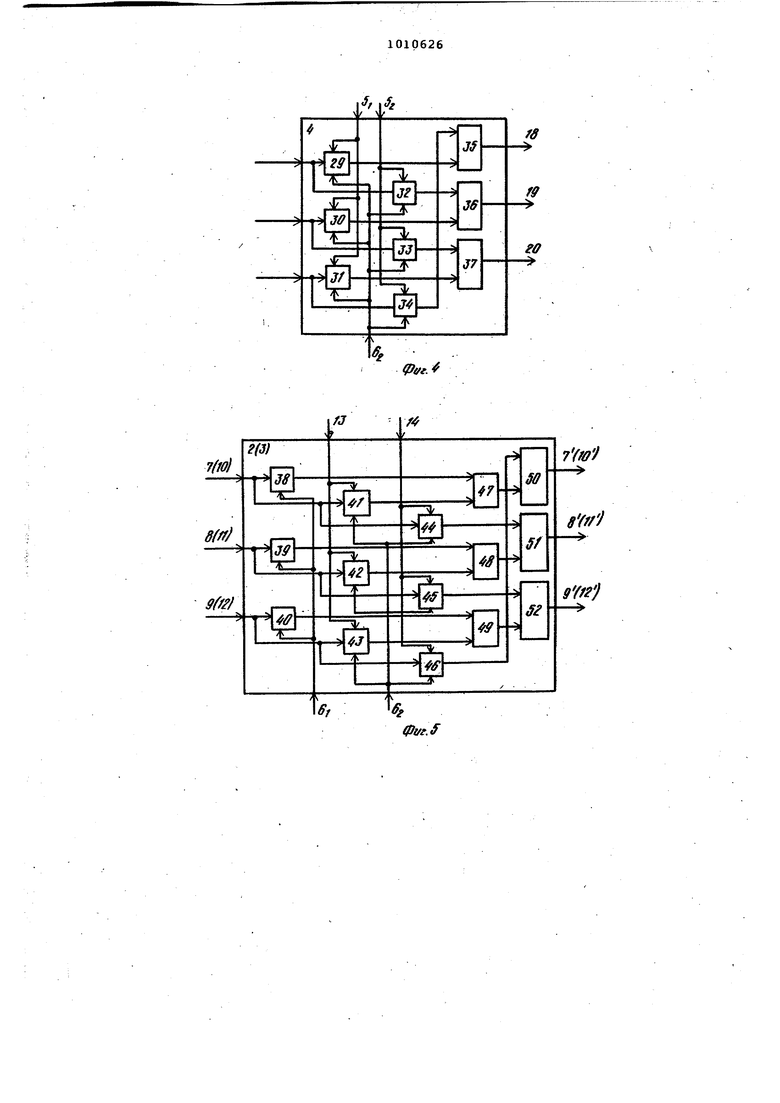

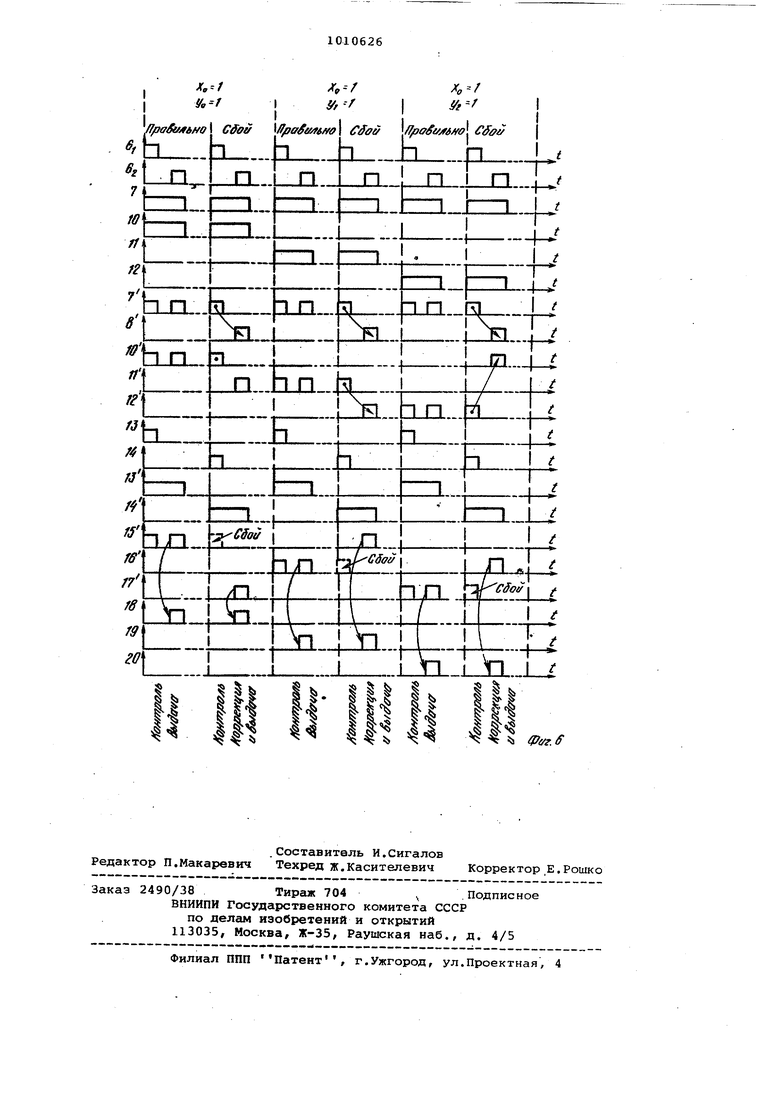

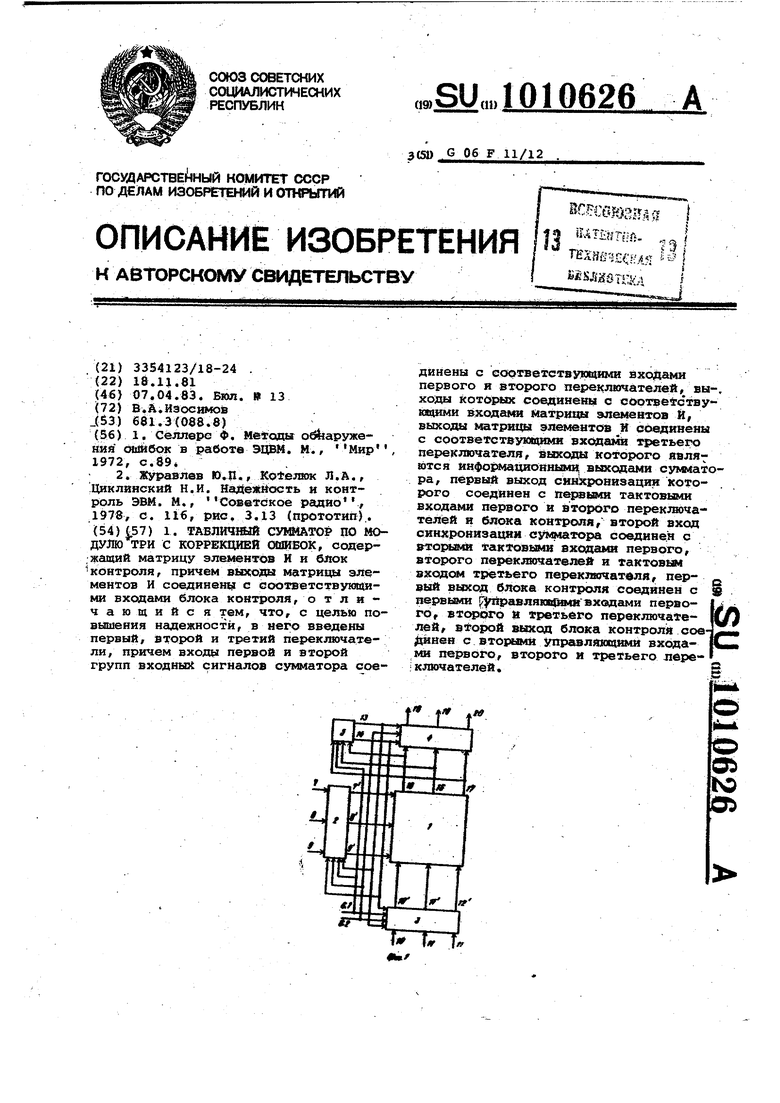

Поставленная цель достигается тем, что в табличный сумматор по модулю три с коррекцией ошибок, содержащий матрицу элементов И и блок контроля, причем выходы матрицы элементов И соединены с соответствукяцими входами блока контроля, введены первый, второй и третий переключатели, причем входы первой и второй групп входных сигналов сумматора соединены с соответствующими входами первого и второго переключателей, выходы которых соединены с соответствукяцими входами матрицы элементов И, выходы матрицы элементов И соединены с соответствующими входами третьего переключателя, выходы которого являются информационными выходами сумматора, первый вход синхронизации которого соединен с первыми тактовыми входами первого и второго переключателей и блока контроля, второй вход синхронизации сумматора соединен с вторыми тактовыми входами первого, второго переключателей и тактовым входом третьего переключателя, первый выход блока контроля соединен с первыми управляющими входами первого, второго и третьего переключателей, второй выход блока контроля соединен с вторыми управлякидими входами первого, второ го и третьего переключателей. Блок контроля содержит триггер первый и второй элементы ИЛИ-НЕ и первый, второй, третий, четвертый и пятый элементы И, причем первый вхо блока соединен с первыми входами пе вого элемента ИЛИ-НЕ, первого и вто рого элементов И, выходы которых со диненЬа соответственно с первым, вто рым и третьим входами второго элеме та ИЛИ-НЕ, второй вход блока соединен с вторым входом первого элемент ИЛИ-НЕ, с вторым входом первого эле мента И и с первым входом третьего элемента И, выход которого соединен с четвертым входом второго элемента ИЛИ-НЕ, третий вход блока соединен с,вторыми входами второго и третьего элементов И и с третьим входом первого элемента ИЛИ-НЕ, выход которого связан с первым входом четвертого .элемента И, выход второго элемента ИЛИ-НЕ соединен с первым входом пятого элемента И, тактовый вход блока соединен с вторини входами четвертого и пятого элементов И, выходы которых соединены соответственно с единичным и нулевым входами триггера, единичный и нулевой выходы которого являются соответственно первым и вторым выходами блока. На фиг. 1 представлена блок-схема устройства; на фиг. 2 - матрица элементов И; на фиг, 3 - блок контроля на .фиг. 4 - третий переключатель; на фиг. 5 - первый и второй переключатели; на фиг. 6 - временные диаграммы работы сумматора. В состав устройства (фиг. 1) входят матрица 1 элементов И, первый 2 второй 3 и третий 4 переключатели, блок 5 контроля и входы 6.1 и 6.2 синхронизации, входы 7, 8 и 9 первого и 10, Ии12 второго операндов .соединены с информационными входами первого и второго переключателей соответственно, выходы которых соответ ;ствённо 7, 8 , 9и10, 11, 12 соединены с входами матрицы 1, тактовые входы соединены с входами 6.1 и 6.2 синхронизации устройства. Управляющие входы первого 2 и-второго 3 и третьего 4 переключателей соединены с выходами 13 и 14 блока 5 контроля. Выходы 15 - 17 матрицы 1 соединены с информационными входами третьего переключателя 4, выходы которого являются выходами 18 - 20 сумматора. Матрица 1 элементов И (фиг. 2) состоит из девяти элементов И. Влок 5 контроля (фиг. 3) содержит первый элемент ИЛИ-НЕ 21, первый 22, второй 23 и третий 24 элементы И, второй элемент ИЛИ-НЕ 25, четвертый 26 и пятый 27 элементы И и триггер 2 В состав третьего переключателя 4 (фиг. 4) входят первый 29, второй 30 третий 31, четвертый 32, пятый 33 и шестой 34 элементы И, первый 35, второй 36 и третий 37 элементы ИЛИ. Переключатели 2 и 3 (фиг. 5) имеют первый 38, второй 39, третий 40, четвертый 41, пятый 42, шестой 43, седьмой 44, восьмой 45, девятый 46, элементы И, первый 47, второй 48, третий 49, .четвертый 50, пятый 51 и шестой 52 элементы ИЛИ. Переключатели 2-4 (фиг. 4 и 5) предназначены для коррекции результата суммирования, искаженного сбоем. Сущность коррекции состоит в Формировании правильного результата за счет перекоммутации входов сумматора (7 - 12) на выходы переключателей 2 и 3 (7- 12) - входы матрицы 1, а также выходов матрицы (15 - 17) на выходы сумматора (18 - 20) с циклическим сдвигом на одну позицию однопозиционного кода (по модулю 3) под воздействием управлякидих сигналов из блока 5 контроля (13 и 14) и синхронизирующего сигнала входа, 6.1 синхронизации. Блок 5 контроля (фиг. 3) осуществляет проверку результата суммирования вычетов (на выходах 15 - 17 матрицы 1) и вырабатывает сигнал на выходе 13 при правильном результате, либо сигнал на выходе 14 ошибке. Для рассматриваемого класса сбоев разрешенными комбинациями входных сигналов являются 001, 010, 100. Сигналы 13, 14 запоминаются на один такт работы суммагора и используются в В1зде сигналов с выходов 13 и 14. Входы синхронизации предназначены для передачи тактовых сигналов (6.1 1 и6. 2) ,синхронизирующих работу сумматора , Устройство работает следующим образом. Рассмотрим его работу с использованием временной диаграммы (фиг. 6) для трех первых комбинаций входных вычетов. Для каждой комбинации на временной диаграмме отображены случаи правильного и искаженного результатов суммирования. Для каждого случая в работе сумматора можно выделить два такта работы, такт контроля по синхросигналу 6.1 и такт вьвдачи результата /при правильной работе сумматора) или коррекции и выдачи правильного результата при сбое по синхросигналу 6.2. Сумматор включается в работу по синхросигналу 6.1 (такт контроля). Переключатели 2 и 3 пропускают коды входных вычетоэ 7- Ю- 12на входы матрицы 1 в виде сигналов 7-9 и10-12.На выходах матрицы должен сформироваться код результата в виде сигналов 15 17. Если результат соответствует значениям входных кодов, то блок 5 контроля вырабатывает сигнал на выходе

В такте коррекции и вьвдачи правильного результата сумматор работает следугадим образом. Если в такте контроля, выработан сигнал на выходе 13,- то переключатели 2 и 3 пропускают коды входных вычетов на входы матрицы 1, а переключатель 4 - правильный результат на выход сумматора напрямую синхронно с сигналом 6.2. Если же в такте контроля выработан сигнал на выходе 14, то переключатели 2 и 3 синхронно с сигналсяи 6.2 производят циклическое переключение входных сигналов {например, для первой комбинации входных вычетов вместо 7 воабудится 8, а вместо 10- 11). За счет этого происходит пврекоммутация неисправных цепей на исправные и возбуждение исправного выхода матрицы 1 (например, для первой комбинации входных вычетов вместо 15-возбудится 16). Переключатель 4 транспортирует полученный сигнал на выход сумматора, соответствующий исходным входным кодам (например, для уже упомянутой комбинации вычетов сигнал с выхода 17 передается на выход 18 сумматора) .

Сопоставительный анализ известноН го и предлагаемого устройств показывает, что существенным преимуществом последнего является повышенная надежность работы. Предлагаемое устройство правильно функционирует при возникновении сбоев типа невозбуждёние выходных шин матрицы 1 и выдает правильные результаты суммы вычетов. Это достигается за счет коррекции сбоев указанного типа, которые {составляют достаточно обширный класс сбоев. Прототип этим свойством не обладает. Необходимые аппаратурные затратна (фиг. 3-5) незначительны и оправданы. Снижение надежности устройства вследствие введения дополнительного оборудования несущественно, так как современная элементная база имеет низкие значения интенсивности отказов. Выигрыш в надежности благодаря коррекции сбоев существенно преобладает над проигрышем из-за введения дополнительного оборудбвания.

Использование предлагаемого устройства позволит повысить надежность функционирования узлов аппаратурного {контроля по модулю три, а также узшов ЭВМ в которых применяютая сумматоры по модулю три.

4V/7

фуе.1

f4

fj

2(3) A 38

7(10}

d/ff}

ffffff

ff

7Wf

8ff/

Sf

9ff2)

S2

4ff

л--/

л /

E::Lta..i

® § S

I 11

IIL.

11- 1

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Селлере Ф | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| М., Мир, 1972, с., 2 | |||

| Журавлев Ю.П., Л.А., Циклйнский Н.И | |||

| НзДеясйость и контроль ЭВМ | |||

| М., Советское радио, 1978, с | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1983-04-07—Публикация

1981-11-18—Подача