ственно седьмого, восьмого и девятого элементов И, выход первого элемента И соединен с вторым входом первого элемента ИЛИ и первыми входами третьего и пятого элементов ИЛИ блока контроля, выход второго элемента И соединен с вторым входом первого элемента ИЛИ и первым входом четвертого и вторым входом пятого элементов ИЛИ блока контроля, выход третьего элемента И соединен с третьим входом первого элемента ИЛИ и вторыми входами третьего и четвертого элементов ИЛИ блока контроля, первый тактовый вход блока контроля соединен с вторыми входами шестого, седьмого.

восьмого и девятого элементов И, выходы которых соединены с единичными входами соответственно второго, третьего, четвертого и пятого триггеров третий тактовый вход блока контроля соединен с нулевыми входами второго, третьего, четвертого и пятого триггеров блока контроля, единичный выход второго триггера блока контроля соединен с вторыми входами второго, четвертого и шестого элементов И блока коррекции, единичные выходы третьего, четвертого и пятого триггеров блока контроля соединены с вторыми входами соответственно первого, третьего и пятого элементов И блока коррекции.

| название | год | авторы | номер документа |

|---|---|---|---|

| Табличный сумматор по модулю три с коррекцией ошибок | 1981 |

|

SU1010626A1 |

| Запоминающее устройство | 1975 |

|

SU746741A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

| Генератор псевдослучайной последовательности импульсов | 1989 |

|

SU1735846A1 |

| Устройство для обнаружения и исправления ошибок | 1985 |

|

SU1368995A1 |

| Система передачи и приема информации с коррекцией ошибок | 1985 |

|

SU1311036A1 |

| Устройство для синхронного накопления кодовых комбинаций двоичных сигналов | 1984 |

|

SU1256211A2 |

| Устройство контроля кода счетчика | 1979 |

|

SU815920A1 |

| УСТРОЙСТВО ДЛЯ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ МНОГОКАНАЛЬНОЙ ЦИФРОВОЙ ИНФОРМАЦИИ | 1995 |

|

RU2107953C1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ РАДИОТЕЛЕМЕТРИЧЕСКИХ СИГНАЛОВ | 1994 |

|

RU2126139C1 |

ТАБЛИЧНЫЙ СУММАТОР ПО МОДУЛЮ ТРИ С КОРРЕКЦИЕЙ ОШИБОК, содержащий матрицу элементов И, первый, второй, третий переключатели и блок контроля, содержащий первый триггер, пять элементов И и элемент ИЛИ-НЕ, причем первый, второй и третий контролирующие выходы элементов И матрицы соединены соответственно с первым, , вторым и третьим входами элемента ИЛИНЕ блока контроля,первый вход элемента ИЛИ-НЕ блока контроля соединен с первыми входами первого и второго элементов И, второй вход элемента ИЛИ-НЕ блока контроля соединен с вторым входом первого элемента И и первым входом третьего элемента И блока контроля, третий вход элемента ИЛИ-НЕ блока контроля соединен с вторыми входами второго и третьего элементов И блока контроля, выходы четвертого и пятого.элементов И блока контроля соединены соответственно с единичным и нулевым входами первого триггера блока контроля, первый тактовый вход устройства соединен с первыми входами четвертого и пятого элементов И блока контроля, с первыми управляющими входами первого и второго переключателей, второй тактовый вход устройства соединен с вторыми управляющими входами первого, второго и первым управляющим входом третьего переключателя, входы первого и второго операндов сумматора соединены соответственно с информационными входами первого и второго переключателей, выходы первого и второго переключателей соединены соответствен но с первыми и вторыми входами элементов И, входами матрицы, единичный выход первого триггера блока контроля соединен с третьими управляющими входами первого, второго и вторым управляющим входом третьего переключателей, нулевой- выход первого триггера блока контроля соединен с четвертыми управляющими входами -первого, второго и третьим управляющим входом третьего переключателей, отличающийся тем, что, с целью повышения достоверности, в него введен блок коррекции, содержащий шесть элементов И и три элег«1ен.та ИЛИ, причем каждый i-й выход матрицы элементов И (где ,2,3) соединен с первыми входами ( 1)-го и 2i-ro элементов И блока коррекции, выходы

Изобретение относится к цифровой вычислительной технике и может исползоваться в системах аппаратного контроля ЭВМ и устройств, функционирующих в системе остаточных классов,

Известен табличный сумматор по модулю три, содержащий две группы

элементов И, ИЛИ, узел контроля ошибки и имеющий две группы входных шин, на которые подаются слагаемые, и одн группу выходных шин, на которых получается результат суммирования, причем выходные шины соединены с входами узла контроля ошибок, на выходе которого формируется сигнал ошибки при возникновении неправильного результата суммирования 13,

Недостатком такого сумматора является невозможность корректировать ошибки.

Наиболее близким к предлагаемому по технической сущности является табличный сумматор по модулю три с коррекцией ошибок, содержащий матрицу элементов И, блок контроля, первый, второй, третий переключатели, причем входы блока контроля соединены с соответствующими выходами матрицы, входы первой и второй групп входных сигналов сумматора соединены с соответствующими входами первого и вто рого переключателей, выходы которых соединены с соответствующими входами матрицы элементов И, выходы матрицы элементов И соединены с соответствующими входами третьего переключателя, выходы которого являются информационными выходами сумматора, первый вход синхронизации которого соединен с первыми тактовыми входами первого и второго переключателей и блока контроля, вто,рой вход синхронизации сумматора соединен с вторыми тактовыми входами

первого, второго переключателей и тактовыми входами третьего переключателя, первый выход блока контроля соединен с первыми управляющими входами первого, второго и третьего переключателей, второй выход блока контроля соединен с вторыми управляющими входами первого, второго и третьего переключателей С23.

Недостатком этого устройства является то, что оно не способно корректировать ошибки типа ложное возбуждение выходных шин матрицы при возникновении одиночных отказов и сбоев в матрице.

Цель изобретения ,- повышение достоверности функционирования табличного сумматора по модулю три путем расширения его возможностей по коррекции Ошибок типа ложное возбуждение выходных шин матрицы вызванных одиночными отказами и сбоями в матрице элементов И,

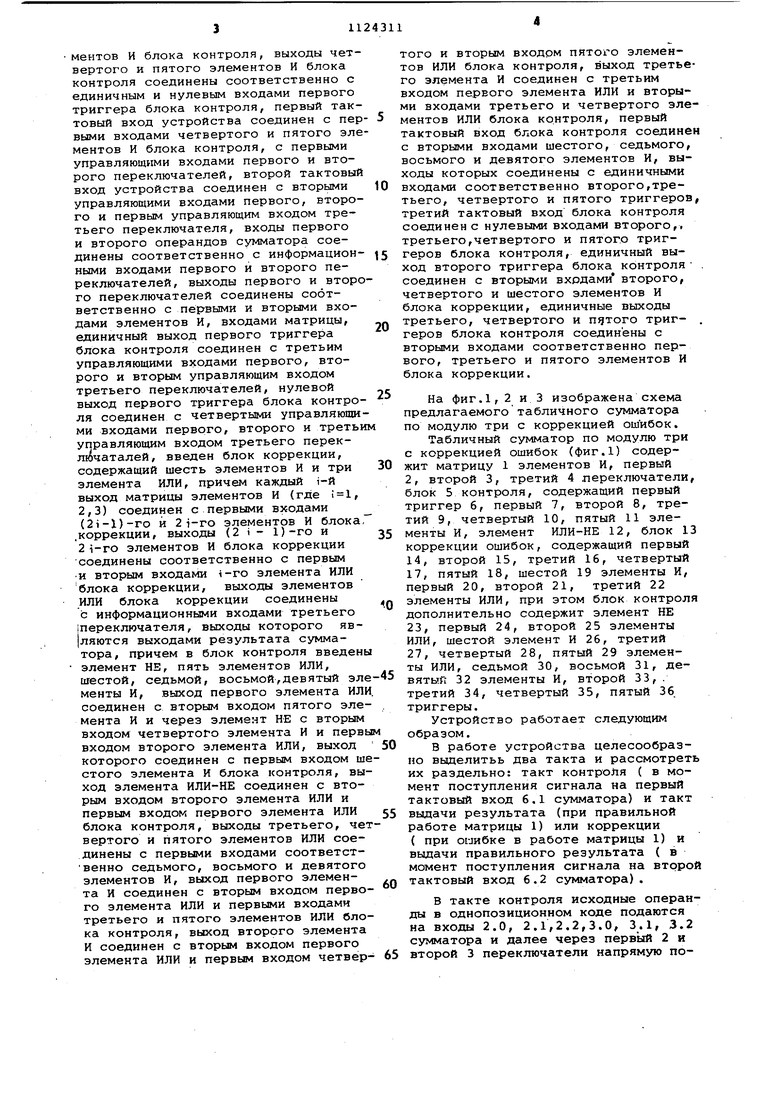

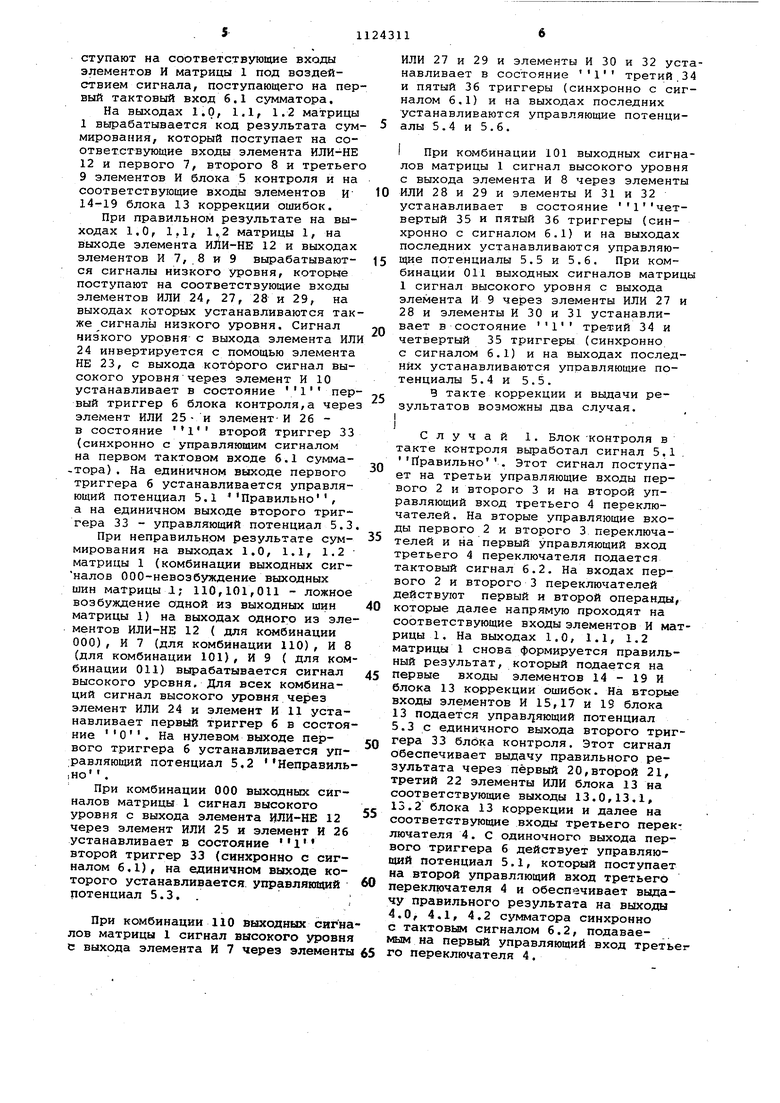

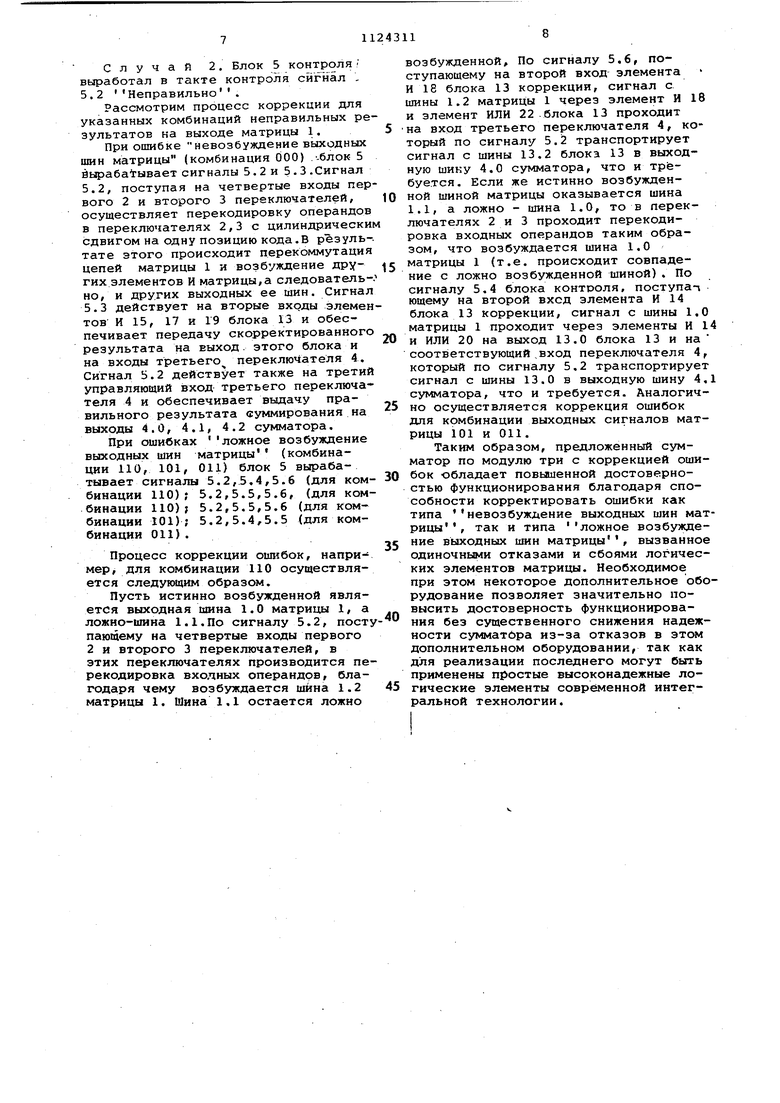

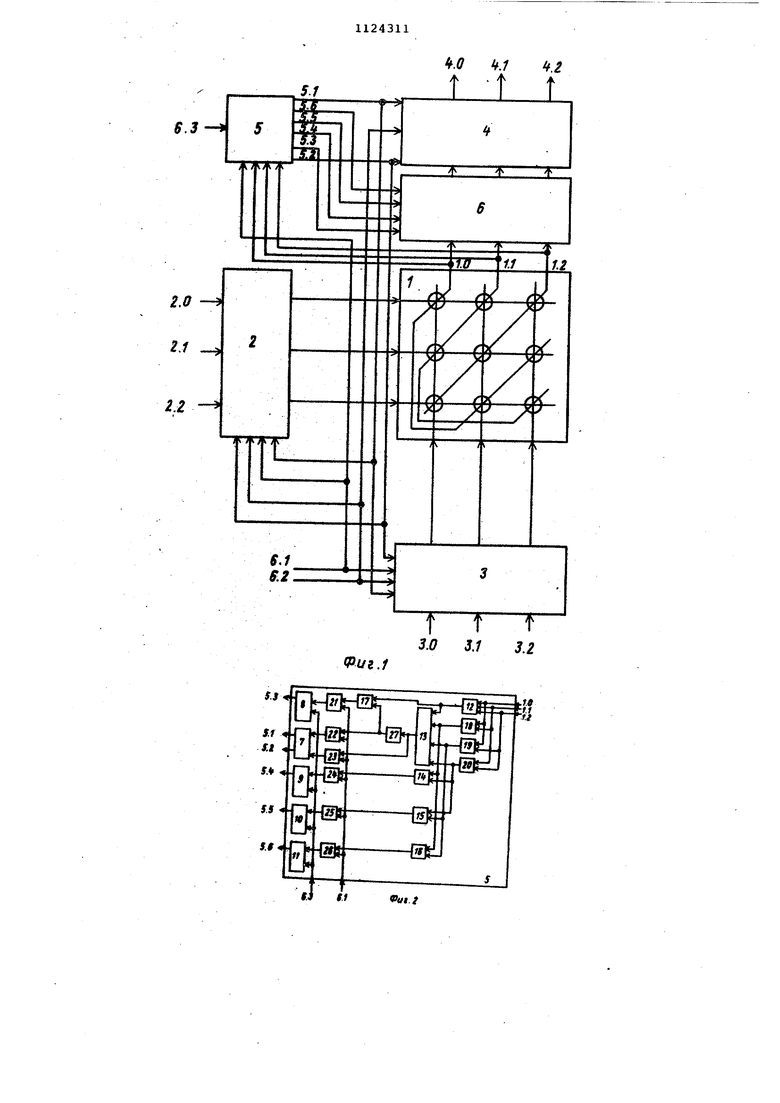

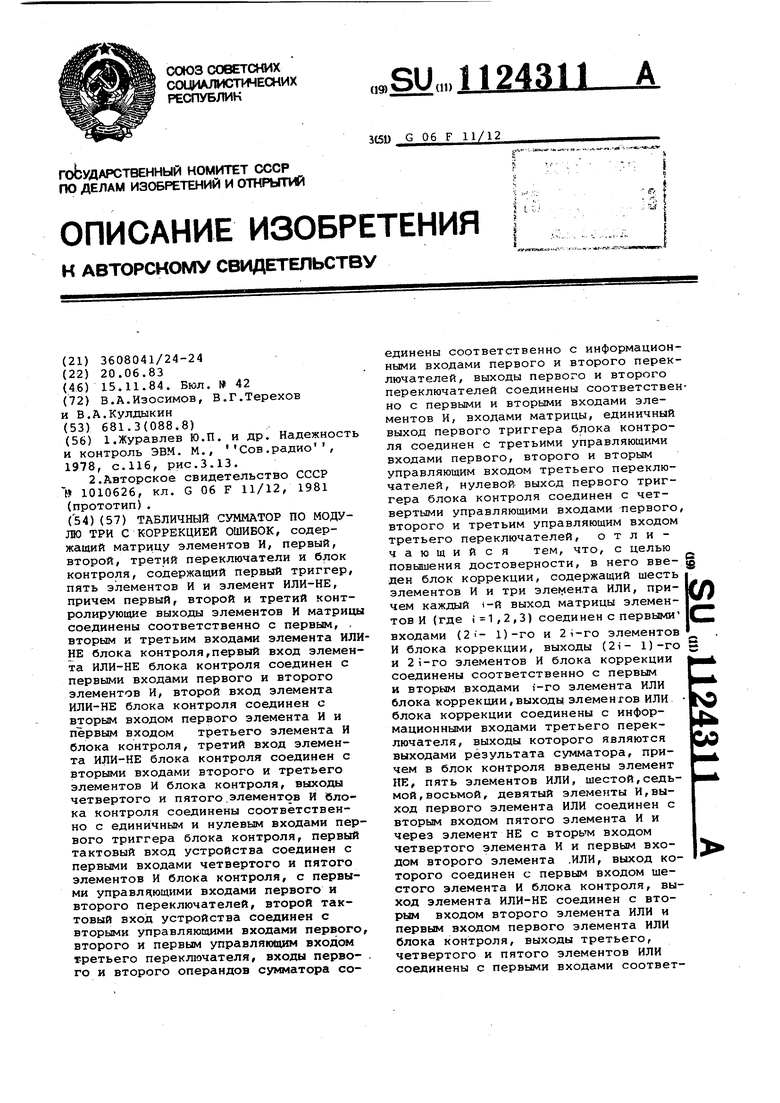

Поставленная цель достигается тем, что.в сумматор по модулю три с коррекцией ошибок, содержащий матрицу элементов И, первый, второй, третий переключатели и блок контроля, содержащий первый триггер, пять элементов И и элемент ИЛИ-НЕ, причем первый, второй и третий контролируемые выходы элементов И матрицы соединены соответственно с первым, вторым и третьим входами элемента ИЛИ-НЕ блока контроля, первый вход элемента ИЛИ-НЕ блока контроля соединен с первыми входами первого и второго элементов И,второй вход элемента ИЛИ-НЕ блока контроля соедине с вторым входом первого элемента И и первым входом третьего элемента И блока контроля, третий вход элемента ИЛИ-НЕ блока контроля соединен с вторыми входами второго и третьего элементов И блока контроля, выходы четвертого и пятого элементов И блока контроля соединены соответственно с единичным и нулевым входами первого триггера блока контроля, первый тактовый вход устройства соединен с пер выми входами четвертого и пятого эле ментов И блока контроля, с первьлми управляющими входами первого и второго переключателей, второй тактовый вход устройства соединен с вторыми управляющими входами первого, второго и первым управляющим входом третьего переключателя, входы первого и второго операндов сумматора соединены соответственно с информационными входами первого и второго переключателей, выходы первого и второ го переключателей соединены соответственно с первыми и вторыми входами элементов И, входами матрицы, единичный выход первого триггера блока контроля соединен с третьим управляющими входами первого, второго и вторым управляющим входом третьего переключателей, нулевой выход первого триггера блока контро ля соединен с четвертыми управляющи ми входами первого, второго и треть управляющим входом третьего перекл 4чаталей, введен блок коррекции, содержащий шесть элементов И и три элемента ИЛИ, причем каждый i-й выход матрицы элементов И (где , 2,3) соединен с первыми входами (2i-l)-ro и 2i-ro элементов И блока .коррекции, выходы (2 i - 1)-го и 2 i-ro элементов И блока коррекции соединены соответственно с первым и вторым входами i-ro элемента ИЛИ блока коррекции, выходы элементов ИЛИ блока коррекции соединены с информационными входами третьего переключателя, выходы которого яв|ляются выходами результата сумматора, причем в блок контроля введен элемент НЕ, пять элементов ИЛИ, шестой, седьмой, восьмой,девятый эл менты И, выход первого элемента ИЛ соединен с вторым входом пятого эле мента И и череэ элемент НЕ с вторым входом четвертого элемента И и перв входом второго элемента ИЛИ, выход которого соединен с первым входом ш стого элемента И блока контроля, вы ход элемента ИЛИ-НЕ соединен с вторым входом второго элемента ИЛИ и первым входом первого элемента ИЛИ блока контроля, выходы третьего, че вертого и пятого элементов ИЛИ соединены с первыми входами соответственно седьмого, восьмого и девятого элементов И, выход первого элемента И соединен с вторым входом перво го элемента ИЛИ и первыми входами третьего и пятого элементов ИЛИ бло ка контроля, выход второго элемента И соединен с вторым входом первого элемента ИЛИ и первым входом четвер того и вторым входом пятого элементов ИЛИ блока контроля, выход третьего элемента И соединен с третьим входом первого элемента ИЛИ и вторыми входами третьего и четвертого элементов ИЛИ блока контроля, первый тактовый вход блока контроля соединен с вторыми входами шестого, седьмого, восьмого и девятого элементов И, выходы которых соединены с единичными входами соответственно второго,третьего, четвертого и пятого триггеров, третий тактовый вход блока контроля соединен с нулевыми входами второго,, третьего,четвертого и пятого триггеров блока контроля, единичный выход второго триггера блока контроля . соединен с вторыми вхрдами второго, четвертого и шестого элементов И блока коррекции, единичные выходы третьего, четвертого и пдтого триг- . геров блока контроля соединены с вторыми входами соответственно первого, третьего и пятого элементов И блока коррекции. На фиг.1,2 и 3 изображена схема предлагаемого табличного суь матора по модулю три с коррекцией ошибок. Табличный сумматор по модулю три с коррекцией ошибок (фиг.1) содержит матрицу 1 элементов И, первый 2, второй 3, третий 4 переключатели, блок 5 контроля, содержащий первый триггер 6, первый 7, второй 8, третий 9, четвертый 10, пятый 11 элементы И, элемент ИЛИ-НЕ 12, блок 13 коррекции ошибок, содержащий первый 14, второй 15, третий 16, четвертый 17, пятый 18, шестой 19 элементы И, первый 20, второй 21, третий 22 элементы ИЛИ, при этом блок контроля дополнительно содержит элемент НЕ 23, первый 24, второй 25 элементы ИЛИ, шестой элемент И 26, третий 27, четвертый 28, пятый 29 элементы ИЛИ, седьмой 30, восьмой 31, девятый 32 элементы И, второй 33,. третий 34, четвертый 35, пятый 36 триггеры. Устройство работает следующим образом. В работе устройства целесообразно выделитьь два такта и рассмотреть их раздельно: такт контроля ( в момент поступления сигнала на первый тактовый вход 6.1 сумматора) и такт выдачи результата (при правильной работе матрицы 1) или коррекции ( при ошибке в работе матрицы 1) и выдачи правильного результата ( в момент поступления сигнала на второй тактовый вход 6.2 сумматора). В такте контроля исходные операнды в однопоэиционном коде подаются на входы 2.0, 2.1,2.2,3.0, 3.1, 3.2 сумматора и далее через первый 2 и второй 3 переключатели напрямую поступают на соответствующие входы элементов И матрицы 1 под воздействием сигнала, поступающего на пер вый тактовый вход 6.1 сумматора. На выходах 1.0, 1.1, 1.2 матрицы 1 вырабатывается код результата сум мирования, который поступает на соответствующие входы элемента ИЛИ-НЕ 12 и первого 7, второго 8 и третьег 9 элементов И блока 5 контроля и на соответствующие входы элементов и 14-19 блока 13 коррекции ошибок. При правильном результате на выходах 1.0, 1,1/ 1.,2 матрицы 1, на выходе элемента иЛИ-НЕ 12 и выходах элементов И 7, 8 и 9 вырабатываются сигналы низкого уровня, которые поступают на соответствующие входы элементов ИЛИ 24, 27, 28 и 29, на выходах которых устанавливаются так же сигналы низкого уровня. Сигнал низкого уровня с выхода элемента ИЛ 24 инвертируется с помощью элемента НЕ 23, с выхода которого сигнал высокого уровня через элемент И 10 устанавливает в состояние 1 пер вый триггер 6 блока контроля,а чере элемент ИЛИ 25-и элемент-И 26 в состояние второй триггер 33 (синхронно с управляющим сигналом на первом тактовом входе б.1 сумма-тора). На единичном выходе первого триггера б устанавливается управляющий потенциал 5.1 Правильно, а на единичном выходе второго триггера 33 - управляющий потенциал 5.3 При неправильном результате суммирования на выходах 1.0, 1.1, 1.2 матрицы 1 (комбинации выходных сигналов 000-невозбуждение выходных шин матрицы J; 110,101,011 - ложное возбуждение одной из выходных шин матрицы 1) на выходах одного из эле ментов ИЛИ-НЕ 12 ( для комбинации 000), И 7 (для комбинации 110), И В (для комбинации 101), И 9 ( для ком бинации 011) вырабатывается сигнал высокого уровня. Для всех комбинаций сигнал высокого уровня через элемент ИЛИ 24 и элемент И 11 устанавливает nepBbffi триггер б в состоя ние О. На нулевом выходе первого триггера б устанавливается уп.равляющий потенциал 5.2 Неправиль При комбинации 000 выходных сигналов матрицы 1 сигнал высокого уровня с выхода элемента ИЛИ-НЕ 12 через элемент ИЛИ 25 и элемент И 26 устанавливает в состояние второй триггер 33 (синхронно с сигналом 6.1), на единичном выходе которого устанавливается управляющий потенциал 5.3, . При комбинации 110 выходных сигна лов матрицы 1 сигнал высокого уровня с выхода элемента И 7 через элементы ИЛИ 27 и 29 и элементы И 30 и 32 устанавливает в состояние третий.34 и пятый 36 триггеры (синхронно с сигналом 6.1) и на выходах последних устанавливаются управляющие потенциалы 5 .4 и 5 . 6. I При комбинации 101 выходных сигналов матрицы 1 сигнал высокого уровня с выхода элемента И 8 через элементы ИЛИ 28 и 29 и элементы И 31 и 32 устанавливает в состояние четвертый 35 и пятый 36 триггеры (синхронно с сигналом 6.1) и на выходах последних устанавливаются управляющие потенциалы 5.5 и 5.6. При комбинации 011 выходных сигналов матрицы 1 сигнал высокого уровня с выхода элемента И 9 через элементы ИЛИ 27 и 28 и элементы И 30 и 31 устанавливает в состояние третий 34 и четвертый 35 триггеры (синхронно с сигналом 6.1) и на выходах последних устанавливаются управляющие потенциалы 5.4 и 5.5. 9 такте коррекции и выдачи результатов возможны два случая. I Случай 1. Блок -контроля в такте контроля выработал сигнал 5,1 . Правильно. Этот сигнал поступает на третьи управляющие входы первого 2 и второго 3 и на второй управляющий вход третьего 4 переключателей. На вторые управляющие входы первого 2 и второго 3 переключателей и на первый управляющий вход третьего 4 переключателя подается тактовый сигнал 6.2. На входах первого 2 и второго 3 переключателей действуют первый и второй операнды, которые далее напрямую проходят на соответствующие входы элементов И матрицы 1. На выходах 1.0, 1.1, 1.2 матрицы 1 снова формируется правильный результат, который подается на первые входы элементов 14 - 19 И блока 13 коррекции ошибок. На вторые входы элементов И 15,17 и 19 блока 13 подается yпpaв JЯющий потенциал 5.3 с единичного выхода второго триггера 33 блбка контроля. Этот сигнал обеспечивает выдачу правильного результата через первый 20,второй 21, третий 22 элементы ИЛИ блока 13 на соответствующие выходы 13.0,13.1, 13.2 блока 13 коррекции и далее на соответствующие входы третьего переключателя 4. с одиночного выхода первого триггера 6 действует управляющий потенциал 5.1, который поступает на второй управляющий вход третьего переключателя 4 и обеспечивает выдачу правильного результата на выходы 4.0, 4.1, 4.2 сумматора синхронно с тактовым сигналом 6.2, подаваемым на первый управляющий вход третьег го переключателя 4. Случай 2. Блок 5 контроля; выработал в такте контроля сигнал , 5.2Неправильно. Рассмотрим процесс коррекции для указанных комбинаций неправильных ре зультатов на выходе матрицы 1. При ошибке невозбуждение выходных шин матрицы (комбинация 000) ..блок 5 Вырабатывает сигналы 5. 2 и 5.3 .Сигнал 5.2, поступая на четвертые входы пер вого 2 и второго 3 переключателей, осуществляет перекодировку операндов в переключателях 2,3 с цилиндрически сдвигом на одну позицию кода.В рёзуль тате этого происходит перекоммутация цепей матрицы 1 и возбуждение других элементов И матрицы,а следовательно, и других выходных ее шин. Сигнал 5.3действует на вторые вхсэды элеме тов И 15, 17 и 19 блока 13 и обеспечивает передачу скорректированного результата на выход. этого блока и на входы третьего переключателя 4. Сигнал Ь.2 действует также на третий управляющий вход третьего переключателя 4 и обеспечивает выдачу правильного результата суммирования на выходы 4.0, 4.1, 4.2 сумматора. При ошибках ложное возбуждение выходных шин матрицы (комбинации 110, 101, 011) блок 5 вырабатывает сигналы 5.2,5,4,5.6 (для ком бинации 110); 5.2,5.5,5.6, (для ком бинации 110) 5.2,5.5,5.6 (для комбинации 101); 5.2,5.4,5.5 (для комбинации 011) . Процесс коррекции ошибок, например, для комбинации 110 осуществляется следующим образом. Пусть истинно возбужденной является выходная шина 1.0 матрицы 1, а ложно-шина 1.1.По сигналу 5.2, пост пающему на четвертые входы первого 2 и второго 3 переключателей, в этих переключателях производится пе рекодировка входных операндов, благодаря чему возбуждается шина 1.2 матрицы 1. Шина 1.1 остается ложно возбужденной. По сигналу 5.6, поступающему на второй вход элемента И 18 блока 13 коррекции, сигнал с шины 1.2 матрицы 1 через элемент И 18 и элемент ИЛИ 22 .блока 13 проходит на вход третьего переключателя 4, который по сигналу 5.2 транспортирует сигнал с шины 13.2 блока 13 в выходную шику 4.0 сумматора, что и требуется. Если же истинно возбужденной шиной матрицы оказывается шина 1.1, а ложно - шина 1.0, то в переключателях 2 и 3 проходит перекодировка входных операндов таким образом, что возбуждается шина 1.0 матрицы 1 (т.е. происходит совпадение с ложно возбужденной шиной). По сигналу 5.4 блока контроля, поступат ющему на второй вход элемента И 14 блока 13 коррекции, сигнал с шины 1,0 матрицы 1 проходит через элементы И 14 и ИЛИ 20 на выход 13.0 блока 13 и на соответствующий,вход переключателя 4, который по сигналу 5,2 транспортирует сигнал с шины 13.0 в выходную шину 4,1 сумматора, что и требуется. Аналогично осуществляется коррекция ошибок для комбинации выходных сигналов матрицы 101 и 011. Таким образом, предложенный сумматор по модулю три с коррекцией ошибок обладает повышенной достоверностью функционирования благодаря способности корректировать ошибки как типа невозбуждение выходных шин матрицы , так и типа ложное возбуждение выходных шин матрицы, вызванное одиночными отказами и сбоями логических элементов матрицы. Необходимое при этом некоторое дополнительное оборудование позволяет значительно повысить достоверность функционирования без существенного снижения надежности сумматбра из-за отказов в этом дополнительном оборудовании, так как для реализации последнего могут быть применены простые высоконадежные логические элементы современной интегральной технологии.

г,1

22

Фи&, J

I м

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| и др | |||

| Надежность и контроль ЭВМ | |||

| М., Сов.радио, 1978, с.116, рис.3.13 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-11-15—Публикация

1983-06-20—Подача