со входом начальной установки третьего триггера, единичный выход которого соединен с первым входом третьего элемента И и через второй элемент НЕ со входом пуска первых i сигнатурных анализаторов группы, выход тактового генератора.соединен со вторым входом ;третьего элемента И блока управления и со вторым входом элемента И блока настраиваемой задержки, выход третьего элемента И блока уп завления соединен со счетным входом второго счетчика, со входом разрешения переписи в 1п+1)-й сигнатурный анализатор группы, с первым входом элемента ИЛИ блока настраиваемой задержки, выходы третьего переключателя блока управления соединены соответственно с единичным и нулевым,входами пятого триггера блока управления, единичный выход которого соединен со входом разрешения записи регистра блока настраиваемой задержки, информационные выходы которого соединены с информационными входами счетчика, выход элемента И блока настраиваемой задержки соединен со счетным входом счетчика, выход переполнения которого соединен со вторым входом элемент ИЛИ блока настраиваемой задержки, со входом первого элемента ИЛИ блока управления и со входом начальной установки третьего триггера блока управления, выход элемента ИЛИ блока настраиваемой задержки соединен с тактовым входом первых п сигнатурных анализаторов, выходы группы переключателей группы блока управлений соединены с информационными входами регистра блока настраиваемой задержки.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля логических блоков | 1983 |

|

SU1149266A1 |

| Устройство для контроля логических блоков | 1987 |

|

SU1432529A1 |

| Сигнатурный анализатор для поиска перемежающихся неисправностей | 1986 |

|

SU1495799A1 |

| Устройство для контроля логических блоков | 1979 |

|

SU875390A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1120338A1 |

| Устройство для контроля цифровых узлов | 1981 |

|

SU978154A1 |

| Устройство для контроля цифровых блоков | 1983 |

|

SU1148009A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1124312A1 |

| Устройство для контроля и диагностики цифровых блоков | 1986 |

|

SU1388871A1 |

| Многовходовой сигнатурный анализатор | 1986 |

|

SU1363213A1 |

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЛОГИЧЕСКИХ БЛОКОВ, содержащее- задатчик тестов, блок управления, генератор импульсов, группу из f, сигнатурных анализаторов (где п- количество информационных входов устройства) и блок индикации, причем блок управления содержит первый, второй и третий триггеры, первый элемент ИЛИ, первый счетчик, первый элемент НЕ, первый элемент И и два переключателя, причем выходы первого и второго переключателей соединены соответственно со входами первого и второго триггеров блока управления, единичный выход первого триггера блока управления соединен с первым входом первого элемента ИЛИ, выход которого соединен с первыгл входом первого элемента И, единичный выход второго триггера блока управления соединен со.входом обнуления первого счетчика блока управления, со входаминачальной установки сигнатурных анализаторов группы, выход переполнения первого счетчика соединен со счётным входом третьего триггера, нулевой выход которого соединен со вторым входом первого элемента И и через первый элемент НЕ блока управления - со входом разрешения за-, писи каждого сигнатурного анализатора группы, информационный выход i 1+1)го сигнатурного анализатора соединен со входом блока индикации, информационные выходы задатчика тестов являются тестовыми выходами устройства, каждый вход группы информационных входов устройства соединен с . первым информационным входом соответствующего сигнатурного анализатора группы, информационный выход каждого i-ro сигнатурного анализатора группы (где i- от 1 до п) соединен со вторым информационным входом (-1 4-1)-го сигнатурного анализатора, второй информационный вход первого I сигнатурного анализатора соединен с шиной нулевого потенциала, о т л ичающееся тем, что, с целью с «g повышения быстродействия, в устройство введен блок настраиваемой задержки, содержащий регистр, счетчик, элемент И и элемент ИЛИ, а в блок - управления введены четвертый и пятый .триггеры, второй счетчик, группа переключателей, второй и третий эле- ё менты И, второй элемент ИЛИ и второй э.пемент НЕ, причем нулевой выход третьего триггера блока управления соединен с первым входом второго элемента И, выход которого соедиСП нен со счетным входом первого счетчика блока управления и с тактовым входом задатчика тестов, выход перво го элемента И соединен со счетным входом четвертого триггера, единичный выход которого соединеНу со вторым входом второго элемента И блока управления, с первым входом элемента И. блока настраиваемой задержки и с входом разрешения счета счетчика бло ка настраиваемой задержки, единичный выход второго триггера блока управления соединен с первым входом второго элемента ИЛИ, со входом начальной установки второго счетчика, выход переполнения которого соединен со вторым входом второго элемента ИЛИ, вы;хоя второго элемента ИЛИ соединен

1

Изобретение относится к вычислительной технике и может быть использовано для контроля логических блоков электронного цифрового оборудования.

Известно устройство для контроля логических блоков, работающее по принципу сравнения эталонных выходных реакций с выходными реакциями, Полученными на выходах контролируемого блока. Оно содержит память, блок записи, генератор импульсов, триггер, первый и второй элементы И, блок управления, счетчик импульсов, дешифратор, регистр теста, коммутатор и схему сравнения логических состояний l.

Недостатками данного устройства являются:.

сравнительно малое быстродействие за счет применения памяти в качестве генератора тестов и за счет последовательного изменения входных воздействий с целью устранения гонок электрических сигналов в схеме;

большой объем памяти, используемый для хранения тестовой, программы и эталонных выходных реакций.

Наиболее близким к предлагаемому является устройство для контроля логических блоков, содержащее задатчик тестов, контролируемый логический блок, блок управления, генератор импульсов, первые п сигнатурных анализаторов, второй сигнатурный анализатор и блок индикации. Выходы блока управления соединены с первыми входами сигнатурных анализаторов и с входом задатчика тестов, выходы которого соединены с входами контролируемого блока, выходы которого соединены с вторыми входами первых п- сигнатурных анализаторов, выход каждого предыдущего из первых п сигнатурных анализаторов соединен с третьим входом каждого последующего из первых и сигнатурных анализаторов, вход последнего п-го сигнатурного анализато0 ра соединен с входом второго сигнатурного анализатора, выход которого соединен с блоком индикации.

Блок управления содержит три триггера, первый элемент И, первый инверс тор, элемента ИЛИ, первый счетчик, два переключателя, коммутирующие установочные входы двух триггеров, причем выход первого триггера через элемент ИЛИ соединен с первым входом первого элемента И, выход второго триггера соединен с входом сброса первого счетчика 23.

Недостатком известного устройства является то, что оно может только контролировать логические блоки, содержащие схемы, предельная частота

работы которых меньше или равна фиксированной частоте устройства. Это приводит к возникновению неопределенных состояний этих схем, что в ко30 нечном результате приводит к неоднозначности выходных сигнатур.

Другим недостатком этого устрой.ства является сравнительно невысокое быстродействие при контроле логиче35 ских блоков, у которых время распространения сигналов от входа к выходу меньше фиксированного времени в устройстве контроля. проведения контроля одного блока устройством определяется временем задержки распространения сигнала от входа к выходу . При проведении контроля блоков/ у которых время распространения сигна|ла со входа на его выход небольшое, (производительность устройства для контроля падает, так как фиксированное время, необходимое для считывания сигнатуры, не меняется при контроле блоков, у которых время контроля меньше. Целью изобретения является повышение быстродействия устройства конт роля логических блоков. Поставленная цель достигается тем что в устройство для контроля логических блоков введен блок настраиваемой задержки, содержаиций регистр, счетчик, элемент И и элемент ИЛИ, а в блок управления введены четвертый и пятый триггеры, второй счетчик, группа переюгючателей, второй и третий элементы И, второй элемент ИЛИ и второй элемент НЕ, причем нулевой выход третьего триггера блока управления соединен с первым входом второ го элемента И, выход которого соединен со счетным входом первого счетчика блока управления и с тактовым входом задатчика тестов, выход перво го элемента И соединен со счетным входом четвертого триггера, единичный выход которого соединен с вторым входом второго элемента И блока управления, с первым входом элемента И блока настраиваемой задержки и с входом разрешения счета счетчика бло ка настраиваемой задержки, единичный выход второго триггера блока управления соединен с первым входом второго элемента ИЛИ, с входом начальной установки второго счетчика, выход переполнения которого соединен с вторым входом второго элемента ИЛИ выход второго элемента ИЛИ соединен с входом начальной установки третьего триггера, единичный выход которого соединен с первым входом третьего элемента И и через второй элемент НЕ с входом пуска первых п сигнатурных анализаторов группы, выход такто вого генератора соединен с вторым входом третьего элемента И блока управления и с вторым входом элемента И блока настраиваемой задержки, выхсд третьего элемента И блока управления соединен со счетным входом вто рого счетчика, с входом разрешения . переписи в (п+1)-и сигнатурный анализатор группы, с первым входом элемента ИЛИ блока настраиваемой задерж ки, выходы третьего переключателя блока управления соединены соответст венно с единичным и нулевым входами пятого триггера блока управления/ единичный выход которого соединен с входом .разрешения записи регистра блока настраиваемой задержки, информационные выходы которого соединены с информационными входами счетчика, выход элемента И блока настраиваемой задержки соединен со счетным входом счетчика, выход переполнения которого соединен с вторьлм входом элемента ИЛИ блока настраиваемой задержки, с входом первого элемента ИЛИ блока управления и с входом начальной установки третьего триггера блока управления, выход элемента ИЛИ блока настраиваемой задержки соединен с тактовым входом первых п сигнатурных анализаторов, выходы группы переключателей группы блока управления соединены с информационными входами регистра блока настраиваемой задержки. На фиг. 1 приведена блок-схема устройства для контроля логических блоков; на фиг. 2 - функциональная схема блока управления; на фиг. 3 функциональная схема блока настраиваемой задержки. Устройство для контроля логических блоков содержит блок 1 управления, шину 2 управляющих сигналов 2.12(+7), генератор 3 импульсов с выходом 4, блок 5 настраиваемой задержки с выходами 6.1, 6.2, задатчик 7 .тестов, вырабатывающий на выходах 8 тестовые последовательности и представляющий собой генератор последовательности псевдослучайных кодов, контролируемый логический блок 9 с выходами 10.1 - 10.h, первые 11 и вторые 12 элементы И, элементы 13 ИЛИ, сумматоры по модулю два 14 и регистры 15 сдвига, образующие группу сигнатурных анализаторов 16.1-16.и, имеющие выходы 17.1-17.п, сигнатурный анализатор 18, содержащий сумматор 14, регистр 15 и блок 19 индикации. Выходы блока 1 управления соединены с входами, элементов 11 и 12 и ус тановочным входом группы сигнатурных анализаторов 16.1-16. ri, с входами блока 5, с входами сигнатурного анализатора 18 и с входом задатчика 7 тестов. Выходы 8 задатчика тестов 7 соединены с вxoдa ш контролируемого блока 9, выходы 10 которого подключены к входам сумматора 14 группы сигнатурных анализаторов 16.1-16.и. Выход 4 генератора 3 импульсов соединен с первым входом блока 1 управления и с входом блока 5. Выход 16.1 блока 5 соединен с вторым входом блока 1 управления. Выход 6.2 блока 5 соединен со стробирующими входами группы сигнатурных анализаторов 16.116.1. в каждом сигнатурном анализаторе 16 выходы сумматоров 14 соединены с входами элемента И 11. Выходы элементов И 11 и 12 соединены с вхо-.

доми элемента ИЛИ 13, выход которого соединен с входом регистра 15. Выходы регистра 15 соединены с входами сумматора 14. Выход последнего разряда регистра 15 предыдущей группы 16 соединен, кроме того, с входом элемента И 12 последующей группы 16, кроме сигнатурного анализатора 16,1, в котором вход элемента 12 заземлен. Б анализаторе 16.п выход последнего разряда регистра 15 соединен с инфор- мационным входом сигнатурного анализатора 18, выход которого соединен с блоком 19 индикации.

Блок 1 управления (фиг. 2) содержит переключатели 20-22, коммутирую- 15 щие установочные входы триггеров 2325, D -триггеры 26 и 27, элементы И 28, ИЛИ 29, И 30, И 31, элементы НЕ 32 и 33, двоичные счетчики импульсов 34, 35, элемент ИЛИ 36 и группу 20 переключателей 37.

Выход триггера 24 соединен с входом обнуления счетчиков 34, 35 и с установочным входом триггера 27 через элемент ИЛИ 29. Выход триггера 25 23 соединен со счетным входом триг- гера 26 через элемент ИЛИ 36 и элемент И 30, выход которого является выходом 2.4 блока управления. Второйвход элемента ИЛИ 36 и установочный 30 вход триггера 26 соединены с входом 6.1 блока управления. Выход триггера 26 является выходом 2.5 блока управления и, кроме того, соединен с вторым входом элемента И 28. Выход 35 элемента И 28 соединен со счетным входом счетчика 34 и является выхо дом 2.1 блока 1. Единичный выход триггера 27 через элемент НЕ 32 поступает на выход 2.2 блока управле- 40 ния .и через элемент И 31 - на счетный вход счетчика 35 и на выход 2.6 блока управления.

Нулевой выход триггера 27 соединен с первым входом элемента И 28, . вторым входом элемента И 30 и через элемент НЕ 33 - с выходом 2.3 блока управления.

Выход 4 соединен с вторым входом элемента И 31. Выход переполнения счет.ика 35 соединен с вторым входом элемента ИЛИ 29. Выход переполнения счетчика 34 соединен со счетным вхоом триггера 27.

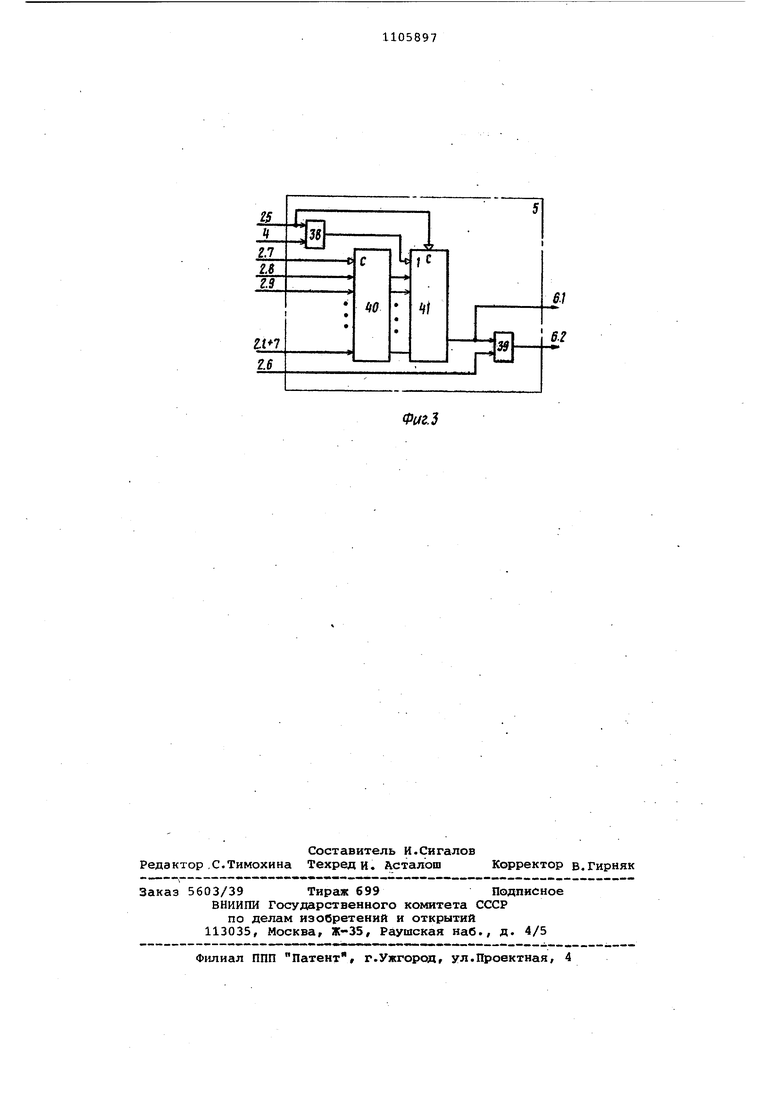

Влок 5 настраиваемой задержки (фиг. 3) содержит элемент И 38, эле- 55 ент ИЛИ 39, регистр 40, реверсивный счетчик 41 импульсов. Входы элемента И 38 соединены с входами 2.5 и 4, а ыход соединен с счетным входом счетика 41. Информационные входы регист-60 а 40 соединены с выходами 2.7-2(+7) лока 1, а выходы соединены с инфорационными входами счетчика 41, выод которого соединен с первым вхоом элемента ИЛИ 3 9 и выходом 6.1 5

блока управления. Второй вход элемента ИЛИ 39 соединен с выходом 2.6 блока 1, а выход соединен с сигналом 6.2. Вход записи счетчика 41 соединен с выходом 2.5 блока 1,

Устройство работает следующим образом.

Влок 1 управления сигналом 2.4 устанавливает группу сигнатурных анализаторов 16.1, ..., 16 .ti и сигнатурный анализатор 18 в исходное состояние по сигналу 2.7 в блок 5 настраиваемой задержки записывается код временной задержки (сигналы 2.8, ..., 2 (2 +7} распространения двоичных сигналов через контролируемый блок 9. Задержка задается при помощи группы переключателей 37 в блоке 1 управления. По управляющему сигналу 2.1 задатчик 7 вьщает на выходы 8 первый тест, который поступает на входы контролируемого блока 9.

С выходов 10.1, ..., 10.П информация 1 реакция на поступающую информацию первого теста) поступает через сумматоры 14, выполняющие операцию сложения по модулю два, через элементы И 11 и элементы ИЛИ 13 на входы регистров 15 сдвига. -Единичное значение сигнала 2. 2 и нулевое значе1ние сигнала 2.3 открывают элементы 11 и закрывают элементы 12 соответственно. Сигналом 2.5 от устройства управления срабатывает блок 5 настраиваемой задержки, который выдает сигнал 6.2 записи информации с выходов блока 9 в первые разделы п сдвигающих регистров 15, каждый из которых имеет tn разрядов. В это время в анализатор 18 импульсы сдвига 2.6не поступают.

Затем выдается второй тест.

Влок 1 управления по сигналу 2.5 включает снова блок 5 настраиваемой. задержки, который повторяет действие записи в регистры 15 (с учетом обратных связей через сумматоры 14 информации, поступающей с выходов 10.1,,.. ..., 10. г блока 9. В результате прохождения всей программы (последовательность тестов) в регистрах 15 сдвига поканально в виде сигнатуры записана выходная информация контролируемого 9 блока.

После прохождения всех тестов блок 1 управления закрывает элемент И 11 и открывает элемент И 12 и выдает последовательность hm импульсов (сигнал 2.6 и 6.2) сдвига, по которой образованные в регистрах 15 сигнатуры передаются через элементы 12 и 13 с регистров предыдущих сигнатурных анализаторов в регистры последующих, а с последнего п-го сигнатурного анализатора в анализатор 18, где образуется результативная сигнатура для контролируемого 9 блока. Это сигнатура представляет собой сжатую информацию от выходной реакции контролируемого блока на входную тестовую последовательность. Сигнатура индици руется блоком 19 индикации. Оператор проводит сравнение полученной сигнатуры с эталонной, рассчитанной для исправного логического блока, и в соответствии с результатом сравнения судит о состоянии исправности контролируемого блока. Блок 5 настраиваемой задержки работает следующим образом. В начале процесса контроля по нажатию кнопочного переключателя Заг 22 ,фиг. 2) на выходе триггера 25 (сигнал 2.7 блока управления I появля ется тактирующий импульс, который поступая в регистр 40, проводит запись кода временной задержки для кон ролируемого блока, задаваемого при помощи тумблерных переключателей 37 Временная задержка сохраняется в этом регистре до конца процесса конт роля. При переходе сигнала 2.5 из уровня нуля к уровню единицы происхо дит перезапись содержимого регистра 40 в реверсивный счетчик 41, при этом открывается элемент И 38, что разрешает подать на счетный вход сч чика 41 последовательность импульсов из генератора 3. При этом прово дится счет до появления сигнала 6.1 переполнения счетчика (что указывает истечение задаваемой задержки), по которому проводится запись в регистры 15 сдвига. При образовании результативной сигнатуры в группе из п сигнатурных анализаторов после довательность импульсов сдвига 6.2 поступает в регистры 15 от генерато ра 3 в виде сигнала 2.6 через элемент ИЛИ 39. Блок настраиваемой задержки позволяет изменять частоту стробирования в пределах от /2 до {р, где fr - частота генератора импульсов} е - разрядность счетчика 41. Код задержки при контроле опреде ленного логического блока задается группой переключателей 37 блока управления. Этот код определяет часто ту стробирования и вычисляется как ближайшее большое целое число, полу ченное в результате деления временной задержки распространения .сигналов через контролируемый блок на пе риод If. генератора 3. Период Т опр деляется суммарной задержкой распро странения сигналов через элементы 1 и 13, сумматор 14 и регистр сдвига Эта частота фиксирована и зависит только от используемой элементной базы в предлагаемом устройстве. Блок 1 управления работает следу щим образом. После нажатия кнопки 21 Иск. импульс с выхода триггера 24 сбрасывает триггер 27, счетчики 34, 35 и сигнатурные анализаторы 16.1 -16.п и 18. Нулевое состояние триггера 27 разрешает прохождение сигналов через элемент 30, открывает через эле-г мент НЕ 32 элементы 11 И сигналом 2.2 и запирает через элемент НЕ 33 сигналом 2.3 элементы 12 И анализаторов 16.1, ..., 16.п. После нажатия кнопки Пуск 20 ш тульс с выхода триггера 23, пройдя через элементы ИЛИ 36, И элемент 30, устанавливает триггер 26 в 1, выход триггера 26 (сигнал 2.5), как указано, запускает блок 5 настраиваемой задержки,.выход 6.1 которого через обратную связь поступает на вход элемента ИЛИ 36 и на установочный вход триггера 26, образуя встроенный генератор импульсов с переменной частотой . Последовательность импульсов 2.5 проходит через открытый элемент И 28 (так как триггер 27 находится в нулевом состоянии), поступает на счетный вход счетчика 34 и выходит с блока 1 управления как сигнал 2.1. Счетчик 34 считает до N импульсов, соответствующих числу тестов. После переполнения с етчика 34 триггер 27 устанавливается в 1, что запирает элемент И 30, открывается через элемент НЕ 33 элемент И 12 и закрывает элемент И 11. При этом заканчивается этап-подачи тестов и выборки.поканальных сигнатур. Единичное состояние триггера 27 открывает элемент И 31. и пропускает последовательность импульсов от генератора 3 на счетный вход счетчика 35. Последний проводит счет необходимых пп импульсов для образования результативной сигнатуры в анализаторе 18. Импульсы с выхода 2.6 блока 1, пройдя через блок 5 настраиваемой задерж ки, выходят как сигнал 6.2 сдвига регистров 15- анализаторов 16.1, ..., 16.и и записи в анализатор 18. Сигнал переполнения счетчика 35 через элемент ИЛИ 29 проводит сброс триггера 27, что блокирует передачу импульсов через элемент И 31. Это свидетельствует об окончании процесса формирования результативной сигнатуры в анализаторе 18. Последняя . отображается блоком 19 индикации. В отличие от прототипа, предлагаемое устройство позволяет контролиро.вать логические блоки с различными задержками распространения сигналов. Если в прототипе для такого контроля требуется проводить замену элементов задержки, находящихся в генераторе импульсов стробирования задатчика (Тестов и записи в группу из w CHrHa турных анализаторов, что неудобно с

точки зрения конструкции устройства и требует больших затрат времени, то в предлагаемом устройстве за счет введения блока настриваемой задержки и модификации блока управления необходимо только записать код згщержки распространения сигналов для контролируемого объекта. Настраивание частоты стробирования и стробирование

входной информации в присутствии тестовых данньтх на входах схемы позво- ляет устранить неопределенные состояния в схеме контролируемого блока, вызывающие неоднозначность сигнатур, свойственные прототипу при контроле в случае, когда предельная частота работы контролируемого блока меньше,чем фиксированная в устройстве контроля.

гл

г.8

г.9

г(7

I

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для контроля логических блоков | 1980 |

|

SU868763A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для контроля логических блоков | 1979 |

|

SU875390A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-07-30—Публикация

1982-07-30—Подача