нератора стробимпульсов, второй вход соединен с входом второго, генератора стробимпульсов и выходом двухпозиционного ключа, входы управления которого соединены с выходами пересчетного блока, информационный вход соединен с ёыходом формирователя импульсов и выходной шиной, а второй выход подключен к входу пересчетного блока и второму входу логического элемента ИЛИ, выход которого Лодключен к входу управляемой линии задержки, входы управления которой подключены к выходам реверсивного счетчика, вйедены два триггера, два двухвходовых логических элемента И, дополнительный управляемый элемент задержки, два диода, конденсатор и два дополнительных генератора стробимпульсов, выходы которых подключены к третьим входам трехвходовых логических элементов И, вход каждого соединен с входом соответствующего основного генератора стробимпульсов и одним из входов одного триггера, вторые входы которых соединены с выходом первого из упомянутых генераторов стробимпульсов, причем входы триггеров первые - соответственно, а вторые - перекрестно соединены с входами двухвходовых логических элементов И, выход одного из которых через диод, а выход второго через последовательно включенные инвертор и второй диод соединены с конденсатором и входом управления дополнительного элемента задержки, включенного между выходом управляемой- линии задержки и входом формирователя импульсов, г.

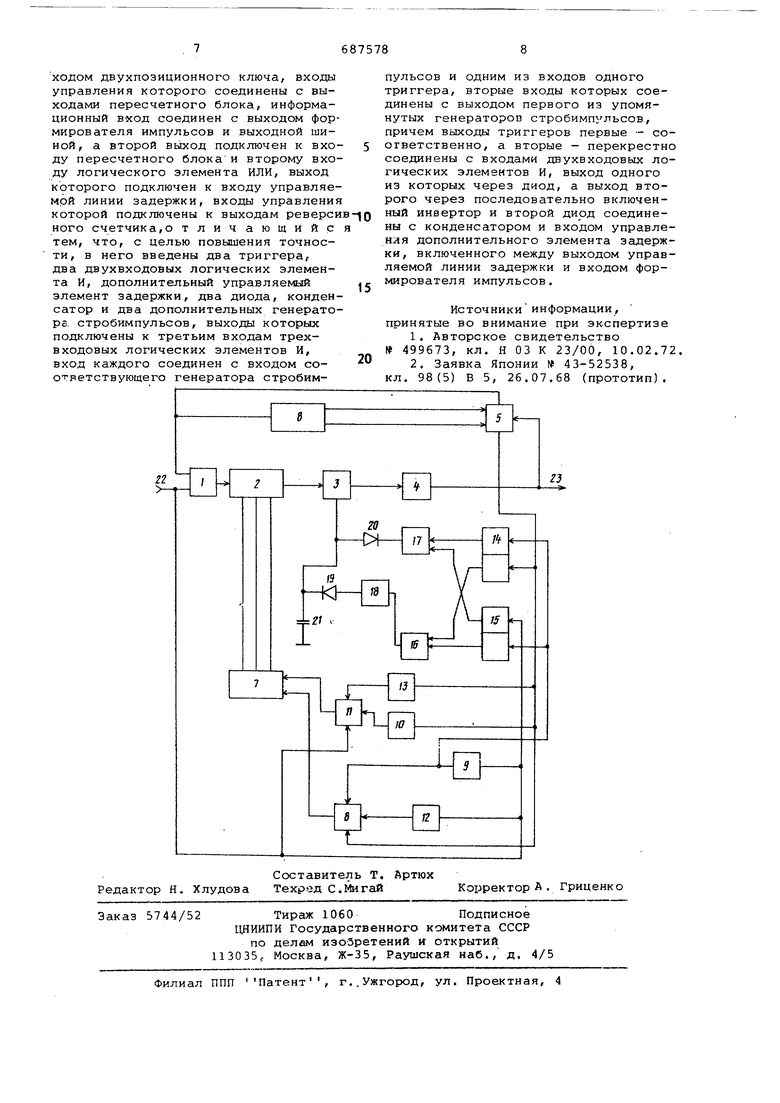

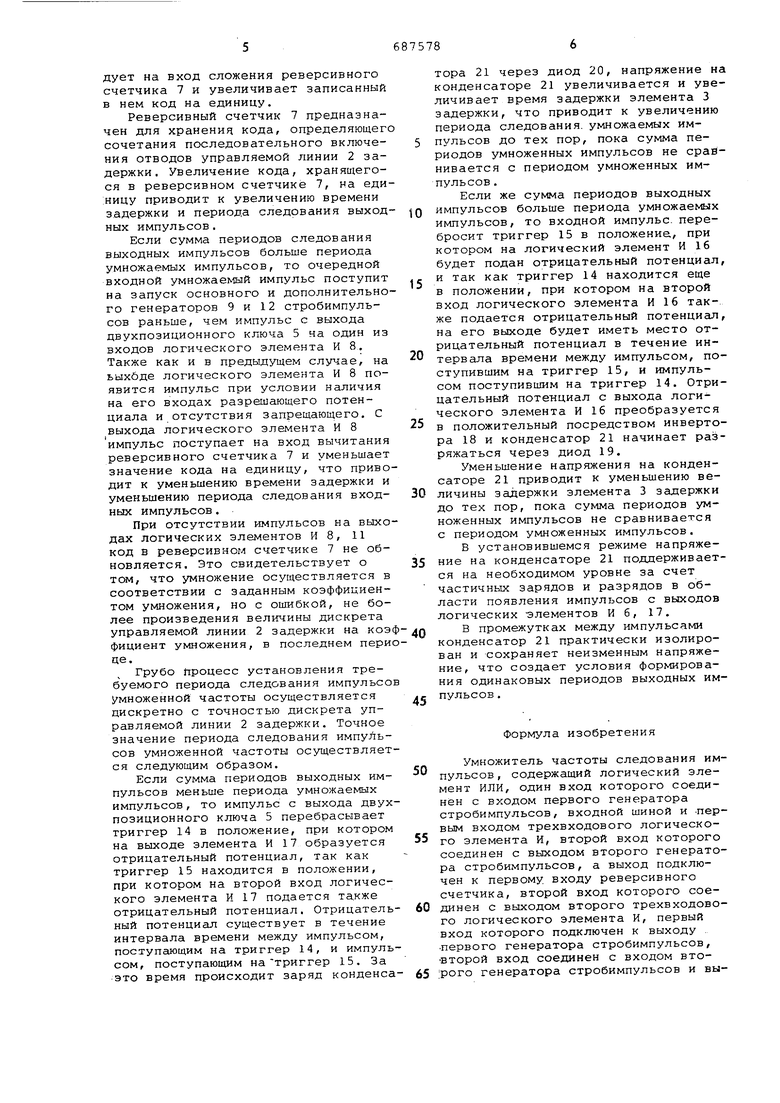

На чертеже приведена структурна электрическая схема предлагаемого умножителя.

Умножитель- содержит логический элемент ИЛИ 1, управляемую линию 2 задержки, дополнительный управляемый элемент 3.задержки, формирователь 4 импульсов, двухпозиционный ключ 5, пересчетный блок б, реверсивный счетчик 7, трехвходовый логический элемент И 8, генераторы 9 и 10 стробимпульсов, трехвходовый логический элемент И 11, дополнительные генераторы 12 и 13 стробимпульсов, триггеры 14 и 15, двухвходовые логические элементы И 16, 17, инвертор 18, диоды 19, 20-и конденсатор ,

Входной сигнал подан на в.ходную шину 22. Выходной сигнал снимается с выхода 23.

Принцип работы умножителя частоты следования импульсов заключается в следующем,

На вход подается первый подлежащий умножению импульс и через логический элемент ИЛИ 1, предназначенный дПя логического суммирования

входных импульсов умножаемой частоты и импульсов обратной связи, поступающих с формирователя 4 импульсов через двухпозиционный ключ 5, он поступает на вход управляемой линии 2 задержки. Одновременно этот импульс поступает на вход логического элемента И 11, первый вход тригера 15 и запускает основной и дополнительный генераторы 9 и 12 стробов, которые выдают: основной - разрешение, а дополнительный - запрет на логический элемент И 8, причем сигнал запрета значительно короче сигнала разрешения и равен произведению величины дискрета управляемой линии 2 задержки на коэффициент умножения.

Через промежуток времени, соответствующий периоду выходных импульсов, импульс с выхода формирователя 4 импульсов поступает на импульсный вход двухпозиционного ключа 5. При нулевом положении пересчетного блока 6, предназначенного для подсчета импульсов на выходе формирователя 4 импульсов и коммутации этих импульсов с помощью двухпозиционного ключа 5, двухпозиционный ключ находится в таком положении, при котором импульсы с выхода формирователя 4 импульсов поступают на вход пересчетного блока б и один из входов лгического элемента ИЛИ 1, а с его выхода - на вход управляемой линии 2 задержки и т.д. Цикл работы умножителя частоты следования импульсов будет повторяться до тех пор, пока на вход пересчетного блока 6 не поступит число импульсов, численно равное коэффициенту умножения. В этот момент пересчетный блок 6 устанавливает двухпозиционный ключ 5 в положение, при котором импульс с выхода пересчетного блока через ключ поступит на цепи сброса пересчетного блока б {для обнуления последнего) , первый вход триггера 14, на вход логического элемента И 8 и на запуск основного и дополнительного генераторов 10 и 13 стробимпульсов при этсм основной генератор 10 стробимпульсов выдает разрешение, а дополнительный генератор 13 запрет, причем сигнал запрета значительно короче сигнала разрешения.

Если сумма периодов выходных импульсов меньше периода умножаемых импульсов, то выходной умножаемый импульс поступает на логический элемент И 11 во время действия строба разрешения, вырабатываемого основным генератором 10 стробимпульсов и если в это время закончилось действие дополнительного строба, вырабатываемого дополнительным генерато рм 13.стробимпульсов, импульс еледует на вход сложения реверсивного счетчика 7 и увеличивает записанный в нем код на единицу.

Реверсивный счетчик 7 предназначен для хранения кода, определяющег сочетания последовательного включения отводов управляемой линии 2 задержки. Увеличение кода, хранящегося в реверсивном счетчике 7, на еди:ницу приводит к увеличению времени задержки и периода следования выходных импульсов.

Если сумма периодов следования выходных импульсов больше периода умножаемых импульсов, то очередной входной умножаемый импульс поступит на запуск основного и дополнительного генераторов 9 и 12 стробимпульсов раньше, чем импульс с выхода двухпозиционного ключа 5 на один из входов логического элемента И 8. Также как и в предьщущем случае, на ьыхбде логического элемента И 8 появится импульс при условии наличия на его входах разрешающего потенциала и отсутствия запрещающего. С выхода логического элемента И 8 импульс поступает на вход вычитания реверсивного счетчика 7 и уменьшает значение кода на единицу, что приводит к уменьшению времени задержки и уменьшению периода следования входных импульсов.

При отсутствии импульсов на выходах логических элементов И 8, 11 код в реверсивном счетчике 7 не обновляется. Это свидетельствует о том, что умножение осуществляется в соответствии с заданным коэффициентом умножения, но с ошибкой, не более произведения величины дискрета управляемой линии 2 задержки на коэфициент умножения, в последнем перице.

Грубо Процесс установления требуемого периода следования импульсо Умноженной частоты осуществляется дискретно с точностью дискрета управляемой линии 2 задержки. Точное значение периода следования импульсов умноженной частоты осуществляется следующим образом.

Если сумма периодов выходных импульсов меньше периода умножаемых импульсов, то импульс с выхода двухпозиционного ключа 5 перебрасывает триггер 14 в положение, при котором на выходе элемента И 17 образуется отрицательный потенциал, так как триггер 15 находится в положении, при котором на второй вход логического элемента И 17 подается также отрицательный потенциал. Отрицательный потенциал существует в течение интервала времени между импульсом, поступающим на триггер 14, и импульсом, поступающим на триггер 15. За это время происходит заряд конденсатора 21 через диод 20, напряжение на конденсаторе 21 увеличивается и увеличивает время задержки элемента 3 задержки, что приводит к увеличению периода следования, умножаемых импульсов до тех пор, пока сумма периодов умноженных импульсов не сравнивается с периодом умноженных импульсов .

Если же сумма периодов выходных импульсов больше периода умножаемых

0 импульсов, то входной импульс, перебросит триггер 15 в положение, при котором на логический элемент И 16 будет подан отрицательный потенциал, и так как триггер 14 находится еще

5 в положении, при котором на второй вход логического элемента И 16 также подается отрицательный потенциал, на его выходе будет иметь место отрицательный потенциал в течение ин0тервала времени между импульсом, поступившим на триггер 15, и импульсом поступившим на триггер 14. Отрицательный потенциал с выхода логического элемента И 16 преобразуется

5 в положительный посредством инвертора 18 и конденсатор 21 начинает разряжаться через диод 19.

Уменьшение напряжения на конденсаторе 21 приводит к уменьшению ве0личины задержки элемента 3 задержки до тех пор, пока сумма периодов умноженных импульсов не сравнивается с периодом умноженных импульсов.

В установившемся режиме напряжение на конденсаторе 21 поддерживает5ся на необходимом уровне за счет частичных зарядов и разрядов в области появления импульсов с выходов логических элементов И б, 17.

В промежутках между импульсами

0 конденсатор 21 практически изолирован и сохраняет неизменным напряжение, что создает условия фopг иpoвaния одинаковых периодов выходных импульсов .

5

Формула изобретения

Умножитель частоты следования импульсов , содержащий логический элемент ИЛИ, один вход которого соединен с входом первого генератора стробимпульсов, входной шиной и -первым входом трехвходового логического элемента И, второй вход которого соединен с выходом второго генератора стробимпульсов, а выход подключен к первому входу реверсивного счетчика, второй вход которого соединен с выходом второго трехвходового логического элемента И, первый вход которого подключен к выходу . первого генератора стробимпульсов, второй вход соединен с входом втоого генератора стробимпульсов и вы

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножитель частоты следования импульсов | 1974 |

|

SU499673A1 |

| Умножитель частоты следованияиМпульСОВ | 1979 |

|

SU845290A1 |

| Умножитель частоты следования импульсов | 1978 |

|

SU748796A1 |

| Умножитель частоты следования импульсов | 1980 |

|

SU923002A2 |

| Умножитель частоты следования импульсов | 1983 |

|

SU1140220A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ЗАДАННОГО ЧИСЛА ИМПУЛЬСОВ | 1993 |

|

RU2066921C1 |

| Цифровой измеритель длительности пачки импульсов | 1980 |

|

SU892412A1 |

| ФОРМИРОВАТЕЛЬ ПЕРИОДИЧЕСКОЙ ПОСЛЕДОВАТЕЛЬНОСТИ ИМПУЛЬСОВ | 2019 |

|

RU2719556C1 |

| Устройство для программного счета изделий | 1983 |

|

SU1113824A1 |

| Умножитель частоты следования импульсов | 1981 |

|

SU991614A2 |

Авторы

Даты

1979-09-25—Публикация

1977-07-11—Подача