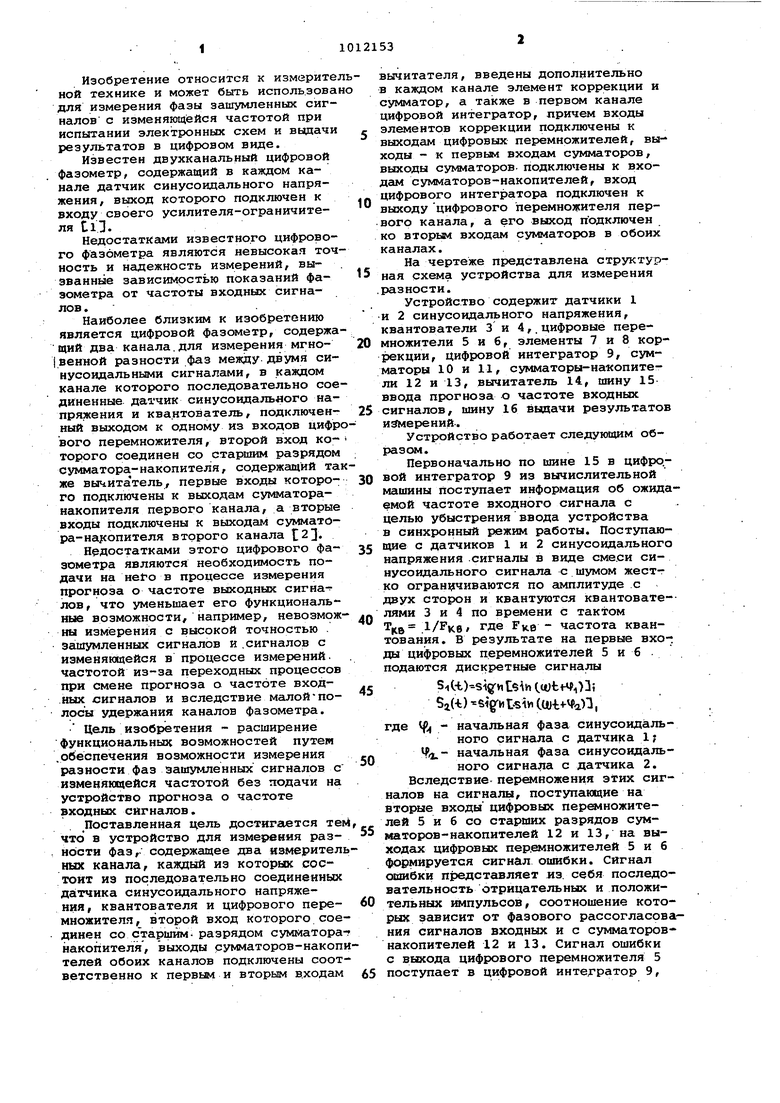

Изобретение относится к измерите ной технике и может быть использова для измерения фазы зашумленных сигналов с изменяющейся частотой при испытании электронных схем и выдачи результатов в цифровом виде. Известен двухканальный цифровой фазометр, содержащий в каждом канале датчик синусоидального напряжения, выход которого подключен к входу своего усилителя-ограничителя til. Недостатками известного цифрового фазометра являются невысокая точ ность и надежность измерений, вызванные зависимостью показаний фазометра от частоты входных сигналов., Наиболее близким к изобретению является цифровой фазометр, содержа щий два канала.для измерения мгно{венной разности фаз между двумя синусоидальными сигналами, в каждом канале которого последовательно сое диненные датчик синусоидальйого напряжения и квантователь, подключенный выходом к одному из входов цифр вого перемножителя, второй вход которого соединен со старшим разрядом сумматора -накопителя, содержащий та же вычитатель, первые входы которого подключены к выходам сумматоранакопителя первого канала, а вторые входы подключены к выходам сумматора- на сопите ля второго канала 2. Недостатками этого цифрового фазометра являются необходимость подачи на Heto в процессе измерения прогноза о частоте выходных сигналов, что уменьшает его функциональные возможности, например, невозмож ны измерения с высокой точностью . зашумленных сигналов и .сигналов с изменяющейся в процессе измерений, частотой из-за переходных процессов при смене прогноза о частоте входных сигналов и вследствие малой по лрсы удержания каналов фазометра. Цель изобретения - расширение функциональных возможностей путет .обеспечения возможности измерения разности фаз зашумленных сигналов с изменянхцейся частотой без подачи на устройство прогноза о частоте входных сигналов. Поставленная цель достигается теМ что в устройство для измерения разиЬсти фаз,, содержащее два измерител ных канала, каждый из которых состоит из последовательно соединенных датчика синусоидального напряжения, квантователя и цифрового перемножителя, второй вход которого соединен со сЪаршим- разрядом сумматоранакопителя, выходы сумматоров-накопи телей обоих каналов подключены соответственно к первьлл и вторым в.ходам вычитателя, введены дополнительно в каждом канале элемент коррекции и сумматор, а также в первом канале цифровой интегратор, причем входы элементов коррекции подключены к выходам цифровых- перемножителей, выходы - к первым входам сумматоров, выходы сумматоров подключены к входам сумматоров-накопителей, вход цифрового интегратора подключен к выходу цифрового перемножителя первого канала, а его выход подключен ко вторым входам сумматоров в обоих каналах. На чертеже представлена структурная схема устройства для измерения .разности. Устройство содержит датчики 1 и 2 синусоидального напряжения, квантователи 3 и 4,.цифровые перемножители 5 и б, элементы 7 и 8 коррекции. Цифровой интегратор 9, сумматоры 10 и 11, сумматоры-накопители 12 и 13, вычитатель 14, шину 15 ввода прогноза о частоте входных сигналов, шину 16 выдачи результатов измерений. Устройство работает следующим образом. Первоначально по шине 15 в цифро.вой интегратор 9 из вычислительной машины поступает информация об ожидаемой частоте входного сигнала с целью убыстрения ввода устройства в синхронный режим работы. Поступаиощие с датчиков 1 и 2 синусоидального напряжения сигналы в виде сме.си синусоидального сигнала с шумом жестко ограничиваются по с1мплитуде с двух сторон и квантуются квантователями 3 и 4 по времени с тактом где FKB частота квантования. В результате на первые входы цифровых перемножителей 5 и б . подаются дискретные сигналы S-it-t)-sign teih (.oottV,)3i Sl(4;) sigrntsin ((.«t4-4 a), где - начальная фаза синусоидального сигнала с датчика 1; начальная фаза синусоидального сигнала с датчика 2. Вследствие, перемножения этих сигналов на сигналы, поступающие на вторые входы цифровых перемножителей 5 и б со старших разрядов сумматоров-накопителей 12 и 13, на выходах цифровых пер.емножителей 5 и б формируется сигнал ошибки, сигнал сшибки представляет из. себя последовательность отрицательных и положительных импульсов, соотношение которых зависит от фазового рассогласования сигналов входных и с сумматоровнакопителей 12 и 13. Сигнал ошибки с выхода цифрового перемножителя 5 поступает в цифровой интед ратор 9,

величина содержимого которого определяет величину изменения фазы сигналову фо 4ируемых сумматорами-накопителями 12 и 13за время Т, так как каждай такт работы устройства содержимое цифрового- интегратора 9 через сумматоры 10 и 11 поступает, в сумматоры-накопители 12 и 13. В сйнхроннсяк режиме работы содержимое цифрового интегратора 9 соответствует приращению фазы входных сигналов за время т.е. частоте входных сигналов, фазовое рассогласование сигналов, формируемых сумматорами-накопителями 12 и 13 относительно сигналов входных равно и разность кодов, формируемая вь1читателем 14, соответствует мгновенной разности фаз сигналов с датчиков 1 и 2

дм,.(:,|),1,.

Если частота обрабатываемых сигнало при этом неизменна 1 то усредненное значение сигнала ошибки с цифровых перемножителей 5 и 6 равно нулю и содержимое цифрового интегратора 9, пропорциональное частоте входных сигналов, не изменяется. Если в процессе обработки сигналов их частота изменяется/ то сигнал ошибки с цифрового персякножителя 5 йзменя ет содержююе 1щфрового интегратр:..: ра 9 таким образом, что осуществляется отработка рассогласования по частоте и фазе между входйьМСИГНАЛОМ с датчика 1 и сигналом, формируемым сумматором-накопителем 12, и результ ты, выдава и1ые по шине 16 соответствуют мгновенному фазовому рассогласованию сигналов с датчиков 1 и 2, т.е. осуществляется обработка сигналов без подачи на устройство прогноза о частоте входных сигналов,

0 автосопровождение сигналов по частоте без подачи прогноза осуществляется в диапазоне частот до % f2

Элементы 7 и 8 коррекции определяют динамические свойства устрой5ства и служат для обеспечения устойчивости работы: сумматоры 10 и 11 служат для сложения сигналов с цифрового интегратора 9 и элементов 7 и 8 коррекции перед подачей на сумматоры-накопители 12 и 13.

0

Необходимая точность измерения мгновенного фазового рассогласования зашумленных сигналов достигается выбором соответствующих коэффициентов связи элементов 7 и 8 коррекции

5 и цифрового интегратора 9 с cjwijMaTOрами-накопителями 12 и 13, причем чем более высокие требования предъ- . являются к точности измерений и чем хуже соотношение сигнал/шум сигна0лов с датчиков 1 и 2, тем Меньшей величины должны быть эти коэффициенты связи.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой фазометр | 1975 |

|

SU540224A1 |

| Устройство автоподстройки несущей частоты | 1984 |

|

SU1298946A1 |

| СПОСОБ ПРИЕМА ШУМОПОДОБНЫХ СИГНАЛОВ С МИНИМАЛЬНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 2006 |

|

RU2307474C1 |

| УСТРОЙСТВО КОМПЕНСАЦИИ СТРУКТУРНЫХ ПОМЕХ | 2010 |

|

RU2450445C2 |

| УСТРОЙСТВО СЛЕЖЕНИЯ ЗА ЧАСТОТОЙ ШУМОПОДОБНЫХ СИГНАЛОВ | 2007 |

|

RU2325041C1 |

| КОРРЕЛЯЦИОННЫЙ ПРИЕМНИК ШУМОПОДОБНЫХ СИГНАЛОВ С МИНИМАЛЬНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 2008 |

|

RU2374776C2 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ ПРИЕМНИКА ШУМОПОДОБНЫХ СИГНАЛОВ С МИНИМАЛЬНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 2007 |

|

RU2357359C2 |

| Адаптивный цифровой корректор | 1982 |

|

SU1083379A1 |

| КОРРЕЛЯЦИОННЫЙ ПРИЕМНИК ШУМОПОДОБНЫХ СИГНАЛОВ | 2010 |

|

RU2431919C1 |

| Фазометр доплеровского набега фазы радиоимпульсных сигналов | 1990 |

|

SU1748086A1 |

УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ РАЗНОСТИ ФАЗ, содержащее два измерительных канала, каждый из которых . состоит из последовательно соединенных датчика синусоидального напряжения, квантователя и цифрового перемножителя , второй вход которого соединен со старшим разрядом сумматора-накопителя, выходы сумматоров-накоВСЕСОЮЗйЗД МТИПШи , I 1 I эШ;.;ша1Р4А пителей обоих каналов подключены соответственно к первым и вторым входам вычитателя, отличающеес я тем, что, с целью расширения функциональных возможностей путем обеспечения возможности измерения разности фаз зашумленных сигналов с изменяющейся частотой, в него ввeдены дополнительно в каждом канале элемент коррекции и сумматор, а также в первом канале цифровой интегратор, причем входы элементов коррекции подключены к выходам цифровых перемножителей, выходы - к первьв входам сумматоров, выходы сумматоров подключены к входам сумматоров- о накопителей, вход цифрового интегра- в тора подключен к выходу цифрового (Л перемножителя первого канала, а его выход подключен к вторым входам сумматоров в обоих каналах.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Е. И. БОЧКО!! | 0 |

|

SU331330A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Цифровой фазометр | 1975 |

|

SU540224A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1983-04-15—Публикация

1981-05-04—Подача