Изобретение относится к радиосвязи и может использоваться в аппаратуре для приема фазоманипулированных сигналов, передаваемых по каналам с межсимвольной интерференцией и доппле- ровским сдвигом часто.ты.

Целью изобретения является повышение помехоустойчивости при цифровой обработке сигнала.

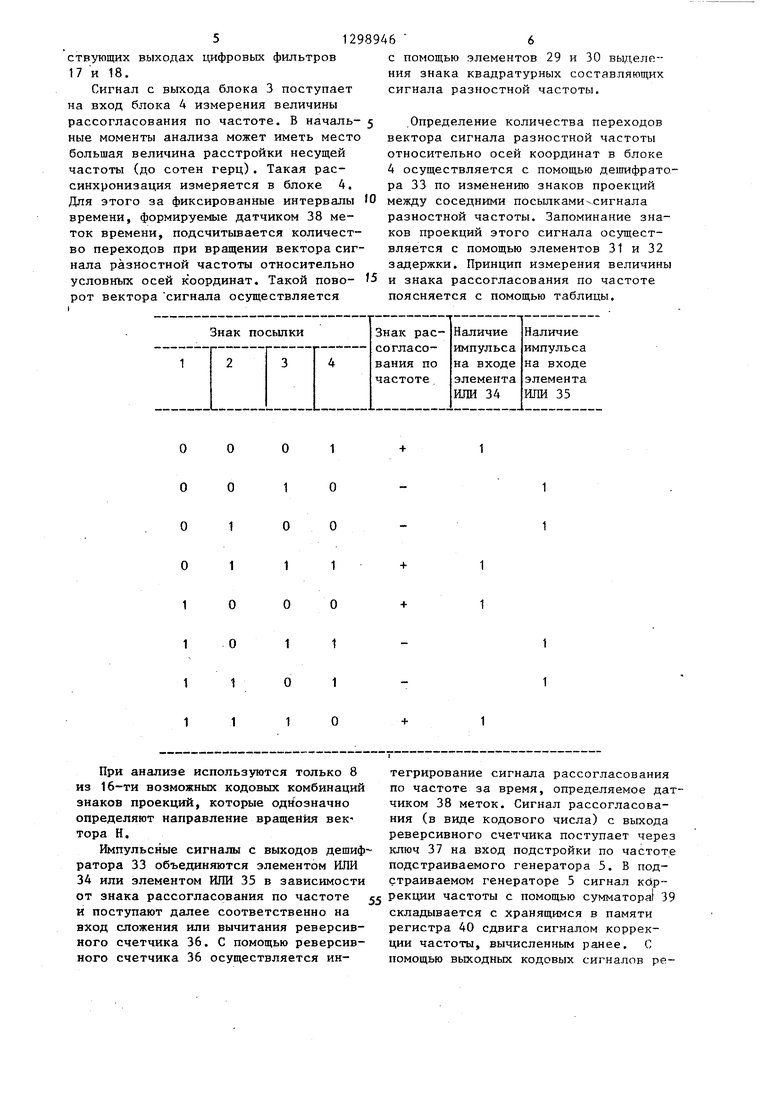

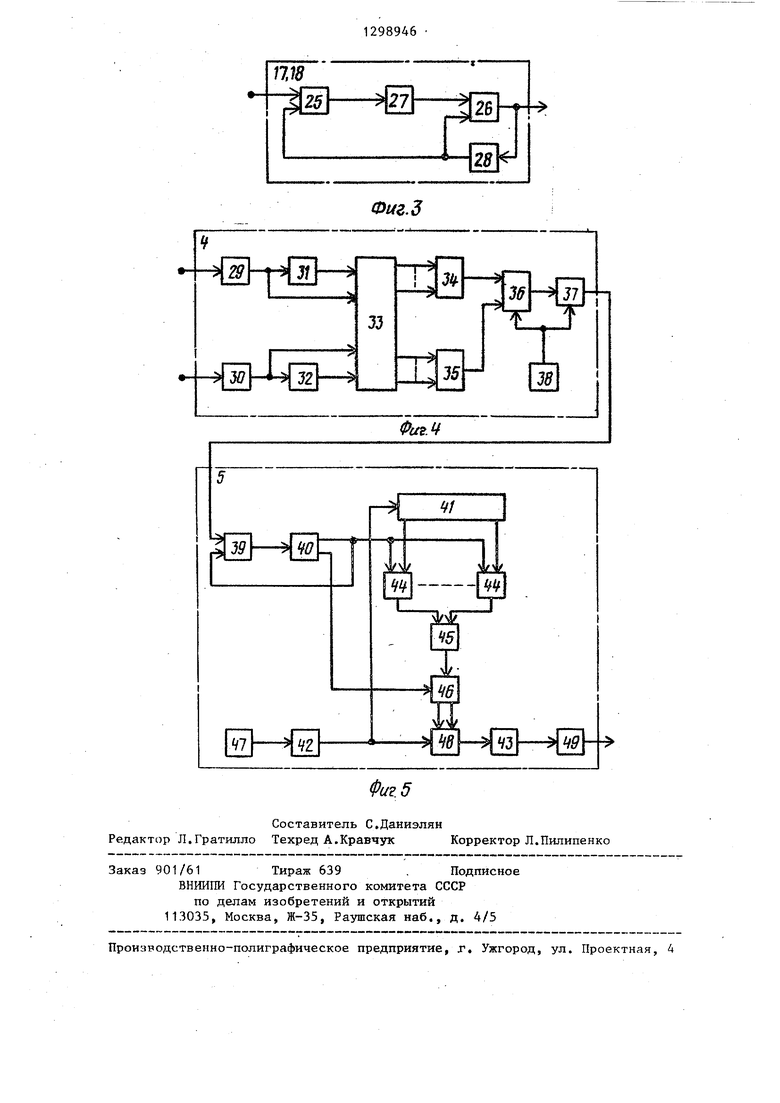

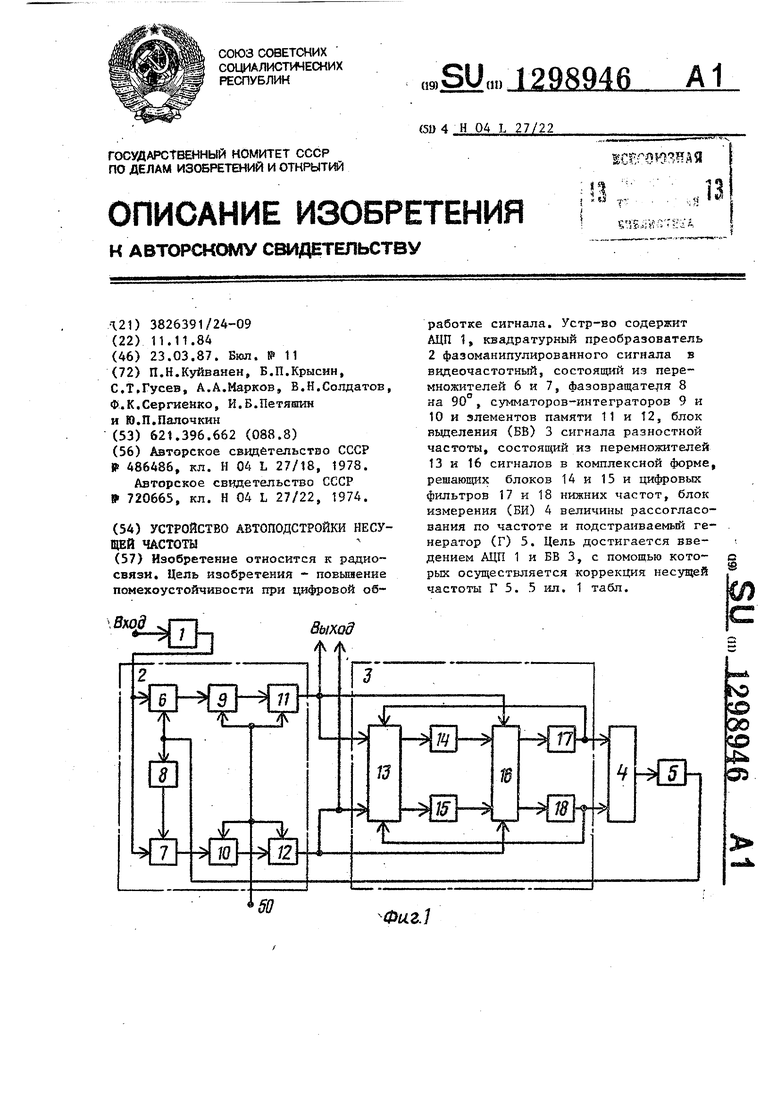

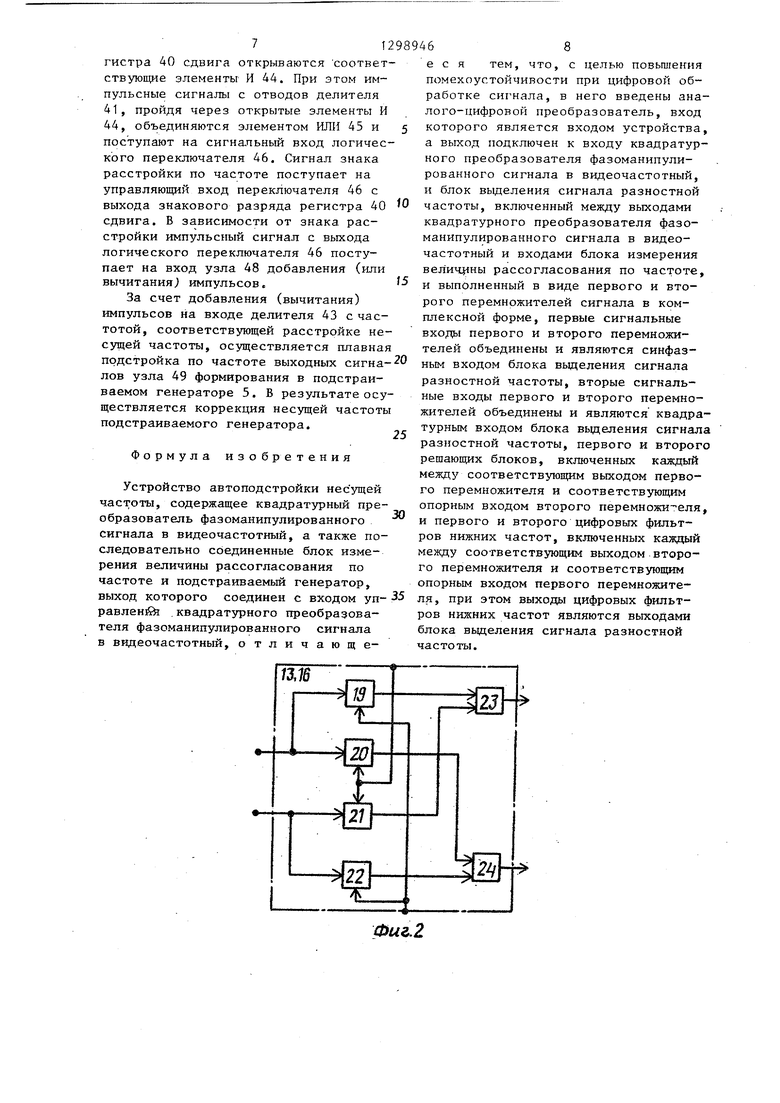

На фиг, 1 приведена структурная электрическая схема устройства автоподстройки несущей частоты;, на фиг.2 - то же,, перемножителя сигналов в комплексной форме; на фиг, 3 - то же, цифрового фильтра нижних частоту на фиг, 4 - то же, блока измерения величины рассогласования по частоте; на фиг. 5 - то же, подстраиваемого генератора.

Устройство автоподстройки несущей частоты содержит аналого-цифровой преобразователь 1, квадратурный преобразователь 2 фазоманипулированного сиг

нала в видеочастотный, блок 3 выделения25 На вторые входы перемножителей 6 и 7 сигнала разностной частоты, блок 4

измерения величины рассогласования

по частоте, подстраиваемый генератор

5, при этом квадратурный преобразовапоступают с частотой дискретизации цифровые пробы косинусоидальной и си нусоидальной составляющих несущей ча тоты,

тель 2

6 и 7.

содержит перемножители фазовращатель 8 на 90 , сумматоры- интеграторы 9 и 10 и элементы 11 и 12 памяти, блок 3 выделения сигнала разностной частоты содержит первый перемножитель 13 сигналов в комплексной форме, первый и второй решающие блоки 14 и 15, второй перемножитель 16 сигналов в комплексной форме и первый и второй цифровые фильтры 17 и 18 нижних частот,

Перемножитель сигналов в комплексной форме содержит умножители 19-22 и сумматоры 23 и 24.

Цифровой фильтр нижних частот содержит сумматоры 25 и 26, множитель 27 на постоянную величину 2 и элемент 28 задержки, блок 4 измерения величины рассогласования по частоте содержит элементы 29 и 30 вьщеления знака квадратурных составляющих сигнала разностной частоты, элементы 31 и 32 задержки, дешифратор 33, элементы ИЛИ 34 и 35, реверсивный счётчик 36, ключ 37 и датчик 38 меток времени, а подстраиваемый генератор 5 со- дерясит сзп яматор 39, параллельный регистр 40 сдвига, импульсный делитель 41 частоты, имеющий отводы от каждого из п делителей на два, импульсные

делители 42 и 43, п логических эле- ментой И 44, элемент КПИ 45, логический переключатель 46, стабильный опорный генератор 47, узел 48 добавления- вычитания импульсов, узел 49 формирования синусоидальной составляющей несущей частоты в цифровой форме.

Устройство автоподстройки несущей частоты работает следующим образом.

Принимаемый из канала связи фазо- манипулированный сигнал преобразуется аналого-цифровым преобразователем 1 в i-разрядные кодовые числа (пробы) с частотой дискретизации и далее поступает на сигнальные входы перемножителей 6 и 7 квадратурного преобразователя 2.

В квадратурном преобразователе 2 имеются два тракта оптимальной обработки фазоманипулированного сигнала, каждый из которых содержит перемножитель 6 или 7, сумматор-интегратор 9 или 10 и элемент памяти 11 или 12,

5 На вторые входы перемножителей 6 и 7

0

5

0

5

0

5

поступают с частотой дискретизации цифровые пробы косинусоидальной и синусоидальной составляющих несущей частоты,

В результате перемножения проб входного сигнала на составляющие не- сущей частоты, сдвинутые по фазе на 90 , и последующего интегрирования результатов перемножения с помощью сумматоров-интеграторов 9 и 10 в пределах длительности элементарной посылки формируются две взаимоортогональные проекции информационного йиг- нала. Эти проекции представляются в виде двух кодовых чисел (определенной разрядности) и записываются в эле- менты 11 и 12 памяти импульсами тактовой частоты, поступающими на вход квадратурного преобразователя 2. Формируемые при приеме каждой k-ой посылки выходные сигналы Zk квадратурного преобразователя 2 можно представить в виде комплексных чисел Re(Zk) + ilm(Zk), характеризующих как амплитуду, так и фазу принимаемого фазоманипулированного сигнала, где Re(Zk) и Ira(Zk) - синфазная и квадратурная составляющие вектора Zk.

С выхода квадратурного преобразователя 2 сигнал подается в блок 3 выделения сигнала разностной частоты. В блоке 3 информационный сигнал поступает на первые входы первого перемножителя 13 сигналов в комплексной

форме (фазового детектора) и на первые входы второго перемножнтеля (фазовращателя) 16. На вторые входы первого перемножителя 13 подается усредненный по времени сигнал разностной частоты с выходов цифровых фильтров 17 и 18. По выходным сигналам первого перемножителя 13 с помощью решаю- пщх блоков 14 и 15 вьщеляются двоичные решения (символы манипуляции). При этом в блоке 3 осуществляются следующие вычислительные операции:

Re(D)(Z)Re(H)-Ira(Z)Im(H) , Im(D)(Z)Re(H)+Re(Z)lm(H)

при приеме сигналов с двухкратной относительной фазовой манипуляцией (ОФМ) или

(Z)Re(H)-Im(Zm)lm(H) + +Im(Z)Re(H)+Re(Z)Im(H) .

при приеме сигналов с ОФМ,

где - знак сигнала у;

D - двоичные решения при приеме сигналов ОФМ;

Re(D) ,Ini(D)- двоичные решения по

кратам при приеме сигналов двукратной ОФМ;

Re(H),Im(H)- ортогональные проекции сигнала разностной часто ты. При обработке сигналов с ОФМ в

устройстве с целью упрощения алгоритВ цифровом фильтре нижних частот (фильтре первого порядка) с помощью сумматора 25 путем вычитания из вход20 ного сигнала задержанного элементом 28 задержки выходного сигнала вычисляется сигнал ошибки для подстройки усредненного сигнала разностной частоты. Сигнал ошибки с помощью мно жителя 27 умножается на постоянную величину (меньшую единице) и суммируется с выходным сигналом фильтра, вычисленным в предьщущей посылке и поступающим на другой вход суммато30 ра 26 с выхода элемента 28 задержки. Усреднение сигнала осуществляется с помощью следующих операций:

ReCH/ Re(Hf- 42- Re()-Re(

ма )Im(D). При этом дальнейшие 35 Im(H) 1т(Н) Ч2 tlta(Z)-Im(H) вычисления не зависят от того, обрабатываются ли сигналы с ОФМ или с двукратной ОФМ.

Двоичный сигнал с выхода решающих блоков 14 и 15 поступает на вторые 40 входы второго перемножителя (фазовращателя) 16, в котором над информационным сигналом осуществляется операция, обратная фазовой манипуляции, производимой на передаче, т.е. 45 снятие манипуляции:

Re(ZA)Re(Z) Re(D)+Im(Z)lm(D); Im(Z)Re(Z) Im(D)+Im(Z) Re(D), где Re(Z) и Im(Z) - составляющие

Im(H) .

lm(H)

(n-)

-K

50

где Re(H) , Re(H) . - синфазные

составляющие сигнала разностной частоты в п и (п-1) посылках;

то же, для квадратурных составляющих, 2 - постоянный множитель, определяющий граничную частоту цифрового фильтра нижних частот первого порядка.

информационного сигнала после снятия манипуляции.

При этом для сигнала с межсимвольной интерференцией снятие манипуляции произойдет только с одной наибольшей по уровню составляющей, которой эти двоичные решения соответствуют. Умножение сигнала других

составляющих на двоичные решения, не соответствующие этим составляющим, приведет лишь к дополнительной случайной манипуляции.

Сигналы, поступающие с синфазного и квадратурного выходов второго перемножителя 16, усредняются во времени соответствующими цифровыми фильтрами 17 и 18 нижних частот, на выходах которых вьщеляются составляющие сигнала разностной частоты; Значение этой частоты равно разности между несущей частотой принимаемого сигнала и частотой подстраиваемого генератора, т.е. соответствует величине частотной расстройки.

В цифровом фильтре нижних частот (фильтре первого порядка) с помощью сумматора 25 путем вычитания из входного сигнала задержанного элементом 28 задержки выходного сигнала вычисляется сигнал ошибки для подстройки усредненного сигнала разностной частоты. Сигнал ошибки с помощью множителя 27 умножается на постоянную величину (меньшую единице) и суммируется с выходным сигналом фильтра, вычисленным в предьщущей посылке и поступающим на другой вход сумматора 26 с выхода элемента 28 задержки. Усреднение сигнала осуществляется с помощью следующих операций:

ReCH/ Re(Hf- 42- Re()-Re(

5 Im(H) 1т(Н) Ч2 tlta(Z)-Im(H)

0 5

Im(H) .

lm(H)

(n-)

-K

0

5

где Re(H) , Re(H) . - синфазные

составляющие сигнала разностной частоты в п и (п-1) посылках;

то же, для квадратурных составляющих, 2 - постоянный множитель, определяющий граничную частоту цифрового фильтра нижних частот первого порядка.

Первый перемножитель 13 в блоке 3 является синхронным детектором, составлякицие когерентного напряжения для которого формируются на соответствующих выходах цифровых фильтров 17 и 18.

Сигнал с выхода блока 3 поступает на вход блока 4 измерения величины рассогласования по частоте. В началь- ные моменты анализа может иметь место большая величина расстройки несущей частоты (до сотен герц). Такая рас- синхронизация измеряется в блоке 4, Для этого за фиксированные интервалы времени, формируемые датчиком 38 меток времени, подсчитывается количество переходов при вращении вектора сигнала разностной частоты относительно условных осей координат. Такой пово- рот вектора сигнала осуществляется

При анализе используются только 8 из 16-ти возможных кодовых комбинаций знаков проекций, которые однозначно определяют направление вращения вектора Н.

Импульсные сигналы с выходов дешиф ратора 33 объединяются элементом ИЛИ 34 или элементом ИЛИ 35 в зависимости от знака рассогласования по частоте и поступают далее соответственно на вход сложения или вычитания реверсивного счетчика 36. С помощью реверсивного счетчика 36 осуществляется инс помощью элементов 29 и 30 выделк- НИН знака квадратурных составляющих сигнала разностной частоты.

Определение количества переходов вектора сигнала разностной частоты относительно осей координат в блоке 4 осуществляется с помощью дешифратора 33 по изменению знаков проекций между соседними посылками сигнала разностной частоты. Запоминание знаков проекций этого сигнала осуществляется с помощью элементов 31 и 32 задержки. Принцип измерения величины и знака рассогласования по частоте поясняется с помощью таблицы.

тегрирование сигнала рассогласования по частоте за время, определяемое датчиком 38 меток. Сигнал рассогласования (в виде кодового числа) с выхода реверсивного счетчика поступает через ключ 37 на вход подстройки по частоте подстраиваемого генератора 5. В подстраиваемом генераторе 5 сигнал кйр рекции частоты с помощью сумматора 39 складывается с хранящимся в памяти регистра 40 сдвига сигналом коррекции частоты, вычисленным ранее. С помощью выходных кодовых сигналов ре

гистра 40 сдвига открываются соответствующие элементы И 44. При этом импульсные сигналы с отводов делителя 41, пройдя через открытые элементы И 44, объединяются элементом ИЛИ 45 и поступают на сигна,пьный вход логического переключателя 46, Сигнал знака расстройки по частоте поступает на управляющий вход переключателя 46 с выхода знакового разряда регистра 40 сдвига. В зависимости от знака расстройки импульсный сигнал с выхода логического переключателя 46 поступает на вход узла 48 добавления (или вычитания импульсов.

За счет добавления (вычитания) импульсов на входе делителя 43 с частотой, соответствующей расстройке несущей частоты, осуществляется плавная подстройка по частоте выходных сигналов узла 49 формирования в подстраиваемом генераторе 5. В результате осуществляется коррекция несущей частоты подстраиваемого генератора.

Формула изобретения

Устройство автоподстройки нес уп ей частоты, содержащее квадратурный преобразователь фазоманипулированного сигнала в видеочастотный, а также последовательно соединенные блок измерения величины рассогласования по частоте и подстраиваемьш генератор, выход которого соединен с входом уп- равленй ,квадратзфного преобразователя фазоманипулированного сигнала в видеочасготный, отличающе0

5

5

еся тем, что, с целью повьшгекия помехоустойчивости при цифровой обработке сигнала, в него введены аналого-цифровой преобразователь, вход которого является входом устройства, а выход подключен к входу квадратурного преобразователя фазоманипулированного сигнала в видеочастотный, и блок выделения сигнала разностной частоты, включенный между выходами квадратурного преобразователя фазоманипулированного сигнала в видеочастотный и входами блока измерения велич 1ны рассогласования по частоте, и выполненный в виде первого и второго перемножителей сигнала в комплексной форме, первые сигнальные входы первого и второго перемножителей объединены и являются синфазным входом блока вьщеления сигнала разностной частоты, вторые сигнальные входы первого и второго перемножителей объединены и являются квадратурным входом блока выделения сигнала разностной частоты, первого и второго решающих блоков, включенных каждый между соответствующим выходом первого перемножителя и соответствующим опорным входом второго перемножи -еля, и первого и второго цифровых фильтров нижних частот, включенных каждый между соответствзтощим выходом второго перемножителя и соответствующим опорным входом первого перемножителя, при этом выходы цифровых фильтров нижних частот являются выходами блока вьщеления сигнала разностной частоты.

Фиг.2

Составитель С.Даниэлян Редактор Л.Гратилло Техред А.Кравчук Корректор Л.Пилипенко

Заказ 901/61 Тираж 639 . Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Фие.З

Фиг. 5

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ автоматической подстройки частоты генератора опорного сигнала | 1974 |

|

SU758527A1 |

| Устройство выделения опорного напряжения из сигнала, манипулированного по фазе | 1975 |

|

SU1338070A1 |

| КОРРЕЛЯЦИОННЫЙ ПРИЕМНИК ШУМОПОДОБНЫХ СИГНАЛОВ С МИНИМАЛЬНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 2008 |

|

RU2374776C2 |

| Устройство для восстановления несущей частоты | 1974 |

|

SU720665A1 |

| Устройство для восстановления несущей частоты | 1975 |

|

SU1046941A1 |

| КОРРЕЛЯЦИОННЫЙ ПРИЕМНИК ШУМОПОДОБНЫХ СИГНАЛОВ С МИНИМАЛЬНОЙ ЧАСТОТНОЙ МОДУЛЯЦИЕЙ | 2014 |

|

RU2548010C1 |

| КОРРЕЛЯЦИОННЫЙ ПРИЕМНИК ШУМОПОДОБНЫХ СИГНАЛОВ | 2010 |

|

RU2431919C1 |

| СПОСОБ ПРИЕМА ШУМОПОДОБНЫХ СИГНАЛОВ С МИНИМАЛЬНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 2006 |

|

RU2307474C1 |

| УСТРОЙСТВО КОМПЕНСАЦИИ СТРУКТУРНЫХ ПОМЕХ | 2010 |

|

RU2450445C2 |

| СПОСОБ ДЕМОДУЛЯЦИИ СИГНАЛОВ С ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МАНИПУЛЯЦИЕЙ И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2000 |

|

RU2168869C1 |

Изобретение относится к радиосвязи. Цель изобретения - повышение помехоустойчивости при цифровой обработке сигнала. Устр-во содержит АЦП 1, квадратурный преобразователь 2 фазоманипулированного сигнала в видеочастотный, соетоящ11й из перемножителей 6 и 7, фазовращателя 8 на 90 , сумматоров-интеграторов 9 и 10 и элементов памяти 11 и t2, блок вьщеления (БВ) 3 сигнала разностной частоты, состоящий из перемножителей 13 и 16 сигналов в комплексной форме, решающих блоков 14 и 15 и цифровых фильтров 17 и 18 нижних частот, блок измерения (БИ) 4 величины рассогласования по частоте и подстраиваемый генератор (Г) 5. Цель достигается введением АЦП 1 и БВ 3, с помощью которых осуществляется коррекция несущей частоты Г 5. 5 ил. 1 табл. выкод 00 оэ Фи.г.1

| Синхронный приемник фазоманипулированного сигнала | 1974 |

|

SU486486A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1987-03-23—Публикация

1984-11-11—Подача